## Offline Inductor-less AC Linear Regulator

### **FEATURES**

High Output Voltage Accuracy: 2%

Programmable Output: 5V/3.3V/2.7V

Smart Control to Maximize Efficiency

Universal Input Range: 80~305VAC

- No Inductor Required

- No Bulk Capacitor Required

- Less Components and Low Cost

- Fast Line and Load Transient Response

- Short Load Protection

- Output Under Voltage Protection (UVP)

- Over Load Protection(OLP)

- On Chip Thermal Shutdown

- Available with SOP8 Package

### **APPLICATIONS**

- Non Isolation AC/DC Converter

- Home Appliance

- Wall Switches and Dimmers

### **GENERAL DESCRIPTION**

KP3310 is a compact, inductor-less, offline linear regulator. It steps down the AC line voltage to 5V/3.3V/2.7V based on SEL pin program. It is a simple solution to provide a bias voltage in offline applications.

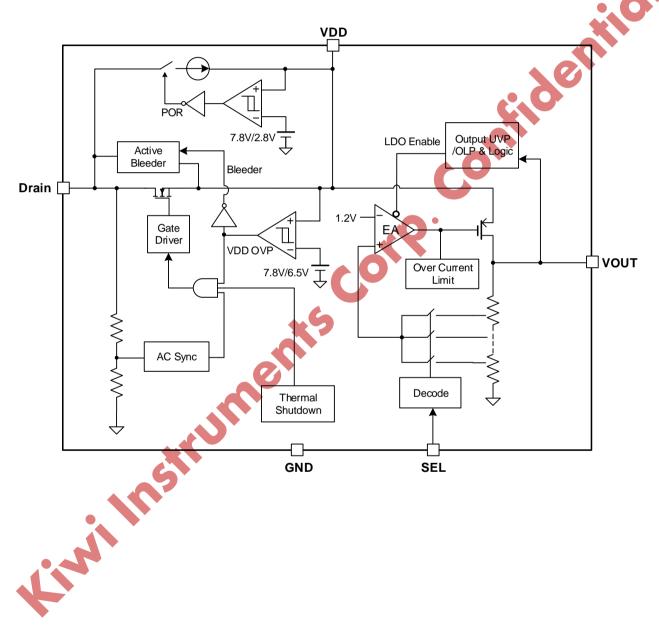

KP3310 integrates a 650V power MOSFET, startup controller, voltage control circuit, AC synchronous circuit, low dropout regulator, etc. The IC also integrates smart control system using AC line power when necessary, thus minimizing device losses to achieve good efficiency. The IC can help system designs meeting new standby power specifications.

KP3310 integrates functions and protections of Under Voltage Lockout (UVLO), VDD over Voltage Protection (VDD OVP), Over Load Protection (OLP), Output Under Voltage Protection (UVP), On-chip Thermal Shutdown, etc.

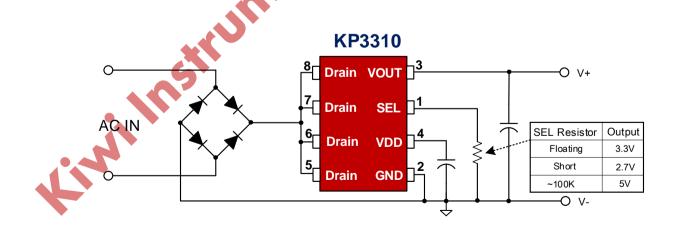

## TYPICAL APPLICATION CIRCUIT

# **Pin Configuration**

## **Marking Information**

# **Pin Description**

| Pin Number | Pin Name | I/O | Description                                                                                                                                |  |  |  |

|------------|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1          | SEL      | 4   | Selection pin. If floating, the LDO outputs 3.3V. If short to GND, LDO outputs 2.7V. If connecting a 100K resistor to GND, LDO outputs 5V. |  |  |  |

| 2          | GND      | Р   | The ground of the IC                                                                                                                       |  |  |  |

| 3          | VOUT     | 0   | LDO output pin.                                                                                                                            |  |  |  |

| 4          | VDD      | Р   | Energy storage. Connect to GND with a capacitor to buffer energy for the output LDO stage.                                                 |  |  |  |

| 5,6,7,8    | Drain    | Р   | Internal power MOSFET drain pin. Provide energy when the voltage falls within the charging window.                                         |  |  |  |

# **Ordering Information**

| Part Number | Description                       |  |  |

|-------------|-----------------------------------|--|--|

| KP3310SGA   | SOP-8, Halogen free, 4000Pcs/Reel |  |  |

# **Block Diagram**

**Absolute Maximum Ratings** (Note 1)

| Parameter                              | Value      | Unit |

|----------------------------------------|------------|------|

| Drain Voltage                          | 650        | V    |

| VDD DC Supply Voltage                  | 9          | V    |

| VDD DC Clamp Current                   | 10         | mA   |

| VOUT, SEL Voltage Range                | -0.3 to 7  | V    |

| Package Thermal Resistance (SOP-8)     | 100        | °C/W |

| Maximum Junction Temperature           | 150        | °C   |

| Operating Temperature Range            | -40 to 85  | °C   |

| Storage Temperature Range              | -65 to 150 | °C   |

| Lead Temperature (Soldering, 10sec.)   | 260        | ∘C   |

| ESD Capability, HBM (Human Body Model) | 3          | kV   |

| ESD Capability, MM (Machine Model)     | 250        | V    |

**Recommended Operation Conditions** (Note 2)

| Parameter                     | Value     | Unit |  |

|-------------------------------|-----------|------|--|

| Operating Ambient Temperature | -40 to 85 | °C   |  |

**ELECTRICAL CHARACTERISTICS** (T<sub>A</sub> = 25°C, if not otherwise noted)

| Symbol                   | Parameter                                      | Test Conditions   | Min | Тур. | Max | Unit |  |  |  |

|--------------------------|------------------------------------------------|-------------------|-----|------|-----|------|--|--|--|

| High Voltag              | High Voltage Startup Section (Drain Pin)       |                   |     |      |     |      |  |  |  |

| I <sub>HV</sub>          | HV Current Source                              | HV=600V, VDD=3V   | 5   | 10   |     | mA   |  |  |  |

| I <sub>HV_leakage</sub>  | HV Leakage Current                             | HV=600V, VDD=8.5V |     |      | 20  | uA   |  |  |  |

| V <sub>BR</sub>          | Power MOSFET Drain<br>Source Breakdown Voltage |                   | 650 |      |     | V    |  |  |  |

| V <sub>AC_sync_OFF</sub> | AC Synchronization Turn OFF Voltage            |                   |     | 50   |     | V    |  |  |  |

| Supply Vol               | Supply Voltage Section (VDD Pin)               |                   |     |      |     |      |  |  |  |

| Ivdd_Op                  | Operation Current                              | lout=1mA          |     | 1.4  |     | mA   |  |  |  |

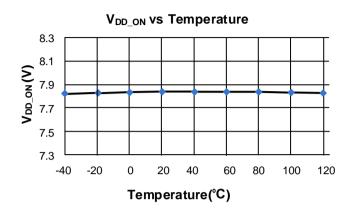

| V <sub>DD_ON</sub>       | VDD Under Voltage Lockout<br>Exit              |                   | 7.6 | 7.8  | 8   | V    |  |  |  |

| V <sub>DD_OFF</sub>      | VDD Under Voltage Lockout<br>Enter             |                   |     | 2.8  |     | V    |  |  |  |

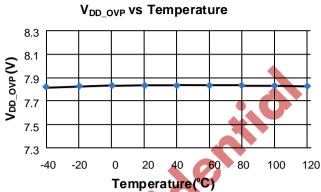

| V <sub>DD_OVP</sub>      | VDD OVP Threshold                              |                   | 7.6 | 7.8  | 8   | V    |  |  |  |

| VDD_OVP_hys              | VDD OVP Threshold Hysteresis                   |                   | 6.3 | 6.5  | 6.7 | V    |  |  |  |

| VOUT Sect                | VOUT Section (VOUT Pin)                        |                   |     |      |     |      |  |  |  |

# KP3310 Offline Inductor-less AC Linear Regulator

|                          | <del>_</del>                                      |                                           |      |      |      |     |  |

|--------------------------|---------------------------------------------------|-------------------------------------------|------|------|------|-----|--|

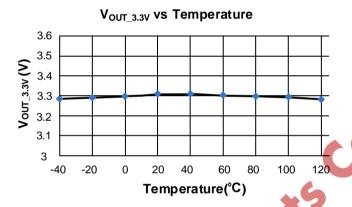

| V <sub>OUT_3.3</sub> v   | Output Voltage                                    | SEL=Floating, lout=2mA                    | 3.2  | 3.3  | 3.4  | V   |  |

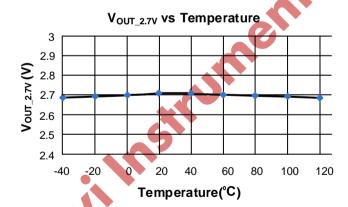

| V <sub>OUT_2.7</sub> V   | Output Voltage                                    | SEL=GND, lout=2mA                         | 2.65 | 2.7  | 2.75 | V   |  |

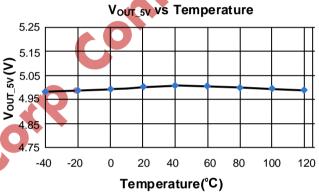

| V <sub>OUT_5V</sub>      | Output Voltage                                    | SEL=100K to GND, lout=2mA                 | 4.9  | 5    | 5.1  | V   |  |

| ILIM                     | Output Current Limit                              |                                           | 100  | 138  | 160  | mA  |  |

| V <sub>UVP</sub>         | Output Under Voltage<br>Protection                |                                           | 10   | 12.5 | 15   | %   |  |

| Δ V <sub>OUT(VIN)</sub>  | Line Regulation dVout/dVin                        | lout=100uA                                |      | 0.2  |      | %/V |  |

| PSRR                     | Power Supply Rejection<br>Ratio                   | Iout=30mA, Cout=4.7uF,<br>f=10Hz to 60KHz |      | 60   |      | dB  |  |

| SEL Section              | SEL Section (SEL Pin)                             |                                           |      |      |      |     |  |

| İsel                     | SEL Pin Pull up Current                           |                                           | 0,   | 13   |      | uA  |  |

| V <sub>SEL_2.7V</sub>    | Below the Threshold Voltage, the LDO outputs 2.7V |                                           |      | 0.4  |      | V   |  |

| On-Chip Thermal Shutdown |                                                   |                                           |      |      |      |     |  |

| T <sub>SD</sub>          | Thermal Shutdown                                  | (Note 3)                                  |      | 160  |      | °C  |  |

| T <sub>RC</sub>          | Thermal Recovery                                  | (Note 3)                                  |      | 140  |      | °C  |  |

**Note1.** Stresses listed as the above "Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to maximum rating conditions for extended periods may remain possibility to affect device reliability.

**Note2.** The device is not guaranteed to function outside its operating conditions.

Note3. Guaranteed by the Design.

## **CHARACTERIZATION PLOT**

#### **OPERATION DESCRIPTION**

KP3310 is a compact, inductor free, and highly monolithic AC/DC linear converter which is designed for non-isolated AC/DC converter and home appliances. The IC covers universal AC voltage input to provide programmable DC output voltage with current limit for the non-isolated AC/DC converter.

## Startup Current

During KP3310 startup, the internal high voltage current source (10mA) charges the VDD capacitor though the rectifier and Drain pin. The IC remains off until the VDD voltage is larger than V<sub>DD\_ON</sub> and the output voltage is built up at the same time. After the IC turns on, the internal high voltage current source is disabled by the control loop. The major energy path changes from the high voltage current source to the inner power MOSFET.

## AC Synchronization with Active Bleeder Circuit

KP3310 integrates AC synchronization block through an internal resistor divider from Drain to GND. The AC synchronous signal is used to open the power MOSFET when AC voltage is under VAC\_sync\_OFF to charge the VDD cap.

The Drain voltage may not enter its charging interval during normal operation due to the parasitic capacitance from Drain to GND. An active bleeder circuit is enabled to pull down the Drain voltage when VDD falls below VDD\_OVP\_hys and disabled when VDD reaches VDD\_OVP, so that enough energy from the input ports can be delivered. In addition, when protection (UVP, OLP or OTP) occurs, the active bleeder circuit discharges the energy stored in the parasitic capacitor to VDD Cap to ensure that the circuit can restart easily.

## Programmable Output: 2.7V/3.3V/5V

In KP3310, the output can be programmed by SEL pin. If SEL pin is floating, the internal LDO will output 3.3V. If SEL is short to GND, the internal LDO will output 2.7V. If 5V output is needed, a 100K resistor is to be connected between SEL and GND.

## Output Current Limit

KP3310 includes a current limiter for safe LDO operation. The limiter monitors the loading current and directly controls the output delivery current of LDO. The typical limited current set is 138mA to avoid the output shorted to ground for an indefinite amount of time without damaging the part if no protection is triggered. At over current operation, the current limiter limits the maximum output current and causes the unregulated output voltage to drop until UVP function occurs.

## Output Under Voltage Protection(UVP)

When the output power is larger than the maximum handling power of KP3310, the condition causes the output voltage to drop. Until the output voltage is less than the nominal voltage -12.5%, the UVP function disables the LDO stage and waits for two AC synchronous signal then restart the KP3310 automatically.

### Over Load Protection(OLP)

When the output voltage decreases due to heavy load, UVP is triggered. If KP3310 continues stay in UVP for 50ms, Over Load Protection is triggered, the power MOSFET and LDO is shut down for the following 640ms (Auto Recovery Delay), and VDD is charged to VDD\_OVP level by the internal high voltage bleeder circuit.

## VDD Over Voltage Protection (VDD OVP)

After startup, KP3310 turns on the OVP function. During conduction angle interval, the VDD voltage has two kinds of behavior. One is that if the VDD capacitor recharges to OVP trigger point (7.8V typical), KP3310 turns off the internal power MOSFET to limit the maximum VDD voltage. The other is that if the voltage of VDD cannot recharge to the OVP level during the conduction interval, the power MOSFET is turned off by AC synchronous signal and continuously recharges VDD capacitor at next duration. Using this technique, energy is drawn from the AC mains only during the low voltage portions of each half cycle. During the power MOSFET turn-on, the current provided by the commutated AC voltage is used to supply the loads and to charge the VDD capacitor. In this way, when the power MOSFET switches off, the loads receive the required currents by the capacitor discharge.

For the VDD capacitor selection, during the conduction angle interval, the energy is drawn from commutated AC bus, which not only meets the output load requirement but also recharges the VDD capacitor to OVP level. Outside of conduction angle, the VDD capacitor can is determined by the maximum loading current:

$$C_{VDD} \approx 0.01 \times I_{LOAD}$$

(unit = F)

## Surge Protection

When Surge happens, AC voltage couples a very high spike voltage. If this spike voltage is higher than 100Vdc and occurs within the AC charging window, Surge Protection is triggered, the power MOSFET shuts down quickly and IC enters Auto-Restart progress.

## On Chip Thermal Shutdown (OTP)

When the IC temperature is over 160 °C, the IC shuts down. Only when the IC temperature drops to 140 °C, IC will enter Auto-Restart progress.

#### Protections with Auto-Restart

In the event of protections such as OTP, OLP, Surge Protection, the IC enters auto-restart and an internal timer begins counting, wherein the power MOSFET is disabled. When 640ms delay had been counted, the IC will reset and start up the system again. However, if the fault still exists, the system will experience the above-mentioned process.

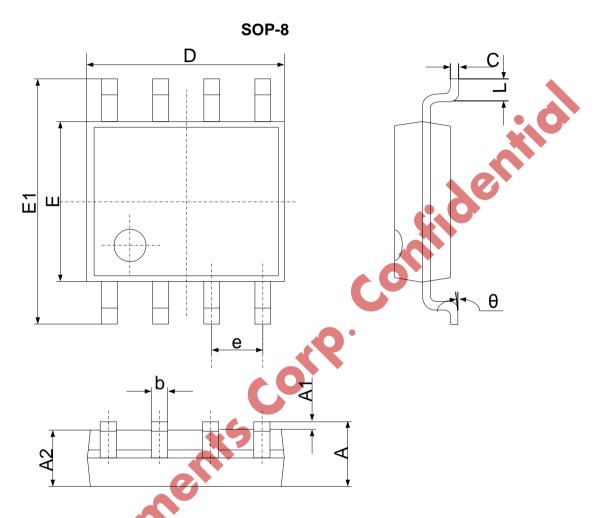

# **Package Dimension**

| Symbol | Dimensions In Millimeters |       | Dimensions In Inches |       |  |

|--------|---------------------------|-------|----------------------|-------|--|

| Symbol | Min                       | Max   | Min                  | Max   |  |

| Α      | 1.350                     | 1.750 | 0.053                | 0.069 |  |

| A1     | 0.100                     | 0.250 | 0.004                | 0.010 |  |

| A2     | 1.350                     | 1.550 | 0.053                | 0.061 |  |

| b      | 0.330                     | 0.510 | 0.013                | 0.020 |  |

| С      | 0.170                     | 0.250 | 0.006                | 0.010 |  |

| D      | 4.700                     | 5.100 | 0.185                | 0.200 |  |

| E      | 3.800                     | 4.000 | 0.150                | 0.157 |  |

| E1     | 5.800                     | 6.200 | 0.228                | 0.244 |  |

| е      | 1.270 (BSC)               |       | 0.050                | (BSC) |  |

| Ĺ      | 0.400                     | 1.270 | 0.016                | 0.050 |  |

| θ      | 00                        | 80    | 00                   | 8°    |  |

**Revision History**

| DATE               |       | EV.        |        | DESCRIPTIO                         | DN                         |

|--------------------|-------|------------|--------|------------------------------------|----------------------------|

| 2018/03/23         | ,     | 1.0        |        | First Releas                       | e                          |

| Contact U          | s:    |            |        |                                    |                            |

| US                 |       |            |        | Hangzhou                           | Shenzhen                   |

| <b>Add:</b> 2060 V | Valsh | Ave, Suite | e 244, | Add: Room 1201, Building C, No.581 | Add: B302-B303, University |

# **Contact Us:**

Add: 2060 Walsh Ave, Suite 244, Santa Clara, CA, 95050

**Tel**: 1-408-475-6888 Fax: 1-408-905-6912

E-mail: marketing@kiwiinst.com

Add: Room 1201, Building C, No.581 HuoJu Rd., Binjiang Dist., Hangzhou,

P.R.C

**Tel:** (86) 571-8795-8612 Fax: (86) 571-8795-5363

E-mail: marketing@kiwiinst.com

Add: B302-B303, University Creative Park, Xili Rd., Nanshan

Dist., Shenzhen, P.R.C Tel: (86)755-8204-2689 Fax: (86)755-8204-2192

E-mail: marketing@kiwiinst.com

# Disclaimer

Information that is provided by Kiwi Instruments Corporation is believed to be accurate and reliable. Kiwi instrument reserves the right to make any change in circuit design, specification or other related things if necessary without notice at any time. No third party intellectual property infringement of the applications should be guaranteed by users when integrating Kiwi instrument products into any application. No legal responsibility for any said applications is assumed by Kiwi Instrument.