# Single-Chip 3-Axis Accelerometer QMA6981

The QMA6981 is a single chip three-axis accelerometer. This surface-mount, small sized chip has an integrated acceleration transducer with signal conditioning ASIC, sensing tilt, motion, shock and vibration. It is targeted for applications such as screen rotation, step counting, sleep quality, gaming and personal navigation in mobile and wearable smart devices.

The QMA6981 is based on our state-of-the-art, high resolution single crystal silicon MEMS technology. Along with custom-designed 10-bit ADC ASIC, it offers the advantages of low noise, high accuracy, low power consumption, and offset trimming. The I<sup>2</sup>C serial bus allows for easy interface.

The QMA6981 is in a 2mmx2mmx0.95mm surface mount 12-pin land grid array (LGA) package.

#### **FEATURES**

- 3-Axis Accelerometer in a 2x2x0.95 mm<sup>3</sup> Land Grid Array Package (LGA), guaranteed to operate over a temperature range of -40 °C to +85 °C.

- 10-Bit ADC with low noise accelerometer sensor

- ▶ I<sup>2</sup>C Interface with Standard and Fast modes.

- Built-In Self-Test

- Wide range operation voltage (2.4V To 3.6V) and low power consumption (27-50μA low power conversion current)

- Integrated FIFO with a depth of 32 frames

- RoHS compliant , halogen-free

- ▶ Built-in motion algorithm

#### BENEFIT

- Small size for highly integrated products. Signals have been digitized and factory trimmed.

- High resolution allows for motion and tilt sensing

- High-Speed Interfaces for fast data communications.

- Enables low-cost functionality test after assembly in production

- Automatically maintains sensor's sensitivity under wide operation voltage range and compatible with battery powered applications

- ▶ High Data-Read rate

- Environmental protection and wide applications

- Low power and easy applications including step counting, sleep quality, gaming and personal navigation

Rev: C

# **CONTENTS**

| CO | NTEN   | TS                                                             | 2  |

|----|--------|----------------------------------------------------------------|----|

| 1  | INTE   | ERNAL SCHEMATIC DIAGRAM                                        | 3  |

|    | 1.1    | Internal Schematic Diagram                                     | 3  |

| 2  | SPEC   | CIFICATIONS AND I/O CHARACTERISTICS                            |    |

|    | 2.1    | Product Specifications                                         |    |

|    | 2.2    | Absolute Maximum Ratings                                       |    |

|    | 2.3    | I/O Characteristics                                            |    |

| 3  | PAC    | KAGE PIN CONFIGURATIONS                                        | 5  |

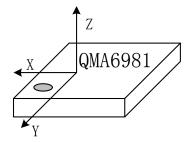

|    | 3.1    | Package 3-D View                                               |    |

|    | 3.2    | Package Outlines                                               |    |

| 4  | EXT    | ERNAL CONNECTION                                               |    |

|    | 4.1    | Dual Supply Connection                                         |    |

|    | 4.2    | Single Supply connection                                       |    |

| 5  | BAS    | IC DEVICE OPERATION                                            |    |

|    | 5.1    | Acceleration Sensors                                           | 10 |

|    | 5.2    | Power Management                                               | 10 |

|    | 5.3    | Power On/Off Time                                              | 10 |

|    | 5.4    | Communication Bus Interface I <sup>2</sup> C and Its Addresses | 11 |

| 6  | MOI    | DES OF OPERATION                                               | 12 |

|    | 6.1    | Modes Transition                                               | 12 |

|    | 6.2    | Description of Modes                                           |    |

| 7  | Func   | etions and interrupts                                          | 14 |

|    | 7.1    | POL_INT                                                        | 14 |

|    | 7.2    | FOB_INT                                                        |    |

|    | 7.3    | STEP/STEP_QUIT INT                                             |    |

|    | 7.4    | TAP_INT                                                        | 16 |

|    | 7.5    | LOW-G_INT                                                      | 18 |

|    | 7.6    | HIGH-G_INT                                                     |    |

|    | 7.7    | DRDY_INT                                                       |    |

|    | 7.8    | FIFO_INT                                                       |    |

|    | 7.9    | Interrupt configuration                                        |    |

| 8  | $I^2C$ | COMMUNICATION PROTOCOL                                         |    |

|    | 8.1    | I <sup>2</sup> C Timings                                       |    |

|    | 8.2    | I <sup>2</sup> C R/W Operation                                 |    |

| 9  | REG    | SISTERS                                                        |    |

|    | 9.1    | Register Map                                                   |    |

|    | 9.2    | Register Definition                                            | 25 |

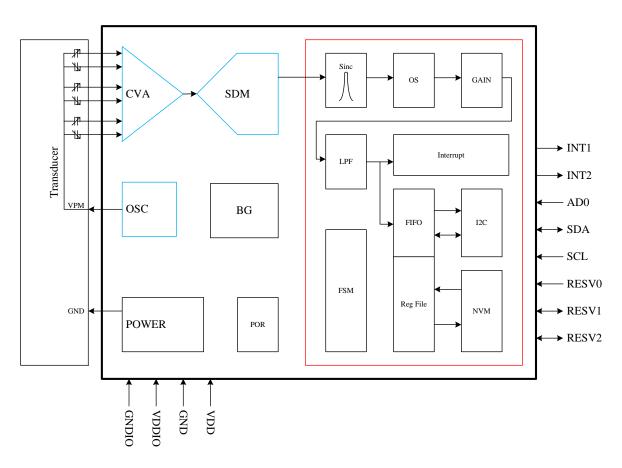

## 1 INTERNAL SCHEMATIC DIAGRAM

# 1.1 Internal Schematic Diagram

Figure 1. Block Diagram

Table 1. Block Function

| Block            | Function                                                                                             |

|------------------|------------------------------------------------------------------------------------------------------|

| Transducer       | 3-axis acceleration sensor                                                                           |

| CVA              | Charge-to-Voltage amplifier for sensor signals                                                       |

| Interrupt        | Digital interrupt engine, to generate interrupt signal on data conversion, FIFO, and motion function |

| FIFO             | Embedded 32-level FIFO                                                                               |

| FSM              | Finite state machine, to control device in different mode                                            |

| I <sup>2</sup> C | Interface logic data I/O                                                                             |

| OSC              | Internal oscillator for internal operation                                                           |

| Power            | Power block, including LDO                                                                           |

# 2 SPECIFICATIONS AND I/O CHARACTERISTICS

## 2.1 Product Specifications

Table 2. Specifications (\* Tested and specified at 25°C and 3.0V VDD except stated otherwise.)

| Parameter                          | Conditions                                                                                                                             | Min | Тур            | Max | Unit            |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----|----------------|-----|-----------------|

| Supply voltage VDD                 | VDD, for internal blocks                                                                                                               | 2.4 | 3.3            | 3.6 | V               |

| I/O voltage VDDIO                  | VDDIO, for IO only                                                                                                                     | 1.7 |                | VDD | V               |

| Standby current                    |                                                                                                                                        |     | 2              |     | μA              |

| Low power current                  | er current BW=500 Hz, ODR=1 Hz                                                                                                         |     | 27             |     | μA              |

| Low power current                  | w power current BW=500 Hz, ODR=10 Hz                                                                                                   |     | 29             |     | μA              |

| Low power current                  | BW=500 Hz, ODR=20 Hz                                                                                                                   |     | 31             |     | μA              |

| Low power current                  | BW=500 Hz, ODR=40 Hz                                                                                                                   |     | 37             |     | μA              |

| Low power current                  | BW=500 Hz, ODR=100 Hz                                                                                                                  |     | 50             |     | μΑ              |

| Full run current                   | All blocks on, device in run state                                                                                                     |     | 220            | 300 | μA              |

| Sleep current                      | For analog, AFE is off, BG, Transducer<br>and oscillator are on or in low power<br>mode<br>For digital, only counter and FSM are<br>on |     | 55             |     | μА              |

| Deep sleep current                 | For analog, only BG and oscillator are on For digital, only counter and FSM are on                                                     |     | 26             |     | μА              |

| BW                                 | Programmable bandwidth                                                                                                                 |     | 3.9~500        |     | Hz              |

| Data output rate (ODR)             | 4*BW (ODRH=1)                                                                                                                          |     | 15.6~2000      |     | Samples<br>/sec |

| Conversion time                    | in full speed                                                                                                                          |     | 1/(4*BW)       |     | ms              |

| Startup time                       | From the time when VDD reaches to 90% of final value to the time when device is ready for conversion                                   |     | 2              |     | ms              |

| Wakeup time                        | From the time device enters into active mode to the time device is ready for conversion                                                |     | 1              |     | ms              |

| Operating temperature              |                                                                                                                                        | -40 |                | 85  | ${\mathbb C}$   |

| Acceleration Full Range            |                                                                                                                                        |     | ±2<br>±4<br>±8 |     | g               |

| Sensitivity                        | FS=±2g                                                                                                                                 |     | 256            |     | LSB/g           |

| Sensitivity                        | FS=±4g                                                                                                                                 |     | 128            |     | LSB/g           |

| Sensitivity                        | FS=±8g                                                                                                                                 |     | 64             |     | LSB/g           |

| Sensitivity Temperature Drift      | FS=±2g, Normal VDD Supplies                                                                                                            |     | ±0.02          |     | %/℃             |

| Sensitivity tolerance              | Gain accuracy                                                                                                                          |     | ±5             |     | %               |

| Zero-g offset                      | FS=±2g, Normal VDD Supplies                                                                                                            |     | ±80            |     | mg              |

| Zero-g offset<br>Temperature Drift | FS=±2g, Normal VDD Supplies                                                                                                            |     | ±2             |     | mg/℃            |

| Noise density                      | FS=±2g, run state                                                                                                                      |     | 600            |     | μg/sqrtHz       |

| Nonlinearity                       | FS=±2g, Best fit straight line,                                                                                                        |     | ±0.5           |     | %FS             |

| The information contained herein is the exclusive property of QST, and shall not be distributed, |

|--------------------------------------------------------------------------------------------------|

| reproduced, or disclosed in whole or in part without prior written permission of QST.            |

Rev: C

| Parameter   | Conditions | Min | Тур | Max | Unit |

|-------------|------------|-----|-----|-----|------|

| Cross Axis  |            |     | 1   |     | %    |

| Sensitivity |            |     | '   |     | 70   |

## 2.2 Absolute Maximum Ratings

Table 3. Absolute Maximum Ratings (Tested at 25°C except stated otherwise.)

| Parameters          | Condition        | Min  | Max   | Units      |

|---------------------|------------------|------|-------|------------|

| VDD                 |                  | -0.3 | 5.4   | V          |

| VDDIO               |                  | -0.3 | 5.4   | V          |

| ESD                 | HBM              |      | 2     | kV         |

| Shock Immunity      | Duration < 200µS |      | 10000 | g          |

| Storage temperature |                  | -50  | 150   | $^{\circ}$ |

#### 2.3 I/O Characteristics

Table 4. I/O Characteristics

| Parameter      | Symbol            | Pin         | Condition      | Min.   | TYP. | Max.   | Unit |

|----------------|-------------------|-------------|----------------|--------|------|--------|------|

| Voltage Input  | V <sub>IH</sub> 1 | SDA, SCL    |                | 0.7*VD |      | VDDIO+ | V    |

| High Level 1   |                   |             |                | DIO    |      | 0.3    |      |

| Voltage Input  | V <sub>IL</sub> 1 | SDA, SCL    |                | -0.3   |      | 0.3*VD | V    |

| Low Level 1    |                   |             |                |        |      | DIO    |      |

| Voltage Output | $V_{OH}$          | INT1, INT2  | Output Current | 0.8*VD |      |        | V    |

| High Level     |                   |             | ≥-100µA        | DIO    |      |        |      |

| Voltage Output | $V_{OL}$          | INT1, INT2, | Output Current |        |      | 0.2*VD | V    |

| Low Level      |                   | SDA         | ≤100µA(INT)    |        |      | DIO    |      |

|                |                   |             | Output Current |        |      |        |      |

|                |                   |             | ≤1mA (SDA)     |        |      |        |      |

## 3 PACKAGE PIN CONFIGURATIONS

#### 3.1 Package 3-D View

Arrow indicates direction of g field that generates a positive output reading in normal measurement configuration.

Figure 2. Package View

Table 5. Pin Configurations

| PIN | PIN   | I/O | Power  | TYPE  | Function                          |  |

|-----|-------|-----|--------|-------|-----------------------------------|--|

| No. | NAME  |     | Supply |       |                                   |  |

| 1   | AD0   | I   | VDDIO  | CMOS  | LSB of I <sup>2</sup> C address   |  |

| 2   | SDA   | 10  | VDDIO  | CMOS  | Serial data for I <sup>2</sup> C  |  |

| 3   | VDDIO |     | VDDIO  | Power | Power supply to digital interface |  |

| 4   | RESV0 | I   | VDDIO  | CMOS  | Reserved. Float or connect to GND |  |

| 5   | INT1  | 0   | VDDIO  | CMOS  | Interrupt 1                       |  |

| 6   | INT2  | 0   | VDDIO  | CMOS  | Interrupt 2                       |  |

| 7   | VDD   |     | VDD    | Power | Power supply to internal block    |  |

| 8   | GNDIO |     | GND    | Power | Ground to digital interface       |  |

| 9   | GND   |     | GND    | Power | Ground to internal block          |  |

| 10  | RESV1 | IO  | VDDIO  | CMOS  | Reserved                          |  |

| 11  | RESV2 | IO  | VDDIO  | CMOS  | Reserved                          |  |

| 12  | SCL   | I   | VDDIO  | CMOS  | Serial clock for I <sup>2</sup> C |  |

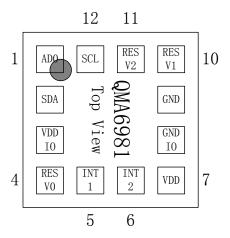

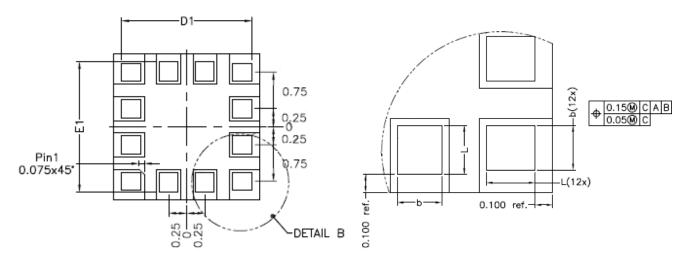

## 3.2 Package Outlines

#### 3.2.1

Package Type LGA (Land Grid Array)

#### 3.2.2 **Package Outline Drawing:**

2.0mm (Length)\*2.0mm (Width)\*0.95mm (Height)

Rev: C

**TOP VIEW**

**DETAIL A**

**SIDE VIEW**

**BOTTOM VIEW**

**DETAIL B**

Rev: C

|        |          | OIMENSION | V     | DIMENSION |         |       |  |

|--------|----------|-----------|-------|-----------|---------|-------|--|

| SYMBOL | (MM)     |           |       | (inch)    |         |       |  |

|        | MIN.     | NØM.      | MAX.  | MIN.      | NOM.    | MAX.  |  |

| Α      | 0.90     | 0.95      | 1.00  | 0.035     | 0.037   | 0.039 |  |

| С      | 0.16     | 0.20      | 0.24  | 0.006     | 0.008   | 0.009 |  |

| р      | 0,20     | 0.25      | 0.30  | 0.008     | 0.010   | 0.012 |  |

| D      | 1.95     | 2.00      | 2.05  | 0.077     | 0.079   | 0.081 |  |

| D1     |          | 1.80 BSC  |       |           | .071 BS | С     |  |

| Ε      | 1.95     | 2.00      | 2.05  | 0.077     | 0.079   | 0.081 |  |

| E1     | 1.80 BSC |           | ;     | C         | .071 BS | С     |  |

| L      | 0.225    | 0.275     | 0.325 | 0.010     | 0.012   | 0.014 |  |

Figure 3. Package Outline Drawing

## 3.2.3 Marking:

6981 YCCC • SP

Figure 4. Marking Format

| Marking Text | Description                 | Comments                                                   |

|--------------|-----------------------------|------------------------------------------------------------|

| Line 1       | Product Name                | "6981" stand for QMA6981                                   |

| Line 2       | Y: the last digital of year | Lot code: 3 alphanumeric digits, variable to generate mass |

|              | CCC: lot code               | production trace-code                                      |

| Line3        | P: Part number              | P: 1 alphanumeric digit, variable to identify part number  |

|              | S: Sub-con ID               | S: 1 alphanumeric digit, variable identify sub-con         |

| •            | Pin 1 identifier            |                                                            |

Rev: C

## **4 EXTERNAL CONNECTION**

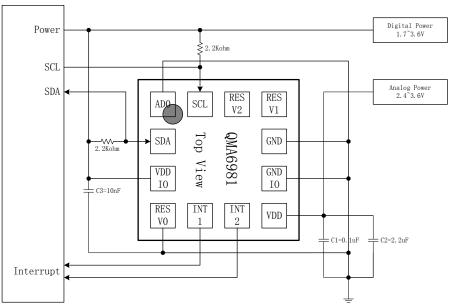

## 4.1 **Dual Supply Connection**

Figure 5. Dual Supply Connection

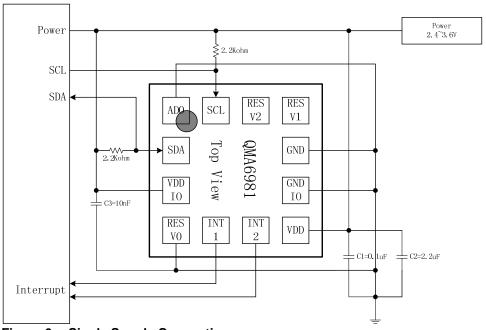

# 4.2 Single Supply connection

Figure 6. Single Supply Connection

## 5 BASIC DEVICE OPERATION

#### 5.1 Acceleration Sensors

The QMA6981 acceleration sensor circuit consists of tri-axial sensors and application specific support circuits to measure the acceleration of device. When a DC power supply is applied to the sensor, the sensor converts any accelerating incident in the sensitive axis directions to charge output.

## 5.2 Power Management

Device has two power supply pins. VDD is the main power supply for all of the internal blocks, including analog and digital. VDDIO is a separate power supply, for digital interface only.

The device contains a power-on-reset generator. It generates reset pulse as power on, which can load the register's default value, for the device to function properly.

To make sure the POR block functions well, we should have such constrains on the timing of VDD and VDDIO.

The device should turn-on both power pins in order to operate properly. When the device is powered on, all registers are reset by POR, then the device transits to the standby mode and waits for further commends.

Table 6 provides references for four power states.

Table 6. Power States

| Power State | VDD       | VDDIO     | Power State description                                                                                                                          |

|-------------|-----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 1           | 0V        | 0V        | Device Off, No Power Consumption                                                                                                                 |

| 2           | 0V        | 1.7v~3.6v | Not allowed. User need to make sure that VDDIO is less than VDD. Otherwise, there will be leakage from VDDIO to VDD through internal ESD devices |

| 3           | 2.4v~3.6v | 0         | Device Off, Same Current as Standby Mode                                                                                                         |

| 4           | 2.4v~3.6v | 1.7v~VDD  | Device On, Normal Operation Mode, Enters Standby Mode after POR                                                                                  |

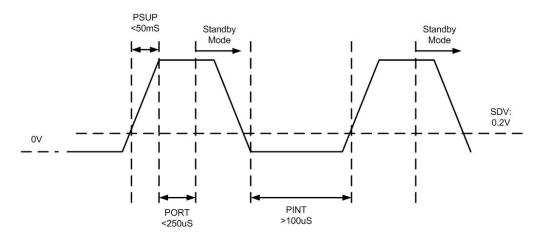

## 5.3 Power On/Off Time

After the device is powered on, some time periods are required for the device fully functional. The external power supply requires a time period for voltage to ramp up (PSUP), typically 50 milli-second. However it isn't controlled by the device. The Power–On–Reset time period (PORT) includes time to reset all the logics, load values in NVM to proper registers, enter the standby mode and get ready for analogy measurements. The power on/off time related to the device is in Table 7

#### Table 7. Time Required for Power On/Off

| The information contained herein is the exclusive property of QST, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of QST. | 10 / 34 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| R    | <b>6</b> 17 |   | C |

|------|-------------|---|---|

| - 1/ | CV.         | • | u |

| Parameter     | Symbol | Condition                              | Min. | Тур. | Max. | Unit |

|---------------|--------|----------------------------------------|------|------|------|------|

| POR           | PORT   | Time Period After VDD and              |      |      | 250  | μs   |

| Completion    |        | VDDIO at Operating Voltage to          |      |      |      |      |

| Time          |        | Ready for I <sup>2</sup> C Commend and |      |      |      |      |

|               |        | Analogy Measurement.                   |      |      |      |      |

| Power off     | SDV    | Voltage that Device Considers          |      |      | 0.2  | V    |

| Voltage       |        | to be Power Down.                      |      |      |      |      |

| Power on      | PINT   | Time Period Required for               | 100  |      |      | μs   |

| Interval      |        | Voltage Lower Than SDV to              |      |      |      |      |

|               |        | Enable Next POR                        |      |      |      |      |

| Power on Time | PSUP   | Time Period Required for               |      |      | 50   | ms   |

|               |        | Voltage from SDV to 90% of             |      |      |      |      |

|               |        | final value                            |      |      |      |      |

**Power On/Off Timing**

Figure 7. Power On/Off Timing

## 5.4 Communication Bus Interface I<sup>2</sup>C and Its Addresses

This device will be connected to a serial interface bus as a slave device under the control of a master device, such as the processor. Control of this device is carried out via I<sup>2</sup>C.

This device is compliant with I<sup>2</sup>C -Bus Specification, document number: 9398 393 40011. As an I<sup>2</sup>C compatible device, this device has a 7-bit serial address and supports I<sup>2</sup>C protocols. This device supports standard and fast speed modes, 100 kHz and 400 kHz, respectively. External pull-up resistors are required to support all these modes.

There are two I<sup>2</sup>C addresses selected by connecting pin 1 (AD0) to GND or VDDIO. The first six MSB are hardware configured to "001001" and the LSB can be configured by AD0.

Table 8. I<sup>2</sup>C Address Options

| AD0 (pin 1)      | I <sup>2</sup> C Slave Address(HEX) | I <sup>2</sup> C Slave Address(BIN) |

|------------------|-------------------------------------|-------------------------------------|

| Connect to GND   | 12                                  | 0010010                             |

| Connect to VDDIO | 13                                  | 0010011                             |

| The information contained herein is the exclusive property of QST, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of QST. |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

Rev: C

#### 6 MODES OF OPERATION

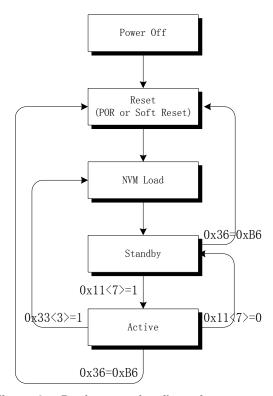

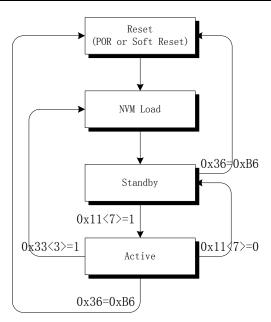

#### 6.1 Modes Transition

QMA6981 has two different operational modes, controlled by register (0x11), MODE\_BIT. The main purpose of these modes is for power management. The modes can be transited from one to another, as shown below, through  $I^2C$  commands. The default mode after power-on is standby mode.

Figure 8. Basic operation flow after power-on

The default mode after power on is standby mode. Through I<sup>2</sup>C instruction, device can switch between standby mode and active mode. With SOFTRESET by writing 0xB6 into register 0x36, all of the registers will get default values. SOFTRESET can be done both in active mode and in standby mode. Also, by writing 1 in NVM\_LOAD (0x33<3>) when device is in active mode, the NVM related image registers will get default value from NVM, however, other registers will keep the values of their own.

Figure 9. The work mode transferring

#### **6.2 Description of Modes**

#### 6.2.1 Active Mode

In active mode, there are two states, run state, and sleep state.

#### 6.2.1.1 Sleep State

In sleep state, whole signal chain is off, including analog and digital signal conditioning, and the rest blocks are on.

#### 6.2.1.2 Run State

In run state, the ADC digitizes the charge signals from transducer, and digital signal processor conditions these signals in digital domain, processes the interrupts, and send data to FIFO (accessible through register 0x3F) and Data registers (0x01~0x06). After the signal conditioning, the signal chain will be off and device enters back into sleep state, leaves timer and FSM on. Also in sleep state, reference and power blocks are on.

This mode can also be called as power cycling. The power cycling duty is configurable through state registers SLEEP\_DUR (0x11<3:0>). Device can enter into active mode by setting MODE\_BIT (0x11<7>) to logic 1. Besides the power cycling, device can also be configured as FULLRUN, by setting SLEEP\_DUR=0000b. In this setting, no sleep state in the active mode, and device consumes most power, deliver the data most frequently.

#### 6.2.2 Standby Mode

In standby mode, most of the blocks are off, while device is ready for access through  $I^2C$ . Standby mode is the default mode after power on or soft reset. Device can enter into this mode by set the soft reset register (0x36) to 0xB6 or set the MODE\_BIT (0x11<7>) to logic 0.

Besides the above two modes, the device also contains NVM loading state. This state is used to reset the value of the NVM related image registers. There are two bits related to this state. When NVM\_LOAD (0x33<3>) is set to 1, NVM loading starts. When the device is in NVM loading state, NVM\_RDY (0x33<2>) is set to logic 0 by device. After NVM loading is finished, NVM\_RDY (0x33<2>) is set back to logic 1 by device, and NVM\_LOAD is reset to 0 by device automatically. NVM loading can only happen when NVM\_LOAD is set to 1 in active mode. If the user sets this NVM\_LOAD bit to 1 in standby mode, the device will not take the action until it enters into active state by setting MODE\_BIT (0x11<7>) to logic 1.

After loading NVM, the device will enter into standby mode directly.

The loading time for NVM is about 100uS.

| The information contained herein is the exclusive property of QST, and shall not be distributed, |

|--------------------------------------------------------------------------------------------------|

| reproduced, or disclosed in whole or in part without prior written permission of QST.            |

Rev: C

## 7 Functions and interrupts

ASIC support interrupts, such as POL\_INT, FOB\_INT, STEP\_INT, TAP\_INT, LOW-G, HIGH-G, DRDY\_INT, and FIFO\_INT.

QMA6981

**Datasheet**

### 7.1 POL INT

The POL\_INT stands for Portrait or Landscape interrupt. It responds to the device in portrait direction or landscape direction. It includes 4 different event types, left, right, up and down events. The different type event stored and can be read from register ORIENT (0x0D<2:0>).

| POLA(0x0D<2:0>) | Left | Right | Down | Up | comments        |

|-----------------|------|-------|------|----|-----------------|

| 000             | 0    | 0     | 0    | 0  | unknown         |

| 001             | 1    | 0     | 0    | 0  | Left/Landscape  |

| 010             | 0    | 1     | 0    | 0  | Right/Landscape |

| 101             | 0    | 0     | 1    | 0  | Down/portrait   |

| 110             | 0    | 0     | 0    | 1  | Up/portrait     |

All different events can be detected by comparing the threshold set by register  $UD_X_TH(0x2D)$ ,  $RL_Y_TH(0x2F)$  with the sensor data , also have dependency on comparing result between the Z sensor readings and the register  $UD_Z_TH(0x2C)$  and  $RL_Z_TH(0x2E)$ . Hysteresis can be introduced to the angle by decreasing a small offset for the threshold registers. All angle data inside the Hysteresis area will be regarded as unknown status in the orient status register (0x0D<2:0>).

Below Table shows the condition four kinds of orient events generation, the default threshold for X, Y is set to 40 degrees

| Event | X          |      | Υ          |      | Z                              |

|-------|------------|------|------------|------|--------------------------------|

| Up    | X >UD_X_TH | X <0 |            |      | Z  <ud_z_th< th=""></ud_z_th<> |

| Down  | X >UD_X_TH | X >0 |            |      | Z  <ud_z_th< th=""></ud_z_th<> |

| Right |            |      | Y >RL_Y_TH | Y <0 | Z  <rl_z_th< th=""></rl_z_th<> |

| Left  |            |      | Y >RL_Y_TH | Y >0 | Z  <rl_z_th< th=""></rl_z_th<> |

For the registers settings, all the orient events threshold 1 LSB bit stand for 3.9mg. For Z axis, it is 8-bit signed 2's complement number ranged from 0.3g to 1.29g, default value 0 as stands for 0.8g. X, Y axis are unsigned data, default value A4 stands for 640mg which angel be regards as 40 degree, there will be around 10 degree dead band left. The degree value for event can be calculated by the equal asin(0.0039\*UD\_X\_TH) or asin(0.0039\*RL\_Y\_TH).

The related interrupt status bit is  $ORIENT_INT$  (0x0A<6>). When the POL status changes the value of  $ORIENT_INT$  will be set to logic 1, and this will be cleared after the interrupt status register is read by user.  $ORIENT_EN$  (0x16<6>) is the enable bit for the POL\_INT. Also, to get this interrupt on PIN\_INT1 and/or PIN\_INT2, we need to set INT1\_ORIENT (0x19<6>) or INT2\_ORIENT (0x1B<6>) to logic 1, to map the internal interrupt to the interrupt PINs.

#### **7.2 FOB INT**

The Front/back event can be detected by comparing Z axis data with a low g value, ranged from 0.1g to 0.6g, which is defined by FB  $\,$ Z  $\,$ TH(0x30<6:0>). The comparing condition shows below:

| The information contained herein is the exclusive property of QST, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of QST. | 14 / 34 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

Rev: C

| Event | Χ | Y | Z            |

|-------|---|---|--------------|

| Front |   |   | Z >FB_TH Z>0 |

| Back  |   |   | Z >FB_TH Z<0 |

The 2 different type events are stored and can be read from register ORIENT (0x0D<4:3>)

| FOB(0x0D<4:3>) | status   |

|----------------|----------|

| 00             | unknown  |

| 01             | Front    |

| 10             | Back     |

| 11             | Reserved |

Angle between the Z-axis and g can have the relationship:

$Acc_Z=1g * cos(theta).$

Each threshold will introduce a dark area, which the Front/Back status cannot be recognized, the dark area angel is +/- (90-theta).

When the threshold register value is 0x00, the default value stands for 0.1g, and 1 LSB is 3.91mg. The minimum angel between sensor and g direction should be 84 degree, so the dark area should be +/-6 degree. When the value is 0x7F, the dark area should be +/-37 degree.

The related interrupt status bit is FOB\_INT (0x0A<7>). When the FOB status changed, the value of FOB\_INT will be set to logic 1, and this will be cleared after the interrupt status register is read by user. FOB\_EN (0x16<7>) is the enable bit for the FOB\_INT. Also, to get this interrupt on PIN\_INT1 and/or PIN\_INT2, we need to set INT1\_FOB (0x19<7>) or INT2\_FOB (0x19<7>) to logic 1, to map the interrupt to the interrupt PINs.

## 7.3 STEP/STEP\_QUIT INT

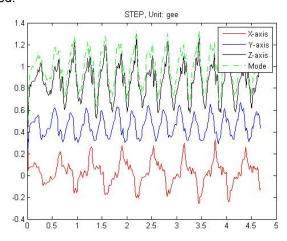

The STEP/STEP\_QUIT detect that the user is entering/exiting step mode. When the user enter into step mode, at least one axis sensor data will vary periodically, by numbering the variation periods the step counter can be calculated.

Figure 10. STEP/STEP\_QUIT

Median data (max+min) /2 is called dynamic threshold, the max and min data can be updated by certainly samples, the sample number can be set by register STEP\_SAMPLE\_CNT (0x12<4:0>). When the sensor data decreasing (or increasing) through the dynamic threshold, a user run step is detected.

| The information contained herein is the exclusive property of QST, and shall not be distributed, |

|--------------------------------------------------------------------------------------------------|

| reproduced, or disclosed in whole or in part without prior written permission of QST.            |

Rev: C

Register STEP PRECISION (0x13<6:0>) is used as threshold when updating the new collected sensor data. Sensor data below the threshold will be discarded, this helps removing unstable variations causing failed detection. The run step event happened at certain interval timing. All of the events outside the timing window will not be regarded as a run step and the step counter will not counted. The timing window can be set by register STEP\_TIME\_UP(0x15) and STEP\_TIME\_LOW(0x14), the conversion ODR numbers ranged from STEP\_TIME\_LOW \*ODR to 8\* STEP\_TIME\_UP\*ODR. Also if no new run step event detected until the up limited timing threshold, STEP\_QUIT INT will generation.

To remove unstable variation which will cause false STEP event detection, the step counter considers steps as valid step events only after 4 continuous steps detected. Also, the step counter register STEP\_CNT\_/ STEP CNT MSB (0x07,0x08) will be updated immediately by value 4, and interrupt STEP is also generated.

The related interrupt status bit is STEP INT (0x0A<3>) and STEP QUIT INT (0x0A<2>). When the interrupt is generated, the value of STEP\_INT/ STEP\_QUIT\_INT will be set to logic 1, which will be cleared after the interrupt status register is read by user. STEP\_EN/STEP\_QUIT\_EN (0x16<3>/0x16<2>) is the enable bit for the STEP\_INT/STEP\_QUIT\_INT. Also, to get this interrupt on PIN\_INT1 and/or PIN\_INT2, we need to set INT1\_STEP (0x19<3>)/INT1\_STEP\_QUIT (0x19<2>) or INT2\_STEP (0x18<3>) /INT2\_STEP\_QUIT (0x18<2>) to logic 1, to map the internal interrupt to the interrupt PINs.

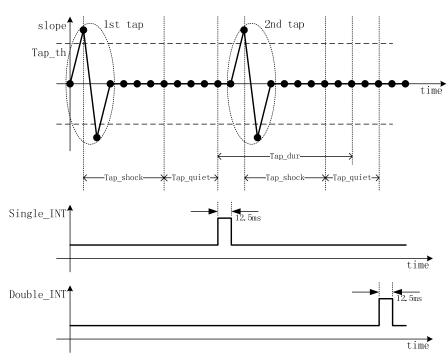

## **7.4 TAP INT**

Tap detection allows the device to detect events such as the clicking or double clicking of a touch-pad. A tap event is detected if a pre-defined slope (absolute value of acceleration difference) with acceleration of at least one axis is exceeded. The tap detection includes single tap (TAPS) and double tap (TAPD). A 'Single tap' is a single event within a certain time, followed by a certain quiet time. A 'double tap' consists of a first such event followed by a second event within a defined time frame.

Single tap interrupt can be enabled (disabled) by setting '1' ('0') to bit S TAP EN (0x16<5>). The double tap

detection can be enabled (disabled) by setting '1' ('0') to (0x16) D\_TAP\_EN (0x16<4>).

The status of single tap interrupt is stored in S\_TAP\_INT (0x0A<5>), and the status of double tap interrupt is stored in D\_TAP\_INT (0x0A<4>).

The slope threshold for detecting a tap event is set by register TAP\_TH (0x2B<4:0>). The meaning of an LSB of TAP\_TH (0x2B<4:0>) depends on the selected g-range: 1 LSB of the TAP\_TH is 62.5mg in 2g-range, 125mg in 4g-range, and 250mg in 8g-range.

In figure 11 the timing for single tap and double tap is visualized:

Figure 11. Timing of tap detection

The parameters TAP\_SHOCK (0x2A<6>) and TAP\_QUIET (0x2A<7>) are affected in both single tap and double tap detection, while TAP\_DUR (0x2A<2:0>) is affected in double tap detection only. Within the duration of TAP\_SHOCK, any slope exceeding TAP\_TH (0x2B<4:0>) after the first event will be ignored. Contrary to this, within duration of TAP\_QUIET, no slope exceeding TAP\_TH must occur; otherwise the first event will be cancelled. A single tap interrupt is generated after the combined duration of TAP\_SHOCK and TAP\_QUIET. The interrupt is cleared after a delay of 12.5ms.

A double tap interrupt is generated if an event fulfilling the conditions for a single tap occurs within the duration defined by TAP\_DUR after the completion of the first tap event. The interrupt is cleared after a delay of 12.5ms. For each of parameter TAP\_SHOCK and TAP\_QUIET two values are selectable. By writing '0' ('1') to bit TAP\_SHOCK, the duration of TAP\_SHOCK is set to 50ms (75ms). By writing '0' ('1') to bit TAP\_QUIET, the duration of TAP\_QUIET is set to 30ms (20ms).

The duration of TAP DUR can be set by TAP DUR bits:

| TAP_DUR | Duration of TAP_DUR |

|---------|---------------------|

| 000     | 50ms                |

| 001     | 100ms               |

| 010     | 150ms               |

| 011     | 200ms               |

| 100     | 250ms               |

| 101     | 375ms               |

| 110     | 500ms               |

| 111     | 700ms               |

The axis which triggered the interrupt is indicated by bits TAP\_FIRST\_X (0x0C<4>), TAP\_FIRST\_Y (0x0C<5>), and HIGH\_FIRST\_Z (0x0C<6>). The bit corresponding to the triggering axis contains a '1' while the other bits hold a '0'. These bits hold until new interrupt is triggered.

The sign of the triggering acceleration is stored in bit TAP\_SIGN (0x0C<7>). If the (0x0C) HIGH\_SIGN = '0' ('1'), the sign is positive (negative). This bit holds until a new interrupt is triggered.

| The information contained herein is the exclusive property of QST, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of QST. | 17 / 34 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

Rev: C

#### 7.5 LOW-G INT

The low-g interrupt is based on the comparison of acceleration data against a low-g threshold for the detection of free-fall.

The low-g interrupt is enabled (disabled) by writing logic '1' ('0') to bits LOW\_EN (0x17<3>). There are two modes available, 'single' mode and 'sum' mode. In 'single' mode, the acceleration of each axis is compared with the threshold; in 'sum' mode, the sum of absolute value of all accelerations  $|acc_x| + |acc_y| + |acc_z|$  is compared with the threshold. The mode is selected by the contents of the LOW\_MODE bit (0x24<2>): '0' means 'single' mode, '1' means 'sum' mode.

The low-g threshold is set through the LOW\_TH (0x23<7:0>) register. 1 LSB of LOW\_TH always corresponds to an acceleration of 7.8mg (increment is independent from g-range setting).

A hysteresis can be set with the LOW\_HYST bits (0x24<1:0>). 1 LSB of LOW\_HYST always corresponds to an acceleration of 125mg (as well, increment is independent from g-range setting).

The low-g interrupt is generated if the absolute values of the acceleration of all axes ('and' relation, in case of 'single' mode) or their sum (in case of 'sum' mode) are lower than the threshold for at least the time defined by the LOW\_DUR (0x22<7:0>) register. The interrupt is reset if the absolute value of the acceleration of at least one axis ('or' relation, in case of 'single' mode) or the sum of absolute values (in case of 'sum' mode) is higher than the threshold plus the hysteresis for at least one data acquisition. The relation between the content of LOW\_DUR and the actual delay of the interrupt generation is delay = [LOW\_DUR+1]\*2ms. The interrupt status is stored in bit LOW\_INT (0x0B<3>).

## 7.6 HIGH-G\_INT

The high-g interrupt is based on the comparison of acceleration data against a high-g threshold for the detection of shock or other high-acceleration events.

The high-g interrupt is enabled (disabled) per axis by writing logic '1' ('0') to bits HIGH\_EN\_X (0x17<0>), HIGH\_EN\_Y (0x17<1>), and HIGH\_EN\_Z (0x17<2>), respectively. The high-g threshold is set through the HIGH\_TH (0x26<7:0>) register. The meaning of an LSB of HIGH\_TH depends on the selected g-range: it corresponds to 7.8mg in 2g-range (15.6mg in 4g-range, 31.2mg in 8g-range).

A hysteresis can be set with the HIGH\_HYST bits (0x24<7:6>). Analogously to the HIGH\_TH, the meaning of an LSB of HIGH\_HYST depends on the selected g-range: it corresponds to 125mg in 2g-range (250mg in 4g-range, 500mg in 8g-range).

The high-g interrupt is generated if the absolute value of the acceleration data of at least one of the enabled axes ('or' relation) is higher than the threshold for at least the time defined by the HIGH\_DUR register (0x25<7:0>). The interrupt is reset if the absolute value of the acceleration of all enabled axes ('and' relation) is lower than the threshold minus the hysteresis. The relation between the content of HIGH\_DUR and the actual delay of the interrupt generation is delay = [HIGH\_DUR+1]\*2ms.

The interrupt status is stored in bit HIGH\_INT (0x0B<2>). The axis which triggered the interrupt is indicated by bits HIGH\_FIRST\_X (0x0C<0>), HIGH\_FIRST\_Y (0x0C<1>), and HIGH\_FIRST\_Z (0x0C<2>). The bit corresponding to the triggering axis contains a '1' while the other bits hold a '0'. These bits hold until new interrupt is triggered. The sign of the triggering acceleration is stored in bit HIGH\_SIGN (0x0C<3>). If the (0x0C) HIGH\_SIGN = '0' ('1'), the sign is positive (negative). This bit holds until new interrupt is triggered.

#### 7.7 DRDY INT

The width of the acceleration data is 10 bits, in two's complement representation. The data of each axis is split into 2 parts, the MSB part (one byte contains bit 9 to bit 2) and the LSB part (one byte contains bit 1 to bit 0). Reading data should start with LSB part. When user is reading the LSB byte of data, to ensure the integrity of the acceleration data, the content of MSB can be locked, by setting SHADOW\_DIS (0x21<6>) to logic 0. This lock function can be disabled by setting SHADOW\_DIS to logic 1. Without lock, the MSB and LSB content will be updated by new value immediately. The bit NEW\_DATA in the LSB byte is the flag of the new data. If new data is updated, this NEW\_DATA flag will be 1, and will be cleared when corresponding MSB or LSB is read by user.

Rev: C

Also, the user should note that even with SHADOW\_DIS=0, the data of 3 axes are not guaranteed from the same time point. If the user need all of the 3 axes data from the same time point, please use FIFO. For detailed information, the user can refer to 6.8.

If SLEEP\_DUR is set to be 0000, then the data can be filtered by low-pass filter, with bandwidth is set by BW (0x10<4:0>). If SLEEP\_DUR is set to be other values, the data also can be averaged in different way (set by BW). In any conditions, the data stored in data registers are offset-compensated.

The device supports four different acceleration measurement ranges. The range is setting through RANGE

(0x0F<3:0>), and the details as following:

| RANGE  | Acceleration range | Resolution |

|--------|--------------------|------------|

| 0001   | 2g                 | 3.9mg/LSB  |

| 0010   | 4g                 | 7.8mg/LSB  |

| 0100   | 8g                 | 15.6mg/LSB |

| Others | 2g                 | 3.9mg/LSB  |

The interrupt for the new data serves for the synchronous data reading for the host. It is generated after storing a new value of z-axis acceleration data into data register. This interrupt will be cleared automatically when the next data conversion cycle starts, when SLEEP\_DUR is not set to 0000b. When device is in full run (SLEEP\_DUR=0000), the interrupt will be effective about 128us, and automatically cleared. The interrupt mode for the new data is fixed to be non-latched.

## 7.8 FIFO INT

The device has integrated FIFO memory, capable of storing up to 32 frames, with each frame contains three 10 bits words, for acceleration data of x, y, and z axis. All of the 3 axes' acceleration is sampled at same point in time line

The FIFO can be configured as three modes, FIFO mode, STREAM mode, and BYPASS mode. FIFO mode.

In FIFO mode, the acceleration data of selected axes are stored in the buffer memory. If enabled, a watermark interrupt can be triggered when the buffer filled up to the defined level. The buffer will continuously be filled until the fill level reaches to 32. When the buffer is full, data collection stops, and the new data will be ignored. Also, FIFO\_FULL interrupt will be triggered when enabled.

STREAM mode

In STREAM mode, the acceleration data of selected axes will be stored into the buffer until the buffer is full. The buffer's depth is 31 now. When the buffer is full, data collection continues, and the oldest data is discarded. If enabled, a watermark interrupt will be triggered when the fill level reached to the defined level. Also, when buffer is full, FIFO\_FULL interrupt will be triggered if enabled. If any old data is discarded, the FIFO\_OR (0x0E<7>) will be set to be logic 1.

BYPASS mode

In BYPASS mode, only the current acceleration data of selected axes can be read out from the FIFO. The FIFO acts like the STREAM mode with a depth of 1. Compare to reading directly from data register, this mode has the advantage of ensuring the package of xyz data are from same point of time line. The data registers are updated sequentially and have chance for the xyz data sampled in different time. Also, if any old data is discarded, the FIFO OR will be set to be logic 1, similar as that in stream mode.

The FIFO mode can be configured by setting FIFO\_MODE (0x3E<7:6>).

| FIFO_MODE | Mode   |

|-----------|--------|

| 00        | BYPASS |

| 01        | FIFO   |

| 10        | STREAM |

| 11        | FIFO   |

Rev: C

User can select the acceleration data of which axes to be stored in the FIFO. This configuration can be done by setting FIFO\_CH (0x3E<1:0>), where '00b' for x-, y-, and z-axis, '01b' for x-axis only, '10b' for y-axis only, '11b' for z-axis only.

If all the 3 axes data are selected, the format of data read from 0x3F is as follows

| XLSB  XMSB  YLSB  YMSB  ZLSB  ZMSE |        |      |       |      |        |        |

|------------------------------------|--------|------|-------|------|--------|--------|

|                                    | I XLSB | XMSB | YI SB | YMSB | / / SB | I ZMSB |

These comprise one frame

If only one axis is enabled, the format of data read from 0x3F is as follows

These comprise one frame

If the frame is not read completely, the remaining parts of the frame will be discarded.

If the FIFO is read beyond the FIFO fill level, all zeroes will be read out.

FIFO\_FRAME\_COUNTER (0x0E<6:0>) reflects the current fill level of the buffer. If additional data frames are written into the buffer when the FIFO is full (in Stream mode or Bypass mode), then, FIFO\_OR (0x0E<7>) is set to 1. This FIFO\_OR can be considered as flag of discarding old data.

When a write access to one of the FIFO configuration registers (0x3E) or (0x31) occurs, the FIFO buffer will be cleared, the FIFO fill level indication register FIFO\_FRAME\_COUNTER (0x0E<6:0>) will be cleared, and the FIFO\_OR (0x0E<7>) will be cleared.

As mentioned, FIFO controller contains two interrupts, FIFO\_FULL interrupt, and watermark interrupt. These two interrupts are functional in all the FIFO operating modes.

The watermark interrupt is triggered when the fill level of buffer reached to the level that is defined by register FIFO\_WM\_TRIGGER (0x31<5:0>), if the interrupt is enabled by setting INT\_FWM\_EN (0x17<6>) to logic 1 and INT1 FWM (0x1A<1>) or INT2 FWM (0x1A<6>) is set.

The FIFO\_FULL interrupt is triggered when the buffer has been fully filled. In FIFO mode, the fill level is 32, and in STREAM mode the fill level is 31, in BYPASS mode the fill level is 1. To enable the FIFO\_FULL interrupt, INT\_FFULL (0x17<5>) should be set to 1, and INT1\_FFULL (0x1A<2>) or INT2\_FFULL (0x1A<7>) should be set to 1.

The status of watermark interrupt and FIFO full interrupt can be read through INT\_STAT (0x0A). After soft-reset, the watermark interrupt and FIFO full interrupt are disabled.

For the FIFO to recollect the data, user should reconfigure the register FIFO MODE.

#### 7.9 Interrupt configuration

The device has the above 8 interrupt engines. Each of the interrupts can be enabled and configured independently. If the trigger condition of the enabled interrupt fulfilled, the corresponding interrupt status bit will be set to logic 1, and the mapped interrupt pin will be activated. The device has two interrupt PINs, INT1 and INT2. Each of the interrupts can be mapped to either PIN or both PINs.

The interrupt status registers update when a new data word is written into the data registers. If an interrupt is disabled, the related active interrupt status bit is disabled immediately.

Device supports 2 interrupt modes, non-latched, and latched mode. The interrupt modes are set through LATCH\_INT (0x21<0>).

In non-latched mode, the interrupt status bit and the mapped interrupt pin are cleared as soon as the associated conditions are no more valid, or read operation to the INT\_STAT (0x09~0x0b). Exceptions to this are the new data, orientation, and flat interrupts, which are automatically reset after a fixed time.

| The information contained herein is the exclusive property of QST, and shall not be distributed, |

|--------------------------------------------------------------------------------------------------|

| reproduced, or disclosed in whole or in part without prior written permission of QST.            |

Rev: C

In latched mode, the clearings of the interrupt status and selected pin are determined by INT\_RD\_CLR (0x21<7>). If INT\_RD\_CLR=0, read operation to the INT\_STAT will clear the interrupt and the selected pin. If INT\_RD\_CLR=1, any read operation to the device will clear the interrupt and the selected pin.

If the condition for trigging the interrupt still holds, the interrupt status will be set again with the next change of the data registers.

Mapping the interrupt pins can be set by INT\_MAP ( $0x19\sim0x1B$ ). The electrical interrupt pins can be set in INT\_PIN\_CONF (0x20<3:0>). The active logic level can be set to 1 or 0, and the interrupt pin can be set to open-drain or push-pull.

If the interrupt mode is configured as latched mode, the interrupt can also be cleared by I<sup>2</sup>C reading any of the interrupt status register ( $0x09 \sim 0x0c$ ).

# 8 I2C COMMUNICATION PROTOCOL

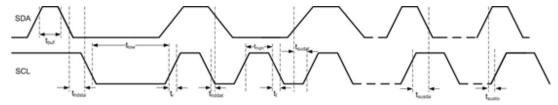

## 8.1 I<sup>2</sup>C Timings

Table 9 and Figure 12 describe the I<sup>2</sup>C communication protocol times

Table 9. I<sup>2</sup>C Timings

| Parameter                | Symbol             | Condition | Min. | Тур. | Max. | Unit |

|--------------------------|--------------------|-----------|------|------|------|------|

| SCL Clock                | f <sub>scl</sub>   |           | 0    |      | 400  | kHz  |

| SCL Low Period           | t <sub>low</sub>   |           | 1    |      |      | μs   |

| SCL High Period          | $t_{high}$         |           | 1    |      |      | μs   |

| SDA Setup Time           | t <sub>sudat</sub> |           | 0.1  |      |      | μs   |

| SDA Hold Time            | t <sub>hddat</sub> |           | 0    |      | 0.9  | μs   |

| Start Hold Time          | t <sub>hdsta</sub> |           | 0.6  |      |      | μs   |

| Start Setup Time         | t <sub>susta</sub> |           | 0.6  |      |      | μs   |

| Stop Setup Time          | t <sub>susto</sub> |           | 0.6  |      |      | μs   |

| New Transmission<br>Time | t <sub>buf</sub>   |           | 1.3  |      |      | μs   |

| Rise Time                | t <sub>r</sub>     |           |      |      |      | μs   |

| Fall Time                | t <sub>f</sub>     |           |      |      |      | μs   |

Figure 12. I<sup>2</sup>C Timing Diagram

## 8.2 I<sup>2</sup>C R/W Operation

## 8.2.1 Abbreviation

Table 10. Abbreviation

| SACK | Acknowledged by slave      |

|------|----------------------------|

| MACK | Acknowledged by master     |

| NACK | Not acknowledged by master |

| RW   | Read/Write                 |

#### 8.2.2 Start/Stop/Ack

START: Data transmission begins with a high to transition on SDA while SCL is held high. Once I<sup>2</sup>C transmission starts, the bus is considered busy.

STOP: STOP condition is a low to high transition on SDA line while SCL is held high.

ACK: Each byte of data transferred must be acknowledged. The transmitter must release the SDA line during the acknowledge pulse while the receiver mush then pull the SDA line low so that it remains stable low during the high period of the acknowledge clock cycle.

| The information contained herein is the exclusive property of QST, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of QST. | 22 / 34 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

Rev: C

NACK: If the receiver doesn't pull down the SDA line during the high period of the acknowledge clock cycle, it's recognized as NACK by the transmitter.

#### 8.2.3 I<sup>2</sup>C Write

I<sup>2</sup>C write sequence begins with start condition generated by master followed by 7 bits slave address and a write bit (R/W=0). The slave sends an acknowledge bit (ACK=0) and releases the bus. The master sends the one byte register address. The slave again acknowledges the transmission and waits for 8 bits data which shall be written to the specified register address. After the slave acknowledges the data byte, the master generates a stop signal and terminates the writing protocol.

Table 11. I<sup>2</sup>C Write

| ST  | Slave Address | R<br>W | ςA | Reg | gister<br>(0x |   | Iress |   | SΑ |     |   | Da<br>(0x | ata<br>80) | ı |   |   | S, | S   |

|-----|---------------|--------|----|-----|---------------|---|-------|---|----|-----|---|-----------|------------|---|---|---|----|-----|

| ART | 0 0 1 0 0 1 0 | 0      | ζ. | 0 0 | 0 1           | 0 | 0 0   | 1 | Š  | 1 ( | 0 | 0         | 0          | 0 | 0 | 0 | CK | ГОР |

#### 8.2.4 I<sup>2</sup>C Read

$I^2C$  write sequence consists of a one-byte  $I^2C$  write phase followed by the  $I^2C$  read phase. A start condition must be generated between two phase. The  $I^2C$  write phase addresses the slave and sends the register address to be read. After slave acknowledges the transmission, the master generates again a start condition and sends the slave address together with a read bit (R/W=1). Then master releases the bus and waits for the data bytes to be read out from slave. After each data byte the master has to generate an acknowledge bit (ACK = 0) to enable further data transfer. A NACK from the master stops the data being transferred from the slave. The slave releases the bus so that the master can generate a STOP condition and terminate the transmission.

The register address is automatically incremented and more than one byte can be sequentially read out. Once a new data read transmission starts, the start address will be set to the register address specified in the current I<sup>2</sup>C write command.

Table 12. I<sup>2</sup>C Read

| ST   |   | SI | ave | e A | ddre         | ess |   | R<br>W | S/   |   | Re | egis |   | Ad<br>(00)  |   | SS |     | s,   |   |   |   |           |            |   |   |   |      |      |

|------|---|----|-----|-----|--------------|-----|---|--------|------|---|----|------|---|-------------|---|----|-----|------|---|---|---|-----------|------------|---|---|---|------|------|

| TART | 0 | 0  | 1   | 0   | 0            | 1   | 0 | 0      | SACK | 0 | 0  | 0    | 0 | 0           | 0 | 0  | 0   | SACK |   |   |   |           |            |   |   |   |      |      |

| ST   |   | SI | ave | e A | ddre         | ess | ı | R<br>W | S,   |   |    |      |   | ata<br>(00) |   |    |     | M    |   |   |   | Da<br>(0x | ata<br>01) |   |   |   |      |      |

| TART | 0 | 0  | 1   | 0   | 0            | 1   | 0 | 1      | SACK | 0 | 0  | 0    | 0 | 0           | 0 | 1  | 0   | MACK | 0 | 0 | 0 | 0         | 0          | 0 | 0 | 0 |      |      |

| ×.   |   |    | ı   |     | Data<br>0x02 |     |   |        | ×    |   |    |      |   |             |   |    | ••• | M    |   |   |   | Da<br>(0x |            |   |   |   | Z,   | S    |

| MACK | 0 | 0  | 0   | 0   | 0            | 0   | 1 | 0      | MACK |   |    |      |   |             |   |    |     | MACK | 0 | 0 | 0 | 0         | 0          | 0 | 0 | 0 | NACK | STOP |

#### **9 REGISTERS**

#### 9.1 Register Map

The table below provides a list of the 8-bit registers embedded in the device and their respective function and addresses

| The information contained herein is the exclusive property of QST, and shall not be distributed, reproduced, or disclosed in whole or in part without prior written permission of QST. | 23 / 34 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

Rev: C

## Table 13. Register Map

| 0x3F           |                 | FIFO DATA<7:             | ۸۱            |                                               |               |                    |                 |                 |              | D       | 00        |

|----------------|-----------------|--------------------------|---------------|-----------------------------------------------|---------------|--------------------|-----------------|-----------------|--------------|---------|-----------|

|                |                 | FIFO MODE<1:             |               |                                               |               |                    | ı               | FIFO CH<1:0>    | •            | RW      | 00        |

|                |                 |                          | U/            | L                                             | L             |                    | l .             | F1FU_CH(1:U/    |              | •       |           |

| 0x3D           |                 | GAIN_Z<7:0>              |               |                                               |               |                    |                 |                 | •            | RW      | NVM       |

| 0x3C           |                 | GAIN_Y<7:0>              |               |                                               |               |                    |                 |                 |              | RW      | NVM       |

| 0x3B           |                 | GAIN_X<7:0>              |               |                                               |               |                    |                 |                 |              | RW      | NVM       |

| 0x3A           |                 | OFFSET_Z<7:0             |               |                                               |               |                    |                 |                 |              | RW      | NVM       |

| 0x39           |                 | OFFSET_Y<7:0             | >             |                                               |               |                    |                 |                 |              | RW      | NVM       |

| 0x38           |                 | OFFSET_X<7:0             | >             |                                               |               |                    |                 |                 |              | RW      | NVM       |

| 0x37           | IMAGE           | OFFSET_X<10:             | 8>            |                                               | GAI           | N_Z<9:8>           | 0               | FFSET_Y<10:8>   |              | RW      | NVM       |

| 0x36           | SOFT RESET      | SOFTRESET: 0:            | xB6           |                                               |               |                    |                 |                 |              | RW      | 00        |

| 0x35           |                 |                          |               |                                               |               |                    |                 |                 |              | RW      | 00        |

| 0x34           |                 |                          |               |                                               |               |                    |                 |                 |              | RW      | 00        |

|                | NVM CFG         |                          |               |                                               |               | NVM LOAD           | NVM RDY         | NVM PROG        |              | RW      | 04        |

| 0x32           |                 | SELFTEST BIT             |               |                                               |               | SingleEn_Step      | SELFTEST SIGN   |                 | <1·0>        | RW      | 00        |

|                | FIFO WM         | ODDITEOT_DIT             |               | FIFO WTMK LVL<5:                              | .0>           | DINGIODN_DUOP      | TODDI TODI_DIGN | DDD1 1DD1_HX10  | (110)        | RW      | 00        |

| 0x30           |                 | ORIENT_DB_DI             |               | <u>                                      </u> | . 07          | FB_Z_TH<6:0>       |                 |                 |              | RW      | 00        |

| 0x2F           |                 | OKIENI_DD_DI             |               |                                               | DI V          | TH<7:0>            |                 |                 |              | RW      | A 4       |

| 0x2F<br>0x2E   |                 |                          |               |                                               |               | TH<7:0>            |                 |                 |              | RW      | 00        |

| 0x2D           |                 |                          |               |                                               |               |                    |                 |                 |              | RW      | 00<br>A 4 |

|                | AD /CD          |                          |               |                                               |               | TH(7:0)            |                 |                 |              |         | 00        |

|                | 4D/6D           |                          |               |                                               |               | _TH<7:0>           |                 |                 |              | RW      | 00<br>0A  |

| 0x2B           | TAD             | TAD OUTDO                | TAD CHACE     | Ι                                             | TAP_TH<4:0>   |                    | TAD DUD (O. O.) |                 |              | RW      | 0A<br>04  |

| 0x2A           | TAP             | TAP_QUIET                | TAP_SHOCK     | L                                             | 00.00         | CT 7/7.0\          | TAP_DUR<2:0>    |                 |              | RW      |           |

| 0x29           |                 |                          |               |                                               |               | ST_Z<7:0>          |                 |                 |              | RW      | 00        |

| 0x28           | 00 01107        |                          |               |                                               |               | ST_Y<7:0>          |                 |                 |              | RW      | 00        |

|                | OS_CUST         |                          |               |                                               | US_CU         | ST_X<7:0>          |                 |                 |              | RW      | 00        |

| 0x26           |                 | HIGH_TH<7:0>             |               |                                               |               |                    |                 |                 |              | RW      | C0        |

| 0x25           |                 | HIGH_DUR<7:0             |               |                                               |               | ı                  | 1               | 1               |              | RW      | 0F        |

| 0x24           |                 | HIGH_HYST<1:             | 0>            |                                               |               |                    | LOW_MODE        | LOW HYST<1:0>   |              | RW      | 81        |

| 0x23           |                 | LOW_TH<7:0>              |               |                                               |               |                    |                 |                 |              | RW      | 30        |

| 0x22           |                 | LOW_DUR<7:0>             |               |                                               |               |                    |                 |                 |              | RW      | 09        |

| 0x21           | INT LATCH       | INT_RD_CLR               | SHADOW DIS    | INT_PULSE                                     |               |                    |                 |                 | LATCH INT    | RW      | 00        |

| 0x20           | INT PIN CONF    |                          |               |                                               |               | INT2_OD            | INT2_LVL        | INT1_OD         | INT1_LVL     | RW      | 05        |

| 0x1F           |                 |                          |               | PEAI                                          | K_B<5:0>      |                    |                 | STEP_MISMATCH   | _B<1:0>      | RW      | 00        |

| 0x1E           |                 |                          |               | VALLI                                         | EY_B<5:0>     |                    |                 |                 |              | RW      | 00        |

| 0x1D           |                 |                          |               |                                               |               |                    |                 |                 |              | RW      | FF        |

| 0x1C           |                 |                          | INT2_FWM      | INT2_FFULL                                    | INT2_DATA     | INT2_LOW           | INT2_HIGH       |                 |              | RW      | 00        |

| 0x1B           |                 | INT2 FOB                 | INT2 ORIENT   | INT2 S TAP                                    | INT2 D TAP    | INT2 STEP          | INT2 STEP QUIT  | INT2 STEP UNS   | IMIL         | RW      | 00        |

| 0x1A           |                 |                          | INT1 FWM      | INT1 FFULL                                    | INT1 DATA     | INT1 LOW           | INT1 HIGH       |                 |              | RW      | 00        |

| 0x19           | INT MAP         | INT1 FOB                 | INT1_ORIENT   | INT1_S_TAP                                    | INT1_D_TAP    | INT1 STEP          | INT1_STEP_QUIT  | INT1 STEP UNS   | IMIL         | RW      | 00        |

| 0x18           | INT SRC         |                          | INT SRC STEP  | INT SRC DATA                                  | INT SRC TAP   | _                  |                 |                 |              | RW      | 00        |

| 0x17           |                 |                          | INT_FWM_EN    | INT_FFULL_EN                                  | DATA EN       | LOW EN             | HIGH EN Z       | HIGH EN Y       | HIGH_EN_X    | RW      | 00        |

| 0x16           | INT EN          | FOB EN                   | ORIENT EN     | S TAP EN                                      | D TAP EN      | STEP EN            |                 | STEP UNSIMILA   |              | RW      | 00        |

| 0x15           |                 |                          |               |                                               |               | IME UP<7:0>        |                 |                 | _            | RW      | 00        |

| 0x14           |                 |                          |               |                                               |               | ME LOW<7:0>        |                 |                 |              | RW      | 00        |

|                | STEP CONF       | STEP CLR                 |               |                                               |               | TEP PRECISION<6:0> |                 |                 |              | RW      | 00        |

| 0x12           |                 | STEP_START               |               |                                               | STEP SAMPLE C |                    |                 |                 |              | RW      | 0C        |

|                |                 |                          | RESV          | PRESET                                        |               | SLEEP_DUR<3:0>     |                 |                 | ,            | RW      | 00        |

|                | BW              |                          |               | ODRH                                          |               |                    | BW<4:0>         |                 | ,            | RW      | 00        |

| 0x0F           | FULL SCALE      |                          |               | 1                                             | 1             | RANGE<3:0>         | 3/              |                 | ,            | RW      | 00        |

|                |                 | FIFO OR                  | FIFO FRAME CO | DUNTER<6:0>                                   | •             | ,                  |                 |                 |              | R       | 00        |

| 0x0D           |                 | STEP CNT OVE             |               |                                               | R             | 0B<1:0>            |                 | ORIENT<2:0>     |              | R       | 00        |

| 0x0C           |                 | TAP SIGN                 | TAP FIRST Z   | TAP FIRST Y                                   |               | HIGH SIGN          | HIGH FIRST Z    | HIGH FIRST Y    | HICH FIRST Y | R       | 00        |

| 0x0B           |                 | 01011                    | FIFO WM INT   | FIFO_FULL_INT                                 | DATA INT      | LOW INT            | HIGH INT        |                 |              | R       | 00        |

|                | INT STATUS      | FOB INT                  | ORIENT_INT    | S TAP INT                                     | D TAP INT     | STEP INT           | STEP QUIT INT   | STED HINGINII A | R            | R       | 00        |

| 0x0A = 0x0A    | INI SINIUS      | 1 01 1111                | OWIDMI_IMI    | D_IMI_IMI                                     | ואו_ואו       | 01D1 THI           | PIDI MOII THI   | OIDI ONOIMIDU   |              | R       | FF        |

| 0x09           |                 |                          | 1             | <u> </u>                                      | CTPD          | CNT<15:8>          | 1               | <u> </u>        | l .          | R       | 00        |

|                | STEP CNT        |                          |               |                                               |               | CNT<7:0>           |                 |                 |              | R       | 00        |

| 0x07<br>0x06   |                 | ACC 7/0.2\               |               |                                               | SIEF          | _UN1 / 1: U/       |                 |                 |              | D IV    | 00        |

| 0x06<br>0x05   |                 | ACC_Z<9:2>               |               |                                               |               | ı                  | 1               |                 | NEW DATA Z   | I/      | 00        |

|                |                 | ACC Z<1:0>               |               | I .                                           | L             | l .                | l               | l .             | INEW DAIA Z  | IV.     | 00        |

| $0x04 \\ 0x03$ |                 | ACC_Y<9:2>               |               | 1                                             | 1             | 1                  | 1               | 1               | NEW DATE V   | N N     |           |

| 1112/112       |                 | ACC_Y<1:0><br>ACC_X<9:2> |               | <u> </u>                                      | <u> </u>      |                    | <u> </u>        |                 | NEW_DATA_Y   | R       | 00        |

|                |                 | IAI'I' YZQ+95            |               |                                               |               |                    |                 |                 |              | K       | 00        |

| 0x02           | DATA            |                          |               |                                               |               |                    |                 |                 | NEW DAMA V   | D       |           |

| 0x02<br>0x01   | DATA<br>CHIP ID | ACC_X<1:0>               |               | 0777                                          | TD 4          | te the product ver |                 |                 | NEW_DATA_X   | R<br>RW | 00<br>BX  |

Rev: C

## 9.2 Register Definition

Register 0x00 (CHIP ID)