# 1EDI EiceDRIVER™ Compact

# 1EDI20N12AF

Single Channel MOSFET and GaN HEMT Gate Driver IC

1EDI20N12AF

# **Data Sheet**

Rev. 2.0, 2015-06-01

# Industrial Power Control

#### Edition 2015-06-01

Published by Infineon Technologies AG 81726 Munich, Germany © 2015 Infineon Technologies AG All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

| <b>Revision Histo</b> | ory                                              |  |

|-----------------------|--------------------------------------------------|--|

| Page or Item          | Subjects (major changes since previous revision) |  |

| Rev. 2.0, 2015        | -06-01                                           |  |

| p17                   | dynamic parameter update                         |  |

| Rev. 1.03, 201        | 4-10-14                                          |  |

| all pages             | parameter completion                             |  |

| Rev. 1.02, 201        | 4-02-14                                          |  |

| p 8                   | application diagram                              |  |

|                       |                                                  |  |

|                       |                                                  |  |

#### Trademarks of Infineon Technologies AG

AURIXTM, BlueMoonTM, C166TM, CanPAKTM, CIPOSTM, CIPURSETM, COMNEONTM, EconoPACKTM, CoolMOSTM, CoolSETTM, CORECONTROLTM, CROSSAVETM, DAVETM, EasyPIMTM, EconoBRIDGETM, EconoDUALTM, EconoPIMTM, EiceDRIVERTM, eupecTM, FCOSTM, HITFETTM, HybridPACKTM, I2RFTM, ISOFACETM, IsoPACKTM, MIPAQTM, ModSTACKTM, my-dTM, NovalithICTM, OmniTuneTM, OptiMOSTM, ORIGATM, PRIMARIONTM, PrimePACKTM, PrimeSTACKTM, PRO-SILTM, PROFETTM, RASICTM, ReverSaveTM, SatRICTM, SIEGETTM, SINDRIONTM, SIPMOSTM, SMARTITM, SmartLEWISTM, SOLID FLASHTM, TEMPFETTM, thinQ!TM, TRENCHSTOPTM, TriCoreTM, X-GOLDTM, X-PMUTM, XMMTM, XPOSYSTM.

#### Other Trademarks

Advance Design System™ (ADS) of Agilent Technologies, AMBA™, ARM™, MULTI-ICE™, KEIL™, PRIMECELL™, REALVIEW™, THUMB™, µVision™ of ARM Limited, UK. AUTOSAR™ is licensed by AUTOSAR development partnership. Bluetooth™ of Bluetooth SIG Inc. CAT-iq™ of DECT Forum. COLOSSUS™, FirstGPS™ of Trimble Navigation Ltd. EMV™ of EMVCo, LLC (Visa Holdings Inc.). EPCOS™ of Epcos AG. FLEXGO™ of Microsoft Corporation. FlexRay™ is licensed by FlexRay Consortium. HYPERTERMINAL™ of Hilgraeve Incorporated. IEC™ of Commission Electrotechnique Internationale. IrDA™ of Infrared Data Association Corporation. ISO™ of INTERNATIONAL ORGANIZATION FOR STANDARDIZATION. MATLAB™ of MathWorks, Inc. MAXIM™ of Maxim Integrated Products, Inc. MICROTEC™, NUCLEUS™ of Mentor Graphics Corporation. Mifare™ of NXP. MIPI™ of MIPI Alliance, Inc. MIPS™ of MIPS Technologies, Inc., USA. muRata™ of MURATA MANUFACTURING CO., MICROWAVE OFFICE™ (MWO) of Applied Wave Research Inc., OmniVision™ of OmniVision Technologies, Inc. Openwave™ Openwave Systems Inc. RED HAT™ Red Hat, Inc. RFMD™ RF Micro Devices, Inc. SIRIUS™ of Sirius Satellite Radio Inc. SOLARIS™ of Sun Microsystems, Inc. SPANSION™ of Spansion LLC Ltd. Symbian™ of Symbian Software Limited. TAIYO YUDEN™ of Taiyo Yuden Co. TEAKLITE™ of CEVA, Inc. TEKTRONIX™ of Tektronix Inc. TOKO™ of TOKO KABUSHIKI KAISHA TA. UNIX™ of X/Open Company Limited. VERILOG™, PALLADIUM™ of Cadence Design Systems, Inc. VLYNQ™ of Texas Instruments Incorporated. VXWORKS™, WIND RIVER™ of WIND RIVER SYSTEMS, INC. ZETEX™ of Diodes Zetex Limited.

Last Trademarks Update 2010-10-26

Data Sheet 3 Rev. 2.0, 2015-06-01

# **Table of Contents**

|                                                                         | Table of Contents                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                         | List of Figures                                                                                                                                                                                                                                                                                                                                                         |

|                                                                         | List of Tables                                                                                                                                                                                                                                                                                                                                                          |

| I                                                                       | Overview                                                                                                                                                                                                                                                                                                                                                                |

| 2                                                                       | Block Diagram                                                                                                                                                                                                                                                                                                                                                           |

| 3.1<br>3.2                                                              | Pin Configuration and Functionality       10         Pin Configuration       10         Pin Functionality       10                                                                                                                                                                                                                                                      |

| 14.1<br>14.2<br>14.3<br>14.3.1<br>14.3.2<br>14.3.3<br>14.4<br>14.5      | Functional Description         12           Introduction         12           Supply         12           Protection Features         13           Undervoltage Lockout (UVLO)         13           Active Shut-Down         13           Short Circuit Clamping         13           Non-Inverting and Inverting Inputs         13           Driver Outputs         13 |

| 5.1<br>5.2<br>5.3<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4<br>5.3.5<br>5.3.6 | Electrical Parameters       14         Absolute Maximum Ratings       14         Operating Parameters       15         Electrical Characteristics       15         Voltage Supply       15         Logic Input       16         Gate Driver       16         Short Circuit Clamping       17         Dynamic Characteristics       17         Active Shut Down       18 |

| 6                                                                       | Timing Diagramms                                                                                                                                                                                                                                                                                                                                                        |

| 7                                                                       | Package Outlines                                                                                                                                                                                                                                                                                                                                                        |

| <b>3</b><br>3.1<br>3.2                                                  | Application Notes       2°         Reference Layout for Thermal Data       2°         Printed Circuit Board Guidelines       2°                                                                                                                                                                                                                                         |

# **List of Figures**

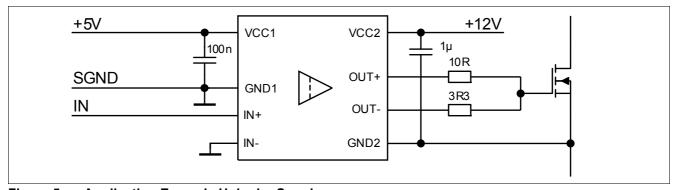

| igure 1  | Typical Application                                        | . 8 |

|----------|------------------------------------------------------------|-----|

| igure 2  | Block Diagram 1EDI20N12AF                                  | . 9 |

| igure 3  | PG-DSO-8-51 (top view)                                     | 10  |

| igure 4  | Application Example Bipolar Supply                         | 12  |

| igure 5  | Application Example Unipolar Supply                        | 12  |

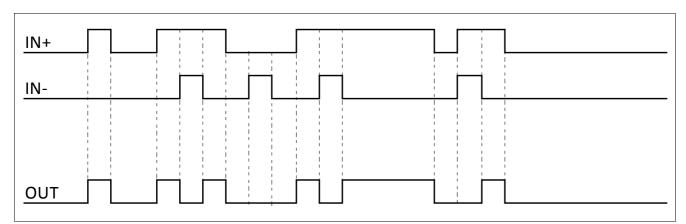

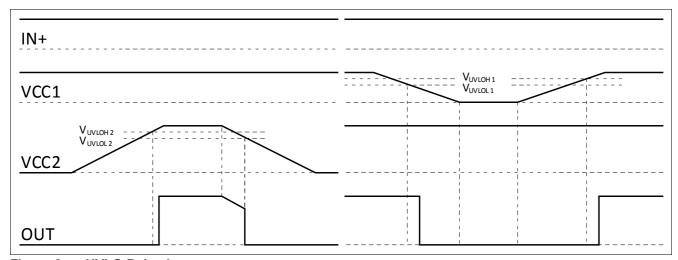

| igure 6  | Propagation Delay, Rise and Fall Time                      | 19  |

| igure 7  | Typical Switching Behavior                                 | 19  |

| igure 8  | UVLO Behavior                                              | 19  |

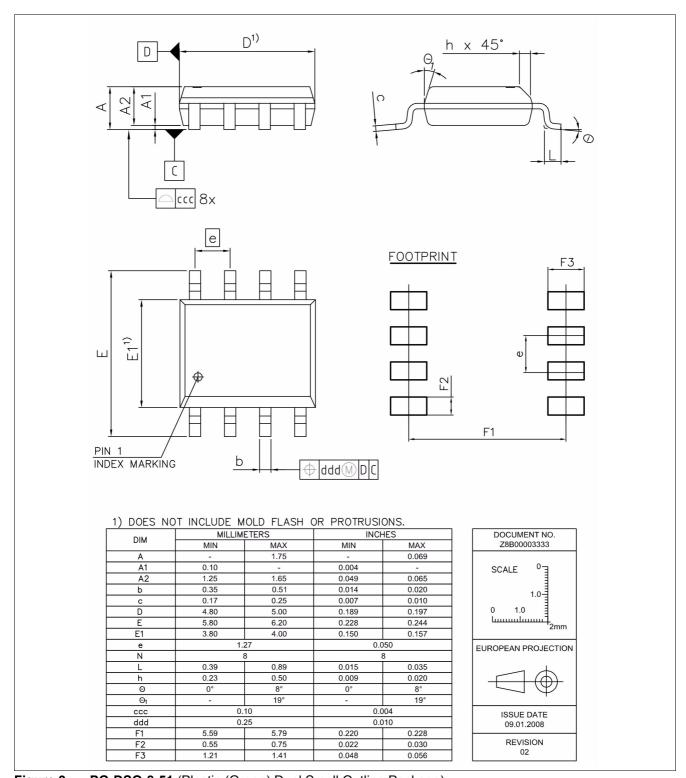

| igure 9  | PG-DSO-8-51 (Plastic (Green) Dual Small Outline Package)   | 20  |

| igure 10 | Reference Layout for Thermal Data (Copper thickness 35 µm) | 21  |

|          |                                                            |     |

Data Sheet 5 Rev. 2.0, 2015-06-01

# **List of Tables**

| Table 1 | Pin Configuration        |

|---------|--------------------------|

| Table 2 | Absolute Maximum Ratings |

| Table 3 | Operating Parameters     |

| Table 4 | Voltage Supply           |

| Table 5 | Logic Input              |

| Table 6 | Gate Driver              |

| Table 7 | Short Circuit Clamping   |

| Table 8 | Dynamic Characteristics  |

| Table 9 | Active Shut Down         |

Data Sheet 6 Rev. 2.0, 2015-06-01

# 1EDI EiceDRIVER™ Compact Single Channel MOSFET and GaN HEMT Gate Driver IC

#### 1EDI20N12AF

#### 1 Overview

#### **Main Features**

- Single channel isolated Gate Driver

- Input to output isolation voltage up to 1200 V

- For high voltage power FETs

- 4 A typical peak current at rail-to-rail outputs

- Separate source and sink outputs

#### **Product Highlights**

- Galvanically isolated Coreless Transformer Driver

- Low input to output capacitive coupling

- Suitable for operation at high ambient temperature

- · Wide input voltage operating range

- ideally suited for driving cascoded or normally-off Gallium Nitride HEMTs

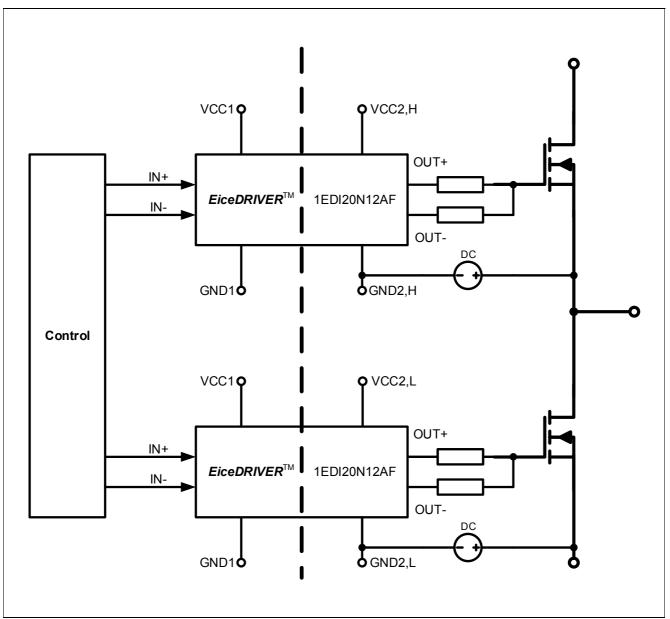

#### **Typical Application**

- · AC and Brushless DC Motor Drives

- High Voltage PFC, DC/DC-Converter and DC/AC-Inverter

- Induction Heating Resonant Application

- UPS-Systems

- Welding

- · Solar MPPT boost converter

#### **Description**

The 1EDI20N12AF is a galvanically isolated single channel FET driver in a PG-DSO-8-51 package that provides output currents of at least 2 A at separated output pins.

The input logic pins operate on a wide input voltage range from 3 V to 15 V using CMOS threshold levels to support even 3.3 V microcontroller.

Data transfer across the isolation barrier is realized by the Coreless Transformer Technology.

The undervoltage lockout (UVLO) functions for both input and output chip and an active shutdown feature are included to always guarantee safe operation.

| Product Name | Gate Drive Current (min)      | Package     |  |  |

|--------------|-------------------------------|-------------|--|--|

| 1EDI20N12AF  | ±2.0 A MOSFET level optimized | PG-DSO-8-51 |  |  |

Overview

Figure 1 Typical Application

Data Sheet 8 Rev. 2.0, 2015-06-01

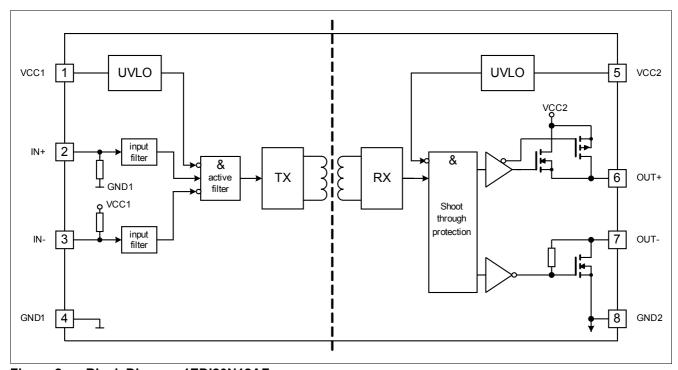

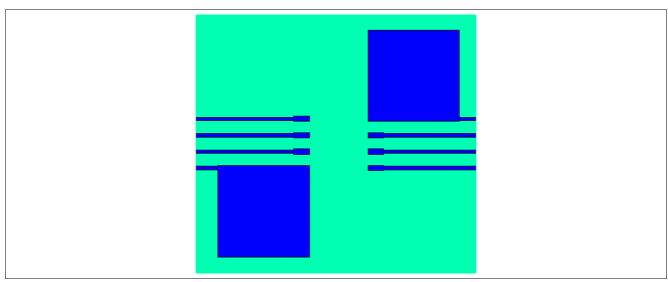

**Block Diagram**

# 2 Block Diagram

Figure 2 Block Diagram 1EDI20N12AF

Data Sheet 9 Rev. 2.0, 2015-06-01

Pin Configuration and Functionality

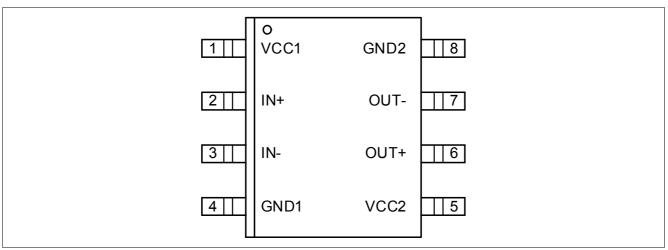

# 3 Pin Configuration and Functionality

### 3.1 Pin Configuration

Table 1 Pin Configuration

| Pin No. | Name | Function                                 |

|---------|------|------------------------------------------|

| 1       | VCC1 | Positive Logic Supply                    |

| 2       | IN+  | Non-Inverting Driver Input (active high) |

| 3       | IN-  | Inverting Driver Input (active low)      |

| 4       | GND1 | Logic Ground                             |

| 5       | VCC2 | Positive Power Supply Output Side        |

| 6       | OUT+ | Driver Source Output                     |

| 7       | OUT- | Driver Sink Output                       |

| 8       | GND2 | Power Ground                             |

Figure 3 PG-DSO-8-51 (top view)

### 3.2 Pin Functionality

#### VCC1

Logic input supply voltage with wide operating range (3.3 V o 15 V).

#### **IN+ Non Inverting Driver Input**

IN+ non-inverted control signal for driver output if IN- is set to low. (Output sourcing active at IN+ = high and IN- = low)

Due to internal filtering a minimum pulse width is defined to ensure robustness against noise at IN+. An internal pull-down-resistor favors off-state.

Data Sheet 10 Rev. 2.0, 2015-06-01

### 1EDI EiceDRIVER™ Compact 1EDI20N12AF

#### Pin Configuration and Functionality

#### **IN- Inverting Driver Input**

IN- inverted control signal for driver output if IN+ is set to high. (Output sourcing active at IN- = low and IN+ = high) Due to internal filtering a minimum pulse width is defined to ensure robustness against noise at IN-. An internal pull-up-resistor favors off-state.

#### **GND1**

Ground connection of input circuit.

#### VCC2

Positive power supply pin of output driving circuit. A proper blocking capacitor has to be placed close to this supply pin.

#### **OUT+ Driver Source Output**

Driver output pin sourcing current to turn on external switch transistor. During on-state the driving output is switched to VCC2. Switching of this output is controlled by IN+ and IN-, resp.. This output will also be turned off at an UVLO event.

During turn off the OUT+ terminal is able to sink approx. 100 mA.

#### **OUT- Driver Sink Output)**

Driver output pin sinking current to turn off external switch transistor. During off-state the driving output is switched to GND2. Switching of this output is controlled by IN+ and IN-, resp.. In case of UVLO an active shut down keeps the output low.

#### **GND2 Reference Ground**

Reference ground of the output driving circuit.

In case of a bipolar supply (positive and negative voltage with respect to switch source potential) this pin is connected to the negative supply voltage.

Data Sheet 11 Rev. 2.0, 2015-06-01

**Functional Description**

# 4 Functional Description

#### 4.1 Introduction

The 1EDI EiceDRIVER™ Compact is a general purpose gate driver. Basic control and protection features support fast and easy design of highly reliable systems.

The galvanic isolation between input logic and driver output is achieved by utilizing on-chip Coreless Transformer Technology. The wide input range supports the direct connection of various signal sources like DSPs and microcontrollers.

The separated rail-to-rail driver outputs simplify gate resistor selection, save an external high current bypass diode and improve dV/dt control.

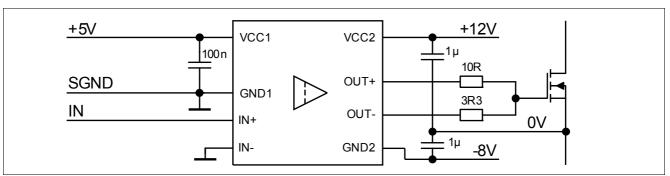

Figure 4 Application Example Bipolar Supply

#### 4.2 Supply

The driver can operate over a wide supply voltage range, either unipolar or bipolar.

With bipolar supply the driver is typically operated with a positive voltage of 12 V at VCC2 and a negative voltage of -8V at GND2 relative to the source potential as seen in **Figure 4**. Negative supply can help to prevent a dynamic turn on.

For unipolar supply configuration the driver is typically supplied with a positive voltage of 12 V at VCC2. In this case, careful evaluation for turn off gate resistor selection is recommended to avoid dynamic turn on (see Figure 5).

Figure 5 Application Example Unipolar Supply

Data Sheet 12 Rev. 2.0, 2015-06-01

### 1EDI EiceDRIVER™ Compact 1EDI20N12AF

**Functional Description**

#### 4.3 Protection Features

#### 4.3.1 Undervoltage Lockout (UVLO)

To ensure correct switching the device is equipped with an undervoltage lockout for input and output independently. Operation starts only after both VCC levels have increased beyond the respective V<sub>UVLOH</sub> levels (see also **Figure 8**).

If the power supply voltage  $V_{VCC1}$  of the input chip drops below  $V_{UVLOL1}$  a turn-off signal is sent to the output chip before power-down. The switch is turned off and the signals at IN+ and IN- are ignored until  $V_{VCC1}$  reaches the power-up voltage  $V_{UVLOH1}$  again.

If the power supply voltage  $V_{VCC2}$  of the output chip goes down below  $V_{UVLOL2}$  the switch is again turned off and signals from the input chip are ignored until  $V_{VCC2}$  reaches the power-up voltage  $V_{UVLOH2}$  again.

Note: V<sub>VCC2</sub> is always referred to GND2; the output UVLO function thus depends on the total supply voltage.

#### 4.3.2 Active Shut-Down

The Active Shut-Down feature ensures a safe off-state if the output chip is not connected to the power supply, The gate is clamped at OUT- to GND2.

#### 4.3.3 Short Circuit Clamping

During short circuit the gate voltage tends to rise because of the feedback via the Miller capacitance. An additional protection circuit connected to OUT+ limits this voltage to a value slightly higher than the supply voltage. A maximum current of 500 mA may be fed back to the supply through this path for 10  $\mu$ s. If higher currents are expected or tighter clamping is desired external Schottky diodes may be added.

#### 4.4 Non-Inverting and Inverting Inputs

There are two possible input modes to control the switch. In the non-inverting mode IN+ controls the driver output while IN- is set to low. In the inverting mode IN- controls the driver output while IN+ is set to high, see **Figure 7**. A minimum input pulse width is required to filter occasional glitches.

#### 4.5 Driver Outputs

The output driver section uses MOSFETs to provide a rail-to-rail output. This feature permits that tight control of gate voltage during on-state and short circuit can be maintained as long as the driver's supply is stable. Due to the low internal voltage drop, switching behaviour is predominantly governed by the gate resistor. Furthermore, it reduces the power to be dissipated in the driver.

Data Sheet 13 Rev. 2.0, 2015-06-01

**Electrical Parameters**

# 5 Electrical Parameters

### 5.1 Absolute Maximum Ratings

Note: Absolute maximum ratings are defined as absolute limits, i.e. exceeding them may lead to destruction of the integrated circuit.

Table 2 Absolute Maximum Ratings

| Parameter                         | Symbol                 | Va              | lues                   | Unit | Note /                               |  |

|-----------------------------------|------------------------|-----------------|------------------------|------|--------------------------------------|--|

|                                   |                        | Min.            | Max.                   |      | Test Condition                       |  |

| Power supply output side          | $V_{\sf VCC2}$         | -0.3            | 40                     | V    | 1)                                   |  |

| Gate driver output                | $V_{OUT}$              | $V_{GND2}$ -0.3 | V <sub>VCC2</sub> +0.3 | V    | _                                    |  |

| Positive power supply input side  | $V_{\sf VCC1}$         | -0.3            | 18.0                   | V    | _                                    |  |

| Logic input voltages (IN+,IN-)    | $V_{LogicIN}$          | -0.3            | 18.0                   | V    | _                                    |  |

| Input to output isolation voltage | $V_{ISO}$              | -1200           | 1200                   | V    |                                      |  |

| Junction temperature              | $T_{J}$                | -40             | 150                    | °C   | _                                    |  |

| Storage temperature               | $T_{S}$                | -55             | 150                    | °C   | _                                    |  |

| Power dissipation (Input side)    | $P_{D,IN}$             | _               | 25                     | mW   | $^{2)}$ @ $T_{A}$ = 25°C             |  |

| Power dissipation (Output side)   | $P_{D,OUT}$            | _               | 400                    | mW   | $^{2)}$ @ $T_{A}$ = 25°C             |  |

| Thermal resistance (Input side)   | $R_{THJA,IN}$          | _               | 145                    | K/W  | <sup>2)</sup> @T <sub>A</sub> = 85°C |  |

| Thermal resistance (Output side)  | $R_{THJA,OUT}$         | _               | 165                    | K/W  | <sup>2)</sup> @T <sub>A</sub> = 85°C |  |

| ESD capability                    | $V_{\mathrm{ESD,HBM}}$ | _               | 2                      | kV   | Human Body<br>Model <sup>3)</sup>    |  |

<sup>1)</sup> With respect to GND2.

Data Sheet 14 Rev. 2.0, 2015-06-01

<sup>2)</sup> See **Figure 10** for reference layouts for these thermal data. Thermal performance may change significantly with layout and heat dissipation of components in close proximity.

<sup>3)</sup> According to EIA/JESD22-A114-C (discharging a 100 pF capacitor through a 1.5 k $\Omega$  series resistor).

**Electrical Parameters**

### 5.2 Operating Parameters

Note: Within the operating range the IC operates as described in the functional description. Unless otherwise noted all parameters refer to GND1.

**Table 3** Operating Parameters

| Parameter                             | Symbol                                     |      | Values |       | Note /                               |

|---------------------------------------|--------------------------------------------|------|--------|-------|--------------------------------------|

|                                       |                                            | Min. | Max.   |       | Test Condition                       |

| Power supply output side              | $V_{\sf VCC2}$                             | 10   | 35     | V     | 1)                                   |

| Power supply input side               | $V_{\text{VCC1}}$                          | 3.1  | 17     | V     | _                                    |

| Logic input voltages (IN+,IN-)        | $V_{LogicIN}$                              | -0.3 | 17     | V     | _                                    |

| Switching frequency                   | $f_{\sf sw}$                               | _    | 4.0    | MHz   | 2) 3)                                |

| Ambient temperature                   | $T_{A}$                                    | -40  | 125    | °C    | _                                    |

| Thermal coefficient, junction-top     | $\Psi_{th,jt}$                             | _    | 4.8    | K/W   | <sup>3)</sup> @T <sub>A</sub> = 85°C |

| Common mode transient immunity (CMTI) | $ \mathrm{d}V_{\mathrm{ISO}}/\mathrm{dt} $ | -    | 100    | kV/μs | <sup>3)</sup> @ 1000 V               |

<sup>1)</sup> With respect to GND2.

#### 5.3 Electrical Characteristics

Note: The electrical characteristics include the spread of values in supply voltages, load and junction temperatures given below. Typical values represent the median values at  $T_A$  = 25°C. Unless otherwise noted all voltages are given with respect to their respective GND (GND1 for pins 1 to 3, GND2 for pins 5 to 7).

## 5.3.1 Voltage Supply

Table 4 Voltage Supply

| Parameter             | Symbol            | Values |      |      | Unit | Note /                |

|-----------------------|-------------------|--------|------|------|------|-----------------------|

|                       |                   | Min.   | Тур. | Max. |      | <b>Test Condition</b> |

| UVLO threshold input  | $V_{\rm UVLOH1}$  | _      | 2.85 | 3.1  | V    | _                     |

| chip                  | $V_{UVLOL1}$      | 2.55   | 2.75 | _    | V    | _                     |

|                       | V <sub>HYS1</sub> | 90     | 100  | -    | mV   | _                     |

| UVLO threshold output | $V_{\sf UVLOH2}$  | _      | 9.1  | 10.0 | V    | _                     |

| chip (MOSFET Supply)  | $V_{\sf UVLOL2}$  | 8.0    | 8.5  | _    | V    | _                     |

|                       | $V_{HYS2}$        | 550    | 600  | -    | mV   | _                     |

Data Sheet 15 Rev. 2.0, 2015-06-01

<sup>2)</sup> do not exceed max. power dissipation

<sup>3)</sup> Parameter is not subject to production test - verified by design/characterization

## 1EDI EiceDRIVER™ Compact 1EDI20N12AF

**Electrical Parameters**

Table 4 Voltage Supply (cont'd)

| Parameter                     | Symbol            |      | Values |      |    | Note /                                                              |

|-------------------------------|-------------------|------|--------|------|----|---------------------------------------------------------------------|

|                               |                   | Min. | Тур.   | Max. |    | Test Condition                                                      |

| Quiescent current input chip  | $I_{\mathrm{Q1}}$ | -    | 0.65   | 1.0  | mA | $V_{\text{VCC1}}$ = 5 V<br>IN+ = High,<br>IN- = Low<br>=>OUT = High |

| Quiescent current output chip | $I_{\mathrm{Q2}}$ | _    | 1.2    | 2.0  | mA | $V_{\rm VCC2}$ = 15 V<br>IN+ = High,<br>IN- = Low<br>=>OUT = High   |

# 5.3.2 Logic Input

Note: Unless stated otherwise VCC1 = 5.0V

Table 5 Logic Input

| Parameter                  | Symbol               | Values |      |      | Unit | Note /                         |

|----------------------------|----------------------|--------|------|------|------|--------------------------------|

|                            |                      | Min.   | Тур. | Max. |      | Test Condition                 |

| IN+,IN- low input voltage  | $V_{IN+L}, V_{IN-L}$ | _      | _    | 30   | %    | of VCC1                        |

| IN+,IN- high input voltage | $V_{IN+H}, V_{IN-H}$ | 70     | _    | _    | %    | of VCC1                        |

| IN+,IN- low input voltage  | $V_{IN+L}, V_{IN-L}$ | _      | _    | 1.5  | V    | _                              |

| IN+,IN- high input voltage | $V_{IN+H}, V_{IN-H}$ | 3.5    | _    | _    | V    | _                              |

| IN- input current          | $I_{IN-}$            | _      | 70   | 200  | μΑ   | $V_{\text{IN-}}$ = GND1        |

| IN+ input current          | $I_{IN+}$            | _      | 70   | 200  | μΑ   | $V_{\text{IN+}} = \text{VCC1}$ |

### 5.3.3 Gate Driver

Table 6 Gate Driver

| Parameter              | Symbol                 | Values |      |      | Unit | Note /                   |

|------------------------|------------------------|--------|------|------|------|--------------------------|

|                        |                        | Min.   | Тур. | Max. |      | <b>Test Condition</b>    |

| High level output peak | $I_{OUT+,PEAK}$        |        |      | _    | Α    | 1)                       |

| current (source)       | 3311,1 E/11            |        |      |      |      | IN+ = High,              |

| 1EDI20N12AF            |                        | 2.0    | 4.0  |      |      | IN- = Low,               |

|                        |                        |        |      |      |      | $V_{\rm VCC2}$ = 15 V    |

| Low level output peak  | $I_{OUT\text{-},PEAK}$ |        |      | _    | Α    | 1)                       |

| current (sink)         | OO. ,I LAIR            |        |      |      |      | IN+ = Low,               |

| 1EDI20N12AF            |                        | 2.0    | 3.5  |      |      | IN- = Low,               |

|                        |                        |        |      |      |      | V <sub>VCC2</sub> = 15 V |

<sup>1)</sup> voltage across the device  $V_{(VCC2-OUT+)}$  or  $V_{(OUT-GND2)} < V_{VCC2}$ .

Data Sheet 16 Rev. 2.0, 2015-06-01

**Electrical Parameters**

# 5.3.4 Short Circuit Clamping

Table 7 Short Circuit Clamping

| Parameter                                                | Symbol       | Values |      |      | Unit | Note /                                                                                                              |

|----------------------------------------------------------|--------------|--------|------|------|------|---------------------------------------------------------------------------------------------------------------------|

|                                                          |              | Min.   | Тур. | Max. |      | Test Condition                                                                                                      |

| Clamping voltage (OUT+) $(V_{\rm OUT}$ - $V_{\rm VCC2})$ | $V_{CLPout}$ | -      | 0.9  | 1.3  | V    | IN+ = High,<br>IN- = Low,<br>OUT = High<br>$I_{\text{OUT}}$ = 500 mA<br>pulse test,<br>$t_{\text{CLPmax}}$ = 10 µs) |

### 5.3.5 Dynamic Characteristics

Dynamic characteristics are measured with  $V_{\rm VCC1}$  = 5 V and  $V_{\rm VCC2}$  = 15 V.

**Table 8** Dynamic Characteristics

| Parameter                                                                                                  | Symbol                                   | Values |      |      | Unit | Note /                                                                        |

|------------------------------------------------------------------------------------------------------------|------------------------------------------|--------|------|------|------|-------------------------------------------------------------------------------|

|                                                                                                            |                                          | Min.   | Тур. | Max. |      | Test Condition                                                                |

| Input IN to output propagation delay ON                                                                    | $T_{PDON}$                               | 90     | 115  | 137  | ns   | $C_{\rm LOAD}$ = 100 pF $V_{\rm IN+}$ = 50%, $V_{\rm OUT}$ =50% @ 25°C        |

| Input IN to output propa-<br>gation delay OFF                                                              | $T_{PDOFF}$                              | 100    | 120  | 143  | ns   |                                                                               |

| Input IN to output propagation delay distortion $(T_{\text{PDOFF}} - T_{\text{PDON}})$                     | $T_{PDISTO}$                             | -15    | 5    | 25   | ns   |                                                                               |

| Input pulse suppression IN+, IN-                                                                           | $T_{\text{MININ+}},$ $T_{\text{MININ-}}$ | 30     | 40   | -    | ns   | _                                                                             |

| IN input to output propagation delay ON variation due to temp                                              | $T_{PDONt}$                              | _      | -    | 10   | ns   | $^{1)}C_{\text{LOAD}}$ = 100 pF $V_{\text{IN+}}$ = 50%, $V_{\text{OUT}}$ =50% |

| IN input to output propagation delay OFF variation due to temp                                             | $T_{PDOFFt}$                             | -      | _    | 10   | ns   | $^{1)}C_{\text{LOAD}}$ = 100 pF $V_{\text{IN+}}$ = 50%, $V_{\text{OUT}}$ =50% |

| IN input to output propagation delay distortion variation due to temp ( $T_{\rm PDOFF}$ - $T_{\rm PDON}$ ) | $T_{ m PDISTOt}$                         | -      | -    | 4    | ns   | $^{1)}C_{\rm LOAD}$ = 100 pF $V_{\rm IN+}$ = 50%, $V_{\rm OUT}$ =50%          |

| Rise time                                                                                                  | $T_{RISE}$                               | 5      | 10   | 20   | ns   | $C_{\rm LOAD}$ = 1 nF $V_{\rm L}$ 20%, $V_{\rm H}$ 80%                        |

| Fall time                                                                                                  | $T_{FALL}$                               | 4      | 9    | 19   | ns   | $C_{\text{LOAD}}$ = 1 nF $V_{\text{L}}$ 20%, $V_{\text{H}}$ 80%               |

<sup>1)</sup> The parameter is not subject to production test - verified by design/characterization

# 1EDI EiceDRIVER™ Compact 1EDI20N12AF

**Electrical Parameters**

### 5.3.6 Active Shut Down

Table 9 Active Shut Down

| Parameter                | Symbol                           | Values |      |      | Unit | Note /                                                             |  |

|--------------------------|----------------------------------|--------|------|------|------|--------------------------------------------------------------------|--|

|                          |                                  | Min.   | Тур. | Max. |      | Test Condition                                                     |  |

| Active shut down voltage | V <sub>ACTSD</sub> <sup>1)</sup> | _      | 2.2  | 2.5  | V    | $I_{\rm OUT-}/I_{\rm OUT-,PEAK} = 0.1,$ $V_{\rm CC2} \ {\rm open}$ |  |

<sup>1)</sup> Referred to GND2

Data Sheet 18 Rev. 2.0, 2015-06-01

**Timing Diagramms**

# 6 Timing Diagramms

Figure 6 Propagation Delay, Rise and Fall Time

Figure 7 Typical Switching Behavior

Figure 8 UVLO Behavior

Data Sheet 19 Rev. 2.0, 2015-06-01

**Package Outlines**

# 7 Package Outlines

Figure 9 PG-DSO-8-51 (Plastic (Green) Dual Small Outline Package)

Data Sheet 20 Rev. 2.0, 2015-06-01

**Application Notes**

# 8 Application Notes

### 8.1 Reference Layout for Thermal Data

The PCB layout shown in **Figure 10** represents the reference layout used for the thermal characterisation. Pin 4 (GND1) and pin 8 (GND2) require each a ground plane of 100 mm<sup>2</sup> for achieving maximum power dissipation. The 1EDI20N12AF is conceived to dissipate most of the heat generated through these pins.

The thermal coefficient junction-top ( $\Psi_{th,jt}$ ) can be used to calculate the junction temperature at a given top case temperature and driver power dissipation:

$$T_i = \Psi_{th,it} \cdot P_D + T_{top}$$

Figure 10 Reference Layout for Thermal Data (Copper thickness 35 μm)

#### 8.2 Printed Circuit Board Guidelines

The following factors should be taken into account for an optimum PCB layout.

- Sufficient spacing should be kept between high voltage isolated side and low voltage side circuits.

- The same minimum distance between two adjacent high-side isolated parts of the PCB should be maintained to increase the effective isolation and to reduce parasitic coupling.

- In order to ensure low supply ripple and clean switching signals, bypass capacitor trace lengths should be kept as short as possible.

Data Sheet 21 Rev. 2.0, 2015-06-01

w w w .in fineon.com