### 3+1-phase dual loop voltage regulator

### **Features**

- Low quiescent power dual output PWM controller supporting 3+1 configuration

- Intel® VR13 rev 1.1, VR12.5 rev1.5, VR12 rev 1.7, IMVP8 rev 1.2 and memory VR modes

- Switching frequency from 200 kHz to 2 MHz per phase

- Infineon efficiency shaping features including dynamic phase control and automatic power state switching

- Programmable 1 or 2-phase operation for light loads and active diode emulation for very light loads

- Digitally programmable load line no external components are needed to set the load line

- Infineon Adaptive Transient Algorithm (ATA) on both loops minimizes output bulk capacitors and system cost

- Auto-phase detection with PID coefficient auto-scaling

- Fault protection: OVP, UVP, OCP, OTP, CFP, cycle-by-cycle current limit

- I2C/SMBus/PMBus system interface for reporting of temperature, voltage, current and power telemetry for both loops

- Multiple Time Programming (MTP) with up to 27 writes for the USER section

- Compatible with industry standard 3.3 V tri-state drivers

- +3.3 V supply voltage; -40°C to 85°C ambient operation

- Pb-Free, RoHS, 5x5 mm 40-pin, 0.4 mm pitch QFN

### **Description**

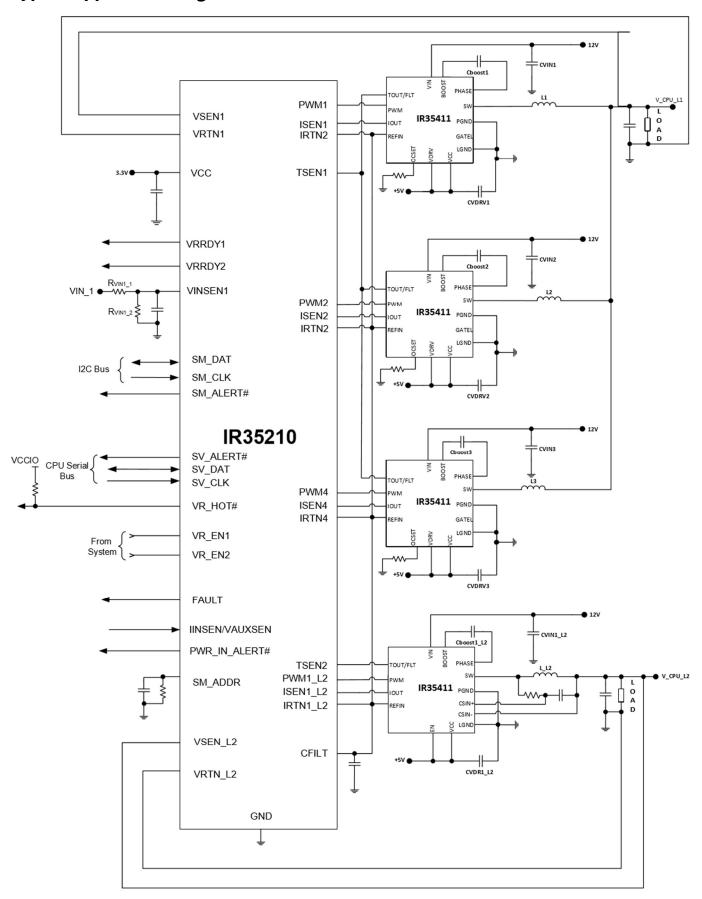

The IR35210 is a dual loop, digital, multi-phase buck controller designed for CPU and DDR voltage regulation, and is fully compliant with Intel® VR13, VR12.5, VR12 & IMVP8.

The IR35210 includes Infineon's efficiency shaping technology to deliver exceptional efficiency at minimum cost across the entire load range. Infineon's dynamic phase control adds/drops phases based upon load current. The IR35210 can be configured to enter 1 or 2-phase operation and active diode emulation mode automatically or by command.

The IR35210 offers digitally programmable load line thereby eliminating the need for any external load line setting component. The controller is designed to work with integrated and DCR current sense power stages and provides accurate input and output current reporting.

Infineon's unique Adaptive Transient Algorithm (ATA), based on proprietary non-linear control algorithms provides excellent transient response with reduced output capacitance. The controller also supports programmable cycle-by-cycle current limit per phase for superior dynamic current limiting.

The device configuration can be easily defined using the Infineon PowIRCenter GUI and is stored in the on-chip memory.

The IR35210 provides extensive OVP, UVP, OCP, OTP and CFP fault protection. The controller requires the fewest possible external components and supports a clean interface with the power stages resulting in a simplified Bill Of Materials (BOM).

### 3+1-phase dual loop voltage regulator

## **Potential applications**

- Intel® VR13, VR12.5, VR12 and IMVP8 based systems

- Servers and high end desktop CPU VRs

- Memory VR

### **Product validation**

Qualified for industrial applications according to the relevant tests of JEDEC47/20/22

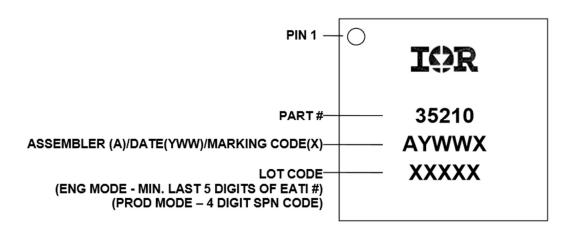

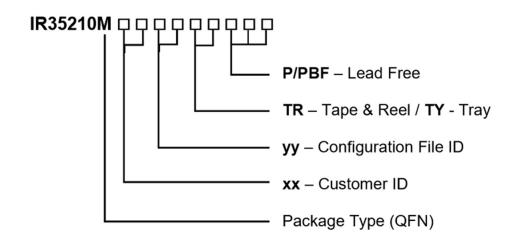

### **Product identification and ordering information**

| Part number | Package type            | Standard pack<br>form and quantity |      | Marking          |

|-------------|-------------------------|------------------------------------|------|------------------|

| IR35210     | 40-pin, QFN 5 mm x 5 mm | Tape and reel                      | 3000 | IR35210MxxyyTRP1 |

| IR35210     | 40-pin, QFN 5 mm x 5 mm | Tape and reel                      | 3000 | IR35210MTRPBF    |

| IR35210     | 40-pin, QFN 5 mm x 5 mm | Tray                               | 4900 | IR35210MTYPBF    |

<sup>&</sup>lt;sup>1</sup> Customer specific configuration file, where xx = customer ID and yy = configeration file (codes assigned by Infineon marketing).

## 3+1-phase dual loop voltage regulator

## Typical application diagram

V 1.0

### 3+1-phase dual loop voltage regulator

#### **Trademarks**

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2019-8-27 Published by Infineon Technologies AG 81726 Munich, Germany

© 2019 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document?

Email: erratum@infineon.com

**Document reference**

IR35210 data brief

### IMPORTANT NOTICE

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (www.infineon.com).

### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.