**Released Data Sheet - Confidential**

# iNAND 7550 64GB+32Gb, 64GB+48Gb MCP

e.MMC 5.1 with Command-Queue, HS400 Interface and LPDDR4x

#### **REVISION HISTORY**

| Doc. No               | Revision | Date        | Description     | Reference |

|-----------------------|----------|-------------|-----------------|-----------|

| 02-05-WW-<br>02-00020 | 0.1      | 04-Jan-2018 | Initial version |           |

SanDisk® general policy does not recommend the use of its products in life support applications where in a failure or malfunction of the product may directly threaten life or injury. Per SanDisk® Terms and Conditions of Sale, the user of SanDisk® products in life support applications assumes all risk of such use and indemnifies SanDisk® against all damages. See "Disclaimer of Liability."

This document is for information use only and is subject to change without prior notice. SanDisk® assumes no responsibility for any errors that may appear in this document, nor for incidental or consequential damages resulting from the furnishing, performance or use of this material. No part of this document may be reproduced, transmitted, transcribed, stored in a retrievable manner or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise, without the prior written consent of an officer of SanDisk®.

All parts of the SanDisk® documentation are protected by copyright law and all rights are reserved. SanDisk® and the SanDisk® logo are registered trademarks of Western Digital Corporation or its affiliates. Product names mentioned herein are for identification purposes only and may be trademarks and/or registered trademarks of their respective companies.

© 2017 Western Digital Corporation or its affiliates. All rights reserved.

## TABLE OF CONTENTS

| 1. | Intro | duction                                                | . 5 |

|----|-------|--------------------------------------------------------|-----|

|    | 1.1.  | General Description                                    | . 5 |

|    | 1.2.  | Plug-and-Play Integration                              | . 5 |

|    | 1.3.  | Feature Overview                                       | . 7 |

|    | 1.4.  | Defect and Error Management.                           |     |

|    | 1.5.  | MMC bus and Power Lines.                               | . 8 |

|    |       | 1.5.1. Bus operating conditions                        |     |

|    |       | 1.5.2. Low Power Mobile DDR4x Bus Operating Conditions |     |

|    | 1.6.  | HS400 Interface                                        | 11  |

|    | 1.7.  | Field Firmware Upgrade (FFU)                           | 11  |

|    | 1.8.  | Cache                                                  |     |

|    | 1.9.  | Discard                                                |     |

|    |       | Power off Notifications                                |     |

|    |       | Packed Commands                                        |     |

|    | 1.12. | Boot Partition                                         | 12  |

|    |       | RPMB Partition                                         |     |

|    | 1.14. | Automatic Sleep Mode                                   | 12  |

|    |       | Sleep (CMD5)                                           |     |

|    | 1.16. | Enhanced Reliable Write                                | 12  |

|    |       | Sanitize                                               |     |

|    | 1.18. | Secure Erase                                           | 13  |

|    | 1.19. | Secure Trim                                            | 13  |

|    | 1.20. | Partition Management                                   | 13  |

|    | 1.21. | Device Health                                          | 13  |

|    | 1.22. | EOL Status                                             | 14  |

|    | 1.23. | Enhanced Write Protection                              | 14  |

|    | 1.24. | High Priority Interrupt (HPI)                          | 14  |

|    | 1.25. | H/W Reset                                              | 14  |

|    | 1.26. | Host-Device Synchronization Flow (Enhanced STROBE)     | 14  |

|    | 1.27. | Command-Queue                                          | 15  |

|    | 1.28. | Frequent Used Commands in CmdQ                         | 15  |

|    |       | HS400 Tuning                                           |     |

| 2. | Prod  | uct Specifications                                     | 16  |

|    |       |                                                        |     |

|    | 2.1.  | Typica   | l Power Requirements                             | 16            |

|----|-------|----------|--------------------------------------------------|---------------|

|    | 2.2.  | Operat   | ing Conditions                                   | 17            |

|    |       | 2.2.1.   | Operating and Storage Temperature Specifications | 17            |

|    |       | 2.2.2.   | Moisture Sensitivity                             | 17            |

|    | 2.3.  | Reliab   | ility                                            | 17            |

|    | 2.4.  | Systen   | n Performance                                    | 19            |

| 3. | Phys  | ical Sp  | ecifications                                     | 20            |

| 4. | Inter | face Do  | escription                                       | 23            |

|    | 4.1.  |          | I/F Ball Array                                   |               |

|    | 4.2.  |          | ers value                                        |               |

|    |       | 4.2.1.   | OCR Register                                     |               |

|    |       | 4.2.2.   | CID Register                                     | 26            |

|    |       | 4.2.3.   | DSR Register                                     | 26            |

|    |       | 4.2.4.   | CSD Register                                     | 27            |

|    |       | 4.2.5.   | EXT_CSD Register                                 | 28            |

|    |       | 4.2.6.   | User Density                                     | 33            |

| 5. | Powe  | er Deliv | very and Capacitor Specifications                | 34            |

|    | 5.1.  | SanDi    | sk iNAND 7550 MCP Power Domains                  | 34            |

|    | 5.2.  | Capac    | itor Connection Guidelines                       | 35            |

| 6. | Prop  | riety iN | NAND 7550 MCP feature overview                   | 37            |

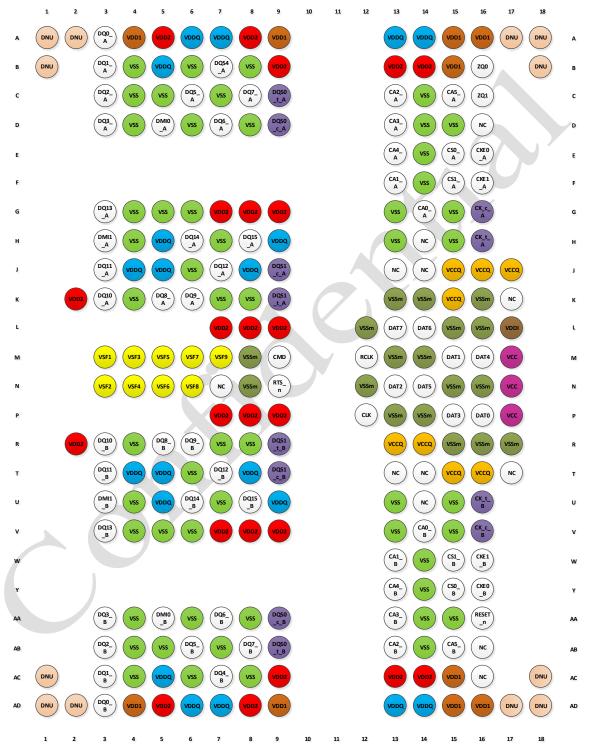

|    | 6.1.  | Conte    | nt Preloading Operation Mode                     | 37            |

|    | 6.2.  | Smart    | SLC                                              | 38            |

|    | 6.3.  | Device   | e Report                                         | 39            |

| 7. | Mar   | king     | •                                                | 42            |

|    |       |          | formation                                        |               |

|    |       |          | I.a.                                             | <del>40</del> |

|    |       |          |                                                  |               |

#### 1. Introduction

#### 1.1. General Description

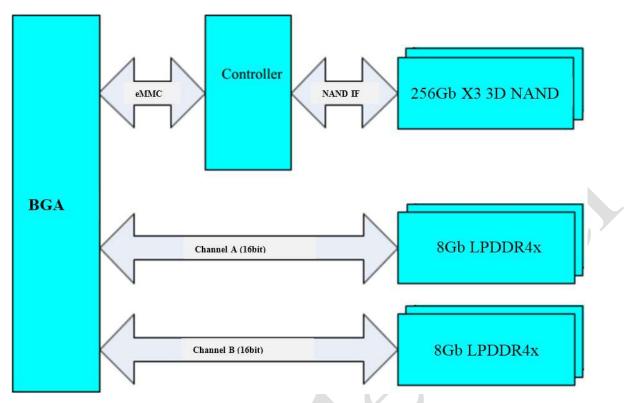

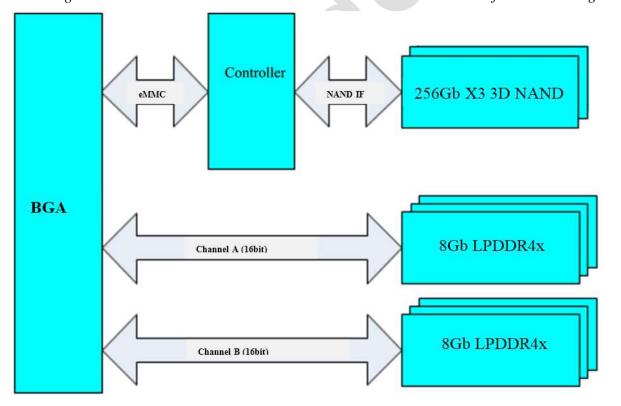

Overview iNAND 7550 MCP is an Embedded Flash Drive (EFD) with low power DRAM in one package that is designed for mobile handsets and consumer electronic devices. iNAND 7550 MCP is a hybrid device combining an embedded thin flash controller and 3D NAND flash memory, with an industry standard e.MMC 5.1interface featuring Command-Queue, HS400, FFU, as well as legacy eMMC 4.51 features such as Power Off Notifications, Packed commands, Cache, Boot / RPMB partitions, HPI, and HW Reset, make it an optimal device for both reliable code and data storage.

iNAND 7550 MCP is based on SanDisk 256Gb X3 3D NAND memory, using 64-layer technology. The memory architecture brings new levels of density, scalability and performance to the Embedded Flash Drive. SanDisk 3D NAND memory also provides enhanced write/erase endurance, write speeds and energy efficiency relative to conventional 2D NAND.

In addition to the high reliability, robustness and consistence system performance offered by the current iNAND family of products, iNAND 7550 MCP offers plug-and-play integration and support for multiple NAND technology transitions, as well as features such as an advanced power management scheme.

The iNAND 7550 MCP architecture and embedded firmware fully emulates a hard disk to the host processor, enabling read/write operations that are identical to a standard, sector-based hard drive. In addition, SanDisk firmware employs patented methods, such as virtual mapping, dynamic and static wear-leveling, and automatic block management to ensure high data reliability and maximizing flash life expectancy.

SanDisk iNAND 7550 MCP provides 64GB of memory for use in mass storage applications and is paired with up to 48 Gb of LPDDR4x DRAM. In addition to the mass-storage-specific flash memory chip and the low-power DRAM, iNAND 7550 MCP includes an intelligent controller, which manages interface protocols, data storage and retrieval, error correction code (ECC) algorithms, defect handling and diagnostics, power management and clock control.

Combining high performance with features for easy integration and exceptional reliability, iNAND 7550 MCP is an EFD designed to exceed the demands of both manufacturers and their customers.

#### 1.2. Plug-and-Play Integration

iNAND's optimized architecture eliminates the need for complicated software integration and testing processes thereby enabling plug-and-play integration into the host system. The replacement of one iNAND device with another, of a newer generation, requires virtually no changes to the host. This allows manufacturers to adopt advanced NAND Flash technologies and update product lines with minimal integration or qualification efforts.

With JEDEC form factors measuring 11.5x13mm for all capacities, iNAND 7550 MCP is ideally suited for a wide variety of portable devices such as multimedia mobile handsets, tablets, and other consumer products.

iNAND 7550 MCP features a MMC interface allows easy integration regardless of the host (chipset) type used. All device and interface configuration data (such as maximum frequency and device identification) are stored on the device.

Figure 1 - SanDisk iNAND 7550 64GB+32Gb MCP with MMC Interface Block Diagram

Figure 2 - SanDisk iNAND 7550 64GB+48Gb MCP with MMC Interface Block Diagram

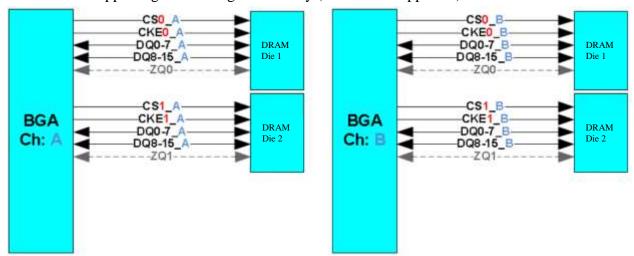

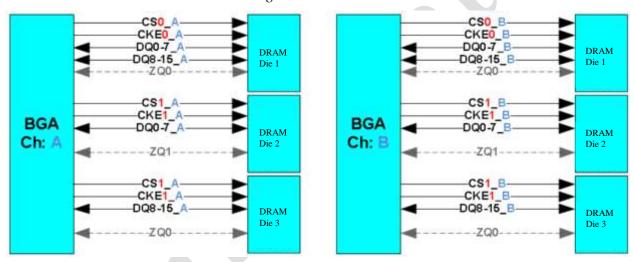

WDC is supporting 2CS configuration only (3CS is not supported)

Figure 3- 32Gb 2CS

Figure 4- 48Gb 2CS

#### 1.3. Feature Overview

SanDisk iNAND 7550 MCP, with MMC interface, includes the following features:

- Memory controller and NAND flash

- Mechanical design complies with JEDEC Specification

- Offered in two package dimensions

- 11.5mm x 13mm x 1.0mm (64GB+32Gb LPDDR4x)

- 11.5mm x 13mm x 1.1mm (64GB+48Gb LPDDR4x)

- Operating temperature range: -25C° to +85C°

- Dual power system

- Core voltage (VCC) 2.7-3.6 V

- I/O (VCCQ) voltage, either: 1.7-1.95V or 2.7-3.6V

- 64 GB of data storage

- Supports three data bus widths: 1bit (default), 4bit, 8bit

- Complies with eMMC Specification Ver. 5.1 HS400

- Variable clock frequencies of 0-20 MHz, 0-26 MHz (default), 0-52 MHz (high-speed), 0-200

- MHz SDR (HS200), 0-200 MHz DDR (HS400)

- Up to 400 MB/sec bus transfer rate, using 8 parallel data lines at 400 MHz, HS400 Mode

- Correction of memory field errors

- Designed for portable and stationary applications that require high performance and reliable data storage

- RPMB Key Reset

- Low-power mobile DDR4x

- $\circ$  Core power 1, Core power 2 and I/O voltage 1.7V 1.95V, 1.06V 1.17V, and 0.57V 0.65V respectively

- o Up to 1866 MHz clock with 32bit data interface

#### 1.4. Defect and Error Management

The SanDisk iNAND 7550 MCP contains a sophisticated defect and error management system for exceptional data reliability. iNAND 7550 MCP will rewrite data from a defective sector to a good sector. This is completely transparent to the host and does not consume additional user data space. In the extremely rare case that a read error does occur, iNAND has innovative algorithms to recover the data

#### 1.5. MMC bus and Power Lines

SanDisk iNAND 7550 MCP with MMC interface supports the MMC protocol. For more details regarding these buses refer to JEDEC standards No. JESD84-B51.

The iNAND bus has the following communication and power lines:

- CMD: Command is a bidirectional signal. The host and iNAND operate in two modes, open drain and push-pull.

- DAT0-7: Data lines are bidirectional signals. Host and iNAND operate in push-pull mode.

- CLK: Clock input.

- RST\_n: Hardware Reset Input.

- VCCQ: VCCQ is the power supply line for host interface.

- VCC: VCC is the power supply line for internal flash memory.

- VDDi: VDDi is iNAND's internal power node, not the power supply. Connect 0.1uF capacitor from VDDi to ground.

- VSS, VSSQ: Ground lines.

- RCLK: Data strobe.

- VSF: Vendor specific functions used for debugging purposes.

#### 1.5.1. Bus operating conditions

Table 1 - Bus operating conditions

| Parameter                                                                                              | Min  | Max      | Unit |

|--------------------------------------------------------------------------------------------------------|------|----------|------|

| Peak voltage on all lines                                                                              | -0.5 | VCCQ+0.5 | V    |

| Input Leakage Current (before initializing and/or connecting the internal pull-up resistors)           | -100 | 100      | μΑ   |

| Input Leakage Current (after changing the bus width and disconnecting the internal pull-up resistors)  | -2   | 2        | μΑ   |

| Output Leakage Current (before initializing and/or connecting the internal pull-up resistors)          | -100 | 100      | μА   |

| Output Leakage Current (after changing the bus width and disconnecting the internal pull-up resistors) | -2   | 2        | μΑ   |

Table 2 – Power supply voltage

| Parameter      | Symbol      | Min  | Max  | Unit |

|----------------|-------------|------|------|------|

|                | VCCQ (Low)  | 1.7  | 1.95 | V    |

| Supply Voltage | VCCQ (High) | 2.7  | 3.6  | V    |

| Supply Voltage | VCC         | 2.7  | 3.6  | V    |

|                | VSS-VSSQ    | -0.3 | 0.3  | V    |

*Note1*: HS400 mode only supports the 1.7 – 1.95 V VCCQ option

Note2: Device operation under 3.3V VCCQ is limited to Max 1 hour

#### 1.5.2. Low Power Mobile DDR4x Bus Operating Conditions

See Appendix A for DRAM operating condition specifications.

## 1.5.3 e.MMC 5.1 Selected Features Overview

iNAND 7550 MCP supported feature list:

| e.MMC     | Device Features              | Benefit                                   | Support        |

|-----------|------------------------------|-------------------------------------------|----------------|

| N/A       | INTERFACE                    | Speed                                     | HS400          |

| N/A       | BUS SPEED                    | Max theoretical Speed                     | Up to 400MB/s  |

| 4.41      | SECURE ERASE/TRIM            | "True Wipe"                               | Yes            |

| 4.41      | BOOT AND MASS STORAGE        | One storage device (reduced BOM)          | Yes            |

| 4.41      | PARTITIONING & PROTECTION    | Flexibility                               | Yes            |

| 4.41      | BACKGROUND OPERATIONS        | Better User Experience (low latency)      | Yes            |

| 4.41      | POWER OFF NOTIFICATION       | Faster Boot; Responsiveness               | Yes            |

| 4.41      | HARDWARE RESET               | Robust System Design                      | Yes            |

| 4.41      | НРІ                          | Control Long Reads/Writes                 | Yes            |

| 4.41      | RPMB                         | Secure Folders                            | Yes            |

| 4.5       | EXTENDED PARTITION ATTRIBUTE | Flexibility                               | Yes            |

| 4.5       | LARGE SECTOR SIZE            | Potential performance                     | No             |

| 4.5       | SANITIZE (4.51)              | "True Wipe"                               | Yes            |

| 4.5       | PACKED COMMANDS              | Reduce Host Overhead                      | Yes            |

| 4.5       | DISCARD                      | Improved Performance on Full Media        | Yes            |

| 4.5       | DATA TAG                     | Performance and/or Reliability            | Yes (API only) |

| 4.5       | CONTEXT MANAGEMENT           | Performance and/or Reliability            | Yes (API only) |

| 4.5       | CACHE                        | Better Sequential & Random Writes         | Yes            |

| 5.0       | FIELD FIRMWARE UPGRADE (FFU) | Enables feature enhancements in the field | Yes            |

| 5.0       | PRODUCTION STATE AWARENESS   | Different operation during production     | Yes            |

| 5.0       | DEVICE HEALTH                | Vital NAND info                           | Yes            |

| 5.1       | ENHANCE STROBE               | Sync between Device and Host in HS400     | Yes            |

| 5.1       | COMMAND QUEUE                | Responsiveness                            | Yes            |

| 5.1       | RPMB THROUGHPUT              | Faster RPMB write throughput              | Yes            |

| 5.1       | CACHE FLUSH AND BARRIER      | Ordered Cache flushing                    | Yes            |

| 5.1       | BKOPS CONTROLLER             | /Host control on BKOPs                    | Yes            |

| 5.1       | SECURE WP                    | Secure Write Protect                      | Yes            |

| 5.2       | HS400 TUNING                 | DLL Tuning command in HS400               | Yes            |

| Propriety | SMART-SLC                    | Fast write speed per application need     | Yes            |

| Propriety | VSF                          | Enable on-board debugging                 | Yes            |

| Propriety | PNM                          | Special product name                      | Yes            |

| Propriety | DEVICE REPORT                | Device Firmware status                    | Yes            |

| Propriety | CONTENT-PRELOADING           | Preloading content at production line     | Yes            |

| Propriety | RPMB-KEY-RESET               | Resetting RPMB partition key              | Yes            |

#### 1.6. HS400 Interface

Support HS400 signaling to achieve a bus speed of 400 MB/s via a 200MHz dual data rate clock frequency. HS400 mode supports 4 or 8 bit bus width and the 1.7 - 1.95 VCCQ option. Due to the speed, the host may need to have an adjustable sampling point to reliably receive the incoming data.

#### 1.7. Field Firmware Upgrade (FFU)

Field Firmware Updates (FFU) enables features enhancement in the field. Using this mechanism,

the host downloads a new version of the firmware to the e.MMC device and instructs the e.MMC device to install the new downloaded firmware into the device. The entire FFU process occurs in the background without affecting the user / OS data. During the FFU process, the host can replace firmware files or single / all file systems.

The secure FFU (sFFU) usage model for firmware upgrades is as follows:

- 1. sFFU files are generated and signed at the SanDisk lab

- 2. The sFFU files are handed to SanDisk's customer

- 3. SanDisk's customer can push the firmware updates to their end-users in a transparent way

Note 1: The sFFU process and sFFU files are protected against leakage to unauthorized entities.

Note 2: During the sFFU process the Host may retrieve the exact status of the process using the smart report feature.

For additional information please refer to JESD84-B51 standard and the SanDisk application note on this subject

#### 1.8. Cache

The e.MMC cache is dedicated volatile memory at the size of 512KB. Caching enables to improve iNAND performance for both sequential and random access. For additional information please refer to JESD84-B51 standard.

#### 1.9. Discard

iNAND supports discard command as defined in e.MMC 5.1 spec. This command allows the host to identify data which is not needed, without requiring the device to remove the data from the Media. It is highly recommended for use to guarantee optimal performance of iNAND and reduce amount of housekeeping operation.

#### 1.10. Power off Notifications

iNAND supports power off notifications as defined in e.MMC 5.1 spec. The usage of power off notifications allows the device to prepare itself to power off, and improve user experience during power-on. Note that the device may be set into sleep mode while power off notification is enabled. Power off notification long allows the device to shutdown properly and save important data for fast boot time on the next power cycle.

#### 1.11. Packed Commands

To enable optimal system performance, iNAND supports packed commands as defined in e.MMC5.1 spec. It allows the host to pack Read or Write commands into groups (of single type of

operation) and transfer these to the device in a single transfer on the bus. Thus, it allows reducing overall bus overheads.

#### 1.12. Boot Partition

iNAND supports e.MMC 5.1 boot operation mode: Factory configuration supplies two boot partitions each 4MB in size.

#### 1.13. RPMB Partition

iNAND supports e.MMC 5.1 RPMB operation mode: Factory configuration supplies one RPMB partition 16MB in size.

#### 1.14. Automatic Sleep Mode

A unique feature of iNAND is automatic entrance and exit from sleep mode. Upon completion of an operation, iNAND enters sleep mode to conserve power if no further commands are received. The host does not have to take any action for this to occur, however, in order to achieve the lowest sleep current, the host needs to shut down its clock to the memory device. In most systems, embedded devices are in sleep mode except when accessed by the host, thus conserving power. When the host is ready to access a memory device in sleep mode, any command issued to it will cause it to exit sleep and respond immediately.

#### **1.15. Sleep (CMD5)**

An iNAND 7550 MCP device may be switched between a Sleep and a Standby state using the SLEEP/AWAKE (CMD5). In the Sleep state the power consumption of the memory device is minimized and the memory device reacts only to the commands RESET (CMD0) and SLEEP/AWAKE (CMD5). All the other commands are ignored by the memory device.

The VCC power supply may be switched off in Sleep state to enable even further system power consumption saving.

For additional information please refer to JESD84-B51.

#### 1.16. Enhanced Reliable Write

iNAND 7550 MCP supports enhanced reliable write as defined in e.MMC 5.1 spec.

Enhanced reliable write is a special write mode in which the old data pointed to by a logical address must remain unchanged until the new data written to same logical address has been successfully programmed. This is to ensure that the target address updated by the reliable write transaction never contains undefined data. When writing in reliable write, data will remain valid even if a sudden power loss occurs during programming.

#### 1.17. Sanitize

The Sanitize operation is used to remove data from the device. The use of the Sanitize operation requires the device to physically remove data from the unmapped user address space. The device will continue the sanitize operation, with busy asserted, until one of the following events occurs:

- Sanitize operation is complete

- HPI is used to abort the operation

- Power failure

- Hardware reset

Following a sanitize operation completion, no data should remain in the unmapped host address space.

#### 1.18. Secure Erase

For backward compatibility reasons, in addition to the standard erase command the iNAND 7550 MCP supports the optional Secure Erase command.

This command allows the host to erase the provided range of LBAs and ensure no older copies of this data exist in the flash.

#### 1.19. Secure Trim

For backward compatibility reasons, iNAND 7550 MCP supports Secure Trim command. The Secure

Trim command is similar to the Secure Erase command but performs a secure purge operation on write blocks instead of erase groups.

The secure trim command is performed in two steps:

- 1. Marks the LBA range as candidate for erase.

- 2. Erases the marked address range and ensures no old copies are left.

#### 1.20. Partition Management

iNAND 7550 MCP offers the possibility for the host to configure additional split local memory partitions with independent addressable space starting from logical address 0x00000000 for different usage models. Therefore, memory block area scan be classified as follows:

- Factory configuration supplies two boot partitions (refer to section 1.12) implemented as enhanced storage media and one RPMB partitioning of 16MB in size (refer to section 1.13).

- Up to four General Purpose Area Partitions can be configured to store user data or sensitive data, or for other host usage models. The size of these partitions is a multiple of the write protect group. Size can be programmed once in device life-cycle (one-time programmable).

#### 1.21. Device Health

Device Health is similar to SMART features of modern hard disks; it provides only vital NAND flash program/erase cycles information in percentage of the flash life span.

The host can query Device Health information utilizing standard MMC command, to get the extended CSD structure:

DEVICE\_LIFE\_TIME\_EST\_TYP\_A[268], The host may use it to query SLC device health information

DEVICE\_LIFE\_TIME\_EST\_TYP\_B[269], The host may use it to query TLC device health information

The device health feature will provide a % of the wear of the device in 10% fragments.

#### 1.22. EOL Status

EOL status is implemented according to the e.MMC 5.1 spec. One additional state (state 4) was added to iNAND 7550 MCP which indicates that the device is in EOL mode.

#### 1.23. Enhanced Write Protection

To allow the host to protect data against erase or write iNAND 7550 MCP supports two levels of write protect command:

- The entire iNAND 7550 MCP (including the Boot Area Partitions, General Purpose Area Partition, and User Area Partition) may be write-protected by setting the permanent or temporary write protect bits in the CSD

- Specific segments of iNAND 7550 MCP may be permanently, power-on or temporarily write protected. Segment size can be programmed via the EXT\_CSD register

For additional information please refer to the JESD84-B51 standard.

#### 1.24. High Priority Interrupt (HPI)

The operating system usually uses demand-paging to launch a process requested by the user. If the host needs to fetch pages while in a middle of a write operation the request will be delayed until the completion of the write command.

The high priority interrupt (HPI) as defined in JESD84-B51 enables low read latency operation by suspending a lower priority operation before it is actually completed.

For additional information on the HPI function, refer to JESD84-B51.

#### 1.25. H/W Reset

Hardware reset may be used by host to reset the device, moving the device to a Pre-idle state and disabling the power-on period write protect on blocks that were power-on write protected before the reset was asserted. For more information, refer to JESD84-B51 standard.

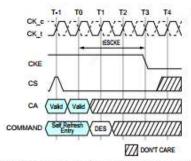

#### **1.26.** Host-Device Synchronization Flow (Enhanced STROBE)

The Enhanced STROBE feature as implemented in iNAND 7550 MCP allows utilizing STROBE to synchronize also the CMD response:

- CMD clocking stays SDR (similar to legacy DDR52)

- Host commands are clocked out with the rising edge of the host clock (as done in legacy e.MMC devices)

- iNAND 7550 MCP will provide STROBE signaling synced with the CMD response in addition to DATA Out

- Host may use the STROBE signaling for DAT and CMD-Response capturing eliminating the need for a tuning mechanism

This feature requires support by the host to enable faster and more reliable operation.

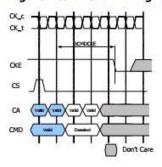

#### 1.27. Command-Queue

e.MMC Command Queue enables device visibility of next commands and allows performance improvement. The protocol allows the host to queue up to 32 data-transfer commands in the device by implementing 5 new commands.

The benefits of command queuing are:

- Random Read performance improvement (higher IOPs)

- Reducing protocol overhead

- Command issuance allowed while data transfer is on-going

- Device order the tasks according to best access to/from flash

#### 1.28. Frequent Used Commands in CmdQ

The Frequent Used Commands feature permits the following commands to be sent by the host when queue is non-empty FLUSH, BARRIER and DISCARD. In addition, the Frequent Used Commands feature provides alternative encodings for these commands to facilitate faster processing in device.

This feature can increase the effective performance when using Command Queue mode.

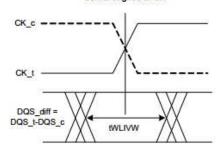

#### 1.29. HS400 Tuning

This feature enables tuning command (CMD21) in HS400 mode, which may be used for calibration of DLL to compensate of PCB design/manufacturing differences. The Host may use adjustable sampling to determine the correct sampling point. A predefined tuning block stored in Device may be used by the Host as an aid for finding the optimal data sampling point. The Host can use CMD21 tuning command to read the tuning block.

#### 2. PRODUCT SPECIFICATIONS

## 2.1. Typical Power Requirements

Table  $3-iNAND\ 7550\ MCP\ Power\ Consumption\ Sleep\ (Ta=25^{\circ}C@3.3/1.8V)$

|                                    | 64GB | Units |

|------------------------------------|------|-------|

| HS400 Sleep (CMD5 – VCCQ, VCC off) | 150  | uA    |

| HS200 Sleep (CMD5 – VCCQ, VCC off) | 150  | uA    |

Table 4 - iNAND 7550 MCP, Power Consumption Peak (Max) VCC / VCCQ (Ta=25°C@3.3V/1.8V)

|        |                                          | 64GB | Units |

|--------|------------------------------------------|------|-------|

| Activo | Peak [2µs window] VCC                    | 270  | mA    |

| HS400  | Active<br>HS400 Max [1ms window]<br>VCCQ |      | mA    |

| Active | Peak [2µs window] VCC                    | 270  | mA    |

| HS200  | Max [1ms window]<br>VCCQ                 | 340  | mA    |

Table 5 - iNAND 7550 MCP, Power Consumption RMS VCC / VCCQ (Ta=25°C@3.3V/1.8V)

|                         |                                                        |       | 64GB | Units |

|-------------------------|--------------------------------------------------------|-------|------|-------|

|                         | HS400 RMS [100ms window] VCC - RMS [100ms window] VCCQ | Read  | 80   | mA    |

| 110400                  |                                                        | Write | 90   | mA    |

| HS400                   |                                                        | Read  | 245  | mA    |

|                         |                                                        | Write | 160  | mA    |

|                         | RMS [100ms window] VCC                                 | Read  | 80   | mA    |

| 110200                  |                                                        | Write | 90   | mA    |

| RMS [100ms window] VCCQ | Read                                                   | 245   | mA   |       |

|                         | Write                                                  | 160   | mA   |       |

## 2.2. Operating Conditions

### 2.2.1. Operating and Storage Temperature Specifications

Table 6 - Operating and Storage Temperature

| Temperature | Minimum and Maximum Operating*                              | -25° C to 85° C |

|-------------|-------------------------------------------------------------|-----------------|

| Case        | Minimum and Maximum Non-Operating: After soldered onto PCBA | -40° C to 85° C |

<sup>\*</sup> Per eMMC5.1 specification (JESD84-B50): To achieve optimized power/performance, maximum Tcase temperature should not exceed 85°C.

#### 2.2.2. Moisture Sensitivity

The moisture sensitivity level for iNAND 7550 MCP is MSL = 3.

#### 2.3. Reliability

SanDisk iNAND 7550 MCP product meets or exceeds NAND type of products Endurance and Data Retention requirements as per evaluated representative usage models for designed market and relevant sections of JESD47I standard.

Table 7 - Critical Reliability Characteristics

| Reliability<br>Characteristics               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Value                                                                                                                                                                    |

|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Uncorrectable Bit Error Rate (UBER)          | Uncorrectable bit error rate will not exceed one sector in the specified number of bits read. In such rare events data can be lost.                                                                                                                                                                                                                                                                                                                                                                              | 1 sector in 10 <sup>15</sup> bits read                                                                                                                                   |

| Write<br>Endurance<br>Specification<br>(TBW) | Write endurance is commonly classified in Total Terabytes Written (TBW) to a device. This is the total amount of data that can be written to the device over its useful life time and depends on workload written at certain operated temperature range.  Representative workload description:  80% Sequential write, 20% Random Write.  Distribution of IO Transaction Sizes:  <16KB: 82% 16KB-128KB: 17% >128KB: 1% Cache On, Packed Off Host data is 4K aligned 30% of product lifetime operate @85° C T-case | Total Terabytes Written [TBW] Per representative Android workload: 64GB: 80[TB]                                                                                          |

|                                              | • 70% of product lifetime operate @55° C T-case                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                          |

| Data Retention<br>Specification<br>(Years)   | Fresh or Early Life Device  (A device whose total write cycles to the flash is less than 10% of the maximum endurance specification)                                                                                                                                                                                                                                                                                                                                                                             | 10 years of Data Retention<br>@ 25°C & 55°C                                                                                                                              |

|                                              | Cycled Device  (Any device whose total write cycles are between 10% of the maximum write endurance specification and equal to or exceed the maximum write endurance specification)                                                                                                                                                                                                                                                                                                                               | 1 year of Data Retention @ 25°C & 55°C  Note: In the case where the number of writes exceed the endurance spec read and Write performance can be intermediately reduced. |

## 2.4. System Performance

Table 8 – Sequential Performance

|      | HS400            |     |

|------|------------------|-----|

|      | Write Read (MBs) |     |

| 64GB | 230              | 300 |

Table 9 – Random Performance

|      | HS400                    |            |             |  |  |

|------|--------------------------|------------|-------------|--|--|

|      | Write (IOPs) Read (IOPs) |            |             |  |  |

|      | Cache ON                 | CmdQ<br>ON | CmdQ<br>OFF |  |  |

| 64GB | 15K                      | 20K        | 8K          |  |  |

Note 1: Sequential Read/Write performance is measured under HS400 mode with a bus width of 8 bit at 200 MHz DDR mode, chunk size of 512KB, and data transfer of 1GB.

Note 2: Random performance is measured with a chunk size of 4KB and address range of 1GB.

Note 3: All performance is measured using SanDisk proprietary test environment, without file system overhead and host turn-around time (HTAT).

Note 4: Sequential Write performance is measured for 400MB host payloads.

#### 3. PHYSICAL SPECIFICATIONS

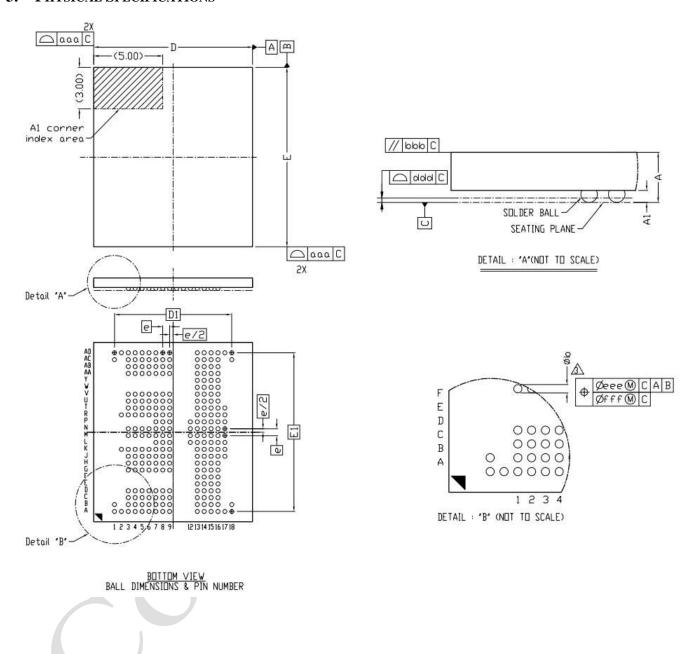

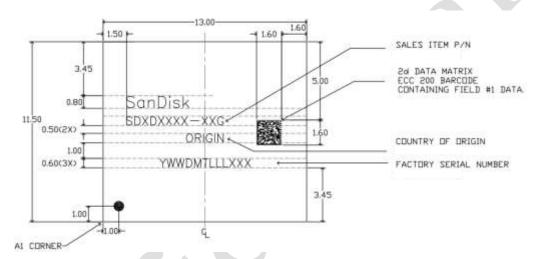

Figure 5- INAND 7550 MCP Package Outline Drawing

Table 10.1 –Package Specification 254-BGA 1.0mm (64+32 configuration)

|        | Dimension in millimeters |         |         |  |  |  |

|--------|--------------------------|---------|---------|--|--|--|

| Symbol | Minimum                  | Nominal | Maximum |  |  |  |

| A      | 0.8                      |         | 1       |  |  |  |

| A1     | 0.17                     | 0.22    | 0.27    |  |  |  |

| D      | 11.4                     | 11.5    | 11.6    |  |  |  |

| Е      | 12.9                     | 13      | 13.1    |  |  |  |

| D1     | -                        | 8.5     | -       |  |  |  |

| E1     | -                        | 11.5    | -       |  |  |  |

| e      | -                        | 0.5     | -       |  |  |  |

| b      | 0.25                     | 0.3     | 0.35    |  |  |  |

| aaa    | 0.1                      |         |         |  |  |  |

| bbb    | 0.1                      |         |         |  |  |  |

| ddd    | 0.08                     |         |         |  |  |  |

| eee    | 0.15                     |         |         |  |  |  |

| fff    |                          | 0.05    |         |  |  |  |

Table 10.2 –Package Specification 254-BGA 1.1mm (64+48 configuration)

|        | T                        |         |         |  |  |

|--------|--------------------------|---------|---------|--|--|

|        | Dimension in millimeters |         |         |  |  |

| Symbol | Minimum                  | Nominal | Maximum |  |  |

| A      | 0.9                      |         | 1.1     |  |  |

| A1     | 0.17                     | 0.22    | 0.27    |  |  |

| D      | 11.4                     | 11.5    | 11.6    |  |  |

| Е      | 12.9                     | 13      | 13.1    |  |  |

| D1     | -                        | 8.5     | -       |  |  |

| E1     | -                        | 11.5    | -       |  |  |

| e      | -                        | 0.5     | -       |  |  |

| b      | 0.25                     | 0.3     | 0.35    |  |  |

| aaa    | 0.1                      |         |         |  |  |

| bbb    | 0.1                      |         |         |  |  |

| ddd    | 0.08                     |         |         |  |  |

| eee    | 0.15                     |         |         |  |  |

| fff    |                          | 0.05    |         |  |  |

#### 4. INTERFACE DESCRIPTION

#### 4.1. MMC I/F Ball Array

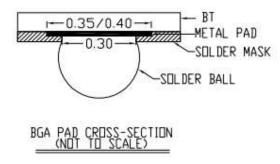

Figure 6 - LPDDR4, 11.5x13mm, 0.5mm pitch, 254ball, 2 channel x32 MCP (top view)

| Symbol            | Туре      | Description                                                                   |  |

|-------------------|-----------|-------------------------------------------------------------------------------|--|

| CK_t_A, CK_c_A    | Input     | Clock: CK_t and CK_c are differential clock inputs. All address, command,     |  |

| CK_t_B, CK_c_B    | 1         | and control input signals are sampled on the crossing of the positive edge of |  |

| The second second |           | CK_t and the negative edge of CK_c. AC timings for CA parameters are refer-   |  |

|                   | N .       | enced to CK. Each channel (A & B) has its own clock pair.                     |  |

| CKE_A             | Input     | Clock Enable: CKE HIGH activates and CKE LOW deactivates the internal         |  |

| CKE_B             |           | clock circuits, input buffers, and output drivers. Power-saving modes         |  |

|                   |           | are entered and exited via CKE transitions.                                   |  |

|                   |           | CKE is part of the command code. Each channel (A & B) has its own CKE sig-    |  |

| 1 1               | _         | nal.                                                                          |  |

| CS_A              | Input     | Chip Select: CS is part of the command code. Each channel (A & B)             |  |

| CS_B              | 63        | has its own CS signal.                                                        |  |

| CA[5:0]_A,        | Input     | Command/Address Inputs: Provide the Command and Address in-                   |  |

| CA[5:0]_B         |           | puts according to the Command Truth Table. Each channel (A&B) has             |  |

| ene const         |           | its own CA signals.                                                           |  |

| ODT_CA_A          | Input     | CA ODT Control: The ODT_CA pin is ignored by LPDDR4X devices.                 |  |

| ODT_CA_B          | 300       | ODT-CS/CA/CK function is fully controlled through MR11 and MR22.              |  |

|                   |           | The ODT_CA pin shall be connected to either VDD2 and VSS.                     |  |

| DQ[15:0]_A,       | I/O       | Data Input/Output: Bi-direction data bus.                                     |  |

| DQ[15:0]_B        |           |                                                                               |  |

| DQS[1:0]_t_A,     | I/O       | Read Strobe: DQS_t and DQS_c are bi-directional differential output           |  |

| DQS[1:0]_c_A,     | 94        | clock signals used to strobe data during a READ or WRITE. The Data            |  |

| DQS[1:0]_t_B,     |           | Strobe is generated by the DRAM for a READ and is edge-aligned with           |  |

| DQS[1:0]_c_B      |           | Data. The Data Strobe is generated by the Memory Controller for a             |  |

|                   |           | WRITE and is center aligned with Data. Each byte of data has a Data           |  |

|                   |           | Strobe signal pair.                                                           |  |

|                   |           | Each channel (A & B) has its own DQS strobes.                                 |  |

| DMI[1:0]_A,       | I/O       | Data Mask Inversion: DMI is a bi-directional signal which is driven           |  |

| DMI[1:0]_B        |           | HIGH when the data on the data bus is inverted, or driven LOW when            |  |

| 11 (2) 1 (2)      |           | the data is in its normal state. Data Inversion can be disabled via a         |  |

|                   |           | mode register setting. Each byte of data has a DMI signal. Each chan-         |  |

|                   |           | nel (A & B) has its own DMI signals.                                          |  |

| ZQ                | Reference | Calibration Reference: Used to calibrate the output drive strength            |  |

|                   | 1111      | and the termination resistance. There is one ZQ pin per die. The ZQ           |  |

|                   |           | pin shall be connected to VDDQ through a 240- $\Omega$ ± 1% resistor.         |  |

| VDD1, VDD2, VDDQ  | Supply    | Power Supplies: Isolated on the die for improved noise immunity.              |  |

| VSS               | GND       | Ground Reference: Power supply ground reference.                              |  |

| RESET_n           | Input     | RESET: When asserted LOW, the RESET pin resets both channels of               |  |

| 211 245           | 110000    | the die.                                                                      |  |

Table 11 – eMMC iNAND pin assignment

| Ball Signal | Туре   | Description                                                                                |

|-------------|--------|--------------------------------------------------------------------------------------------|

| _           | Турс   | Description                                                                                |

| DAT0        |        |                                                                                            |

| DAT1        |        |                                                                                            |

| DAT2        |        |                                                                                            |

| DAT3        | I/O    | Data I/O: Bidirectional channel used for data transfer                                     |

| DAT4        |        |                                                                                            |

| DAT5        |        |                                                                                            |

| DAT6        |        |                                                                                            |

| DAT7        |        |                                                                                            |

| CMD         | I/O    | Command: A bidirectional channel used for device initialization and command transfers.     |

| QRDY        | О      | An optional pin, disabled by default, toggled by the device when the value of QSR changes. |

| CLK         | Input  | Clock: Each cycle directs a 1-bit transfer on the command and DAT lines                    |

| RST n       | -      | Hardware Reset                                                                             |

| RCLK        | Output | Data Strobe                                                                                |

| VCC         |        |                                                                                            |

| VCC         | Supply | Flash I/O and memory power supply                                                          |

| VCC         |        |                                                                                            |

| VCCQ        |        |                                                                                            |

| VCCO        | Supply |                                                                                            |

| VCCQ        |        | Memory controller core and MMC I/F I/O power supply                                        |

| VCCO        |        |                                                                                            |

| VCCO        |        |                                                                                            |

| VSS         |        |                                                                                            |

| VSS         |        |                                                                                            |

| VSS         | Supply | Flash I/O and memory ground connection                                                     |

| VSS         | Suppry |                                                                                            |

| VSS         |        |                                                                                            |

| VSS         |        |                                                                                            |

| VSSm        | Supply | Flash I/O and memory ground connection (dedicated to eMMC)                                 |

| VSSO        |        |                                                                                            |

| VSSQ        |        |                                                                                            |

| VSSO        | Supply | Memory controller core and MMC I/F ground connection                                       |

| VSSQ        |        |                                                                                            |

| VSSO        |        |                                                                                            |

| VDDi        |        | Internal power node. Connect 0.1uF capacitor from VDDi to ground                           |

| VSF1        |        |                                                                                            |

| VSF2        | MOD    | Vendor Specific Function balls for test/debug.                                             |

| VSF3        | VSF    | VSF balls should be floating and be brought out to test pads.                              |

| VSF4        |        |                                                                                            |

Note: All other pins are not connected [NC] and can be connected to GND or left floating

## 4.2. Registers value

#### 4.2.1. OCR Register

| Parameter   | DSR<br>slice | Description           | Value | Width |

|-------------|--------------|-----------------------|-------|-------|

| Access Mode | [30:29]      | Access mode           | 2h    | 2     |

|             | [23:15]      | VDD: 2.7 - 3.6 range  | 1FFh  | 9     |

|             | [14:8]       | VDD: 2.0 - 2.6 range  | 00h   | 7     |

|             | [7]          | VDD: 1.7 - 1.95 range | 1h    | 1     |

*Note*: Bit 30 is set because the device is High Capacity; bit 31 will be set only when the device is ready.

## 4.2.2. CID Register

| Parameter | DSR<br>slice | Description           | Value                | Widt<br>h |

|-----------|--------------|-----------------------|----------------------|-----------|

| MMC MID   | [127:120]    | Manufacturer ID       | 45h                  | 8         |

| CBX       | [113:112]    | Card BGA              | 01h                  | 2         |

| OID       | [111:104]    | OEM/Application ID    | 00h                  | 8         |

| PNM       | [103:56]     | Product name          | 32GB – DL2032        | 48        |

| PRV       | [55:48]      | Product revision      | 01h                  | 8         |

| PSN       | [47:16]      | Product serial number | Random by Production | 32        |

| MDT       | [15:8]       | Manufacturing date    | month, year          | 8         |

| CRC       | [7:1]        | CRC7 checksum         | CRC7 Generator       | 7         |

Note: Please refer to the definition of the MDT field as defined in eMMC Spec version 5.0.

## 4.2.3. DSR Register

| Parameter | DSR<br>slice | Description | Value | Width |

|-----------|--------------|-------------|-------|-------|

| RSRVD     | [15:8]       | Reserved    | 04h   | 8     |

| RSRVD     | [7:0]        | Reserved    | 04h   | 8     |

*Note*: DSR is not implemented; in case of read, a value of 0x0404 will be returned.

# 4.2.4. CSD Register

| Parameter              | CSD Slice | Description                                      | Value          | Width |

|------------------------|-----------|--------------------------------------------------|----------------|-------|

| CSD_STRUCTURE          | [127:126] | CSD structure                                    | 3h             | 3     |

| SPEC_VERS              | [125:122] | System specification version                     | 4h             | 4     |

| TAAC                   | [119:112] | Data read access-time 1                          | 0Fh            | 8     |

| NSAC                   | [111:104] | Data read access-time 2 in CLK cycles (NSAC*100) | 00h            | 8     |

| TRAN_SPEED             | [103:96]  | Max. bus clock frequency                         | 32h            | 8     |

| CCC                    | [95:84]   | Card command classes                             | 8F5h           | 12    |

| READ_BL_LEN            | [83:80]   | Max. read data block length                      | 9h             | 4     |

| READ_BL_PARTIAL        | [79:79]   | Partial blocks for read allowed                  | 0b             | 1     |

| WRITE_BLK_MISALIG<br>N | [78:78]   | Write block misalignment                         | Ob             | 1     |

| READ_BLK_MISALIGN      | [77:77]   | Read block misalignment                          | 0b             | 1     |

| DSR_IMP                | [76:76]   | DSR implemented                                  | 0b             | 1     |

| *C_SIZE                | [73:62]   | Device size                                      | FFFh           | 12    |

| VDD_R_CURR_MIN         | [61:59]   | Max. read current @ VDD min                      | 7h             | 3     |

| VDD_R_CURR_MAX         | [58:56]   | Max. read current @ VDD max                      | 7h             | 3     |

| VDD_W_CURR_MIN         | [55:53]   | Max. write current @ VDD min                     | 7h             | 3     |

| VDD_W_CURR_MAX         | [52:50]   | Max. write current @ VDD max                     | 7h             | 3     |

| C_SIZE_MULT            | [49:47]   | Device size multiplier                           | 7h             | 3     |

| ERASE_GRP_SIZE         | [46:42]   | Erase group size                                 | 1Fh            | 5     |

| ERASE_GRP_MULT         | [41:37]   | Erase group size multiplier                      | 1Fh            | 5     |

| WP_GRP_SIZE            | [36:32]   | Write protect group size                         | 0Fh            | 5     |

| WP_GRP_ENABLE          | [31:31]   | Write protect group enable                       | 1h             | 1     |

| DEFAULT_ECC            | [30:29]   | Manufacturer default                             | 0h             | 2     |

| R2W_FACTOR             | [28:26]   | Write speed factor                               | 2h             | 3     |

| WRITE_BL_LEN           | [25:22]   | Max. write data block length                     | 9h             | 4     |

| WRITE_BL_PARTIAL       | [21:21]   | Partial blocks for write allowed                 | 0h             | 1     |

| CONTENT_PROT_APP       | [16:16]   | Content protection application                   | 0h             | 1     |

| FILE_FORMAT_GRP        | [15:15]   | File format group                                | 0h             | 1     |

| COPY                   | [14:14]   | Copy flag (OTP)                                  | 1h             | 1     |

| PERM_WRITE_PROTEC T    | [13:13]   | Permanent write protection                       | Oh             | 1     |

| TMP_WRITE_PROTECT      | [12:12]   | Temporary write protection                       | 0h             | 1     |

| FILE_FORMAT            | [11:10]   | File format                                      | 0h             | 2     |

| ECC                    | [9:8]     | ECC code                                         | 0h             | 2     |

| CRC                    | [7:1]     | Calculated CRC                                   | CRC7 Generator | 7     |

# 4.2.5. EXT\_CSD Register

| Parameter                                         | ECSD<br>slice | Description                               | Value      |

|---------------------------------------------------|---------------|-------------------------------------------|------------|

| S_CMD_SET                                         | [504]         | Supported Command Sets                    | 1h         |

| HPI_FEATURES                                      | [503]         | HPI Features                              | 1h         |

| BKOPS_SUPPORT                                     | [502]         | Background operations support             | 1h         |

| MAX_PACKED_READS                                  | [501]         | Max packed read commands                  | 3Fh        |

| MAX_PACKED_WRITES                                 | [500]         | Max packed write commands                 | 3Fh        |

| DATA_TAG_SUPPORT                                  | [499]         | Data Tag Support                          | 1h         |

| TAG_UNIT_SIZE                                     | [498]         | Tag Unit Size                             | 3h         |

| TAG_RES_SIZE                                      | [497]         | Tag Resources Size                        | 3h         |

| CONTEXT_CAPABILITIES                              | [496]         | Context management capabilities           | 5h         |

| LARGE_UNIT_SIZE_M1                                | [495]         | Large Unit size                           | 0h         |

| EXT_SUPPORT                                       | [494]         | Extended partitions attribute support     | 3h         |

| SUPPORTED_MODES                                   | [493]         | FFU supported modes                       | 3h         |

| FFU_FEATURES                                      | [492]         | FFU features                              | 0h         |

| OPERATION_CODES_TIME<br>OUT                       | [491]         | Operation codes timeout                   | 10h        |

| FFU_ARG                                           | [490:487]     | FFU Argument                              | 0h         |

| BARRIER_SUPPORT                                   | [486]         | Cache barrier support                     | 1h         |

| CMDQ_SUPPORT                                      | [308]         | Command queue support                     | 1h         |

| CMDQ_DEPTH                                        | [307]         | Command queue depth                       | 1Fh        |

| NUMBER_OF_FW_SECTOR<br>S_CORRECTLY_PROGRAM<br>MED | [305:302]     | Number of FW sectors correctly programmed | Oh         |

| VENDOR_PROPRIETARY_<br>HEALTH_REPORT              | [301:270]     | Vendor proprietary health report          | Oh         |

| DEVICE_LIFE_TIME_EST_T<br>YP_B                    | [269]         | Device life time estimation type B (MLC)  | Oh         |

| DEVICE_LIFE_TIME_EST_T<br>YP_A                    | [268]         | Device life time estimation type A (SLC)  | Oh         |

| PRE_EOL_INFO                                      | [267]         | Pre EOL information                       | 0h         |

| OPTIMAL_READ_SIZE                                 | [266]         | Optimal read size                         | 8h         |

| OPTIMAL_WRITE_SIZE                                | [265]         | Optimal write size                        | 8h         |

| OPTIMAL_TRIM_UNIT_SIZ<br>E                        | [264]         | Optimal trim unit size                    | 8h         |

| DEVICE_VERSION                                    | [263:262]     | Device version                            | 5051h      |

| FIRMWARE_VERSION                                  | [261:254]     | Firmware version                          | FW Version |

| PWR_CL_DDR_200_360                                | [253]         | Power class for 200MHz, DDR at VCC= 3.6V  | 0h         |

| CACHE_SIZE                                        | [252:249]     | Cache size                                | 0h         |

| Parameter                              | ECSD<br>slice | Description                                             | Value                               |

|----------------------------------------|---------------|---------------------------------------------------------|-------------------------------------|

| GENERIC_CMD6_TIME                      | [248]         | Generic CMD6 timeout                                    | 19h                                 |

| POWER_OFF_LONG_TIME                    | [247]         | Power off notification(long) timeout                    | 19h                                 |

| BKOPS_STATUS                           | [246]         | Background operations status                            | Default = 0h                        |

| CORRECTLY_PRG_SECTO<br>RS_NUM          | [245:242]     | Number of correctly programmed sectors                  | Default = 0h                        |

| INI_TIMEOUT_AP                         | [241]         | 1st Initialization time after partitioning              | FFh                                 |

| CACHE_FLUSH_POLICY                     | [240]         | Cache Flush Policy                                      | 1h                                  |

| PWR_CL_DDR_52_360                      | [239]         | Power class for 52MHz, DDR at VCC = 3.6V                | 0h                                  |

| PWR_CL_DDR_52_195                      | [238]         | Power class for 52MHz, DDR at VCC = 1.95V               | 0h                                  |

| PWR_CL_200_195                         | [237]         | Power class for 200MHz at VCCQ =1.95V, VCC = 3.6V       | Oh                                  |

| PWR_CL_200_130                         | [236]         | Power class for 200MHz, at VCCQ =1.3V, VCC = 3.6V       | Oh                                  |

| MIN_PERF_DDR_W_8_52                    | [235]         | Minimum Write Performance for 8bit at 52MHz in DDR mode | Oh                                  |

| MIN_PERF_DDR_R_8_52                    | [234]         | Minimum Read Performance for 8bit at 52MHz in DDR mode  | Oh                                  |

| TRIM _MULT                             | [232]         | TRIM Multiplier                                         | 3h                                  |

| SEC_FEATURE_SUPPORT                    | [231]         | Secure Feature support                                  | 55h                                 |

| SEC_ERASE_MULT                         | [230]         | Secure Erase Multiplier                                 | A6h                                 |

| SEC_TRIM_MULT                          | [229]         | Secure TRIM Multiplier                                  | A6h                                 |

| BOOT_INFO                              | [228]         | Boot Information                                        | 7h                                  |

| BOOT_SIZE_MULT                         | [226]         | Boot partition size                                     | 20h                                 |

| ACCESS_SIZE                            | [225]         | Access size                                             | 8h                                  |

| HC_ERASE_GROUP_SIZE                    | [224]         | High Capacity Erase unit size                           | 1h (see WP group size table below)  |

| ERASE_TIMEOUT_MULT                     | [223]         | High capacity erase time out                            | 3h                                  |

| REL_WR_SEC_C                           | [222]         | Reliable write sector count                             | 1h                                  |

| HC_WP_GRP_SIZE                         | [221]         | High capacity write protect group size                  | 10h (see WP group size table below) |

| S_C_VCC                                | [220]         | Sleep current [VCC]                                     | 64GB: 8h                            |

| S_C_VCCQ                               | [219]         | Sleep current [VCCQ]                                    | 7h                                  |

| PRODUCTION_STATE_AW<br>ARENESS_TIMEOUT | [218]         | Production state awareness timeout                      | 17h                                 |

| S_A_TIMEOUT                            | [217]         | Sleep/Awake time out                                    | 13h                                 |

| SLEEP_NOTIFICATION_TI<br>ME            | [216]         | Sleep notification timeout                              | 17h                                 |

| Parameter                  | ECSD slice | Description                                              | Value                                                   |

|----------------------------|------------|----------------------------------------------------------|---------------------------------------------------------|

| SEC_COUNT                  | [215:212]  | Sector count                                             | See exported capacity table below                       |

| SECURE_WP_INFO             | [211]      | Secure Write Protect Info                                | 1h                                                      |

| MIN_PERF_W_8_52            | [210]      | Minimum Write Performance for 8bit @52MHz                | Ah                                                      |

| MIN_PERF_R_8_52            | [209]      | Minimum Read Performance for 8bit @52MHz                 | Ah                                                      |

| MIN_PERF_W_8_26_4_52       | [208]      | Minimum Write Performance for 4bit @52MHz or 8bit @26MHz | Ah                                                      |

| MIN_PERF_R_8_26_4_52       | [207]      | Minimum Read Performance for 4bit @52MHz or 8bit @26MHz  | Ah                                                      |

| MIN_PERF_W_4_26            | [206]      | Minimum Write Performance for 4bit @26MHz                | Ah                                                      |

| MIN_PERF_R_4_26            | [205]      | Minimum Read Performance for 4bit @26MHz                 | Ah                                                      |

| PWR_CL_26_360              | [203]      | Power Class for 26MHz @ 3.6V                             | 0h                                                      |

| PWR_CL_52_360              | [202]      | Power Class for 52MHz @ 3.6V                             | 0h                                                      |

| PWR_CL_26_195              | [201]      | Power Class for 26MHz @ 1.95V                            | 0h                                                      |

| PWR_CL_52_195              | [200]      | Power Class for 52MHz @ 1.95V                            | 0h                                                      |

| PARTITION_SWITCH_TIME      | [199]      | Partition switching timing                               | 3h                                                      |

| OUT_OF_INTERRUPT_TIM<br>E  | [198]      | Out-of-interrupt busy timing                             | Ah                                                      |

| DRIVER_STRENGTH            | [197]      | I/O Driver Strength                                      | 1Fh (Reporting four strengths, but supporting only one) |

| CARD_TYPE                  | [196:195]  | Card Type                                                | 57h                                                     |

| CSD_STRUCTURE              | [194]      | CSD Structure Version                                    | 2h                                                      |

| EXT_CSD_REV                | [192]      | Extended CSD Revision                                    | 8h                                                      |

| CMD_SET                    | [191]      | Command Set                                              | Default = 0h<br>Updated in runtime                      |

| CMD_SET_REV                | [189]      | Command Set Revision                                     | 0h                                                      |

| POWER_CLASS                | [187]      | Power Class                                              | Dh                                                      |

| HS_TIMING                  | [185]      | High Speed Interface Timing                              | Default = 0h<br>Updated in runtime by the host          |

| DATA_STRB_MODE_SUPP<br>ORT | [184]      | Data strobe mode support                                 | 1h                                                      |

| BUS_WIDTH                  | [183]      | Bus Width Mode                                           | Default = 0h<br>Updated in runtime by the host          |

| ERASE_MEM_CONT             | [181]      | Content of explicit erased memory range                  | 0h                                                      |

| PARTITION_CONFIG           | [179]      | Partition Configuration                                  | Default = 0h                                            |

|                            |            |                                                          | Updated in runtime by the host                          |

| BOOT_CONFIG_PROT           | [178]      | Boot config protection                                   | Default = 0h Updated in runtime by the host             |

| BOOT_BUS_CONDITIONS        | [177]      | Boot bus width1                                          | Default = 0h                                            |

| Parameter                       | ECSD<br>slice | Description                            | Value                                          |

|---------------------------------|---------------|----------------------------------------|------------------------------------------------|

|                                 |               |                                        | Updated in runtime by the host                 |

| ERASE_GROUP_DEF                 | [175]         | High-density erase group definition    | Default = 0h<br>Updated in runtime by the host |

| BOOT_WP_STATUS                  | [174]         | Boot write protection status registers | Default = 0h Updated in runtime                |

| BOOT_WP                         | [173]         | Boot area write protect register       | 0h                                             |

| USER_WP                         | [171]         | User area write protect register       | 0h                                             |

| FW_CONFIG                       | [169]         | FW Configuration                       | 0h                                             |

| RPMB_SIZE_MULT                  | [168]         | RPMB Size                              | 80h                                            |

| WR_REL_SET                      | [167]         | Write reliability setting register     | 1Fh                                            |

| WR_REL_PARAM                    | [166]         | Write reliability parameter register   | 15h                                            |

| SANITIZE_START                  | [165]         | Start Sanitize operation               | Default = 0h<br>Updated in runtime by the host |

| BKOPS_START                     | [164]         | Manually start background operations   | Default = 0h<br>Updated in runtime by the host |

| BKOPS_EN                        | [163]         | Enable background operations handshake | 2h                                             |

| RST_n_FUNCTION                  | [162]         | H/W reset function                     | Default = 0h<br>Updated by the host            |

| HPI_MGMT                        | [161]         | HPI management                         | Default = 0h<br>Updated by the host            |

| PARTITIONING SUPPORT            | [160]         | Partitioning support                   | 7h<br>Note: EUDA is not supported              |

| MAX_ENH_SIZE_MULT               | [159:157]     | Max Enhanced Area Size                 | 0h                                             |

| PARTITIONS_ATTRIBUTE            | [156]         | Partitions Attribute                   | Default = 0h<br>Updated by the host            |

| PARTITION_SETTING_<br>COMPLETED | [155]         | Partitioning Setting                   | Default = 0h<br>Updated by the host            |

| GP_SIZE_MULT                    | [154:143]     | General Purpose Partition Size (GP4)   | 0h                                             |

| GP_SIZE_MULT                    | [151:149]     | General Purpose Partition Size (GP3)   | 0h                                             |

| GP_SIZE_MULT                    | [148:146]     | General Purpose Partition Size (GP2)   | 0h                                             |

| GP_SIZE_MULT                    | [145:143]     | General Purpose Partition Size (GP1)   | 0h                                             |

| ENH_SIZE_MULT                   | [142:140]     | Enhanced User Data Area Size           | 0h                                             |

| ENH_START_ADDR                  | [139:136]     | Enhanced User Data Start Address       | 0h                                             |

| SEC_BAD_BLK_MGMNT               | [134]         | Bad Block Management mode              | 0h                                             |

| PRODUCTION_STATE_AW ARENESS     | [133]         | Production state awareness             | Oh                                             |

| TCASE_SUPPORT                   | [132]         | Package Case Temperature is controlled | 0h                                             |

| PERIODIC_WAKEUP                 | [131]         | Periodic Wake-up                       | Oh                                             |

| Parameter                           | ECSD slice | Description                                              | Value                                       |

|-------------------------------------|------------|----------------------------------------------------------|---------------------------------------------|

| PROGRAM_CID_CSD_DDR<br>_SUPPORT     | [130]      | Program CID/CSD in DDR mode support                      | Oh                                          |

| VENDOR_SPECIFIC_FIELD               | [127:64]   | Vendor Specific Fields                                   | Reserved                                    |

| NATIVE_SECTOR_SIZE                  | [63]       | Native sector size                                       | 0h                                          |

| USE_NATIVE_SECTOR                   | [62]       | Sector size emulation                                    | 0h                                          |

| DATA_SECTOR_SIZE                    | [61]       | Sector size                                              | 0h                                          |

| INI_TIMEOUT_EMU                     | [60]       | 1st initialization after disabling sector size emulation | Ah                                          |

| CLASS_6_CTRL                        | [59]       | Class 6 commands control                                 | 0h                                          |