# RX64M Group, RX71M Group Flash Memory

User's Manual: Hardware Interface

RENESAS 32-Bit MCU RX Family / RX600 Series, RX700 Series

All information contained in these materials, including products and product specifications, represents information on the product at the time of publication and is subject to change by Renesas Electronics Corp. without notice. Please review the latest information published by Renesas Electronics Corp. through various means, including the Renesas Electronics Corp. website (http://www.renesas.com).

Renesas Electronics www.renesas.com

User's Manual

#### Notice

- 1. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 2. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 3. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 4. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from such alteration, modification, copy or otherwise misappropriation of Renesas Electronics product.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below.

"Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; and safety equipment etc.

Renesas Electronics products are neither intended nor authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems, surgical implantations etc.), or may cause serious property damages (nuclear reactor control systems, military equipment etc.). You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for which it is not intended. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for which the product is not intended by Renesas Electronics.

- 6. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 9. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You should not use Renesas Electronics products or technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. When exporting the Renesas Electronics products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the contents and conditions set forth in this document, Renesas Electronics assumes no responsibility for any losses incurred by you or third parties as a result of unauthorized use of Renesas Electronics products.

- 11. This document may not be reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

## General Precautions in the Handling of MPU/MCU Products

The following usage notes are applicable to all MPU/MCU products from Renesas. For detailed usage notes on the products covered by this document, refer to the relevant sections of the document as well as any technical updates that have been issued for the products.

1. Handling of Unused Pins

Handle unused pins in accordance with the directions given under Handling of Unused Pins in the manual.

— The input pins of CMOS products are generally in the high-impedance state. In operation with an unused pin in the open-circuit state, extra electromagnetic noise is induced in the vicinity of LSI, an associated shoot-through current flows internally, and malfunctions occur due to the false recognition of the pin state as an input signal become possible. Unused pins should be handled as described under Handling of Unused Pins in the manual.

2. Processing at Power-on

The state of the product is undefined at the moment when power is supplied.

The states of internal circuits in the LSI are indeterminate and the states of register settings and pins are undefined at the moment when power is supplied.

In a finished product where the reset signal is applied to the external reset pin, the states of pins are not guaranteed from the moment when power is supplied until the reset process is completed.

In a similar way, the states of pins in a product that is reset by an on-chip power-on reset function are not guaranteed from the moment when power is supplied until the power reaches the level at which resetting has been specified.

3. Prohibition of Access to Reserved Addresses

Access to reserved addresses is prohibited.

- The reserved addresses are provided for the possible future expansion of functions. Do not access

these addresses; the correct operation of LSI is not guaranteed if they are accessed.

- 4. Clock Signals

After applying a reset, only release the reset line after the operating clock signal has become stable. When switching the clock signal during program execution, wait until the target clock signal has stabilized.

When the clock signal is generated with an external resonator (or from an external oscillator) during a reset, ensure that the reset line is only released after full stabilization of the clock signal. Moreover, when switching to a clock signal produced with an external resonator (or by an external oscillator) while program execution is in progress, wait until the target clock signal is stable.

5. Differences between Products

Before changing from one product to another, i.e. to a product with a different part number, confirm that the change will not lead to problems.

— The characteristics of an MPU or MCU in the same group but having a different part number may differ in terms of the internal memory capacity, layout pattern, and other factors, which can affect the ranges of electrical characteristics, such as characteristic values, operating margins, immunity to noise, and amount of radiated noise. When changing to a product with a different part number, implement a system-evaluation test for the given product.

## Contents

| 1. | Featu  | res                                                              | 6  |

|----|--------|------------------------------------------------------------------|----|

| 2. | Modu   | le Configuration                                                 | 7  |

| 3. | Addre  | ess Space                                                        | 8  |

| 4. | Regis  | ters                                                             | 9  |

|    | 4.1    | Flash P/E Protect Register (FWEPROR)                             | 10 |

|    | 4.2    | Flash Access Status Register (FASTAT)                            | 11 |

|    | 4.3    | Flash Access Error Interrupt Enable Register (FAEINT)            | 13 |

|    | 4.4    | Flash Ready Interrupt Enable Register (FRDYIE)                   | 14 |

|    | 4.5    | FACI Command Start Address Register (FSADDR)                     | 15 |

|    | 4.6    | FACI Command End Address Register (FEADDR)                       | 16 |

|    | 4.7    | FCURAM Enable Register (FCURAME)                                 | 17 |

|    | 4.8    | Flash Status Register (FSTATR)                                   | 18 |

|    | 4.9    | Flash P/E Mode Entry Register (FENTRYR)                          | 22 |

|    | 4.10   | Flash Protection Register (FPROTR)                               | 23 |

|    | 4.11   | Flash Sequencer Set-Up Initialization Register (FSUINITR)        | 24 |

|    | 4.12   | Lock Bit Status Register (FLKSTAT)                               | 25 |

|    | 4.13   | FACI Command Register (FCMDR)                                    | 26 |

|    | 4.14   | Flash P/E Status Register (FPESTAT)                              | 27 |

|    | 4.15   | Data Flash Blank Check Control Register (FBCCNT)                 | 27 |

|    | 4.16   | Data Flash Blank Check Status Register (FBCSTAT)                 | 28 |

|    | 4.17   | Data Flash Programming Start Address Register (FPSADDR)          |    |

|    | 4.18   | Flash Sequencer Processing Switching Register (FCPSR)            | 29 |

|    | 4.19   | Flash Sequencer Processing Clock Notification Register (FPCKAR)  | 30 |

| 5. | Opera  | ating Modes of the Flash Sequencer                               | 31 |

| 6. | FACI   | Commands                                                         | 32 |

|    | 6.1    | List of FACI Commands                                            | 32 |

|    | 6.2    | Relationship between the Flash Sequencer State and FACI Commands | 33 |

|    | 6.3    | Usage of FACI Commands                                           | 35 |

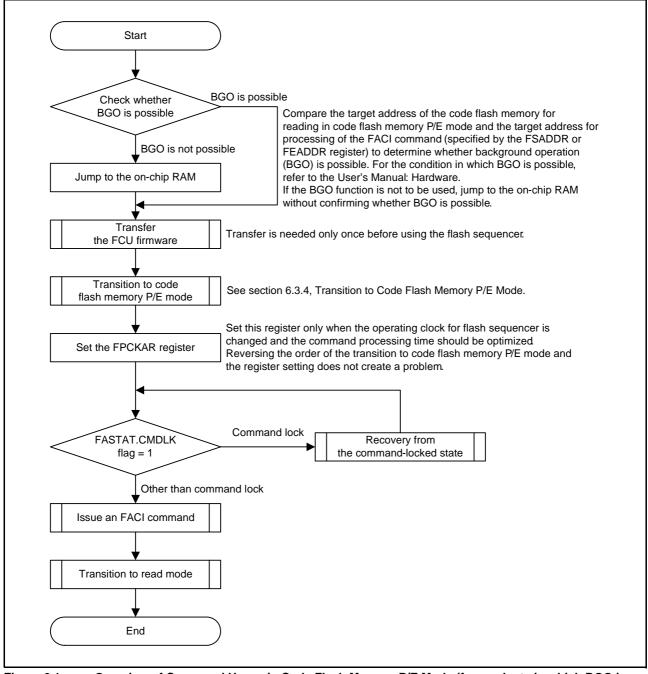

|    | 6.3.1  | Overview of Command Usage in Code Flash memory P/E Mode          | 35 |

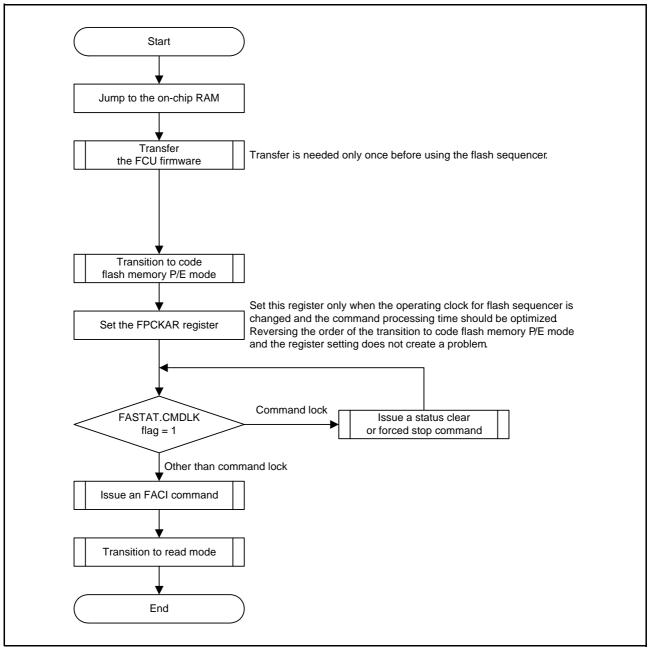

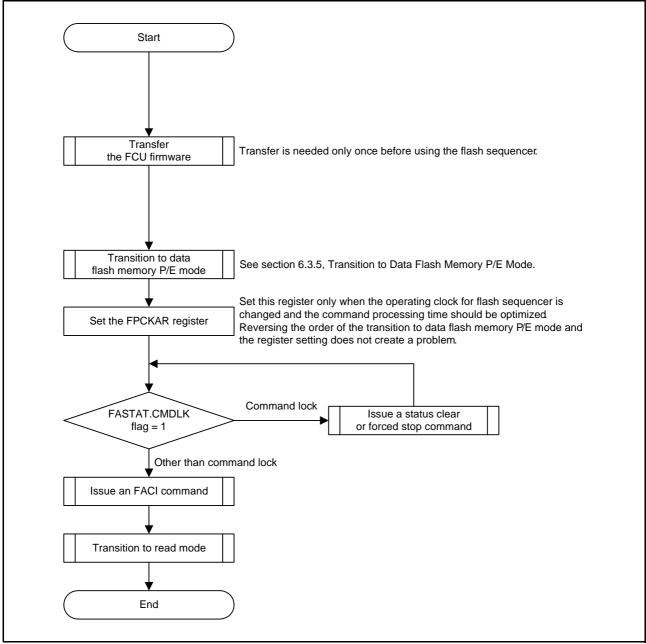

|    | 6.3.2  | Overview of Command Usage in Data Flash Memory P/E Mode          | 37 |

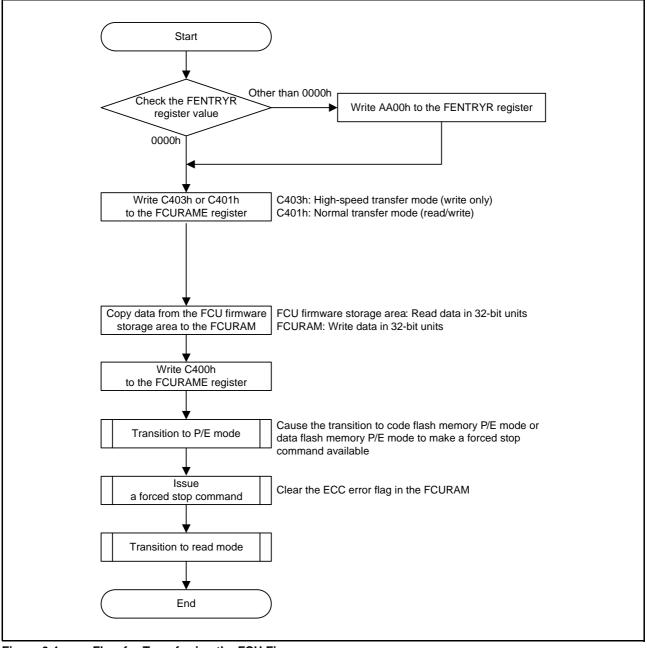

|    | 6.3.3  | Transferring the FCU Firmware                                    | 38 |

|    | 6.3.4  | Transition to Code Flash Memory P/E Mode                         | 39 |

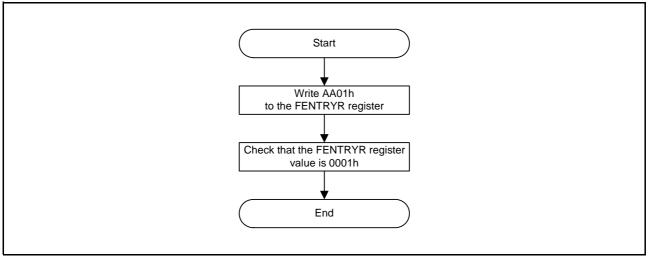

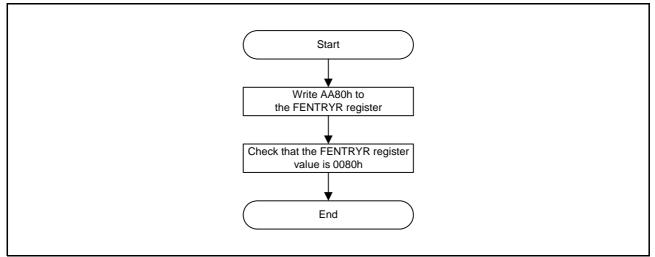

|    | 6.3.5  | Transition to Data Flash Memory P/E Mode                         | 39 |

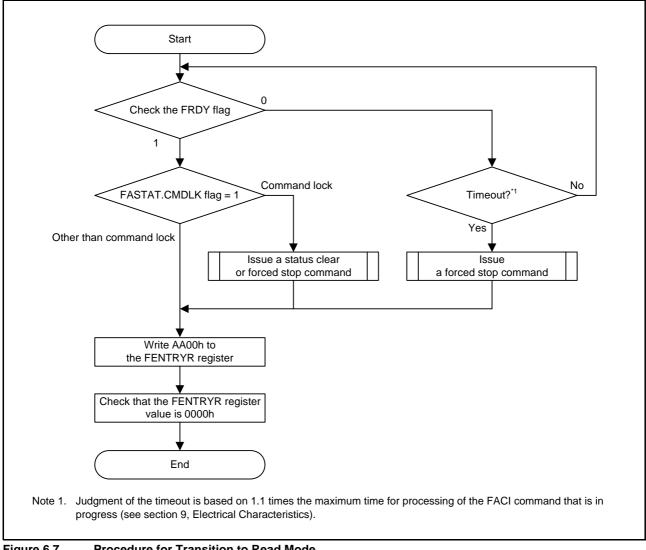

|    | 6.3.6  | Transition to Read Mode                                          | 40 |

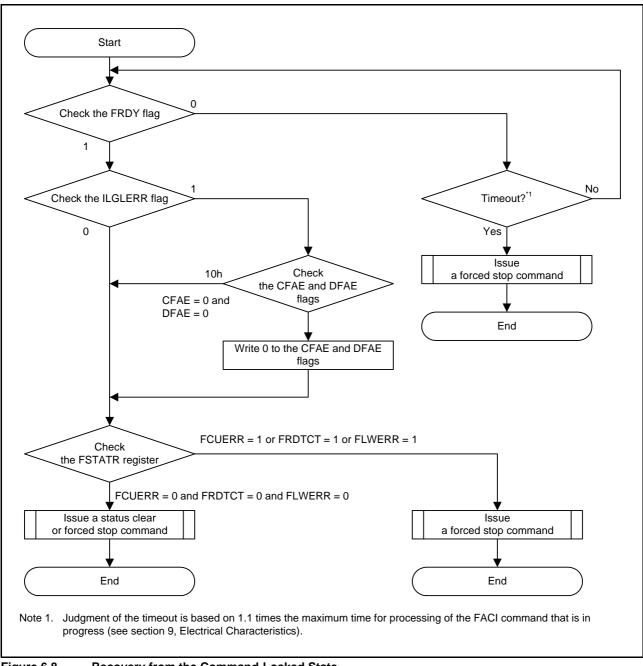

|    | 6.3.7  | Recovery from the Command-Locked State                           | 41 |

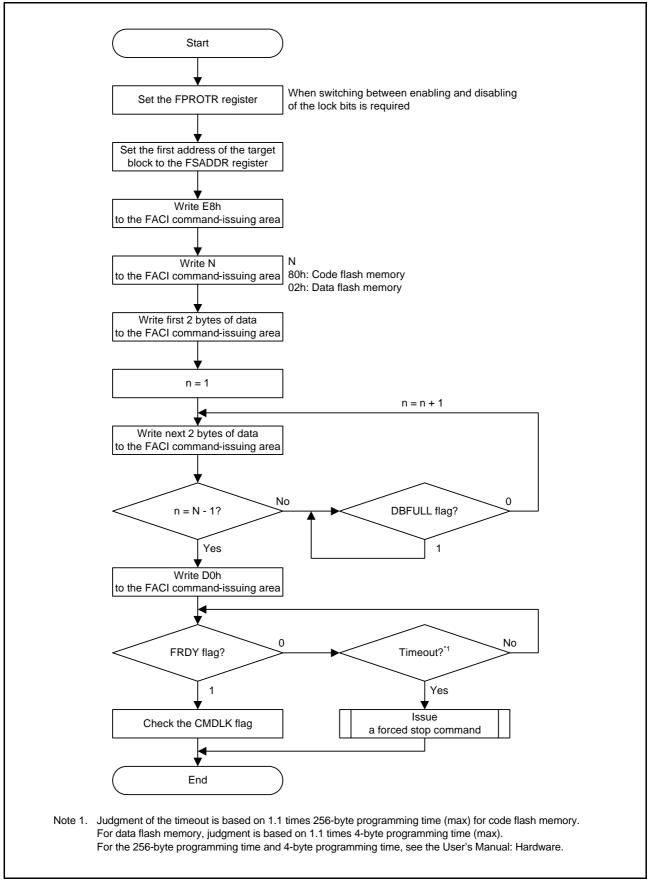

|    | 6.3.8  | Programming Command                                              | 43 |

|    | 6.3.9  | Block Erase Command                                              | 45 |

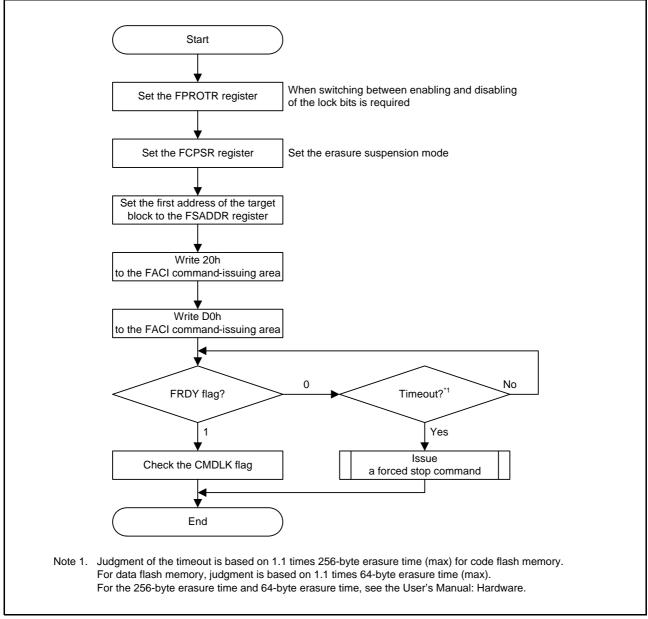

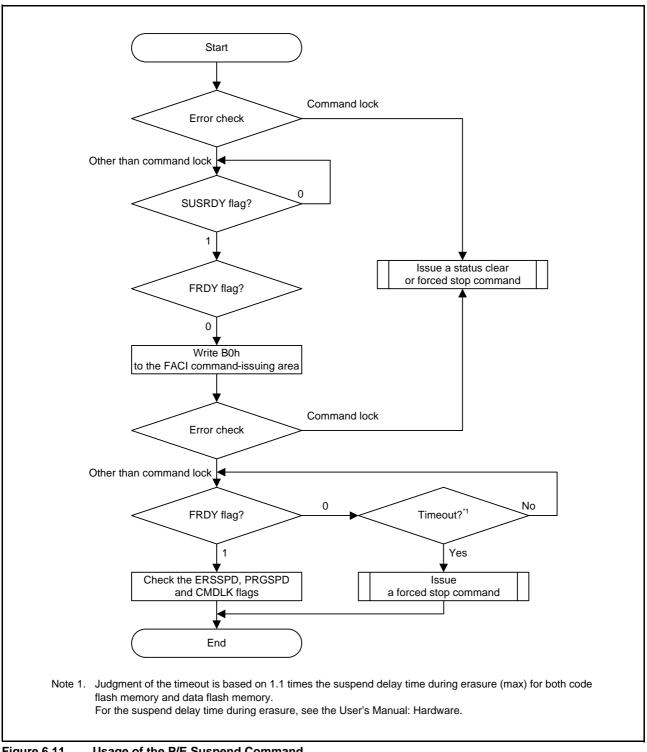

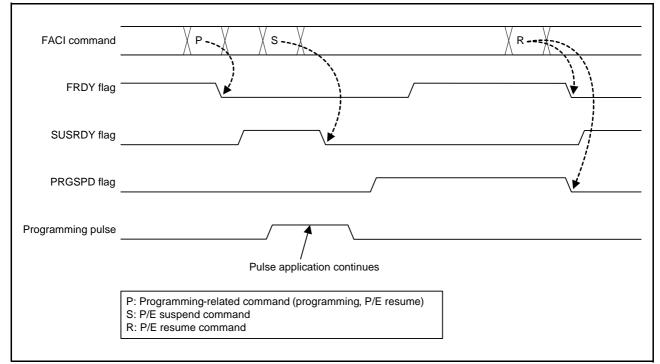

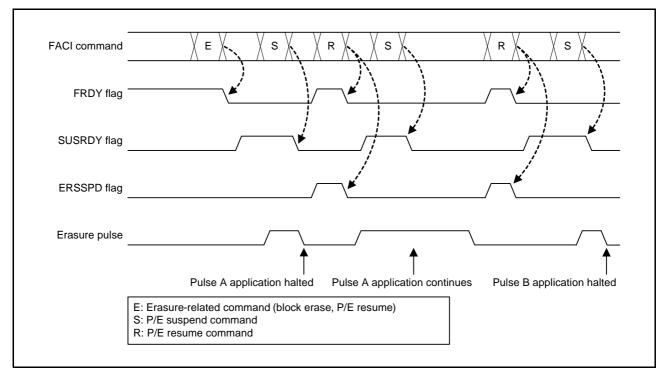

|    | 6.3.10 | P/E Suspend Command                                              | 46 |

|    | 6.3.1  | P/E Resume Command                                               | 51 |

|    | 6.3.12 | 2 Status Clear Command                                           | 51 |

|    | 6.3.13 | 3 Forced Stop Command                                            | 52 |

|    |        |                                                                  |    |

|    | 6.3.14   | 4 Blank Check Command          |    |

|----|----------|--------------------------------|----|

|    | 6.3.1    | 5 Configuration Set Command    | 55 |

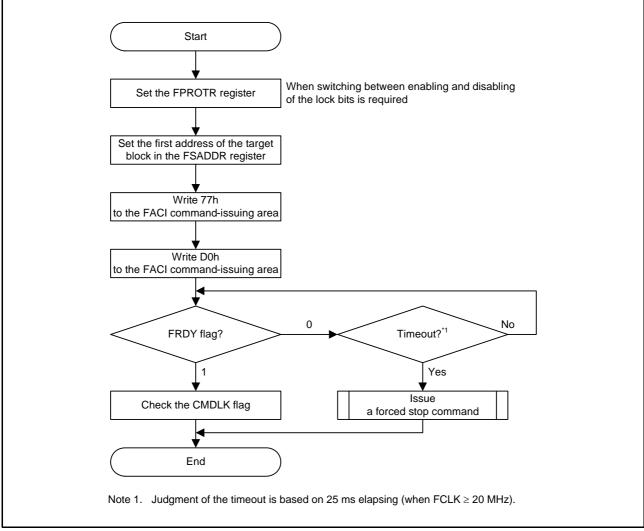

|    | 6.3.1    | 6 Lock-Bit Programming Command |    |

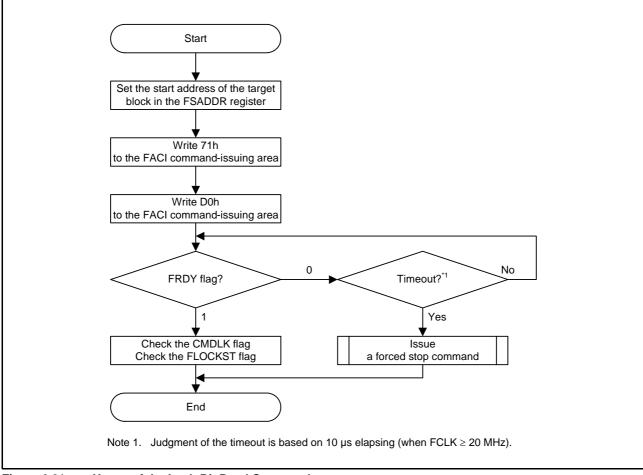

|    | 6.3.1    | 7 Lock-Bit Read Command        |    |

| 7. | Safet    | y Function                     | 59 |

|    | 7.1      | Software Protection            | 59 |

|    | 7.1.1    | Protection through FWEPROR     |    |

|    | 7.1.2    | Protection through FENTRYR     |    |

|    | 7.1.3    | Protection through Lock Bit    |    |

|    | 7.2      | Error Protection               | 59 |

|    | 7.3      | Boot Program Protection        | 61 |

|    | 7.3.1    | User Boot Protection           | 61 |

| 8. | Usage    | e Notes                        | 62 |

| 9. | Electr   | ical Characteristics           | 63 |

|    | 9.1      | AC Characteristics             | 63 |

| RE | VISION I | HISTORY                        | 64 |

## RENESAS

## RX64M Group, RX71M Group Flash Memory

User's Manual: Hardware Interface

## 1. Features

The features of the flash memory are described below. See the User's Manual: Hardware for information on the capacity, block configuration, and addresses of the flash memory in this MCU.

#### Programming/Erasure

A dedicated sequencer for the flash memory (flash sequencer) executes programming and erasure via internal peripheral bus 6. The flash sequencer also supports the suspension or resumption of programming or erasure, and background operations (BGO).

#### **Security Functions**

The flash memory incorporates hardware functions to prevent illicit tampering with or reading out of data in flash memory.

#### **Protection Functions**

The flash memory incorporates hardware functions to prevent erroneous programming.

#### Interrupts

The flash memory supports an interrupt to indicate completion of processing by the flash sequencer and an error interrupt to indicate operations that were in error.

## 2. Module Configuration

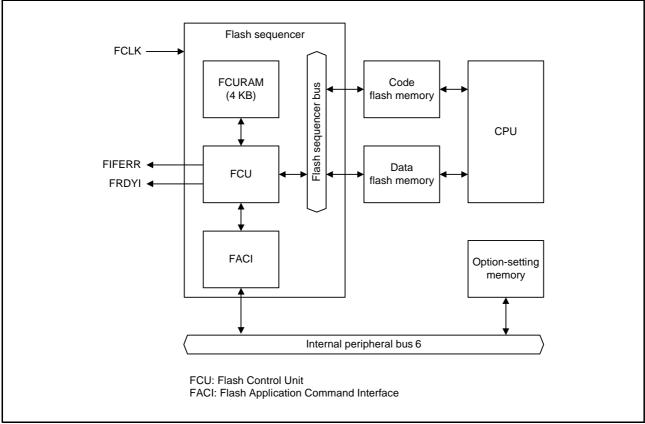

Modules related to the flash memory are configured as shown in Figure 2.1. The flash sequencer is configured of the Flash Control Unit (FCU) and Flash Application Command Interface (FACI). The FCU executes basic control of overwriting of the flash memory. The FCURAM is RAM for the storage of firmware to control execution by the FCU. The FACI receives FACI commands via internal peripheral bus 6 and controls FCU operations accordingly.

In response to a reset, the FACI transfers data from the flash memory to the option-setting memory.

Figure 2.1 Configuration of Flash Memory Related Modules

## 3. Address Space

Using the hardware interface with the flash memory requires accessing to the area containing registers of the hardware, that for the issuing of FACI commands, that for storage of the FCU firmware, and that for the FCURAM. Table 3.1 gives information on all of these areas.

| Table 3.1 | Information on the Hardware Interface Area |

|-----------|--------------------------------------------|

|-----------|--------------------------------------------|

| Area                                                  | Address                   | Capacity                  |

|-------------------------------------------------------|---------------------------|---------------------------|

| Area containing the various registers of the hardware | See section 4, Registers. | See section 4, Registers. |

| FACI command-issuing area                             | 007E 0000h                | 4 bytes                   |

| FCU firmware storage area                             | FEFF F000h to FEFF FFFFh  | 4 Kbytes                  |

| FCURAM area                                           | 007F 8000h to 007F 8FFFh  | 4 Kbytes                  |

| Configuration setting area                            | 0012 0040h to 0012 007Fh  | 64 bytes                  |

Refer to the User's Manual: Hardware for information on the addresses of the flash memory.

This section gives information on registers to which access is required when using the hardware interface of the flash memory. Reset registers that are not specifically mentioned to their initial states.

For information on the option-setting memory, see the User's Manual: Hardware for the product you are using.

| Table 4.1 | List of Registers |

|-----------|-------------------|

|-----------|-------------------|

|            |                  |                                                        |                    |                   |                | Number of A         |                      |                   |

|------------|------------------|--------------------------------------------------------|--------------------|-------------------|----------------|---------------------|----------------------|-------------------|

| Address    | Module<br>Symbol | Register Name                                          | Register<br>Symbol | Number<br>of Bits | Access<br>Size | ICLK≥<br>PCLKB/FCLK | ICLK <<br>PCLKB/FCLK | Reference<br>Page |

| 0008 C296h | FLASH            | Flash P/E Protect Register                             | FWEPROR            | 8                 | 8              | 4 to 5 PCLKB        | 2 to 3 ICLK          | 10                |

| 007F E010h | FLASH            | Flash Access Status Register                           | FASTAT             | 8                 | 8              | 2 to 4 FCLK         | 2 to 3 ICLK          | 11                |

| 007F E014h | FLASH            | Flash Access Error Interrupt Enable Register           | FAEINT             | 8                 | 8              | 2 to 4 FCLK         | 2 to 3 ICLK          | 13                |

| 007F E018h | FLASH            | Flash Ready Interrupt Enable Register                  | FRDYIE             | 8                 | 8              | 2 to 4 FCLK         | 2 to 3 ICLK          | 14                |

| 007F E030h | FLASH            | FACI Command Start Address Register                    | FSADDR             | 32                | 32             | 2 to 4 FCLK         | 2 to 3 ICLK          | 15                |

| 007F E034h | FLASH            | FACI Command End Address Register                      | FEADDR             | 32                | 32             | 2 to 4 FCLK         | 2 to 3 ICLK          | 16                |

| 007F E054h | FLASH            | FCURAM Enable Register                                 | FCURAME            | 16                | 16             | 2 to 4 FCLK         | 2 to 3 ICLK          | 17                |

| 007F E080h | FLASH            | Flash Status Register                                  | FSTATR             | 32                | 32             | 2 to 4 FCLK         | 2 to 3 ICLK          | 18                |

| 007F E084h | FLASH            | Flash P/E Mode Entry Register                          | FENTRYR            | 16                | 16             | 2 to 4 FCLK         | 2 to 3 ICLK          | 22                |

| 007F E088h | FLASH            | Flash Protection Register                              | FPROTR             | 16                | 16             | 2 to 4 FCLK         | 2 to 3 ICLK          | 23                |

| 007F E08Ch | FLASH            | Flash Sequencer Set-Up Initialization Register         | FSUINITR           | 16                | 16             | 2 to 4 FCLK         | 2 to 3 ICLK          | 24                |

| 007F E090h | FLASH            | Lock Bit Status Register                               | FLKSTAT            | 8                 | 8              | 2 to 4 FCLK         | 2 to 3 ICLK          | 25                |

| 007F E0A0h | FLASH            | FACI Command Register                                  | FCMDR              | 16                | 16             | 2 to 4 FCLK         | 2 to 3 ICLK          | 26                |

| 007F E0C0h | FLASH            | Flash P/E Status Register                              | FPESTAT            | 16                | 16             | 2 to 4 FCLK         | 2 to 3 ICLK          | 27                |

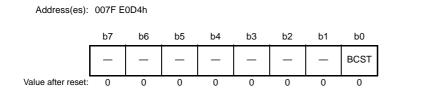

| 007F E0D0h | FLASH            | Data Flash Blank Check Control Register                | FBCCNT             | 8                 | 8              | 2 to 4 FCLK         | 2 to 3 ICLK          | 27                |

| 007F E0D4h | FLASH            | Data Flash Blank Check Status Register                 | FBCSTAT            | 8                 | 8              | 2 to 4 FCLK         | 2 to 3 ICLK          | 28                |

| 007F E0D8h | FLASH            | Data Flash Programming Start Address Register          | FPSADDR            | 32                | 32             | 2 to 4 FCLK         | 2 to 3 ICLK          | 28                |

| 007F E0E0h | FLASH            | Flash Sequencer Processing Switching Register          | FCPSR              | 16                | 16             | 2 to 4 FCLK         | 2 to 3 ICLK          | 29                |

| 007F E0E4h | FLASH            | Flash Sequencer Processing Clock Notification Register | FPCKAR             | 16                | 16             | 2 to 4 FCLK         | 2 to 3 ICLK          | 30                |

## 4.1 Flash P/E Protect Register (FWEPROR)

Reserved

| Address(es)       | : 0008 C | 296h |          |        |         |    |             |                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|-------------------|----------|------|----------|--------|---------|----|-------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|                   | b7       | b6   | b5       | b4     | b3      | b2 | b           | o1 b0                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|                   | _        | _    | —        | -      | —       | _  | I           | FLWE[1:0]                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| Value after reset | : 0      | 0    | 0        | 0      | 0       | 0  |             | 1 0                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|                   |          |      |          |        |         |    |             |                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| Bit               | Symbol   | I E  | Bit Name | e      |         |    | Des         | cription                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                     | R/W |

| b1, b0            | FLWE[1   | -    | Tash Pro | ogramm | ing and |    | ы<br>0<br>0 | flash, or<br>of lock b<br>1: Permits<br>flash, or<br>of lock b<br>0: Prohibits<br>flash, or | s programming and erasure of the code flash, data<br>option-setting memory, programming and erasure<br>its, and blank checking.<br>programming and erasure of the code flash, data<br>option-setting memory, programming and erasure<br>its, and blank checking.<br>s programming and erasure of the code flash, data<br>option-setting memory, programming and erasure<br>its, and blank checking. | R/W |

|                   |          |      |          |        |         |    | 1           | flash, or                                                                                   | s programming and erasure of the code flash, data<br>option-setting memory, programming and erasure<br>its, and blank checking.                                                                                                                                                                                                                                                                     |     |

Programming and erasure of the code flash memory, data flash memory, or option-setting memory, programming and erasure of lock bits, and blank checking are prohibited by hardware.

These bits are read as 0. The write value should be 0.

FWEPROR is initialized by a reset due to the signal on the RES# pin, a power-on reset, a voltage-monitoring 0 reset, an independent watchdog timer reset, a watchdog timer reset, a voltage-monitoring 1 reset, a voltage-monitoring 2 reset, and a software reset, and by transitions to software standby and deep software standby.

R/W

b7 to b2

Address(es): 007F E010h

R/W

R/W R/W\*1

R

R/W R/W\*<sup>1</sup>

## 4.2 Flash Access Status Register (FASTAT)

|                   | b7     | b6 | b5                  | b4              | b3       | b2  | b1                                                                                                                                     | b0         |                                                                                  |  |

|-------------------|--------|----|---------------------|-----------------|----------|-----|----------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------------------------------------------------------------------|--|

|                   | CFAE   | _  | -                   | CMDLK           | DFAE     | _   | _                                                                                                                                      | ECRCT      |                                                                                  |  |

| /alue after reset | :: 0   | 0  | 0                   | 0               | 0        | 0   | 0                                                                                                                                      | 0          |                                                                                  |  |

|                   |        |    |                     |                 |          |     |                                                                                                                                        |            |                                                                                  |  |

| Bit               | Symbol | В  | it Nam              | e               |          |     | Descri                                                                                                                                 | ption      |                                                                                  |  |

| b0                | ECRCT  | E  | rror Fla            | g               |          |     |                                                                                                                                        |            | occurred.<br>occurred.                                                           |  |

| b2, b1            | _      | R  | eserve              | d               |          |     | These                                                                                                                                  | bits are r | ead as 0. The write value should be 0.                                           |  |

| b3                | DFAE   |    | ata Fla<br>iolation | sh Memo<br>Flag | ory Acce | ess | <ul><li>0: No data flash memory access violation has occurred.</li><li>1: A data flash memory access violation has occurred.</li></ul> |            |                                                                                  |  |

| b4                | CMDLK  | C  | ommar               | nd Lock I       | Flag     |     |                                                                                                                                        |            | uencer is not in the command-locked st<br>uencer is in the command-locked state. |  |

| b6, b5            | _      | R  | eserve              | d               |          |     | These                                                                                                                                  | bits are r | ead as 0. The write value should be 0.                                           |  |

Note 1. Only 0 can be written to clear the flag after 1 is read.

Violation Flag

Code Flash Memory Access

FASTAT register indicates whether a code flash memory or data flash memory access violation has occurred. If any of the CFAE, CMDLK and DFAE flags is set to 1, the flash sequencer enters the command-locked state (see section 7.2, Error Protection). To release it from the command-locked state, a status clear command or forced stop command must be issued by the FACI after clearing the CFAE and DFAE flags in the FASTAT register to 0.

0: No code flash memory access violation has occurred. 1: A code flash memory access violation has occurred.

#### ECRCT Flag (Error Flag)

CFAE

This flag indicates that a 1-bit error has been corrected in reading of the flash memory area by the flash sequencer (with parameters for configuration setting or programming) or reading of the FCURAM.

When a 2-bit error is detected in reading of the FCURAM, CMDLK is set to 1 (the flash sequencer is in the command-locked state) and the ECRCT flag does not change.

[Setting Conditions]

b7

- When the flash sequencer reads the flash memory area (configuration setting and programming parameters).

- When a 1-bit error is corrected by reading the FCURAM.

[Clearing Condition]

• When the flash sequencer starts processing of a forced stop command while the FRCRCT flag in the FSTATR register is 1.

#### DFAE Flag (Data Flash Memory Access Violation Flag)

This flag indicates whether a data flash memory access violation occurred. If this flag is set to 1, the FSTATR.ILGLERR flag is set to 1, placing the flash sequencer in the command-locked state.

[Setting Conditions]

In general, commands being issued in data flash memory P/E mode as described below.

- An FACI command being issued while the setting of b18 to b0 in the FSADDR register is 1 0000h to 7 FFFFh (indicating the reserved portion of the data area)

- A configuration setting command being issued while the setting of b18 to b0 in the FSADDR register is 0 0000h to 0 003Fh or 0 0100h to 7 FFFFh.

[Clearing Condition]

• 0 being written after reading of 1.

#### CMDLK Flag (Command Lock Flag)

This flag indicates that the flash sequencer is in the command-locked state. [Setting Condition]

• The flash sequencer detects an error and enters the command-locked state.

[Clearing Condition]

• The flash sequencer starting to process a status clear or forced stop command while the CFAE or DFAE flag in the FASTAT register is 0.

#### CFAE Flag (Code Flash Memory Access Violation Flag)

This flag indicates whether a code flash memory access violation has occurred. If this flag is set to 1, the FSTATR.ILGLERR flag is set to 1, placing the flash sequencer in the command-locked state.

[Setting Conditions]

An FACI command being issued in code flash memory P/E mode while settings are as follows:

• The setting of b23 to b0 in the FSADDR register is 00 0000h to BF FFFFh (reserved portion of the user area). [Clearing Condition]

• 0 being written after reading of 1.

Address(es): 007F E014h

## 4.3 Flash Access Error Interrupt Enable Register (FAEINT)

| ( )                |        |    |    |             |        |    |    |             |

|--------------------|--------|----|----|-------------|--------|----|----|-------------|

|                    | b7     | b6 | b5 | b4          | b3     | b2 | b1 | b0          |

|                    | CFAEIE | -  | _  | CMDLK<br>IE | DFAEIE | _  | _  | ECRCT<br>IE |

| Value after reset: | 1      | 0  | 0  | 1           | 1      | 0  | 0  | 1           |

| Bit    | Symbol  | Bit Name                                               | Description                                                                                                                                                                                                       | R/W |

|--------|---------|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b0     | ECRCTIE | Error Interrupt Enable                                 | <ul> <li>0: Generation of an FIFERR interrupt request is disabled when FASTAT.ECRCT is set to 1.</li> <li>1: Generation of an FIFERR interrupt request is enabled when FASTAT.ECRCT is set to 1.</li> </ul>       | R/W |

| b2, b1 | _       | Reserved                                               | These bits are read as 0. The write value should be 0.                                                                                                                                                            | R/W |

| b3     | DFAEIE  | Data Flash Memory Access<br>Violation Interrupt Enable | <ul><li>0: Generation of an FIFERR interrupt request is disabled when FASTAT.DFAE is set to 1.</li><li>1: Generation of an FIFERR interrupt request is enabled when FASTAT.DFAE is set to 1.</li></ul>            |     |

| b4     | CMDLKIE | Command Lock Interrupt<br>Enable                       | <ul> <li>0: Generation of an FIFERR interrupt request is disabled when FASTAT.CMDLK is set to 1.</li> <li>1: Generation of an FIFERR interrupt request is enabled when FASTAT.CMDLK is set to 1.</li> </ul>       |     |

| b6, b5 | _       | Reserved                                               | These bits are read as 0. The write value should be 0.                                                                                                                                                            | R/W |

| b7     | CFAEIE  | Code Flash Memory Access<br>Violation Interrupt Enable | <ol> <li>O: Generation of an FIFERR interrupt request is disabled when<br/>FASTAT.CFAE is set to 1.</li> <li>1: Generation of an FIFERR interrupt request is enabled when<br/>FASTAT.CFAE is set to 1.</li> </ol> | R/W |

FAEINT register enables or disables generation of a flash access error (FIFERR) interrupt request.

#### ECRCTIE Bit (Error Interrupt Enable)

This bit enables or disables generation of an FIFERR interrupt request when a 1-bit error has been corrected in reading of the flash memory area by the flash sequencer (with parameters for configuration setting or programming) or reading of the FCURAM, leading to setting of the FASTAT.ECRCT flag to 1.

#### DFAEIE Bit (Data Flash Memory Access Violation Interrupt Enable)

This bit enables or disables generation of an FIFERR interrupt request when a data flash memory access violation occurs leading to the FASTAT.DFAE flag being set to 1.

#### CMDLKIE Bit (Command Lock Interrupt Enable)

This bit enables or disables generation of an FIFERR interrupt request when the flash sequencer enters the command-locked state leading to the FASTAT.CMDLK flag being set to 1.

#### CFAEIE Bit (Code Flash Memory Access Violation Interrupt Enable)

This bit enables or disables generation of an FIFERR interrupt request when a code flash memory access violation occurs leading to the FASTAT.CFAE flag being set to 1.

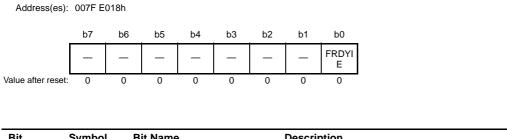

## 4.4 Flash Ready Interrupt Enable Register (FRDYIE)

| Bit      | Symbol | Bit Name                     | Description                                                                                                                              | R/W |

|----------|--------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b0       | FRDYIE | Flash Ready Interrupt Enable | <ul><li>0: Generation of an FRDY interrupt request is disabled.</li><li>1: Generation of an FRDY interrupt request is enabled.</li></ul> | R/W |

| b7 to b1 | _      | Reserved                     | These bits are read as 0. The write value should be 0.                                                                                   | R/W |

FRDYIE register enables or disables generation of a flash ready (FRDY) interrupt request.

#### FRDYIE Bit (Flash Ready Interrupt Enable)

This bit is used to enable or disable generation of an FRDY interrupt request when the FASTAT.FRDY flag is changed from 0 to 1 on completion of processing by the flash sequencer of programming and erasure or a blank checking command.

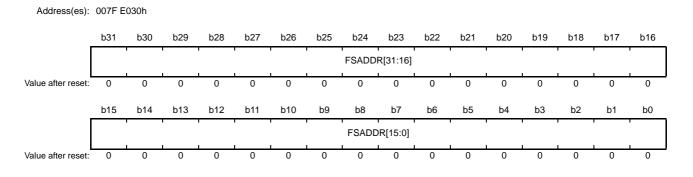

## 4.5 FACI Command Start Address Register (FSADDR)

| Bit       | Symbol           | Bit Name                                     | Description                                                                                                                                                                                                                                    |                                                                                                                                               | R/W               |

|-----------|------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| b31 to b0 | FSADDR<br>[31:0] | Start Address for FACI<br>Command Processing | [Command]<br>Programming (code flash memory):<br>Programming (data flash memory):<br>Block erase (code flash memory):<br>Block erase (data flash memory):<br>Blank check:<br>Configuration setting:<br>Lock-bit programming:<br>Lock-bit read: | [Address boundary]<br>256-byte<br>4-byte<br>8-Kbyte or 32-Kbyte<br>64-byte<br>4-byte<br>16-byte<br>8-Kbyte or 32-Kbyte<br>8-Kbyte or 32-Kbyte | R/W* <sup>1</sup> |

Note 1. Writing to these bits is only possible when the FSTATR.FRDY flag is 1. Writing to these bits while the FSTATR.FRDY flag = 0 is ignored. Note that b0 and b1 are read-only.

FSADDR register specifies the address where the target area for command processing starts when the FACI command for programming, block erasure, blank checking, configuration setting, lock-bit programming, or lock-bit reading is issued.

The FSADDR register is initialized when the FSUINITR.SUINIT bit is set to 1. It is also initialized by a reset.

#### FSADDR[31:0] Bits (Start Address for FACI Command Processing)

These bits specify the start address for FACI command processing. b31 to b24 are ignored in FACI command processing for the code flash memory. b31 to b19 are ignored in FACI command processing for the data flash memory. Bits corresponding to address bits of lower order than the corresponding boundary listed above are also ignored. Refer to the User's Manual: Hardware for the start addresses of the code flash memory area and data flash memory area. See Table 6.5, Address Used by Configuration Set Command for the start address of the configuration set area

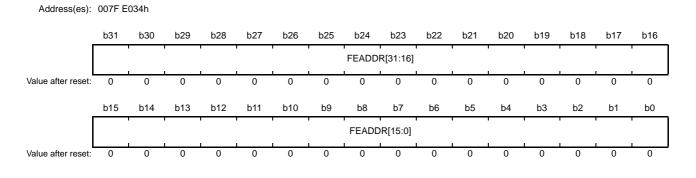

## 4.6 FACI Command End Address Register (FEADDR)

| Bit       | Symbol           | Bit Name                                   | Description                                 | R/W   |

|-----------|------------------|--------------------------------------------|---------------------------------------------|-------|

| b31 to b0 | FEADDR<br>[31:0] | End Address for FACI<br>Command Processing | The end address for FACI command processing | R/W*1 |

Note 1. Writing to these bits is only possible when the FSTATR.FRDY flag is 1. Writing to these bits while the FSTATR.FRDY flag = 0 is ignored. Note that b0 and b1 are read-only.

FEADDR register specifies the address where the target area for blank check command processing ends. When incremental mode is selected as the addressing mode for blank checking (i.e. when FBCCNT.BCDIR = 0), the address specified in the FSADDR register should be smaller than the address in the FEADDR register. Conversely, the address in the FSADDR register should be larger than the address in the FEADDR register when decremental mode is selected as the addressing mode for blank checking (i.e. when FBCCNT.BCDIR = 1). If the settings of the FBCCNT.BCDIR bit and the FSADDR and FEADDR registers are inconsistent with the above rules, the flash sequencer enters the command-locked state (see section 7.2, Error Protection).

The FEADDR register is initialized when the FSUINITR.SUINIT bit is set to 1. It is also initialized by a reset.

#### FEADDR[31:0] Bits (End Address for FACI Command Processing)

These bits specify the end address for blank check command processing. b31 to b19, b1, and b0 are ignored in command processing.

Refer to the User's Manual: Hardware for the end address of the data flash memory area.

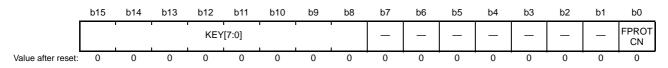

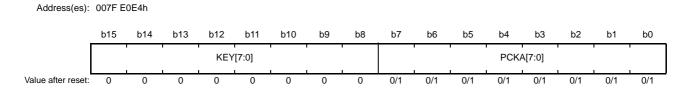

## 4.7 FCURAM Enable Register (FCURAME)

| Address(es):       | 007F E | 054h |     |     |       |     |    |    |    |    |    |    |    |    |              |       |

|--------------------|--------|------|-----|-----|-------|-----|----|----|----|----|----|----|----|----|--------------|-------|

|                    | b15    | b14  | b13 | b12 | b11   | b10 | b9 | b8 | b7 | b6 | b5 | b4 | b3 | b2 | b1           | b0    |

|                    |        |      | 1   | KEY | [7:0] |     |    | 1  |    |    | Ι  |    | _  | _  | FRAMT<br>RAN | FCRME |

| Value after reset: | 0      | 0    | 0   | 0   | 0     | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0            | 0     |

| Bit       | Symbol   | Bit Name             | Description                                                                                                                                                                                          | R/W   |

|-----------|----------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| b0        | FCRME    | FCURAM Enable        | 0: Disables access to the FCURAM.<br>1: Enables access to the FCURAM.                                                                                                                                | R/W*1 |

| b1        | FRAMTRAN | FCURAM Transfer Mode | <ol> <li>0: Normal transfer mode<br/>Both read and write access to the FCURAM are possible.</li> <li>1: High-speed write mode<br/>Only high-speed write access to the FCURAM is possible.</li> </ol> | R/W*1 |

| b7 to b2  | _        | Reserved             | These bits are read as 0. The write value should be 0.                                                                                                                                               | R/W   |

| b15 to b8 | KEY[7:0] | Key Code             | Key code                                                                                                                                                                                             | R/W*2 |

Note 1. Writing to these bits is only possible when 16 bits are written and the value written to the KEY bits is C4h. Note 2. Written values are not retained by these bits. These bits are read as 0.

FCURAME register enables or disables access to the FCURAM area.

#### FCRME Bit (FCURAM Enable)

This bit enables or disables access to the FCURAM. Before writing to the FCURAM, stop the flash sequencer by clearing the FENTRYR register to 0000h.

#### FRAMTRAN Bit (FCURAM Transfer Mode)

This bit specifies the FCURAM transfer mode.

#### KEY[7:0] Bits (Key Code)

These bits control permission and prohibition of writing to the FRAMTRAN and FCRME bits.

## 4.8 Flash Status Register (FSTATR)

Address(es): 007F E080h

|                    | b31  | b30         | b29        | b28        | b27        | b26        | b25        | b24        | b23        | b22         | b21 | b20 | b19 | b18 | b17        | b16        |

|--------------------|------|-------------|------------|------------|------------|------------|------------|------------|------------|-------------|-----|-----|-----|-----|------------|------------|

|                    | _    | -           | _          | _          | _          | _          | _          | _          | _          | —           | Ι   | _   | _   | _   | -          | —          |

| Value after reset: | 0    | 0           | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0           | 0   | 0   | 0   | 0   | 0          | 0          |

|                    | b15  | b14         | b13        | b12        | b11        | b10        | b9         | b8         | b7         | b6          | b5  | b4  | b3  | b2  | b1         | b0         |

|                    | FRDY | ILGLER<br>R | ERSER<br>R | PRGER<br>R | SUSRD<br>Y | DBFUL<br>L | ERSSP<br>D | PRGSP<br>D | FCUER<br>R | FLWEE<br>RR | Ι   | _   |     |     | FRDTC<br>T | FRCRC<br>T |

| Value after reset: | 1    | 0           | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 0           | 0   | 0   | 0   | 0   | 0          | 0          |

| Bit        | Symbol  | Bit Name                             | Description                                                                                                                                                                                                                                        | R/W |

|------------|---------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| b0         | FRCRCT  | 1-Bit Error Correction Monitor Flag  | <ul><li>0: A 1-bit error correction has not been detected.</li><li>1: A 1-bit error correction has been detected.</li></ul>                                                                                                                        | R   |

| b1         | FRDTCT  | 2-Bit Error Detection Monitor Flag   | 0: A 2-bit error has not been detected.<br>1: A 2-bit error has been detected.                                                                                                                                                                     | R   |

| b5 to b2   | _       | Reserved                             | These bits are read as 0. The write value should be 0.                                                                                                                                                                                             | R/W |

| b6         | FLWEERR | Flash Write/Erase Protect Error Flag | 0: An error has not occurred.<br>1: An error has occurred.                                                                                                                                                                                         | R   |

| b7         | FCUERR  | FCU Error Flag                       | 0: An error has not occurred during FCU processing.<br>1: An error has occurred during FCU processing.                                                                                                                                             | R   |

| b8         | PRGSPD  | Programming Suspend Status Flag      | <ul><li>0: The flash sequencer is in a state other than those corresponding to the value 1.</li><li>1: The flash sequencer is in the programming suspension processing state or the programming suspended state.</li></ul>                         | R   |

| b9         | ERSSPD  | Erasure Suspend Status Flag          | <ul><li>0: The flash sequencer is in a state other than those corresponding to the value 1.</li><li>1: The flash sequencer is in the erasure suspension processing state or the erasure-suspended state.</li></ul>                                 | R   |

| b10        | DBFULL  | Data Buffer Full Flag                | 0: The data buffer is empty.<br>1: The data buffer is full.                                                                                                                                                                                        | R   |

| b11        | SUSRDY  | Suspend Ready Flag                   | <ul><li>0: The flash sequencer cannot receive P/E suspend commands.</li><li>1: The flash sequencer can receive P/E suspend commands.</li></ul>                                                                                                     | R   |

| b12        | PRGERR  | Programming Error Flag               | <ul><li>0: Programming has been completed successfully.</li><li>1: An error has occurred during programming.</li></ul>                                                                                                                             | R   |

| b13        | ERSERR  | Erasure Error Flag                   | <ul><li>0: Erasure has been completed successfully.</li><li>1: An error has occurred during erasure.</li></ul>                                                                                                                                     | R   |

| b14        | ILGLERR | Illegal Command Error Flag           | <ul><li>0: The flash sequencer has not detected an illegal FACI command or illegal flash memory access.</li><li>1: The flash sequencer has detected an illegal FACI command or illegal flash memory access.</li></ul>                              | R   |

| b15        | FRDY    | Flash Ready Flag                     | <ul> <li>0: Programming, block erase, P/E suspend, P/E resume, forced stop, blank check, configuration setting, lock-bit programming, or lock-bit read command processing is in progress.</li> <li>1: None of the above is in progress.</li> </ul> | R   |

| b31 to b16 | _       | Reserved                             | These bits are read as 0. The write value should be 0.                                                                                                                                                                                             | R/W |

FSTATR register indicates the state of the flash sequencer.

#### FRCRCT Flag (1-Bit Error Correction Monitor Flag)

This flag indicates that a 1-bit error has been corrected by reading FCURAM by the FCU. When the FRCRCT flag is 1, the flash sequencer is not in the command locked state.

[Clearing Condition]

• When the flash sequencer starts processing of a forced stop command. After the FCU is initialized by issuing a forced stop command, reload the FCU firmware into the FCURAM.

#### FRDTCT Flag (2-Bit Error Detection Monitor Flag)

This flag indicates that a 2-bit error has been detected by reading FCURAM by the FCU. When the FRDTCT flag is 1, the flash sequencer is in the command locked state.

[Clearing Condition]

• When the flash sequencer starts processing of a forced stop command. After the FCU is initialized by issuing a forced stop command, reload the FCU firmware into the FCURAM.

#### FLWEERR Flag (Flash Write/Erase Protect Error Flag)

This flag indicates a violation of the flash memory overwrite protection setting in the FWEPROR register. If this flag is 1, the flash sequencer is in the command-locked state.

[Clearing Condition]

• The flash sequencer starts processing of a forced stop command.

#### FCUERR Flag (FCU Error Flag)

This flag indicates that an error has occurred during FCU processing. If this flag is 1, the flash sequencer is in the command-locked state.

[Clearing Condition]

• The flash sequencer starts processing of a forced stop command.

When this flag is 1, issue a forced stop command and initialize the FCU, and then reload the FCU firmware into the FCURAM.

#### PRGSPD Flag (Programming Suspend Status Flag)

This flag indicates that the flash sequencer is in the programming suspension processing state or programming suspended state.

[Setting Condition]

• The flash sequencer starts processing in response to a programming suspend command.

[Clearing Conditions]

- Reception of the P/E resume command by the flash sequencer (after write access to the FACI command-issuing area is completed).

- The flash sequencer starts processing of a forced stop command.

#### ERSSPD Flag (Erasure Suspend Status Flag)

This flag indicates that the flash sequencer is in the erasure suspension processing state or erasure suspended state. [Setting Condition]

• The flash sequencer starts processing in response to an erasure suspend command.

[Clearing Conditions]

- Reception of the P/E resume command by the flash sequencer (after write access to the FACI command-issuing area is completed).

- The flash sequencer starts processing of a forced stop command.

#### DBFULL Flag (Data Buffer Full Flag)

This flag indicates the state of the data buffer when a programming command is issued. The FACI incorporates a buffer for write data (data buffer). When data for writing to the flash memory are issued to the FACI command-issuing area while the data buffer is full, the FACI inserts a wait cycle in the peripheral bus 6.

[Setting Condition]

• The data buffer becomes full while programming commands are being issued.

[Clearing Condition]

• The data buffer becomes empty.

#### SUSRDY Flag (Suspend Ready Flag)

This flag indicates whether the flash sequencer can receive a P/E suspend command. [Setting Condition]

• After starting programming/erasure processing, the flash sequencer enters a state in which P/E suspend commands can be received.

[Clearing Conditions]

- Reception of the P/E suspend command or forced stop command by the flash sequencer (after write access to the FACI command-issuing area is completed).

- During programming or erasure, the flash sequencer enters the command-locked state.

- Programming or erasure has been completed.

#### PRGERR Flag (Programming Error Flag)

This flag indicates the result of programming of the flash memory. If this flag is 1, the flash sequencer is in the command-locked state.

[Setting Conditions]

- An error occurs during programming.

- A programming or lock-bit programming command is issued for an area where the lock bit setting is for protection. [Clearing Condition]

- The flash sequencer starts processing of a status clear or forced stop command.

#### **ERSERR Flag (Erasure Error Flag)**

This flag indicates the result of erasure of the flash memory. If this flag is 1, the flash sequencer is in the command-locked state.

[Setting Conditions]

- An error has occurred during erasure.

- A block erase command is issued for an area where the lock bit setting is for protection.

[Clearing Condition]

• The flash sequencer starts processing of a status clear or forced stop command.

#### ILGLERR Flag (Illegal Command Error Flag)

This flag indicates that the flash sequencer has detected an illegal FACI command or flash memory access. If this flag is 1, the flash sequencer is in the command-locked state.

[Setting Conditions] (See section 7.2, Error Protection)

- The flash sequencer has detected an illegal command.

- The flash sequencer has detected illegal flash memory access.

- The setting of the FENTRYR register is invalid.

[Clearing Condition]

• The flash sequencer starts processing of a status clear or forced stop command while the DFAE and CFAE flag in the FASTAT register is 0.

If the flash sequencer completes processing of a status clear or forced stop command while the CFAE or DFAE flag in the FASTAT register is 1, this flag is set to 1. This flag is temporarily set to 0 during processing of a forced stop command, and is re-set to 1 when the CFAE or DFAE flag is detected as 1 on completion of command processing.

## FRDY Flag (Flash Ready Flag)

This flag indicates the command processing state of the flash sequencer. [Setting Conditions]

- The flash sequencer completes command processing.

- The flash sequencer receives a P/E suspend command and suspends programming of the flash memory.

- The flash sequencer has received a forced stop command and ended command processing.

[Clearing Conditions]

- The flash sequencer has received an FACI command.

- For programming and configuration setting, the first write access to the FACI command-issuing area.

- For other commands, the last write access to the FACI command-issuing area.

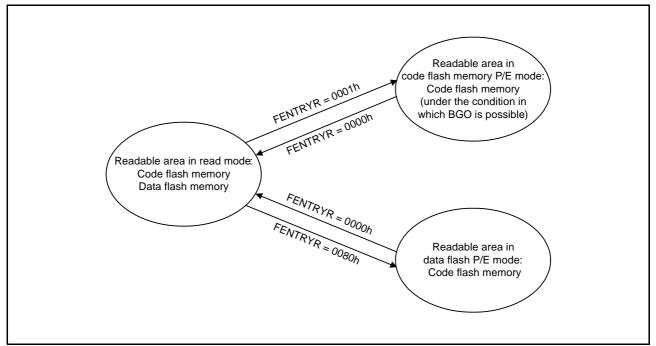

## 4.9 Flash P/E Mode Entry Register (FENTRYR)

Address(es): 007F E084h

|                    | b15 | b14 | b13 | b12 | b11   | b10 | b9 | b8 | b7          | b6 | b5 | b4 | b3 | b2 | b1 | b0          |

|--------------------|-----|-----|-----|-----|-------|-----|----|----|-------------|----|----|----|----|----|----|-------------|

|                    |     | 1   | 1   | KEY | [7:0] | 1   |    | 1  | FENTR<br>YD | _  |    |    |    | -  | _  | FENTR<br>YC |

| Value after reset: | 0   | 0   | 0   | 0   | 0     | 0   | 0  | 0  | 0           | 0  | 0  | 0  | 0  | 0  | 0  | 0           |

| Bit       | Symbol   | Bit Name                            | Description                                                                   | R/W                   |

|-----------|----------|-------------------------------------|-------------------------------------------------------------------------------|-----------------------|

| b0        | FENTRYC  | Code Flash Memory P/E Mode<br>Entry | 0: Code flash memory is in read mode.<br>1: Code flash memory is in P/E mode. | R/W*1, *2             |

| b6 to b1  | _        | Reserved                            | These bits are read as 0. The write value should be 0.                        | R/W                   |

| b7        | FENTRYD  | Data Flash Memory P/E Mode<br>Entry | 0: Data flash memory is in read mode.<br>1: Data flash memory is in P/E mode. | R/W* <sup>1, *2</sup> |

| b15 to b8 | KEY[7:0] | Key Code                            | Key code                                                                      | R/W*3                 |

Note 1. Writing to these bits is only possible when the FSTATR.FRDY flag is 1. Writing to these bits while the FSTATR.FRDY flag = 0 is ignored.

Note 2. Writing to these bits is only possible when 16 bits are written and the value written to the KEY bits is AAh.

Note 3. Written values are not retained by these bits. These bits are read as 0.

FENTRYR is used to specify code flash memory P/E mode and data flash memory P/E mode. To specify code flash memory P/E mode or data flash memory P/E mode so that the flash sequencer can receive FACI commands, set either the FENTRYD or FENTRYC bit to 1 to place the flash sequencer in P/E mode.

Note that setting this register to a value other than 0001h and 0080h, the FSTATR.ILGLERR flag will be set to 1, leading to the flash sequencer being placed in the command-locked state.

The FENTRYR register is initialized when the FSUINITR.SUINIT bit is set to 1. It is also initialized by a reset.

#### FENTRYC Bit (Code Flash Memory P/E Mode Entry)

This bit specifies the P/E mode for code flash memory. [Setting Condition]

• 1 being written to the FENTRYC bit while writing to FENTRYR is enabled and FENTRYR is 0000h.

[Clearing Conditions]

- 8 bits being written to FENTRYR while the FSTATR.FRDY flag is 1.

- A value other than AAh is specified in the KEY bits and 16 bits are written to FENTRYR while the FSTATR.FRDY flag is 1.

- 0 being written to the FENTRYC bit while writing to FENTRYR is enabled.

- FENTRYR being written to while writing to FENTRYR is enabled and the value of FENTRYR is other than 0000h.

#### FENTRYD Bit (Data Flash Memory P/E Mode Entry)

This bit specifies the P/E mode for data flash memory. [Setting Condition]

• 1 being written to the FENTRYR.FENTRYD bit while writing to FENTRYR is enabled and FENTRYR is 0000h. [Clearing Conditions]

- 8 bits being written to FENTRYR while the FSTATR.FRDY flag is 1.

- Writing of 16 bits to FENTRYR with a value other than AAh specified for the KEY bits while the FSTATR.FRDY flag is 1.

- 0 being written to the FENTRYD bit while writing to FENTRYR is enabled.

- FENTRYR being written to while writing to FENTRYR is enabled and the value of FENTRYR is other than 0000h.

#### KEY[7:0] Bits (Key Code)

These bits control permission and prohibition of writing to the FENTRYD and FENTRYC bits.

## 4.10 Flash Protection Register (FPROTR)

Address(es): 007F E088h

| Bit       | Symbol   | Bit Name                   | Description                                                                                                | R/W   |

|-----------|----------|----------------------------|------------------------------------------------------------------------------------------------------------|-------|

| b0        | FPROTCN  | Lock Bit Protection Cancel | <ul><li>0: Enables protection by the lock bits.</li><li>1: Disables protection by the lock bits.</li></ul> | R/W*1 |

| b7 to b1  | _        | Reserved                   | These bits are read as 0. The write value should be 0.                                                     | R/W   |

| b15 to b8 | KEY[7:0] | Key Code                   | Key code                                                                                                   | R/W*2 |

Note 1. Writing to these bits is only possible when 16 bits are written and the value written to the KEY bits is 55h. Note 2. Written values are not retained by these bits. These bits are read as 0.

FPROTR enables or disables protection by the lock bits of the code flash memory against programming and erasure. The FPROTR register is initialized when the FSUINITR.SUINIT bit is set to 1. It is also initialized by a reset.

#### FPROTCN Bit (Lock Bit Protection Cancel)

This bit enables or disables protection by the lock bits of the code flash memory against programming and erasure. [Setting Condition]

• 1 being written to the FPROTCN bit while writing to FPROTR is enabled and the value of FENTRYR is other than 0000h.

[Clearing Conditions]

- 8 bits being written to FPROTR

- Writing of 16 bits to FPROTR with a value other than 55h specified for the KEY bits

- 0 being written to the FPROTRCN bit while writing to FPROTR is enabled

- The value of FENTRYR being 0000h

#### KEY[7:0] Bits (Key Code)

These bits control permission and prohibition of writing to the FPROTCN bit.

## 4.11 Flash Sequencer Set-Up Initialization Register (FSUINITR)

| Address(es)       | : 007F E0 | 08Ch |          |             |        |     |                              |                            |                            |                  |                   |                                        |                    |                   |    |          |

|-------------------|-----------|------|----------|-------------|--------|-----|------------------------------|----------------------------|----------------------------|------------------|-------------------|----------------------------------------|--------------------|-------------------|----|----------|

|                   | b15       | b14  | b13      | b12         | b11    | b10 | b9                           | b8                         | b7                         | b6               | b5                | b4                                     | b3                 | b2                | b1 | b0       |

|                   |           |      | I        | KEY         | ′[7:0] | 1   | 1                            | I                          | _                          | _                | _                 | -                                      | _                  | —                 | _  | SUINIT   |

| Value after reset | :: 0      | 0    | 0        | 0           | 0      | 0   | 0                            | 0                          | 0                          | 0                | 0                 | 0                                      | 0                  | 0                 | 0  | 0        |

| Bit               | Symbol    | В    | it Name  | 9           |        |     | Descr                        | iption                     |                            |                  |                   |                                        |                    |                   | -  | w        |

| b0                | SUINIT    | S    | et-Up Ir | nitializati | ion    |     | and<br>curr<br>1: The<br>and | FBCCN<br>ent valu<br>FEADD | IT flash<br>es.<br>PR, FPR | sequen<br>OTR, F | cer set-<br>CPSR, | FSADD<br>up regis<br>FSADD<br>up regis | sters ke<br>R, FEN | ep their<br>TRYR, | R  | /W*1, *2 |

|           |          |          | initialized.                                           |       |

|-----------|----------|----------|--------------------------------------------------------|-------|

| b7 to b1  | _        | Reserved | These bits are read as 0. The write value should be 0. | R/W   |

| b15 to b8 | KEY[7:0] | Key Code | Key code                                               | R/W*3 |

Note 1. Writing to these bits is only possible when the FSTATR.FRDY flag is 1. Writing to these bits while the FSTATR.FRDY flag = 0 is ignored.

Note 2. Writing to these bits is only possible when 16 bits are written and the value written to the KEY bits is 2Dh.

Note 3. Written values are not retained by these bits. This bit is read as 0.

FSUINITR is used for initialization of the flash sequencer set-up.

#### SUINIT Bit (Set-Up Initialization)

This bit initializes the following flash sequencer set-up registers.

- FEADDR

- FPROTR

- FCPSR

- FSADDR

- FENTRYR

- FBCCNT

#### KEY[7:0] Bits (Key Code)

These bits control permission and prohibition of writing to the SUINIT bit.

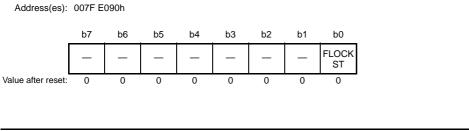

## 4.12 Lock Bit Status Register (FLKSTAT)

| Bit      | Symbol  | Bit Name             | Description                                            | R/W |

|----------|---------|----------------------|--------------------------------------------------------|-----|

| b0       | FLOCKST | Lock Bit Status Flag | 0: Protected state<br>1: Non-protected state           | R   |

| b7 to b1 | _       | Reserved             | These bits are read as 0. The write value should be 0. | R/W |

#### FLOCKST Flag (Lock Bit Status Flag)

This flag reflects the state of a lock bit as read by executing a lock-bit read command. When the FSTATR.FRDY flag becomes 1 after the lock-bit read command is issued, the value of the target lock bit is stored in the FLOCKST flag. The value of the FLOCKST flag is retained until the next lock-bit read command is completed.

## 4.13 FACI Command Register (FCMDR)

| b15 to b8         | CMDR[     | 7:0]   | Corr | mand F | lag    |     |    | The late           | st comr | nand is | stored.  |         |          |       |      | R   |

|-------------------|-----------|--------|------|--------|--------|-----|----|--------------------|---------|---------|----------|---------|----------|-------|------|-----|

| b7 to b0          | PCMDF     | R[7:0] | Prec | omman  | d Flag |     |    | The con<br>stored. | nmand i | mmedia  | tely bef | ore the | latest c | omman | d is | R   |

| Bit               | Symbo     | 1      | Bit  | Name   |        |     |    | Descrip            | tion    |         |          |         |          |       |      | R/W |

| Value after reset | L<br>I: 1 | 1      | 1    | 1      | 1      | 1   | 1  | 1                  | 1       | 1       | 1        | 1       | 1        | 1     | 1    | 1   |

|                   |           |        |      | CMDI   | R[7:0] |     |    |                    |         |         | 1        | PCME    | DR[7:0]  |       | 1    | I   |

|                   | b15       | b14    | b13  | b12    | b11    | b10 | b9 | b8                 | b7      | b6      | b5       | b4      | b3       | b2    | b1   | b0  |

| Address(es)       | : 007F E  | 0A0h   |      |        |        |     |    |                    |         |         |          |         |          |       |      |     |

FCMDR records the two most recent commands accepted by the FACI.

#### PCMDR[7:0] Flags (Precommand Flag)

These flags indicate the command received immediately before the latest command received by the FACI.

#### CMDR[7:0] Flags (Command Flag)

These flags indicate the latest command received by the FACI.

#### Table 4.2 States of FCMDR after Receiving Commands

| Command               | CMDR | PCMDR            |

|-----------------------|------|------------------|

| Programming           | E8h  | Previous command |

| Block erase           | D0h  | 20h              |

| P/E suspend           | B0h  | Previous command |

| P/E resume            | D0h  | Previous command |

| Status clear          | 50h  | Previous command |

| Forced stop           | B3h  | Previous command |

| Blank check           | D0h  | 71h              |

| Configuration setting | 40h  | Previous command |

| Lock-bit programming  | D0h  | 77h              |

| Lock-bit read         | D0h  | 71h              |

## 4.14 Flash P/E Status Register (FPESTAT)

| Address(es       | ): 007F E      | 0C0h     |          |        |      |               |                                                        |                                 |                      |          |                    |                    |                                                 |                     |     |     |

|------------------|----------------|----------|----------|--------|------|---------------|--------------------------------------------------------|---------------------------------|----------------------|----------|--------------------|--------------------|-------------------------------------------------|---------------------|-----|-----|

|                  | b15            | b14      | b13      | b12    | b11  | b10           | b9                                                     | b8                              | b7                   | b6       | b5                 | b4                 | b3                                              | b2                  | b1  | b0  |

|                  | _              | _        | _        | _      | _    | _             | _                                                      | _                               |                      |          | I                  | PEERF              | RST[7:0]                                        |                     | I   | T   |

| Value after rese | t: 0           | 0        | 0        | 0      | 0    | 0             | 0                                                      | 0                               | 0                    | 0        | 0                  | 0                  | 0                                               | 0                   | 0   | 0   |

| Bit              | Symbo          | I Bi     | it Name  | •      |      | D             | escript                                                | ion                             |                      |          |                    |                    |                                                 |                     |     | R/W |

| b7 to b0         | PEERR<br>[7:0] | ST P/    | 'E Error | Status | Flag | 0<br>02<br>12 | 2h: Prog<br>1h: Eras                                   | grammin<br>grammin<br>sure erro | g error<br>or due to | for reas | ons oth<br>a being | er than<br>protect | rotected<br>lock-bit<br>ed by its<br>bit proted | protecti<br>lock bi | ion | R   |

| b15 to b8        |                | Reserved |          |        |      |               | These bits are read as 0. The write value should be 0. |                                 |                      |          |                    |                    |                                                 |                     |     | R/W |

FPESTAT indicates the result of programming or erasure of the flash memory.

#### PEERRST[7:0] Flags (P/E Error Status Flag)

These flags indicate the source of an error that occurred during processing for the programming or erasure of the code flash memory or data flash memory. The value of these flags is only valid if the ERSERR or PRGERR flag in the FSTATR register is 1 while the FSTATR.FRDY flag is 1. When the ERSERR and PRGERR flags are 0, these flags retain their value to indicate the source of the last error to have occurred.

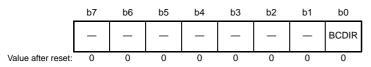

## 4.15 Data Flash Blank Check Control Register (FBCCNT)

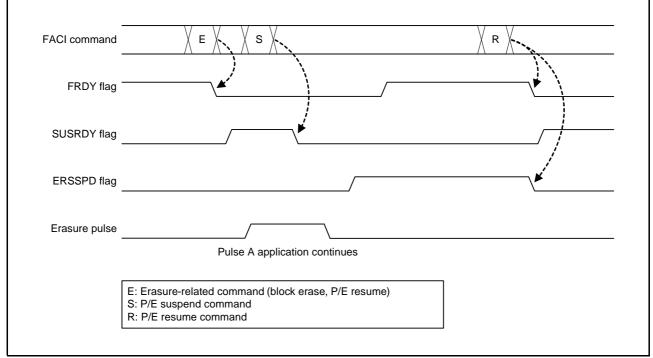

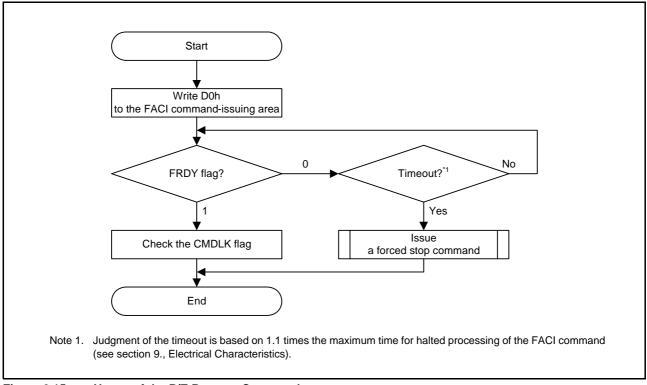

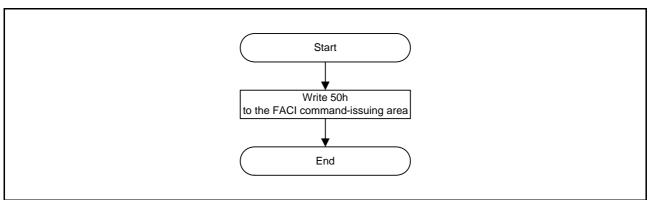

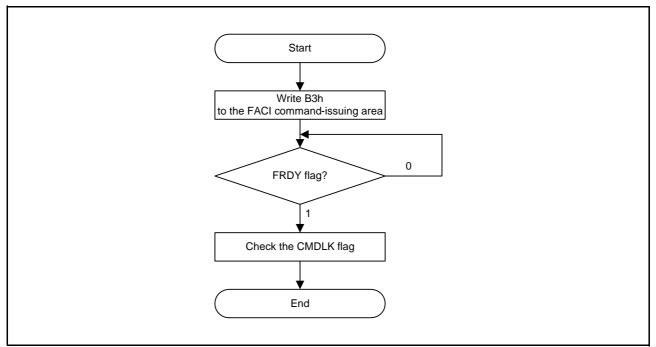

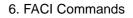

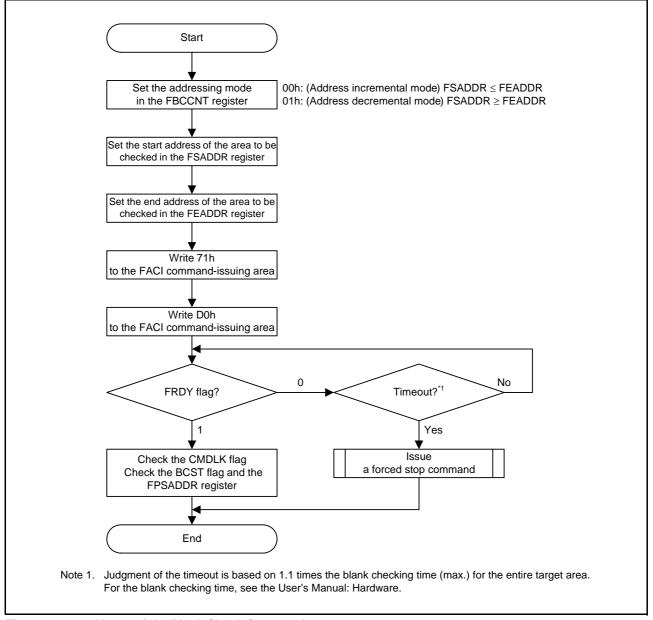

Address(es): 007F E0D0h