# 35V/3.2A Multicell Lithium-lon Step-Down Battery Charger with PowerPath and I<sup>2</sup>C Telemetry

# **FEATURES**

- Li-lon/Polymer Battery Charger with Termination

- Wide Charging Input Voltage Range: 4.5V to 35V

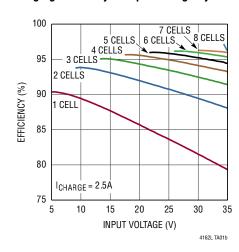

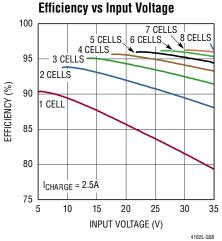

- High Efficiency Synchronous Operation

- 16-Bit Digital Telemetry System Monitors V<sub>BAT</sub>, I<sub>BAT</sub>, R<sub>BAT</sub>, T<sub>BAT</sub>, T<sub>DIE</sub>, V<sub>IN</sub>, I<sub>IN</sub>, V<sub>OUT</sub>

- Charges 1-8 Lithium-Ion/Polymer Cells

- Input Undervoltage Charge Current Limit Loop

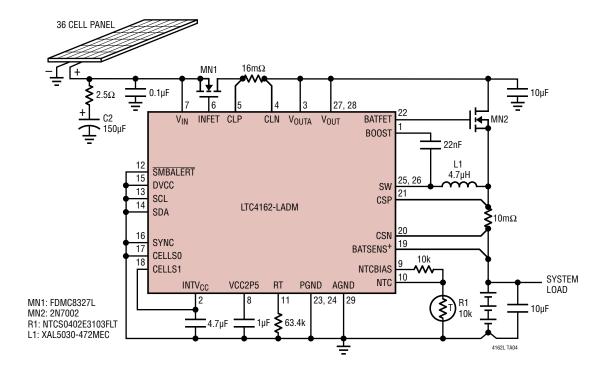

- Input MPPT for Solar Panel Inputs

- Input Current Limit Prioritizes System Load Output

- Low Loss PowerPath<sup>™</sup>

- Instant-On Operation with Discharged or Missing Battery

- JEITA Temperature Controlled Charging

- Pin Compatible with LiFePO<sub>4</sub> and SLA Versions

### **APPLICATIONS**

- Medical Instruments

- USB-C Power Delivery

- Industrial Handhelds

- Ruggedized Notebooks

- Tablet Computers

# DESCRIPTION

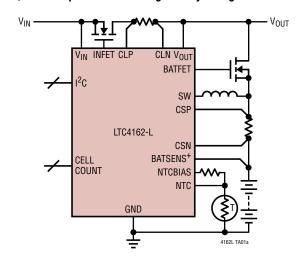

The LTC®4162-L is an advanced monolithic synchronous step-down switching battery charger and PowerPath™ manager that seamlessly manages power distribution between input sources such as wall adapters, backplanes, solar panels, etc., and a rechargeable Lithium-Ion/Polymer battery.

A high resolution measurement system provides extensive telemetry information for circuit voltages, currents, battery resistance and temperature which can all be read back over the I<sup>2</sup>C port. The I<sup>2</sup>C port can also be used to configure many charging parameters including charging voltages and currents, termination algorithms and numerous system status alerts.

The LTC4162-L can charge Lithium-Ion cell stacks from 1 cell to 8 cells with as much as 3.2A of charge current.

The power path topology decouples the output voltage from the battery allowing a portable product to start up instantly under very low battery voltage conditions.

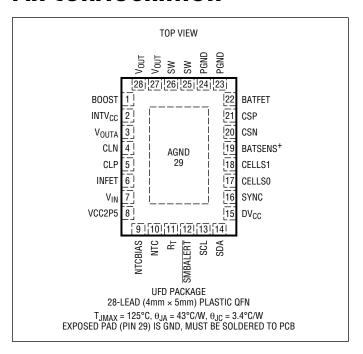

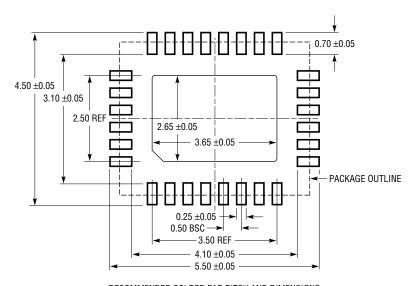

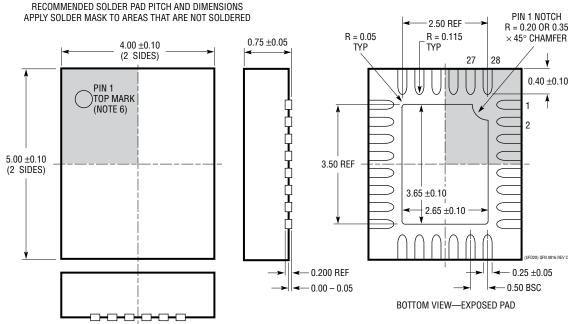

The LTC4162-L is available in a thermally enhanced 28-pin  $4mm \times 5mm \times 0.75mm$  QFN surface mount package.

All registered trademarks and trademarks are the property of their respective owners.

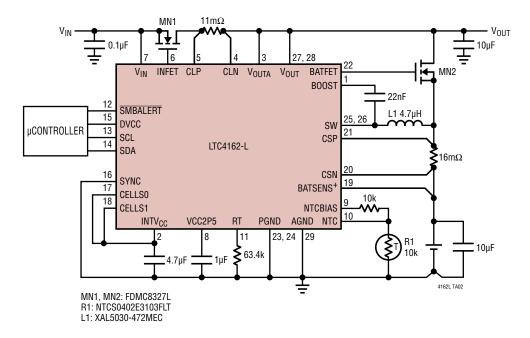

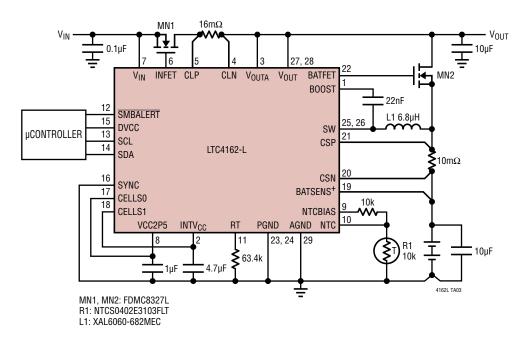

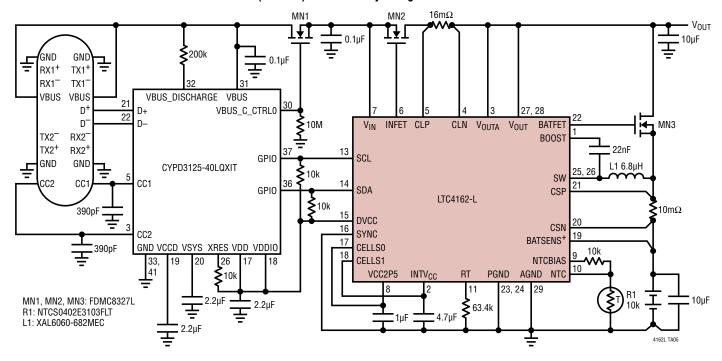

# TYPICAL APPLICATION

1-8 Cell, 3.2A Step-Down Switching Battery Charger with PowerPath

#### Charging Efficiency vs Input Voltage by Cell Count

Rev A

# LTC4162-L

# TABLE OF CONTENTS

| Features                            |    |

|-------------------------------------|----|

| Applications                        |    |

| Typical Application                 |    |

| Description                         |    |

| Absolute Maximum Ratings            |    |

| Order Information                   |    |

| Pin Configuration                   |    |

| Electrical Characteristics          | 4  |

| Typical Performance Characteristics | 7  |

| Pin Functions                       | 10 |

| Block Diagram                       | 12 |

| ESD Diagram                         |    |

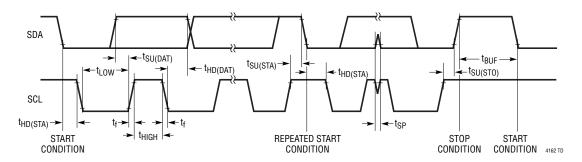

| Timing Diagram                      | 14 |

| Operation                           | 15 |

| Applications Information            |    |

| Register Descriptions               |    |

| Typical Applications                |    |

| Package Description                 | 50 |

| Revision History                    |    |

| Typical Application                 |    |

| Related Parts                       | 52 |

# **ABSOLUTE MAXIMUM RATINGS**

# (Note 1)

| BATSENS+, V <sub>IN</sub> , CSP, CSN, CLP, |                          |

|--------------------------------------------|--------------------------|

| CLN, V <sub>OUT</sub> , V <sub>OUTA</sub>  | 0.3V to 36V              |

| CSP to CSN, CLP to CLN                     | ±0.3V                    |

| CELLSO, CELLS1, SYNC                       | 0.3V to INTVCC           |

| DV <sub>CC</sub>                           | 0.3V to 5.5V             |

| SDA, SCL, SMBALERT                         | 0.3V to DV <sub>CC</sub> |

| I <sub>SW</sub>                            | ±3.5Å                    |

| <b>Operating Junction Temperature Ran</b>  | nge                      |

| (Notes 2, 4)                               | 40 to 125°C              |

| Storage Temperature Range                  | 65 to 150°C              |

# PIN CONFIGURATION

# ORDER INFORMATION

| PART NUMBER            | PART<br>Marking* | TAPE AND<br>REEL | TEMP<br>Grade | DESCRIPTION                                 | TEMPERATURE RANGE |

|------------------------|------------------|------------------|---------------|---------------------------------------------|-------------------|

| LTC4162EUFD-LAD#PBF    | 4162A            |                  | Е             | I <sup>2</sup> C Adjustable Voltage         | -40°C to 125°C    |

| LTC4162EUFD-L40#PBF    | 4162B            |                  | Е             | 4.0V Fixed Voltage                          | -40°C to 125°C    |

| LTC4162EUFD-L41#PBF    | 4162C            |                  | Е             | 4.1V Fixed Voltage                          | -40°C to 125°C    |

| LTC4162EUFD-L42#PBF    | 4162D            |                  | Е             | 4.2V Fixed Voltage                          | -40°C to 125°C    |

| LTC4162EUFD-LADM#PBF   | 4162K            |                  | Е             | I <sup>2</sup> C Adjustable Voltage MPPT ON | -40°C to 125°C    |

| LTC4162EUFD-L40M#PBF   | 4162L            |                  | E             | 4.0V Fixed Voltage MPPT ON                  | -40°C to 125°C    |

| LTC4162EUFD-L41M#PBF   | 4162M            |                  | Е             | 4.1V Fixed Voltage MPPT ON                  | -40°C to 125°C    |

| LTC4162EUFD-L42M#PBF   | 4162N            |                  | E             | 4.2V Fixed Voltage MPPT ON                  | -40°C to 125°C    |

| LTC4162EUFD-LAD#TRPBF  | 4162A            | 1                | Е             | I <sup>2</sup> C Adjustable Voltage         | -40°C to 125°C    |

| LTC4162EUFD-L40#TRPBF  | 4162B            | 1                | Е             | 4.0V Fixed Voltage                          | -40°C to 125°C    |

| LTC4162EUFD-L41#TRPBF  | 4162C            | 1                | Е             | 4.1V Fixed Voltage                          | -40°C to 125°C    |

| LTC4162EUFD-L42#TRPBF  | 4162D            | 1                | Е             | 4.2V Fixed Voltage                          | -40°C to 125°C    |

| LTC4162EUFD-LADM#TRPBF | 4162K            | 1                | Е             | I <sup>2</sup> C Adjustable Voltage MPPT ON | -40°C to 125°C    |

| LTC4162EUFD-L40M#TRPBF | 4162L            | 1                | Е             | 4.0V Fixed Voltage MPPT ON                  | -40°C to 125°C    |

| LTC4162EUFD-L41M#TRPBF | 4162M            | 1                | Е             | 4.1V Fixed Voltage MPPT ON                  | -40°C to 125°C    |

| LTC4162EUFD-L42M#TRPBF | 4162N            | 1                | Е             | 4.2V Fixed Voltage MPPT ON                  | -40°C to 125°C    |

# ORDER INFORMATION

| PART NUMBER            | PART<br>MARKING* | TAPE AND<br>REEL | TEMP<br>Grade | DESCRIPTION                                 | TEMPERATURE RANGE |

|------------------------|------------------|------------------|---------------|---------------------------------------------|-------------------|

| LTC4162IUFD-LAD#PBF    | 4162A            |                  | I             | I <sup>2</sup> C Adjustable Voltage         | -40°C to 125°C    |

| LTC4162IUFD-L40#PBF    | 4162B            |                  | I             | 4.0V Fixed Voltage                          | -40°C to 125°C    |

| LTC4162IUFD-L41#PBF    | 4162C            |                  | I             | 4.1V Fixed Voltage                          | -40°C to 125°C    |

| LTC4162IUFD-L42#PBF    | 4162D            |                  | I             | 4.2V Fixed Voltage                          | -40°C to 125°C    |

| LTC4162IUFD-LADM#PBF   | 4162K            |                  | I             | I <sup>2</sup> C Adjustable Voltage MPPT ON | -40°C to 125°C    |

| LTC4162IUFD-L40M#PBF   | 4162L            |                  | I             | 4.0V Fixed Voltage MPPT ON                  | -40°C to 125°C    |

| LTC4162IUFD-L41M#PBF   | 4162M            |                  | I             | 4.1V Fixed Voltage MPPT ON                  | -40°C to 125°C    |

| LTC4162IUFD-L42M#PBF   | 4162N            |                  | I             | 4.2V Fixed Voltage MPPT ON                  | -40°C to 125°C    |

| LTC4162IUFD-LAD#TRPBF  | 4162A            | 1                | I             | I <sup>2</sup> C Adjustable Voltage         | -40°C to 125°C    |

| LTC4162IUFD-L40#TRPBF  | 4162B            | 1                | I             | 4.0V Fixed Voltage                          | -40°C to 125°C    |

| LTC4162IUFD-L41#TRPBF  | 4162C            | 1                | I             | 4.1V Fixed Voltage                          | -40°C to 125°C    |

| LTC4162IUFD-L42#TRPBF  | 4162D            | 1                | I             | 4.2V Fixed Voltage                          | -40°C to 125°C    |

| LTC4162IUFD-LADM#TRPBF | 4162K            | 1                | I             | I <sup>2</sup> C Adjustable Voltage MPPT ON | -40°C to 125°C    |

| LTC4162IUFD-L40M#TRPBF | 4162L            | /                | I             | 4.0V Fixed Voltage MPPT ON                  | -40°C to 125°C    |

| LTC4162IUFD-L41M#TRPBF | 4162M            | /                | I             | 4.1V Fixed Voltage MPPT ON                  | -40°C to 125°C    |

| LTC4162IUFD-L42M#TRPBF | 4162N            | /                | I             | 4.2V Fixed Voltage MPPT ON                  | -40°C to 125°C    |

Contact the factory for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.

Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full specified operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 4).  $V_{IN} = 18V$ ,  $DV_{CC} = 3.3V$ ,  $R_{SNSI} = 10m\Omega$ ,  $R_{SNSB} = 10m\Omega$  unless otherwise noted.

| SYMBOL                 | PARAMETER                                | CONDITIONS                                                                                                                                                                  |   | MIN          | TYP                | MAX                                   | UNITS          |

|------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------|--------------------|---------------------------------------|----------------|

| System Volta           | ges and Currents                         |                                                                                                                                                                             |   | l.           |                    | · · · · · · · · · · · · · · · · · · · |                |

| $\overline{V_{IN}}$    | Input Supply Voltage                     |                                                                                                                                                                             | • | 4.5          |                    | 35                                    | V              |

| $V_{BAT}$              | Battery Voltage                          |                                                                                                                                                                             | • | 2.7          |                    | 35                                    | V              |

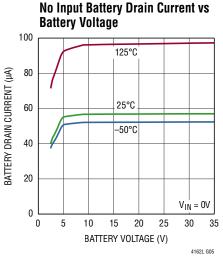

| I <sub>BATSENS</sub> + | Battery Drain Current                    | $\begin{array}{l} V_{IN} - V_{BATSENS} + > V_{IN\_DUVLO}, \text{Terminated} \\ V_{IN} - V_{BATSENS} + < V_{IN\_DUVLO} \\ V_{IN} = 0, \text{SHIPMODE Activated} \end{array}$ |   |              | 0.5<br>54<br>2.8   | 1<br>100<br>5                         | μΑ<br>μΑ<br>μΑ |

| I <sub>VIN</sub>       | V <sub>IN</sub> Drain Current            | $V_{IN} - V_{BATSENS} + > V_{IN\_DUVLO}$ , Terminated                                                                                                                       |   |              | 115                | 200                                   | μA             |

| Switching Ba           | ttery Charger                            |                                                                                                                                                                             |   |              |                    |                                       |                |

| V <sub>CHARGE</sub>    | Range<br>Resolution (5 Bits)<br>Accuracy | Per cell_count                                                                                                                                                              | • | -0.5<br>-1.5 | 3.8125–4.2<br>12.5 | 0.5<br>1.5                            | V<br>mV<br>%   |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full specified operating junction temperature range, otherwise specifications are at T<sub>A</sub> = 25°C (Note 4). V<sub>IN</sub> = 18V, DVCC = 3.3V, R<sub>SNSI</sub> = 10m $\Omega$ , RSNSB = 10m $\Omega$  unless otherwise noted.

| SYMBOL                                                                         | PARAMETER                                                                       | CONDITIONS                                                                                                                          |   | MIN            | TYP                   | MAX          | UNITS                     |

|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|---|----------------|-----------------------|--------------|---------------------------|

| I <sub>CHARGE</sub><br>Servo Voltage<br>(V <sub>CSP</sub> – V <sub>CSN</sub> ) | Range<br>Resolution (5 Bits)<br>Accuracy                                        | I <sub>CHARGE</sub> = (V <sub>CSP</sub> - V <sub>CSN</sub> )/R <sub>SNSB</sub><br>Note 5                                            | • | -0.25<br>-0.75 | 1–32<br>1             | 0.25<br>0.75 | mV<br>mV<br>mV            |

| I <sub>INLIM</sub><br>Servo Voltage<br>(V <sub>CLP</sub> – V <sub>CLN</sub> )  | Range<br>Resolution (6 Bits)<br>Accuracy                                        | I <sub>IN</sub> = (V <sub>CLP</sub> - V <sub>CLN</sub> )/R <sub>SNSI</sub><br>Note 6                                                |   | -0.2           | 0.5–32<br>0.5         | 0.2          | mV<br>mV<br>mV            |

| V <sub>INLIM</sub>                                                             | Range<br>Resolution (8 Bits)<br>Full Scale Accuracy                             |                                                                                                                                     |   | -1             | 0.14–36<br>140.625    | 1            | V<br>mV<br>%              |

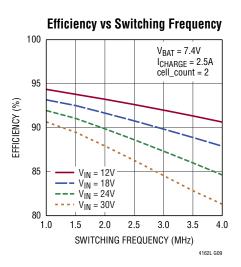

| f <sub>OSC</sub>                                                               | Switching Frequency                                                             | R <sub>T</sub> = 63.4k                                                                                                              | • | 1.4            | 1.5                   | 1.6          | MHz                       |

| D <sub>MAX</sub>                                                               | Maximum Duty Cycle                                                              |                                                                                                                                     |   |                | 99.5                  |              | %                         |

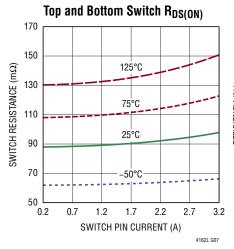

| R <sub>SWITCH</sub>                                                            | Primary Switch On-Resistance                                                    |                                                                                                                                     |   |                | 90                    |              | mΩ                        |

| R <sub>RECT</sub>                                                              | Rectifier Switch On-Resistance                                                  |                                                                                                                                     |   |                | 90                    |              | mΩ                        |

| I <sub>PEAK</sub>                                                              | Peak Inductor Current Limit                                                     | Note 3                                                                                                                              |   | 4              | 45mV/R <sub>SNS</sub> | В            | А                         |

| System Controls                                                                |                                                                                 | ·                                                                                                                                   |   |                |                       |              |                           |

| V <sub>IN_UVLO</sub>                                                           | V <sub>IN</sub> Charger Enable<br>Input Undervoltage Lockout                    | Rising Threshold<br>Hysteresis                                                                                                      |   | 4.2            | 4.4<br>0.2            | 4.6          | V                         |

| V <sub>IN_DUVLO</sub>                                                          | V <sub>IN</sub> to BATSENS+ Charger Enable<br>Differential Undervoltage Lockout | Rising Threshold<br>Hysteresis                                                                                                      |   | 100            | 150<br>170            | 200          | mV<br>mV                  |

| V <sub>IN_OVLO</sub>                                                           | V <sub>IN</sub> Charger Disable<br>Overvoltage Lockout                          | Rising Threshold<br>Hysteresis                                                                                                      |   | 37.6           | 38.6<br>1.4           | 40           | V                         |

| V <sub>INTVCC_UVLO</sub>                                                       | INTV <sub>CC</sub> Telemetry Enable<br>Undervoltage Lockout                     | Rising Threshold<br>Hysteresis                                                                                                      |   | 2.75           | 2.85<br>0.12          | 2.95         | V                         |

| Telemetry A/D M                                                                | leasurement Subsystem                                                           | ·                                                                                                                                   |   |                |                       |              |                           |

| I <sub>BAT</sub> (V <sub>CSP</sub> – V <sub>CSN</sub> )                        | Resolution<br>Offset Error<br>Span Error                                        | $I_{BAT} = (V_{CSP} - V_{CSN})/R_{SNSB}$ $0.32\text{mV} < V_{CSP} - V_{CSN} < 32\text{mV}$                                          |   | -0.15<br>-1.25 | 1.466                 | 0.15<br>1.25 | μV /LSB<br>mV<br>%rdng    |

| $I_{IN} (V_{CLP} - V_{CLN})$                                                   | Resolution<br>Offset Error<br>Span Error                                        | $I_{\text{IN}} = (V_{\text{CLP}} - V_{\text{CLN}})/R_{\text{SNSI}}$ $0.32\text{mV} < V_{\text{CLP}} - V_{\text{CLN}} < 32\text{mV}$ |   | -0.15<br>-1.25 | 1.466                 | 0.15<br>1.25 | μV/LSB<br>mV<br>%rdng     |

| V <sub>IN</sub>                                                                | Resolution<br>Offset Error<br>Span Error                                        | 3V < V <sub>IN</sub> < 35V                                                                                                          |   | -25<br>-1      | 1.649                 | 25<br>1      | mV/LSB<br>mV<br>%rdng     |

| V <sub>BATSENS</sub> +<br>(Per cell_count)                                     | Resolution<br>Offset Error<br>Span Error                                        | 2V < V <sub>BATSENS</sub> + < 4.2V                                                                                                  |   | -10<br>-1      | 192.4                 | 10<br>1      | μV/LSB<br>mV<br>%rdng     |

| V <sub>OUT</sub>                                                               | Resolution<br>Offset Error<br>Span Error                                        | 3V < V <sub>OUT</sub> < 35V                                                                                                         |   | -25<br>-1      | 1.653                 | 25<br>1      | mV/LSB<br>mV<br>%rdng     |

| V <sub>NTC</sub> /V <sub>NTCBIAS</sub>                                         | Resolution<br>Offset Error<br>Span Error                                        | 0 < V <sub>NTC</sub> /V <sub>NTCBIAS</sub> < 1                                                                                      |   | -1<br>-1       | 45.833                | 1 1          | μV/V/LSB<br>mV/V<br>%rdng |

| T_die                                                                          | Resolution<br>Offset                                                            |                                                                                                                                     |   |                | 0.0215<br>-264.4      |              | °C/LSB<br>°C              |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full specified operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 4).  $V_{IN} = 18V$ , DVCC = 3.3V,  $R_{SNSI} = 10m\Omega$ , RSNSB =  $10m\Omega$  unless otherwise noted.

| SYMBOL                   | PARAMETER                                          |                                   | MIN | TYP | MAX       | UNITS |                    |

|--------------------------|----------------------------------------------------|-----------------------------------|-----|-----|-----------|-------|--------------------|

| Serial Port, SI          | DA, SCL, SMBALERT                                  |                                   |     | ı   |           |       |                    |

| DV <sub>CC</sub>         | Logic Reference Level                              |                                   | •   | 1.8 |           | 5.5   | V                  |

| I <sub>DVCCQ</sub>       | DV <sub>CC</sub> Current                           | SCL/SDA = DV <sub>CC</sub> , 0kHz |     |     | 0         |       | μА                 |

| ADDRESS                  | I <sup>2</sup> C Address                           |                                   |     | 0b  | 1101000[F | R/W]  |                    |

| V <sub>IHI2C</sub>       | Input High Threshold                               |                                   |     | 70  |           |       | % DV <sub>CC</sub> |

| V <sub>ILI2C</sub>       | Input Low Threshold                                |                                   |     |     |           | 30    | % DV <sub>CC</sub> |

| V <sub>OLI2C</sub>       | Digital Output Low (SDA/SMBALERT)                  | I <sub>SDA/SMBALERT</sub> = 3mA   |     |     |           | 400   | mV                 |

| F <sub>SCL</sub>         | SCL Clock Frequency                                |                                   |     |     |           | 400   | kHz                |

| $t_{LOW}$                | LOW Period of SCL Clock                            |                                   |     | 1.3 |           |       | μs                 |

| t <sub>HIGH</sub>        | HIGH Period of SCL Clock                           |                                   |     | 0.6 |           |       | μs                 |

| t <sub>BUF</sub>         | Bus Free Time Between Start and Stop<br>Conditions |                                   |     | 1.3 |           |       | μs                 |

| t <sub>HD,STA</sub>      | Hold Time, After (Repeated) Start<br>Condition     |                                   |     | 0.6 |           |       | μs                 |

| t <sub>SU,STA</sub>      | Setup Time after a Repeated Start<br>Condition     |                                   |     | 0.6 |           |       | μs                 |

| t <sub>SU,STO</sub>      | Stop Condition Set-Up Time                         |                                   |     | 0.6 |           |       | μs                 |

| t <sub>HD,DAT(OUT)</sub> | Output Data Hold Time                              |                                   |     | 0   |           | 900   | ns                 |

| t <sub>HD,DAT(IN)</sub>  | Input Data Hold Time                               |                                   |     | 0   |           |       | ns                 |

| t <sub>SU,DAT</sub>      | Data Set-Up Time                                   |                                   |     | 100 |           |       | ns                 |

| t <sub>SP</sub>          | Input Spike Suppression Pulse Width                |                                   |     |     |           | 50    | ns                 |

| SYNC Pin                 |                                                    |                                   |     |     |           |       |                    |

| VIHSYNC                  | Input High Threshold                               |                                   | •   | 1.5 |           |       | V                  |

| VILSYNC                  | Input Low Threshold                                |                                   | •   |     |           | 0.2   | V                  |

| Pin Leakages             | (NTC, CELLSO, CELLS1, SDA, SCL, SYNC,              | SMBALERT)                         | ·   |     |           |       |                    |

|                          | Pin Current                                        |                                   |     | -50 |           | 50    | nA                 |

|                          |                                                    |                                   |     |     |           |       |                    |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LTC4162 includes over-temperature protection that is intended to protect the device during momentary overload conditions. The maximum rated junction temperature will be exceeded when this protection is active. Continuous operation above the specified absolute maximum operating junction temperature may impair device reliability or permanently damage the device.

**Note 3:** The safety current limit features of this part are intended to protect the IC from short term or intermittent fault conditions. Continuous operation above the maximum specified pin current may result in device degradation or failure.

**Note 4:** The E-grade is tested under pulsed load conditions such that  $T_J \approx T_A$ . The E-grade is guaranteed to meet specifications from

0°C to 85°C junction temperature. Specifications over the -40°C to 125°C operating junction temperature range are assured by design, characterization, and correlation with statistical process controls. The I-grade is guaranteed over the full -40°C to 125°C operating junction temperature range. The junction temperature ( $T_J$ ) is calculated from the ambient temperature ( $T_A$ ) and power dissipation ( $P_D$ ) according to the formula  $T_J = T_A + (P_D \bullet \theta J_A)$ . Note that the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal resistance and other environmental factors.

**Note 5:** Charge Current is given by the charger servo voltage,  $V_{CSP-CSN}$ , divided by the charge current setting resistor  $R_{SNSB}$ . Errors in the value of the external resistor contribute directly to the total charge current error.

**Note 6:** Input Current is given by the  $V_{CLP-CLN}$  servo voltage divided by the input current setting resistor  $R_{SNSI}$ . Errors in the value of the external resistor contribute directly to the total input current error.

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25$ °C, unless otherwise noted.

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25$ °C, unless otherwise noted.

Rev A

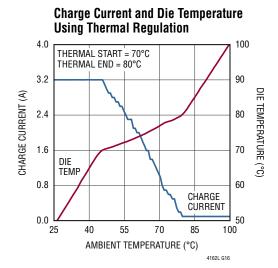

4162L G15

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25$ °C, unless otherwise noted.

# PIN FUNCTIONS

**BOOST (Pin 1):** Gate-Drive bias for the high side switch in the switching regulator. This pin provides a pumped bias voltage relative to SW. The voltage on this pin is charged up through an internal diode from INTV<sub>CC</sub>. A 22nF multilayer ceramic capacitor is required from SW to BOOST.

**INTV<sub>CC</sub> (Pin 2):** Bypass pin for the internal 5V regulator. This regulator provides power to the internal analog circuitry. A  $4.7\mu F$  multilayer ceramic capacitor is required from INTV<sub>CC</sub> to GND.

$V_{OUTA}$  (Pin 3): Analog system power pin.  $V_{OUTA}$  powers the majority of circuits on the LTC4162. A 0.1µF multilayer ceramic capacitor is required from  $V_{OUTA}$  to GND.

**CLN (Pin 4):** Connection point for the negative terminal of the sense resistor that measures and regulates input current by limiting charge current.

**CLP (Pin 5):** Connection point for the positive terminal of the sense resistor that measures and regulates input current by limiting charge current.

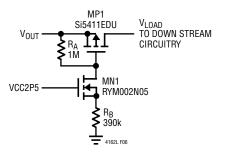

**INFET (Pin 6):** Gate control output pin for an input reverse blocking external N-channel MOSFET between  $V_{IN}$  and  $V_{OUT}$ .

$V_{IN}$  (Pin 7): Supply voltage detection and INFET charge pump supply for the INFET/BATFET PowerPath. When voltage at  $V_{IN}$  is detected as being high enough to charge a battery, the INFET charge-pump is activated and the BATFET charge-pump is deactivated thereby powering  $V_{OUTA}$  from the input supply through an external NMOS transistor and also starting a charge cycle. A  $0.1\mu F$  multilayer ceramic capacitor is required from  $V_{IN}$  to GND.

**VCC2P5 (Pin 8):** Bypass pin for the internal 2.5V regulator. This regulator provides power to the internal logic circuitry. A 1µF multilayer ceramic capacitor is required from VCC2P5 to GND.

NTCBIAS (Pin 9): NTC thermistor bias output. Connect a low temperature coefficient bias resistor between NTCBIAS and NTC, and a thermistor between NTC and GND. The bias resistor should be equal in value to the nominal value of the thermistor. The LTC4162 applies 1.2V to this pin during NTC measurement and expects a thermistor  $\beta$  value of 3490K. Higher  $\beta$  value thermistors can be used with simple circuit modifications.

**NTC (Pin 10):** Thermistor input. The NTC pin connects to a negative temperature coefficient thermistor to monitor the temperature of the battery. The voltage on this pin is digitized by the analog to digital converter to qualify battery charging and is available for readout via the I<sup>2</sup>C port. A low drift bias resistor is required from NTCBIAS to NTC and a thermistor is required from NTC to ground.

$R_T$  (Pin 11): Switching regulator frequency control pin. The  $R_T$  pin controls the switching regulator's internal oscillator frequency by placing a resistor from  $R_T$  to GND.

**SMBALERT** (**Pin 12**): Interrupt output. This open drain output pulls low when one or more of the programmable alerts is triggered.

**SCL** (**Pin 13**): Open drain clock input for the I<sup>2</sup>C port. The I<sup>2</sup>C port input levels are scaled with respect to DV<sub>CC</sub> for I<sup>2</sup>C compliance.

**SDA (Pin 14):** Open drain data input/output for the I<sup>2</sup>C port. The I<sup>2</sup>C port input levels are scaled with respect to DV<sub>CC</sub> for I<sup>2</sup>C compliance.

**DV<sub>CC</sub> (Pin 15):** Logic supply for the I<sup>2</sup>C port. DV<sub>CC</sub> sets the reference level of the SDA and SCL pins for I<sup>2</sup>C compliance. It should be connected to the same power supply as the SDA and SCL pull up resistors.

**SYNC (Pin 16):** Optional external clock input for the switching battery charger. The switching battery charger will lock to a square wave or pulse on this pin that is close to the frequency programmed by the  $R_T$  pin. Ground SYNC if this feature is not needed.

# PIN FUNCTIONS

**CELLSO (Pin 17):** Cell count selection pin. Used in combination with CELLS1, this pin sets the total number of series cells to be charged. The pin should be strapped to either INTV<sub>CC</sub>, VCC2P5 or GND to represent one of three possible states. See Table 5.

**CELLS1 (Pin 18):** Cell count selection pin. Used in combination with CELLSO, this pin sets the total number of series cells to be charged. The pin should be strapped to either INTV<sub>CC</sub>, VCC2P5 or GND to represent one of three possible states. See Table 5.

BATSENS+ (Pin 19): Positive terminal battery sense pin. BATSENS+ should Kelvin sense the positive terminal of the battery for optimized charging. A 10µF multilayer ceramic capacitor is required from BATSENS+ to ground.

**CSN (Pin 20):** Connection point for the negative terminal of the current sense resistor used to measure and limit charge current.

**CSP** (Pin 21): Connection point for the positive terminal of the current sense resistor used to measure and limit charge current.

**BATFET (Pin 22):** Gate control pin for a reverse blocking external N-channel MOSFET between the battery and V<sub>OLIT</sub>.

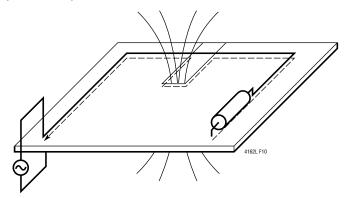

**PGND** (Pins 23,24): Power ground pins. These pins should be connected to a copper pour that forms the return for the  $V_{OUT}$  bypass capacitor on the top layer of the printed circuit board.

**SW** (**Pin 25**, **26**): Switching regulator power transmission pins. The SW pins deliver power from the  $V_{OUT}$  pins to the battery via the step-down switching regulator. An inductor should be connected from SW to a sense resistor at CSP. See the Applications Information section for a discussion of inductor value and current rating.

$V_{OUT}$  (Pin 27, 28): Switching regulator input pins. The  $V_{OUT}$  pins deliver power to the switching charger. Having extremely high frequency current pulses, bypassing of the  $V_{OUT}$  pins should take precedence over all other PCB layout considerations. A bypass capacitor of  $10\mu F$  is a good starting point.

**AGND (Exposed PAD, Pin 29):** Analog ground pin. This is the ground pin used to return all of the analog circuitry inside the LTC4162 and should be connected to an analog ground pour that is common with PGND (pins 23 and 24). It should also be connected to a ground plane on layer 2 of the PCB to which all of the analog components return such as the  $R_T$  resistor and the INTV<sub>CC</sub> and VCC2P5 bypass capacitors.

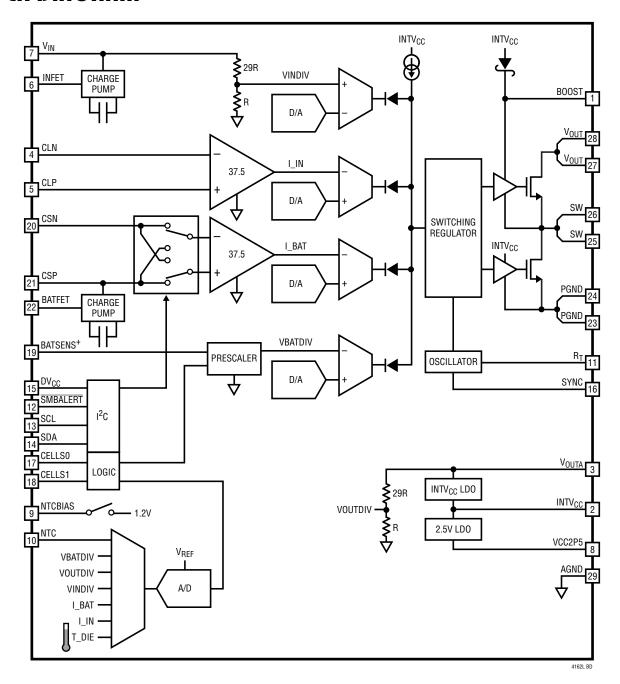

# **BLOCK DIAGRAM**

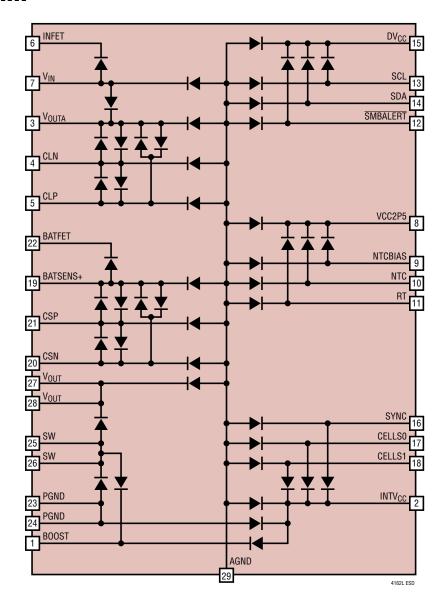

# **ESD DIAGRAM**

# TIMING DIAGRAM

#### I<sup>2</sup>C SMBus Legend

START CONDITION S

REPEATED START CONDITION Sr

Rd

READ (BIT VALUE OF 1)

WRITE (BIT VALUE OF 0) Wr

ACKNOWLEDGE Α

Ν NACK

STOP CONDITION

PEC\* PACKET ERROR CODE

MASTER TO SLAVE

SLAVE TO MASTER

#### **SMBus WRITE WORD PROTOCOL**

|   |   |               |    |   |              |   |               | _ |                |   | _ |

|---|---|---------------|----|---|--------------|---|---------------|---|----------------|---|---|

| ı | S | SLAVE ADDRESS | Wr | Α | COMMAND CODE | Α | DATA BYTE LOW | Α | DATA BYTE HIGH | Α | Р |

#### SMBus WRITE WORD WITH PEC PROTOCOL

| S   SLAVE ADDRESS   Wr   A   COMMAND CODE   A   DATA BYTE LOW   A   DATA BYTE HIGH   A   PEC* |

|-----------------------------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------------------|

#### **SMBus READ WORD PROTOCOL**

|  | S | SLAVE ADDRESS | Wr | Α | COMMAND CODE | Α | Sr | SLAVE ADDRESS | Rd | Α | DATA BYTE LOW | Α | DATA BYTE HIGH | N | Р |

|--|---|---------------|----|---|--------------|---|----|---------------|----|---|---------------|---|----------------|---|---|

|--|---|---------------|----|---|--------------|---|----|---------------|----|---|---------------|---|----------------|---|---|

### SMBus READ WORD WITH PEC PROTOCOL

| S | SLAVE ADDRESS | Wr | Α | COMMAND CODE | Α | Sr | SLAVE ADDRESS | Rd | Α | DATA BYTE LOW | Α | DATA BYTE HIGH | Α | PEC* | N | Р |

|---|---------------|----|---|--------------|---|----|---------------|----|---|---------------|---|----------------|---|------|---|---|

|   |               |    |   |              |   |    |               |    |   |               |   |                |   |      |   |   |

#### **SMBus ALERT RESPONSE ADDRESS PROTOCOL**

S ALERT RESPONSE ADDRESS Rd A DEVICE ADDRESS Rd N P

#### SMBus ALERT RESPONSE ADDRESS PROTOCOL WITH PEC

| S | ALERT RESPONSE ADDRESS | Rd | Α | DEVICE ADDRESS | Rd | Α | PEC* | N | Р |

|---|------------------------|----|---|----------------|----|---|------|---|---|

|   |                        |    |   |                |    |   |      |   |   |

<sup>\*</sup>USE OF PACKET ERROR CHECKING IS OPTIONAL

#### Introduction

The LTC4162 is an advanced power manager and switching battery charger utilizing a high efficiency synchronous step-down switching regulator.

Using multiple feedback control signals, power is delivered from the input to the battery by a 1.5MHz constant-frequency step-down switching regulator. The switching regulator reduces output power in response to one of its four regulation loops including battery voltage, battery charge current, input current and input voltage.

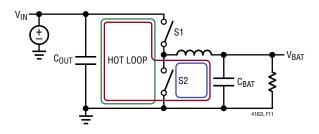

The switching regulator is designed to efficiently transfer power from a variety of possible sources, such as USB ports, wall adapters and solar panels, to a battery while minimizing power dissipation and easing thermal budgeting constraints. Since a switching regulator conserves power, the LTC4162 allows the charge current to exceed the source's output current, making maximum use of the allowable power for battery charging without exceeding the source's delivery specifications. By incorporating input voltage and system current measurement and control systems, the switching charger ports seamlessly to these sources without requiring application software to monitor and adjust system loads. By decoupling the system load from the battery and prioritizing power to the system, the instant-on PowerPath architecture ensures that the system is powered upon input power arrival, even with a completely dead battery.

Two low power charge pumps drive external MOSFETs to provide low loss power paths from the input supply and battery to the system load while preventing the system node from back-driving the input supply or overcharging the battery. The power path from the battery to the system load guarantees that power is available to the system even if there is insufficient or absent power from  $V_{IN}$ . A wide range of input current settings as well as battery charge current settings are available by software control and by choosing the values of input and charge current sense resistors  $R_{SNSI}$  and  $R_{SNSR}$ .

A measurement subsystem periodically monitors and reports on a large collection of system parameters via the I<sup>2</sup>C port. An interrupt subsystem can be enabled to alert the host microprocessor of various status change events

so that system parameters can be varied as needed. All of the status change events are maskable for maximum flexibility. For example, features such as battery presence detection and battery impedance measurement are easily enabled.

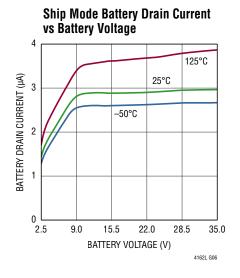

To eliminate battery drain between manufacture and sale, a ship-and-store feature reduces the already low battery drain current even further.

The input undervoltage control loop can be engaged to keep the input voltage from decreasing beyond a minimum level when a resistive cable or power limited supply such as a solar panel is providing input power. A maximum power point tracking algorithm using this control loop can be deployed to maximize power extraction from solar panels and other resistive sources.

Finally, the LTC4162 has a digital subsystem that provides substantial adjustability so that power levels and status information can be controlled and monitored via the conventional  $I^2C$  port.

# LTC4162 Digital System Overview

The LTC4162 contains an advanced digital system which can be accessed using the I<sup>2</sup>C port. Use of the I<sup>2</sup>C port is optional, it can be used extensively in the application or not at all, as dictated by the application requirements. Cell count, charge current, input current regulation and switching charger frequency are all externally configurable without using the I<sup>2</sup>C port. For applications requiring the LTC4162's advanced digital features, the I<sup>2</sup>C port provides a means to use status and A/D telemetry data from the measurement system, monitor charger operation, configure charger settings (e.g. charge voltage, charge current, temperature response, termination algorithm, etc), enable, disable, read and clear alerts, activate the low power ship mode, and enable/disable the battery charger.

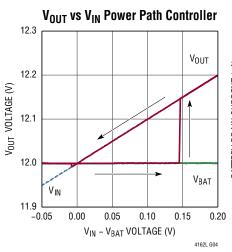

#### **Power Path Controller**

The LTC4162 features input and output N-channel MOS-FET charge pump gate drivers. These drivers make up a dual unidirectional power path system that allows power to be delivered to the system load by either the input supply or the battery, whichever is greater. Only one of

the external MOSFETs will be enabled at a time. If  $V_{IN}$  is more than 150mV above BATSENS+, the MOSFET from the input to the system load will be enabled and the one from the system load to BATSENS+ will block conduction preventing overcharging of the battery. If  $V_{IN}$  falls more than 20mV below BATSENS+ the MOSFET from the input supply to the system load will be disabled preventing reverse conduction and the MOSFET from BATSENS+ to the system load will be enabled powering downstream circuitry from the battery. It is important not to back drive  $V_{OUT}$  as one or the other of the power path MOSFETs will always be enabled.

#### **Step Down Switching Battery Charger**

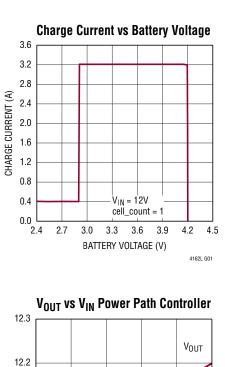

The LTC4162's battery charger is based on a very efficient synchronous step down switching regulator. As with any modern battery charger, the LTC4162 incorporates both constant-current and constant-voltage feedback control loops to prevent overcharging. The switching charger can charge either a single cell or a battery of up to eight series Lithium-Ion/Polymer cells.

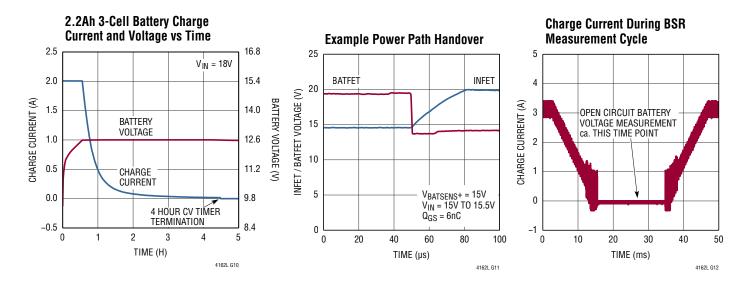

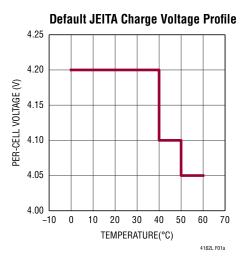

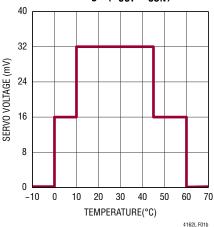

Normal charging begins with a constant current until the battery reaches its target voltage. The charge current is determined by the combination of the sense resistor, R<sub>SNSB</sub>, placed in series with the inductor and the servo control voltage set by either icharge jeita 2 through icharge\_jeita\_6 with en\_jeita set or just charge current setting if en jeita is cleared. An internal soft-start algorithm ramps up the charge current setting from zero to its present setting. Once the battery voltage reaches the programmed voltage limit the constant-current control loop hands off to the constant-voltage control loop. The final battery voltage is set with the combination of either vcharge\_jeita\_2 through vcharge\_jeita\_6 with en\_jeita set or with just vcharge setting if en jeita is cleared. The cell count, controlled by the CELLSO and CELLS1 pins, is a charge voltage multiplier so that multiple series cells can be charged.

If en\_jeita is set, the charge current is given by the expression:

$$I_{CHARGE} = (ich arge_jeita_x + 1) \frac{1mV}{R_{SNSB}}$$

where icharge\_jeita\_2 through icharge\_jeita\_6 each range from 0 to 31.

If en\_jeita is not set:

$$I_{CHARGE} = (charge\_current\_setting + 1) \frac{1mV}{R_{SNSB}}$$

where charge\_current\_setting ranges from 0 to 31.

If en\_jeita is set, the charge voltage is given by the expression:

where vcharge\_jeita\_2 through vcharge\_jeita\_6 each range from 0 to 31.

If en\_jeita is not set:

$$V_{CHARGE} = (3.8125V + 12.5mV \cdot vcharge\_setting) \cdot cell count$$

where vcharge setting ranges from 0 to 31.

Beyond the conventional constant-current and constantvoltage control loops, the LTC4162 also has the ability to monitor and control both input current and input voltage, regulating battery charge power based on any one of these four control loops. Power limit is prioritized based on the lowest set-point of the group. For example, if the combined system load plus battery charge current is large enough to cause the switching charger to reach the programmed input current limit, the input current limit will reduce charge current to limit the voltage across the input sense resistor, R<sub>SNSI</sub>, to the iin\_limit\_target. Even if the charge current is programmed to exceed the allowable input current, the input current due to charge current will not be violated; the charger will reduce its current as needed. Similarly, the input voltage limit loop, controlled by input undervoltage setting, can be used to prevent resistive power sources such as a solar panel from dragging the input voltage down below its under-voltage lockout level.

Only target values can be programmed with the I<sup>2</sup>C port. The LTC4162 uses the target values as a starting point from which the charging algorithms calculate the actual values to be applied to the DACs to support functions such as

Rev A

temperature compensated charge voltages and currents, maximum power point tracking, charger soft starting, etc. The target value registers are read/write whereas the actual DAC value registers, icharge\_dac, vcharge\_dac, iin\_limit\_dac and input\_undervoltage\_dac are read only.

Due to its all NMOS switch design, a small charge pump capacitor is required from SW to BOOST to provide high side boosted drive for the top switch.

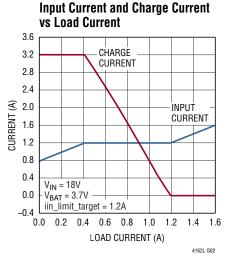

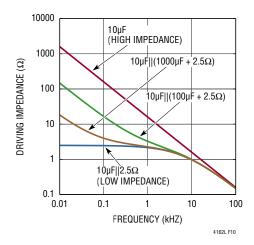

#### **Input Current Regulation**

Input current control limits loading on the input source during periods of high system demand by sacrificing charge current. Note that the LTC4162 only has the authority to reduce charge current to zero and cannot further reduce input current below the system load current. The input current limit is controlled by a combination of the sense resistor,  $R_{SNSI}$ , from CLP to CLN and either the default 32mV servo voltage or a lower value set by iin\_limit\_target. The servo voltage across the sense resistor divided by the resistor's value determines the input current regulation set point. A  $10m\Omega$  resistor, for example, would have an upper input current limit of 3.2A using the default 32mV servo voltage. iin\_limit\_target has 6 bit resolution giving adjustable values from  $500\mu V$  to 32mV in  $500\mu V$  steps and can be calculated in Amperes, by the following expression:

$$I_{INLIM} = (iin_limit_target + 1) \frac{500\mu V}{R_{SNSI}}$$

$where \ iin\_limit\_target \ ranges \ from \ integer \ values \ of \ 0 \ to \ 63.$

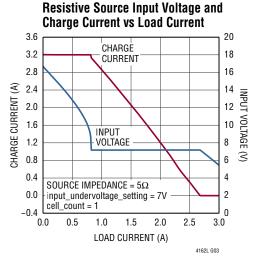

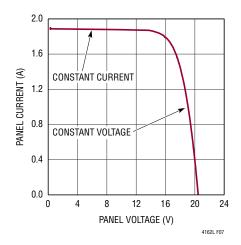

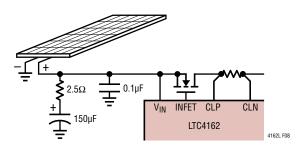

# Input Undervoltage Regulation and Solar Panel Maximum Power Point Tracking (MPPT)

The LTC4162 also contains an undervoltage control loop that allows it to tolerate a resistive connection to the input power source by automatically reducing charge current as the  $V_{IN}$  pin drops to input\_undervoltage\_setting. This circuit helps prevent UVLO oscillations by linearly regulating the input voltage above the LTC4162's undervoltage lockout level.

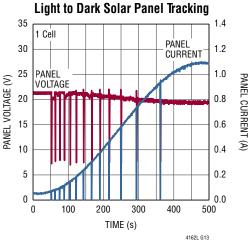

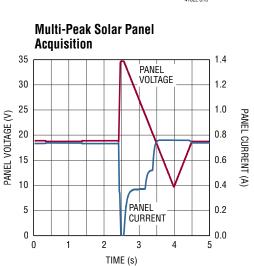

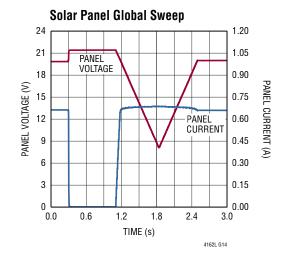

Optionally, the LTC4162 includes a maximum power point tracking (MPPT) algorithm to find and track the input\_undervoltage\_dac value that delivers the maximum charge current to the battery. If mppt\_en is set, the MPPT algorithm performs a global sweep of input undervoltage dac values, measuring battery charge current at each setting. Once the sweep is complete, the LTC4162 applies the input\_undervoltage\_dac value corresponding to the maximum battery charge current ibat (i.e. the maximum power point). The LTC4162 then tracks small changes in the maximum power point by slowly dithering the input undervoltage dac. The LTC4162 performs a new global sweep of input undervoltage dac values every 15 minutes, applies the new maximum power point, and resumes dithering at that point. Alternatively, the global sweep will run immediately, bypassing the 15 minute wait, if ibat changes by more that 25%. With mppt\_en, a solar panel can be used as a suitable power source for charging a battery and powering a load. The MPPT algorithm may not work for all solar panel applications and does not have to be used. Alternatively a solar panel can be used without the MPPT algorithm by setting the input undervoltage setting value to match the optimum loaded solar panel voltage, but significant shadows or drops in light will likely result in suboptimum power delivery.

Note that, due to the Power Path topology, current can flow from the input to the system load without being controlled by the LTC4162's switching charger. Therefore, the MPPT algorithm does not have full authority to track and find the maximum power point under all conditions. To obtain complete Maximum Power Point operation, it may be necessary to forgo the Power Path feature of the LTC4162 and connect the system load directly to the battery pack. In this configuration, the LTC4162 has full authority to track the maximum power point of the solar panel.

The input under voltage value, in Volts, will be given by the following expression:

V<sub>INLIM</sub> = (input\_undervoltage\_setting + 1) • 140.625mV where input\_undervoltage\_setting ranges from integer values of 0 to 255.

### **System Controls**

The switching battery charger can be disabled by setting suspend\_charger. This might be necessary, for instance, to pass USB Suspend compliance testing. suspend\_charger should be used with caution as a low battery situation could prevent the system processor from being able to clear it and may require a factory service call to remove and replace the battery.

#### **Input Overvoltage Protection**

The LTC4162 has over-voltage detection on its input. If  $V_{IN}$  exceeds approximately 38.6V as indicated by vin\_ovlo, the switching charger will stop delivering power. The charger will resume switching if  $V_{IN}$  falls below roughly 37.2V. The overvoltage detection cutoff circuit provides only modest over voltage protection and is not intended to prevent damage in all circumstances.

#### **Measurement Subsystem**

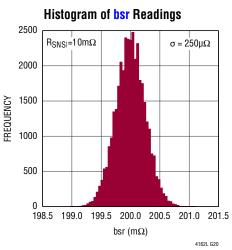

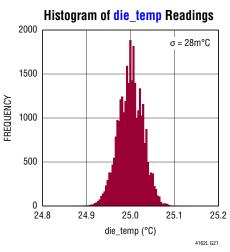

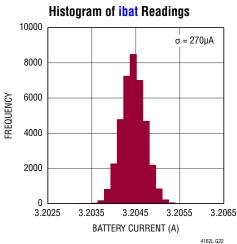

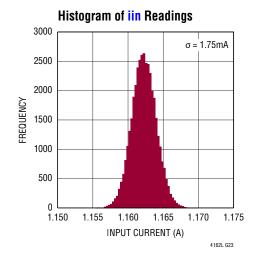

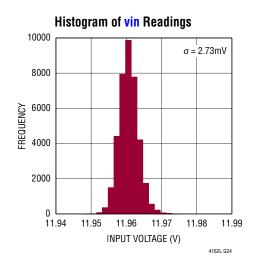

The LTC4162 includes a 16-bit  $\Delta\Sigma$  A/D converter and signal multiplexer to monitor numerous analog parameters. It can measure the voltages at vin, vbat and vout, the input current (voltage between CLP and CLN), iin, the battery charge current (voltage between CSP and CSN), ibat, the battery pack thermistor\_voltage, its own internal die\_temp and, once a charge cycle begins, the series resistance of the battery, bsr. To save battery current, the measurement system is disabled if the battery is the only source of power (vin\_gt\_vbat = 0). This can be overridden with force\_telemetry\_on. The A/D converter is automatically multiplexed between all of the measured channels and

its 16-bit signed two's complement results are stored in registers accessible via the I<sup>2</sup>C port. The seven channels measured by the ADC each take approximately 1.6ms to convert. The maximum range of the 16 bit  $\Delta\Sigma$  A/D converter is ±1.8V and it has an internal span term of 18191 counts per Volt. It measures each of the above parameters through different paths giving different sensitivity terms for each measurement as summarized in Table 1.

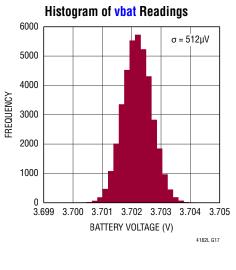

# **Battery Voltage Measurement**

Battery voltage is measured through a resistive voltage divider whose attenuation ratio is based on the cell\_count. The result is reported in vbat. The divider ratio is BAT-SENS+/(3.5 • cell\_count) making the A/D span term 3.5 • cell\_count/18191 or 192.4µV • cell\_count per LSB where cell\_count varies from 1 to 8. An alert may be set on battery voltage by setting the vbat based value vbat\_lo\_alert\_limit or vbat\_hi\_alert\_limit and setting en\_vbat\_lo\_alert or en\_vbat\_hi\_alert. These alerts are indicated by vbat\_lo\_alert or vbat\_hi\_alert and are cleared by writing them to 0.

#### **Input Voltage Measurement**

Input voltage is measured through a 30:1 resistive voltage divider making the A/D span term for input voltage measurements 30/18191 or 1.649mV/LSB and is digitized to vin. An alert may be set on input voltage by setting the value vin\_lo\_alert\_limit or vin\_hi\_alert\_limit and setting en\_vin\_lo\_alert or en\_vin\_hi\_alert. These alerts are indicated by vin\_lo\_alert and vin\_hi\_alert and are cleared by writing them to 0.

Table 1. Measurement Subsystem LSB Sizes

| MEASUREMENT        | UNITS | REGISTER SYMBOL    | LSB SIZE               | OFFSET  |

|--------------------|-------|--------------------|------------------------|---------|

| BATTERY VOLTAGE    | V     | vbat               | 192.4µV • cell_count   |         |

| INPUT VOLTAGE      | V     | vin                | 1.649mV                |         |

| OUTPUT VOLTAGE     | V     | vout               | 1.653mV                |         |

| INPUT CURRENT      | А     | iin                | 1.466µV/RSNSI          |         |

| BATTERY CURRENT    | A     | ibat               | 1.466µV/RSNSB          |         |

| DIE TEMPERATURE    | °C    | die_temp           | 0.0215°C               | 264.4°C |

| BATTERY IMPEDANCE  | Ω     | bsr                | RSNSB • cell_count/500 |         |

| THERMISTOR VOLTAGE | V     | thermistor_voltage | 45.833μV/V             |         |

Rev A

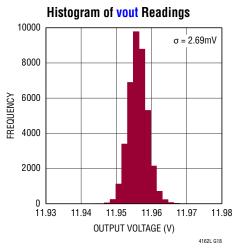

### **V<sub>OUT</sub> Voltage Measurement**

Output voltage is measured through a 30.07:1 resistive voltage divider making the A/D span term for output voltage measurements 30.07/18191 or 1.653mV/LSB and is digitized to vout. An alert may be set on output voltage by setting the value vout\_lo\_alert\_limit or vout\_hi\_alert\_limit and setting en\_vout\_lo\_alert or en\_vout\_hi\_alert. These alerts are indicated by vout\_lo\_alert and vout\_hi\_alert and are cleared by writing them to 0.

#### **Battery Current Measurement**

Battery current is measured with a current sense resistor between the CSP and CSN pins. An amplifier with a gain of 37.5 amplifies this signal and refers it to ground internally so that the A/D converter can measure it. The sensed battery current is therefore given by I<sub>BAT</sub> • R<sub>SNSB</sub> • 37.5. For a  $10m\Omega$  R<sub>SNSR</sub> current sense resistor, the A/D sensitivity is  $1/(18191 \cdot 10 \text{ m}\Omega \cdot 37.5)$  or  $146.6 \mu \text{A/LSB}$ . The battery current measurement system has a built in commutator. While charging a battery, two's complement number ibat will be positive representing current into the battery. When the battery charger is disabled or terminated, as detected by charger suspended, the commutator is activated and ibat will be negative, representing current out of the battery. An alert may be set on the ibat measurement by setting the desired value in ibat\_lo\_alert\_limit and setting en ibat lo alert. While charging, ibat lo alert limit can be used to detect when the charge current has dropped below a given threshold. When charger suspended, if set to a negative number, ibat lo alert limit can be used to detect if the battery load has exceeded a given threshold. This alert is indicated by ibat lo alert and is cleared by writing it to 0.

### **Input Current Measurement**

Input current is measured with a current sense resistor between the CLP and CLN pins. An amplifier with a gain of 37.5 amplifies this signal and refers it to ground internally so that the A/D converter can measure it. The sensed input current is therefore given by  $I_{IN} \bullet R_{SNSI} \bullet 37.5.$  For a  $10m\Omega$   $R_{SNSI}$  current sense resistor, the A/D sensitivity is  $1/(18191 \bullet 10m\Omega \bullet 37.5)$  or  $146.6\mu A/LSB$ . The input current is digitized to iin. An upper limit alert may be set

on input current by setting the value iin\_hi\_alert\_limit and setting the en\_iin\_hi\_alert. This alert is indicated by iin\_hi\_alert and is cleared by writing it to 0.

#### **Battery Series Resistance (BSR) Measurement**

The LTC4162 can optionally measure the series resistance of the battery stack or cell. If run\_bsr is set, the LTC4162 momentarily suspends the battery charger and calculates the battery series resistance by dividing the voltage change (charging vs not charging) by the measured charge current (bsr\_charge\_current).

The per-cell resistance value is reported in bsr and the charge current observed during the measurement is reported in bsr\_charge\_current. The LTC4162 automatically resets run\_bsr after the bsr measurement is complete. The total battery series resistance value is proportional to the charge current sense resistor,  $R_{\text{SNSB}}$ , as well as the cell\_count, and can be computed in  $\Omega$  from the expression:

$$R_{BAT}(\Omega) = \frac{bsr \cdot cell\_count \cdot R_{SNSB}}{500}$$

Higher bsr\_charge\_current during a bsr measurement results in a more accurate bsr measurement. Very low values of bsr\_charge\_current may adversely impact the accuracy of the bsr measurement. If charge current is less than C/10 (bsr\_charge\_current < icharge\_over\_10), bsr\_questionable will be set indicating that bsr\_charge\_current during the bsr test was less than optimum for an accurate reading. Recall that full charge current typically flows at the beginning of a charge cycle (presuming the battery is more deeply depleted) and will diminish when the charger enters the constant voltage phase of charging.

If run\_bsr is set to 1 and the battery charger is not currently running, then the LTC4162 will be queued to perform the bsr measurement only after the start of the next charge cycle. An alert can be set with en\_bsr\_done\_alert to generate a bsr\_done\_alert indicating that a bsr measurement is complete and that the result is available. A bsr\_hi\_alert may also be set on battery series impedance by writing a bsr\_hi\_alert\_limit and setting en\_bsr\_hi\_alert. Again, the bsr reading is the per-cell battery resistance and should be scaled by cell\_count or, consequently, the target total re-

sistance threshold for bsr\_hi\_alert\_limit should be divided by cell\_count before being written to bsr\_hi\_alert\_limit.

bsr\_done\_alert and bsr\_hi\_alert are cleared by writing them to 0.

### **Die Temperature Measurement**

The LTC4162 has an integrated die temperature sensor that is monitored by the A/D converter and is digitized to die\_temp. The die temperature is derived from an internal circuit and follows the equation:

$$T_{DIF}(^{\circ}C) = die_{temp} \cdot 0.0215^{\circ}C/LSB - 264.4^{\circ}C$$

An alert may be set on die temperature by setting the value die\_temp\_hi\_alert\_limit and setting en\_die\_temp\_hi\_alert. This alert is indicated by die\_temp\_hi\_alert and is cleared by writing it to 0.

To set the die\_temp\_hi\_alert\_limit, compute the threshold value from:

$$die\_temp\_hi\_alert\_limit = \frac{T_{DIE}(^{\circ}C) + 264.4^{\circ}C}{0.0215^{\circ}C/LSB}$$

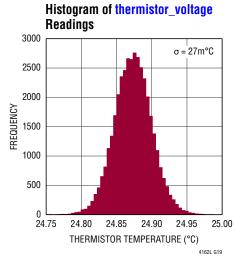

# **Battery Temperature (NTC Thermistor) Measurement**

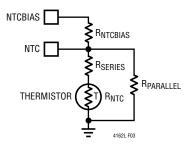

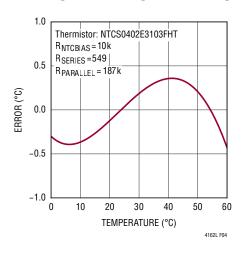

To measure the battery temperature using a thermistor, connect the thermistor, R<sub>NTC</sub>, normally being located in the battery pack, between the NTC pin and ground, and a low drift bias resistor, R<sub>NTCBIAS</sub>, between NTCBIAS and NTC. R<sub>NTCBIAS</sub> should be a 1% or better resistor with a value equal to the value of the chosen thermistor at 25°C (R25). The LTC4162 applies an excitation voltage of 1.2V to R<sub>NTCBIAS</sub> to measure the thermistor value. The thermistor measurement result is available at thermistor voltage. To minimize battery stress due to charging at temperature extremes, the LTC4162 has both a simple and a more advanced JEITA (Japan Electronics and Information Technology Industries Association) temperature qualified charging algorithm. If the application does not require temperature controlled charging, then the thermistor should be replaced with a resistor of equal value to the bias resistor R<sub>NTCRIAS</sub> to continuously simulate 25°C. If the thermistor is found to be open (thermistor\_voltage > open\_thermistor) either during the battery detection test or during charging, charger\_state will switch to bat\_missing\_fault and charging will halt. Either a thermistor\_voltage\_lo\_alert or thermistor\_voltage\_hi\_alert may be set with en\_thermistor\_voltage\_lo\_alert or en\_thermistor\_voltage\_hi\_alert, both of which are cleared by writing them to 0.

The temperature vs resistance curve of a thermistor can be obtained from thermistor manufacturers in either table form or estimated by applying the modified Steinhart-Hart equation:

$$R_{NTC} = R_{25} \cdot e^{\left(A + \frac{B}{T_C + 273.15} + \frac{C}{(T_C + 273.15)^2} + \frac{D}{(T_C + 273.15)^3}\right)}$$

Where  $R_{25}$  is the thermistor's resistance at 25°C and A, B, C and D are provided by the thermistor manufacturer and  $T_{\rm C}$  is the temperature in °C.

The temperature of the thermistor is computed from its resistance value by the complementary Steinhart-Hart expression where A1, B1, C1 and D1 are also provided by the thermistor manufacturer.

$$T_{C} = \frac{1}{A_{1} + B_{1} \ln(\frac{R_{NTC}}{R_{25}}) + C_{1} \ln^{2}(\frac{R_{NTC}}{R_{25}}) + D_{1} \ln^{3}(\frac{R_{NTC}}{R_{25}})}$$

$$-273 \cdot 15^{\circ} C$$

(1)

Alternatively, the more common but less accurate condensed version of Steinhart-Hart using the ubiquitous  $\beta$  parameter may be employed:

$$R_{NTC} = R_{25} \cdot e^{-\beta_{25/85} (\frac{1}{298.15^{\circ}C} - \frac{1}{T_{C} + 273.15^{\circ}C})}$$

Where again,  $R_{25}$  is the thermistor's resistance at 25°C and several  $\beta$  values are provided by the thermistor manufacturer, one for each of a number of temperature ranges.

The inverse  $\beta$  form is:

$$T_{\rm C} = \frac{\beta_{25/85}}{\ln(\frac{R_{\rm NTC}}{R_{25}}) + \frac{\beta_{25/85}}{298.15^{\circ}\rm C}} - 273.15^{\circ}\rm C$$

(2)

Rev A

The LTC4162 thermistor measurement system is designed specifically for a thermistor with a  $\beta_{25/85}$  value of 3490K and returns thermistor\_voltage where:

thermistor\_voltage =

$$18191 \cdot 1.2 \cdot \frac{R_{NTC}}{R_{NTC} + R_{NTCBIAS}}$$

where typically  $R_{NTCBIAS}$  is set equal to  $R_{25}$ , the 25°C value of the thermistor. To arrive at the thermistor's temperature in °C from thermistor\_voltage substitute  $R_{NTC}$  from:

$$R_{NTC} = R_{NTCBIAS} \cdot \frac{thermistor\_voltage}{18191 \cdot 1.2 - thermistor\_voltage}$$

into Equation 1 or Equation 2.

For thermistors with a  $\beta_{25/85}$  value higher than 3490K see Alternate Thermistors and Biasing in the Applications Information section.

#### **Output Current Measurement**

There is no sense resistor dedicated to measuring output current but its value can be obtained nonetheless. Output current is delivered from the input supply if vin\_gt\_vbat is true and from the battery if it is false.

If vin\_gt\_vbat is true and the battery charger is enabled (en\_chg is true) then the input current measurement will be the sum of current to the switching charger and the output load. In this instance the switching charger will need to be disabled with suspend\_charger to obtain an output current reading. It's also possible that the charger may already be terminated. If en\_chg is false then set telemetry\_speed to tel\_high\_speed, wait 20ms or more, and record iin as output current. If en\_chg is true then set both suspend\_charger and force\_telemetry\_on to 1 and telemetry\_speed to tel\_high\_speed, wait 20ms or more for at least one telemetry cycle, and again record iin as output current. suspend\_charger should then be cleared. Note that suspending the charger resets the tchargetimer and tcvtimer termination timers to 0.

On the other hand if vin\_gt\_vbat is false then the output current will be delivered from the battery and its value can be obtained from –ibat. Since vin\_gt\_vbat is low, the telemetry system will be disabled and the ibat reading will be stale. To enable the telemetry system, set force\_telemetry\_on to 1

and telemetry\_speed to tel\_high\_speed. telemetry\_valid indicates when fresh telemetry readings are available. To avoid polling for telemetry\_valid a telemetry\_valid\_alert can be set with en\_telemetry\_valid\_alert. Once the reading is obtained, force\_telemetry\_on can be cleared or telemetry\_speed set to tel\_low\_speed for power savings.

#### **Low Power Telemetry**

If input power is available (vin\_gt\_vbat = 1), and the battery is being charged, the telemetry system will be in its high speed mode returning results at a rate of roughly once per 11ms. If, on the other hand, charging has terminated normally or paused due to battery temperature out of range, the telemetry system will drop back to a rate of about once every 5 seconds to save power. When input power is not available (vin\_gt\_vbat = 0) it is still possible to collect telemetry data by setting force\_telemetry\_on. To save power in this mode the telemetry system will default to the lower speed 5 second mode. To force the higher telemetry rate, and suffer the higher quiescent current of roughly 2.5mA, the telemetry\_speed can be set to the higher ~11ms rate by setting it to tel\_high\_speed.

# **Configurable Limit Alert Subsystem**

The I<sup>2</sup>C port also supports the SMBus SMBALERT protocol, including the Alert Response Address. An alert can optionally be generated if a monitored parameter exceeds a programmed limit or if a selected battery charger\_state or any of a wide number of other charge\_status change or fault events occur. This off-loads much of the continuous monitoring from the system's microcontroller and onto the LTC4162; reducing bus traffic and microprocessor load.

The SMBALERT pin is asserted (pulled low) whenever an enabled alert occurs. After asserting an interrupt, the LTC4162 responds to the host's Alert Response Address (ARA = 0b0001100[1]) with its own read address. If another part with a pending alert and a lower address also responds, that part wins the arbitration and the LTC4162 will stop responding to this ARA, keeping its SMBALERT pin asserted. Only a response of the LTC4162's complete read address will clear the LTC4162's SMBALERT signal. This allows the system to have many parts share a common interrupt line. If multiple parts are asserting the SMBALERT

# **Table 2. Summary of Limit Alerts Registers**

| ALERT VALUE SETTING (0x01 - 0x0C) | EN_LIMIT_ALERTS_REG LIMIT_ALERTS_REG |                             |  |

|-----------------------------------|--------------------------------------|-----------------------------|--|

| vin_hi_alert_limit                | en_vin_hi_alert                      | vin_hi_alert                |  |

| vin_lo_alert_limit                | en_vin_lo_alert                      | vin_lo_alert                |  |

| thermistor_voltage_hi_alert_limit | en_thermistor_voltage_hi_alert       | thermistor_voltage_hi_alert |  |

| thermistor_voltage_lo_alert_limit | en_thermistor_voltage_lo_alert       | thermistor_voltage_lo_alert |  |

| bsr_hi_alert_limit                | en_bsr_hi_alert                      | bsr_hi_alert                |  |

| die_temp_hi_alert_limit           | en_die_temp_hi_alert                 | die_temp_hi_alert           |  |

| ibat_lo_alert_limit               | en_ibat_lo_alert                     | ibat_lo_alert               |  |

| iin_hi_alert_limit                | en_iin_hi_alert                      | iin_hi_alert                |  |

| vout_hi_alert_limit               | en_vout_hi_alert                     | vout_hi_alert               |  |

| vout_lo_alert_limit               | en_vout_lo_alert                     | vout_lo_alert               |  |

| vbat_hi_alert_limit               | en_vbat_hi_alert                     | vbat_hi_alert               |  |

| vbat_lo_alert_limit               | en_vbat_lo_alert                     | vbat_lo_alert               |  |

| NA                                | en_bsr_done_alert                    | bsr_done_alert              |  |

| NA                                | telemetry_valid_alert                |                             |  |

# **Table 3. Summary of Charger State Alerts**

| CHARGER_STATE_REG       | EN_CHARGER_STATE_ALERTS_REG                              | CHARGER_STATE_ALERTS_REG      |  |

|-------------------------|----------------------------------------------------------|-------------------------------|--|

| bat_detect_failed_fault | en_bat_detect_failed_fault_alert                         | bat_detect_failed_fault_alert |  |

| battery_detection       | en_battery_detection_alert                               | battery_detection_alert       |  |

| charger_suspended       | en_charger_suspended_alert                               | charger_suspended_alert       |  |

| precharge               | en_precharge_alert                                       | precharge_alert               |  |

| cc_cv_charge            | en_cc_cv_charge_alert                                    | cc_cv_charge_alert            |  |

| ntc_pause               | en_ntc_pause_alert                                       | ntc_pause_alert               |  |

| timer_term              | en_timer_term_alert                                      | timer_term_alert              |  |

| c_over_x_term           | en_c_over_x_term_alert                                   | c_over_x_term_alert           |  |

| max_charge_time_fault   | en_max_charge_time_alert                                 | max_charge_time_fault_alert   |  |

| bat_missing_fault       | en_bat_missing_fault_alert                               | bat_missing_fault_alert       |  |

| bat_short_fault         | ort_fault en_bat_short_fault_alert bat_short_fault_alert |                               |  |

#### **Table 4. Summary of Charger Status Alerts**

| CHARGE_STATUS_REG  | EN_CHARGE_STATUS_ALERTS_REG | CHARGE_STATUS_ALERTS_REG |

|--------------------|-----------------------------|--------------------------|

| constant_voltage   | en_constant_voltage_alert   | constant_voltage_alert   |

| constant_current   | en_constant_current_alert   | constant_current_alert   |

| iin_limit_active   | en_iin_limit_active_alert   | iin_limit_active_alert   |

| vin_uvcl_active    | en_vin_uvcl_active_alert    | vin_uvcl_active_alert    |

| thermal_reg_active | en_thermal_reg_active_alert | thermal_reg_active_alert |

| ilim_reg_active    | en_ilim_reg_active_alert    | ilim_reg_active_alert    |

signal then multiple reads from the ARA are needed. For more information refer to the SMBus specification.

After the ARA process is complete, alert bits can be cleared by individually writing them to 0 and writing the remaining bits in the register to 1. This preserves any other pending alert bits as writing 1s to the alert registers are ignored.

#### **Series Cell Count Selection**

Cell count selection of up to eight series cells is made via the CELLS1 and CELLS0 pins. CELLS1 and CELLS0 should be pin strapped to either GND, VCC2P5, or INTV $_{CC}$  to make the cell\_count selection (see Table 5). For added safety, cell\_count can be read back from the I $^2$ C port. The GND/GND combination will result in a cell\_count\_err and will inhibit charging. Note that the number of cells multiplied by their expected maximum cell voltage during charging cannot exceed  $V_{IN}-V_{IN}$  DUVLO.

Table 5. CELLSO and CELLS1 Pin Mapping to Series Cell Count

| CELLS1             | CELLS0             | cell_count |

|--------------------|--------------------|------------|

| INTV <sub>CC</sub> | INTV <sub>CC</sub> | 1          |

| INTV <sub>CC</sub> | VCC2P5             | 2          |

| INTV <sub>CC</sub> | GND                | 3          |

| VCC2P5             | INTV <sub>CC</sub> | 4          |

| VCC2P5             | VCC2P5             | 5          |

| VCC2P5             | GND                | 6          |

| GND                | INTV <sub>CC</sub> | 7          |

| GND                | VCC2P5             | 8          |

When charging stacks of two or more cells in series it is important to consult with the battery manufacturer to ascertain requirements pertaining to cell balancing. Repeatedly charging series stacks of cells without balancing is usually degenerative and typically leads to increased mismatch accompanied with shorter battery life. For high reliability applications an auxiliary battery balancer is recommended.

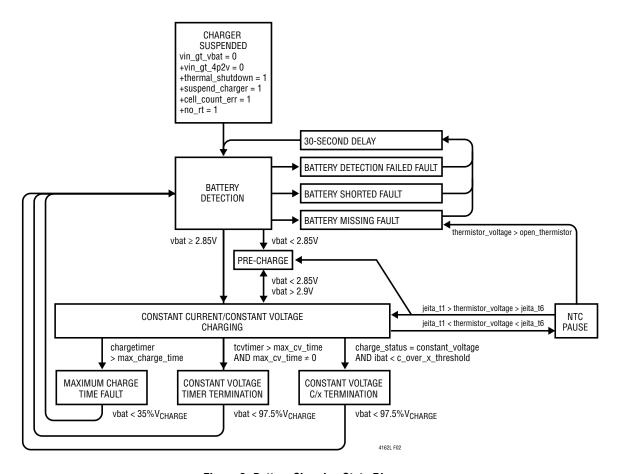

#### **Battery Detection**

The LTC4162 begins a charging cycle by performing a 2-4 second battery detection test, during which a 1mA load is drawn from the battery followed by a small charge current being sent to the battery. If the battery voltage remains stable during the battery detection test, the LTC4162

proceeds with battery charger soft-start. If the battery voltage does not remain stable, the LTC4162 proceeds with a battery open/short test. The battery is charged at minimum charge current for one to two seconds. Abnormal results from the battery detection test result in charger\_state becoming bat\_missing\_fault, bat\_short\_fault or bat\_detect\_failed\_fault and will prevent further charging. A charger\_state of bat\_missing\_fault will also occur if the thermistor is open or has a very high value (thermistor\_voltage>open\_thermistor). Programmable interrupts en\_bat\_short\_fault\_alert, en\_bat\_missing\_fault\_alert and en\_bat\_detect\_failed\_fault\_alert can be set to generate an SMBALERT if one of these cases occurs. In the event of a battery detection fault, the battery detection test will retry every 30 seconds.

#### **Battery Charger Soft-Start**

The LTC4162 soft starts charge current by ramping icharge\_dac from 0 to its target charge current setting at a nominal rate of 400µS per icharge\_dac LSB. This results in a maximum charge current soft start time of 31 • 400µs or 12.4ms. Any time the battery charger needs to change its charge current setting up or down, the ramp routine is invoked. The charge current target is derived from either charge\_current\_setting or the JEITA temperature qualified charging system, icharge\_jeita\_2 through icharge\_jeita\_6 (See Advanced JEITA Temperature Controlled Charging).

#### **Low Battery**

When a charge cycle begins, The LTC4162 first determines if the battery is deeply discharged. If the BATSENS+ pin voltage is lower than about 2.5V, the battery charger delivers roughly 10mA directly from INTV<sub>CC</sub>. This operating mode is mainly used to pull a pack protected battery out of protection mode. When the BATSENS+ pin voltage reaches 2.5V, charging hands over to the switching battery charger. Above 2.5V absolute level but below about 2.85V per cell\_count the LTC4162 applies a preconditioning charge setting equal to approximately C/10 (icharge\_dac = 3), and reports precharge. When the battery voltage exceeds 2.85V per cell\_count, the LTC4162 proceeds to the full constant-current/constant-voltage charging phase and reports cc\_cv\_charge.

#### **Constant-Current Charging**

When the battery voltage is above 2.85V per cell count, the charger will attempt to deliver either (icharge jeita x + 1) 1mV/R<sub>SNSB</sub> with en\_jeita or (charge\_current\_setting + 1) 1mV/R<sub>SNSB</sub> without en\_jeita in constant-current mode where icharge\_jeita\_x or charge\_current\_setting ranges from 0 to 31. For example, A  $10m\Omega$  resistor between CPS and CSN would give an upper limit charge current of 3.2A. Depending on available input power and external load conditions, the battery charger may not be able to charge at the full programmed rate. An alternate control loop such as the input current limit loop or input voltage limit loop may be in force and only partial power will be available to charge the battery. If input current limit is reached, for instance, the system load will be prioritized over the battery charge current. When system loads are light, battery charge current will be maximized and could be as high as the value programmed by icharge\_jeita\_x or charge current setting.