|      |     |

|------|-----|

| 文件编号 |     |

| 代号   | T45 |

| 总页数  | 共 页 |

# GM8775C 型 DSI 转双通道 LVDS 发送器

## 数据手册

版 本 号: 1.0

拟 制: \_\_\_\_\_

确 认: \_\_\_\_\_

审 核: \_\_\_\_\_

批 准: \_\_\_\_\_

成都振芯科技股份有限公司

陈丽玲 : 13724376200

# 数据手册

**GM8775C**

**DSI 转双通道 LVDS 发送器**

2019.07

成都振芯科技股份有限公司

## DSI 转双通道 LVDS 发送器

GM8775C

| GM8775C    |            |                                              |

|------------|------------|----------------------------------------------|

| 当前版本号: 1.0 |            | 当前版本时间: 2019 年 07 月                          |

| 版本更新记录     |            |                                              |

| 版本号        | 更新时间       | 版本更新说明                                       |

| 0.1        | 2019.03.09 | 初始版本                                         |

| 1.0        | 2019.07.31 | 修改已知错误项, 增加时序说明, 修改芯片功能结构图, 修改参考原理图. 增加包装信息。 |

|            |            |                                              |

## 目录

|     |                         |    |

|-----|-------------------------|----|

| 1   | 产品概述.....               | 1  |

| 2   | 产品特征.....               | 1  |

| 3   | 产品功能框图.....             | 1  |

| 4   | 封装及引脚功能说明.....          | 2  |

| 5   | 芯片详细功能描述.....           | 5  |

| 5.1 | DSI 接收功能 .....          | 5  |

| 5.2 | LVDS FPD LINK 发送功能..... | 5  |

| 5.3 | 时钟源选择功能.....            | 5  |

| 5.4 | PWM 时钟输出功能 .....        | 5  |

| 5.5 | 寄存器配置.....              | 5  |

| 6   | 参数指标.....               | 6  |

| 6.1 | 最大额定值.....              | 6  |

| 6.2 | 推荐工作条件.....             | 6  |

| 6.3 | 电特性.....                | 6  |

| 7   | 产品应用信息.....             | 7  |

| 7.1 | 参考原理图.....              | 7  |

| 7.2 | 应用说明.....               | 8  |

| 7.3 | 产品包装信息与丝印信息.....        | 9  |

| 附 1 | 芯片配置流程及推荐配置.....        | 10 |

| 1)  | 芯片初始化时序.....            | 10 |

| 2)  | 推荐配置字.....              | 10 |

## DSI 转双通道 LVDS 发送器

GM8775C

## 1 产品概述

GM8775C 型 DSI 转双通道 LVDS 发送器产品主要实现将 MIPI DSI 转单/双通道 LVDS 功能, MIPI 支持 1/2/3/4 通道可选, 最大支持 4Gbps 速率。LVDS 时钟频率最高 154MHz, 最大支持视频格式为 FULL HD (1920 x 1200)。

该芯片主要应用于手持设备、双屏显示, 大屏幕显示等应用需求。

## 2 产品特征

- a) I/O 电源电压: 1.8V /3.3V;

- b) core 电源电压: 1.8V;

- c) 支持 MIPI® D-PHY 1.00.00 和 MIPI® DSI 1.02.00。

- d) MIPI 支持 1/2/3/4 通道可选的传输方式, 最高速率 1Gbps/通道。

- e) MIPI 接收 18bpp RGB666 、 24bpp RGB888 、 16bpp RGB565 的打包格式。

- f) MIPI 支持 LPDT 传输 (Low-Power Data Transmission) 和反向 LPDT 传输。

- g) LVDS 的时钟范围为 25MHz 到 154MHz。

- h) LVDS 输出支持单/双通道模式。选择双通道模式时, 可配置输出为 18/24bit, JEIDA/VESA 模式; 选择单通道时, 每通道可同时输出, 且可单独配置输出模式 (18/24bit, JEIDA/VESA 模式)。

- i) LVDS 的输出数据通道可灵活调整顺序以方便 PCB 布线。

- j) 可选择采用 MIPI 时钟或外部参考时钟做 LVDS 输出的参考频率, 且支持自动校准功能。

- k) 支持 MIPI command mode 配置和外部 I2C 配置两种芯片配置方式;

- l) GPO 可以输出 PWM 信号, 控制屏幕背光。

- m) 封装: QFN48-pins with e-pad.

- n) 工作温度: -40°C~85°C;

- o) ESD 能力:  $\geq 2\text{KV}$ 。

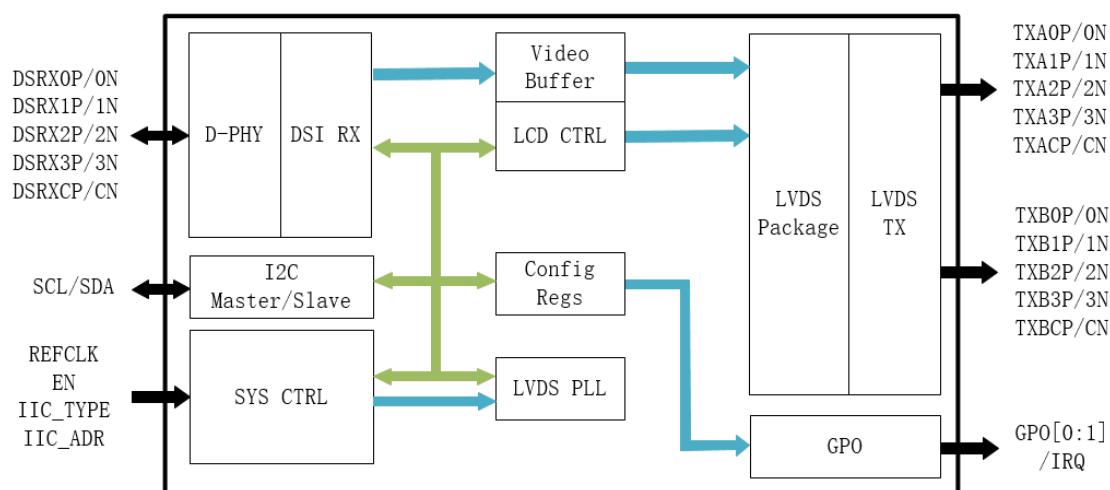

## 3 产品功能框图

图 1 功能结构图

## DSI 转双通道 LVDS 发送器

GM8775C

功能框图按图 1 规定。本器件主要由 DSI 接收通道、数据缓冲、锁相环、LVDS 信号打包、LVDS TX 等模块组成，实现将 1/2/3/4 通道的 DSI 图像信号转换成单/双通道 LVDS 信号输出的功能。

## 4 封装及引脚功能说明

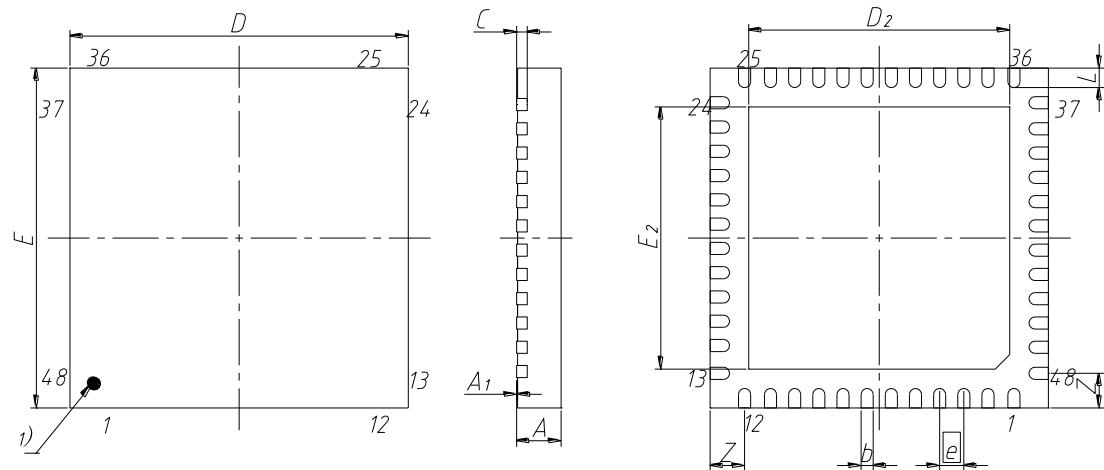

本器件采用 48 引线的方形扁平无引脚 (QFN48) 封装。外形如下所示：

注:1) 为引出端识别标志。

单位为毫米

| 尺寸符号           | 数值   |      |      |

|----------------|------|------|------|

|                | 最小   | 公称   | 最大   |

| A              | 0.70 | —    | 0.80 |

| A <sub>1</sub> | 0    | —    | 0.05 |

| b              | 0.18 | —    | 0.30 |

| c              | 0.18 | —    | 0.23 |

| D              | —    | —    | 7.10 |

| E              | —    | —    | 7.10 |

| e              | —    | 0.50 | —    |

| D <sub>2</sub> | 5.30 | —    | 5.50 |

| E <sub>2</sub> | 5.30 | —    | 5.50 |

| L              | 0.35 | —    | 0.45 |

| Z              | —    | 0.75 | —    |

图 2 外壳外形

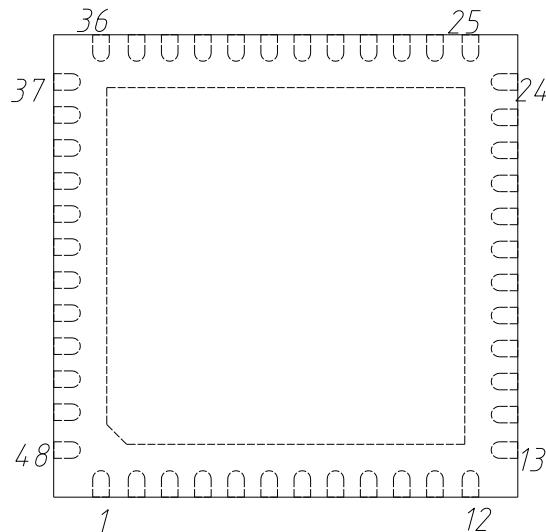

引出端排列如下所示：

## DSI 转双通道 LVDS 发送器

GM8775C

图 3 引出端排列

芯片的引脚功能详细说明：

表 1 引脚功能说明

| 引脚号       | 引脚名称          | IO 方向 | 功能说明                     |

|-----------|---------------|-------|--------------------------|

| MIPI 输入端口 |               |       |                          |

| 14/15     | DA0P/ DA0N    | In    | MIPI DSI 数据 0 通道差分输入正/负端 |

| 16/17     | DA1P/ DA1N    | In    | MIPI DSI 数据 1 通道差分输入正/负端 |

| 20/21     | DA2P/ DA2N    | In    | MIPI DSI 数据 2 通道差分输入正/负端 |

| 22/23     | DA3P/ DA3N    | In    | MIPI DSI 数据 3 通道差分输入正/负端 |

| 18/19     | DACP/ DACN    | In    | MIPI DSI 时钟差分输入正/负端      |

| LVDS 输出端口 |               |       |                          |

| 34/33     | A_Y0P/A_Y0N   | Out   | A 通道 LVDS 数据 0 路差分输出正/负端 |

| 32/31     | A_Y1P/A_Y1N   | Out   | A 通道 LVDS 数据 1 路差分输出正/负端 |

| 30/29     | A_Y2P/A_Y2N   | Out   | A 通道 LVDS 数据 2 路差分输出正/负端 |

| 26/25     | A_Y3P/A_Y3N   | Out   | A 通道 LVDS 数据 3 路差分输出正/负端 |

| 28/27     | A_CLKP/A_CLKN | Out   | A 通道 LVDS 时钟差分输出正/负端     |

| 48/47     | B_Y0P/B_Y0N   | Out   | B 通道 LVDS 数据 0 路差分输出正/负端 |

| 46/45     | B_Y1P/B_Y1N   | Out   | B 通道 LVDS 数据 1 路差分输出正/负端 |

| 44/43     | B_Y2P/B_Y2N   | Out   | B 通道 LVDS 数据 2 路差分输出正/负端 |

## DSI 转双通道 LVDS 发送器

GM8775C

|                  |                       |       |                                                                                                                                                                                                                                                   |

|------------------|-----------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40/39            | B_Y3P/B_Y3N           | Out   | B 通道 LVDS 数据 3 路差分输出正/负端                                                                                                                                                                                                                          |

| 42/41            | B_CLKP/B_CLKN         | Out   | B 通道 LVDS 时钟差分输出正/负端                                                                                                                                                                                                                              |

| 数字及控制端口 (TTL 电平) |                       |       |                                                                                                                                                                                                                                                   |

| 1                | SCL                   | InOut | I <sup>2</sup> C Master/Slave 的 SCL 管脚                                                                                                                                                                                                            |

| 2                | SDA                   | InOut | I <sup>2</sup> C Master/Slave 的 SDA 管脚                                                                                                                                                                                                            |

| 8                | I <sup>2</sup> C_TYPE | In    | 高: SCL/SDA 为 Master, 上电复位后自动读取外部 EEPROM 的内容, EEPROM 地址为 0xA0;<br>低: SCL/SDA 为 Slave                                                                                                                                                               |

| 7                | I <sup>2</sup> C_ADDR | In    | 1) 当 I <sup>2</sup> C_TYPE 为低时, 该芯片的 I <sup>2</sup> C 地址为:<br>(1) I <sup>2</sup> C_ADDR 为高, 芯片 I <sup>2</sup> C 地址为 0x5A;<br>(2) I <sup>2</sup> C_ADDR=Low, 芯片 I <sup>2</sup> C 地址为 0x58;<br>2) 当 I <sup>2</sup> C_TYPE 为高时, 外部 EEPROM 的地址为 0xA0。 |

| 6                | IRQ                   | Out   | 通过寄存器配置输出信号                                                                                                                                                                                                                                       |

| 3                | GPO_0                 | Out   | 通过寄存器配置输出信号                                                                                                                                                                                                                                       |

| 4                | GPO_1                 | Out   | 通过寄存器配置输出信号                                                                                                                                                                                                                                       |

| 9                | RESERVE               | In    | 保留管脚, 接地。                                                                                                                                                                                                                                         |

| 12               | EN                    | In    | 芯片使能控制输入端:<br>1) 为高时, 芯片正常工作;<br>2) 为低时, 芯片进入关断状态。                                                                                                                                                                                                |

| 24               | REFCLK                | In    | 外部参考时钟输入管脚。当不用该管脚的参考时钟时, 该管脚接 GND。                                                                                                                                                                                                                |

| 电源端口             |                       |       |                                                                                                                                                                                                                                                   |

| 35/38            | VDD_LVDS              | Power | 1.8V LVDS 电源, 电源纹波≤±100mV                                                                                                                                                                                                                         |

| 36               | VDD_PLL               | Power | 1.8V PLL 电源, 电源纹波≤±100mV                                                                                                                                                                                                                          |

| 10               | VDDIO                 | Power | 1.8V/3.3V I/O 电源, 与 VDD_RX 电压相同, 电源波动≤10%                                                                                                                                                                                                         |

| 13               | VDD_RX                | Power | 1.8V/3.3VMIPI 电源, 与 VDDIO 电压相同, 电源纹波≤±10%                                                                                                                                                                                                         |

| 11               | Vcore                 | Power | 芯片内部 1.2V 电源, 该管脚必须接到地电容。电容至少为一个 0.1uF 和一个 1uF 并联。                                                                                                                                                                                                |

| 37               | VSS_PLL               | GND   | PLL 地。                                                                                                                                                                                                                                            |

| 5                | GND                   | GND   | VDDIO 地。                                                                                                                                                                                                                                          |

| DAP              | GND                   | GND   | 芯片地                                                                                                                                                                                                                                               |

## DSI 转双通道 LVDS 发送器

GM8775C

### 5 芯片详细功能描述

#### 5.1 DSI 接收功能

GM8775C DSI 协议支持 MIPI® D-PHY 1.00.00 和 MIPI® DSI 1.02.00，可实现 1 到 4 通道 DSI 信号接收。最大数据率 1Gbps/通道。

视频输入格式支持 16bit RGB565、18bit RGB666 和 24bit RGB888 模式。MIPI 通道支持 LPDT 传输（Low-Power Data Transmission）和反向 LPDT 传输。

#### 5.2 LVDS FPD LINK 发送功能

LVDS FPD LINK 发送输出支持单/双通道模式。选择双通道模式时，可配置输出为 18/24bit，JEIDA/VESA 格式；选择单通道时，每通道可同时输出，且可单独配置输出模式（18/24bit，JEIDA/VESA 模式）。

LVDS 像素时钟频率支持 25MHz~154MHz。双通道 LVDS 最大视频格式为 FULL HD (1920 x 1200@60Hz)。

LVDS 输出数据通道可灵活调整顺序以方便 PCB 布线。

#### 5.3 时钟源选择功能

GM8775C LVDS 像素时钟源可由 DSI 内部时钟（HS 模式下）提供，也可配置成外部 RFECLK 提供，且支持自动校准功能。

#### 5.4 PWM 时钟输出功能

GM8775C 具有 PWM 信号输出功能，可通过配置实现由 GPO 输出 PWM 信号，用于控制屏幕背光。

#### 5.5 寄存器配置

GM8775C 的寄存器配置支持 MIPI DSI Command mode 配置和外部 I2C 配置。

## DSI 转双通道 LVDS 发送器

GM8775C

## 6 参数指标

## 6.1 最大额定值

- a) I/O 电源电压 ( $V_{DDIO}$ ) : -0.3V~4V;

- b) 电源电压 ( $V_{DD}$ ) : -0.3V~2V;

- c) 结温 ( $T_J$ ) : 150°C;

- d) 引线耐焊接温度 ( $T_h$ ) (4s) : 260°C;

- e) 功耗 ( $P_D$ ) : 0.5W;

- f) 热阻 ( $R_{\theta Jc}$ ) : 20°C/W;

- g) 贮存环境温度 ( $T_{stg}$ ) : -65°C~150°C;

- h) 静电放电敏感度 ( $V_{ESD}$ ) : 2000V (HBM)。

## 6.2 推荐工作条件

- a) I/O 电源电压 ( $V_{DDIO}$ ) : 3.0V~3.6V, 1.65V~1.95V;

- b) 电源电压 ( $V_{DD}$ ) : 1.65V~1.95V;

- c) 输入高电平电压 ( $V_{IH}$ ) : 2.0V~ $V_{DDIO}$ ;

- d) 输入低电平电压 ( $V_{IL}$ ) : GND~0.8V;

- e) 参数时钟频率 ( $f_{CLK}$ ) : 25MHz~154MHz;

- f) 工作温度 ( $T_A$ ) : -40°C~85°C。

## 6.3 电特性

表 2 电特性

| 特性                          | 符号                    | 条件: 除另有规定,<br>$-40^{\circ}\text{C} \leq T_A \leq 85^{\circ}\text{C}$ , $V_{DDIO}=3.0\text{V} \sim 3.6\text{V}$ 或 $1.65\text{V} \sim 1.95\text{V}$<br>$V_{DD}=1.65\text{V} \sim 1.95\text{V}$ | 极限值  |      | 单位       |

|-----------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|----------|

|                             |                       |                                                                                                                                                                                              | 最小   | 最大   |          |

| 逻辑 1 输入电压                   | $V_{IH}$              |                                                                                                                                                                                              | 900  | —    | mV       |

| 逻辑 0 输入电压                   | $V_{IL}$              |                                                                                                                                                                                              | —    | 450  | mV       |

| HS 差分输入电压                   | $ V_{ID} $            |                                                                                                                                                                                              | 150  | 270  | mV       |

| HS 差分输入阈值电压 <sup>a</sup>    | $ V_{IDT} $           |                                                                                                                                                                                              | —    | 50   | mV       |

| ULP 接收器逻辑 0 电压 <sup>a</sup> | $V_{IL-ULPS}$         |                                                                                                                                                                                              | —    | 300  | mV       |

| HS 模式共模电压                   | $V_{CMRX(DC)}$        |                                                                                                                                                                                              | 70   | 300  | mV       |

| HS 模式共模电压波动 <sup>a</sup>    | $\Delta V_{CMRX(HF)}$ |                                                                                                                                                                                              | —    | 100  | mV       |

| HS 模式单端输入高电平电压              | $V_{IHHS}$            |                                                                                                                                                                                              | —    | 460  | mV       |

| HS 模式单端阈值电压 <sup>a</sup>    | $V_{TERM-EN}$         |                                                                                                                                                                                              | —    | 450  | mV       |

| HS 模式单端输入低电平电压              | $V_{ILHS}$            |                                                                                                                                                                                              | 0    | —    | mV       |

| 差分输入电阻                      | $Z_{ID}$              |                                                                                                                                                                                              | 80   | 124  | $\Omega$ |

| 输出差分电压摆幅可调范围                | $ V_{OD} $            | $R_L=100\Omega$                                                                                                                                                                              | 150  | 400  | mV       |

| 互补态输出差分电压变化                 | $\Delta V_{OD} $      | $R_L=100\Omega$                                                                                                                                                                              | —    | 50   | mV       |

| 输出共模电压                      | $V_{OC(ss)}$          | $R_L=100\Omega$                                                                                                                                                                              | 0.8  | 1    | V        |

|                             |                       |                                                                                                                                                                                              | 1.15 | 1.35 | V        |

## DSI 转双通道 LVDS 发送器

GM8775C

|                          |                 |                 |                |                |    |

|--------------------------|-----------------|-----------------|----------------|----------------|----|

| 输出共模电压峰峰值                | $V_{OC(PP)}$    | $R_L=100\Omega$ | —              | 50             | mV |

| 输出短路电流                   | $I_{OS}$        | 短路到地            | —              | 12             | mA |

| 输出差分电路电流                 | $I_{OSD}$       | —               | —              | 30             | mA |

| TTL 输入高电平电压              | $V_{IH\_TTL}$   | —               | $0.7*V_{DDIO}$ | —              | V  |

| TTL 输入低电平电压              | $V_{IL\_TTL}$   | —               | —              | $0.3*V_{DDIO}$ | V  |

| TTL 输入漏电流                | $I_{IN\_TTL}$   | —               | -20            | 20             | uA |

| LVDS 端口下拉电阻 <sup>a</sup> | $R_{LVDS\_DIS}$ | —               | 1              | —              | KΩ |

| 输出时钟高电平宽度 <sup>a</sup>   | $t_w$           | —               | $4/7t_C$       | —              | ns |

| DSI 输入脉冲抑制 <sup>a</sup>  | $t_{GS}$        | —               | —              | 300            | ps |

| LVDS 输出时钟周期              | $t_C$           | —               | 6              | 41             | ns |

| D0 相对延迟时间                | $t_0$           | —               | -0.65          | 0.65           | ns |

| D1 相对延迟时间                | $t_1$           | —               | $t_C/7-0.65$   | $t_C/7+0.65$   | ns |

| D2 相对延迟时间                | $t_2$           | —               | $2t_C/7-0.65$  | $2t_C/7+0.65$  | ns |

| D3 相对延迟时间                | $t_3$           | —               | $3t_C/7-0.65$  | $3t_C/7+0.65$  | ns |

| D4 相对延迟时间                | $t_4$           | —               | $4t_C/7-0.65$  | $4t_C/7+0.65$  | ns |

| D5 相对延迟时间                | $t_5$           | —               | $5t_C/7-0.65$  | $5t_C/7+0.65$  | ns |

| D6 相对延迟时间                | $t_6$           | —               | $6t_C/7-0.65$  | $6t_C/7+0.65$  | ns |

| 输出上升时间                   | $t_r$           | —               | 180            | 2000           | ps |

| 输出下降时间                   | $t_f$           | —               | 180            | 2000           | ps |

| 使能时间                     | $t_{en}$        | —               | —              | 1              | ms |

| 关断时间                     | $t_{dis}$       | —               | —              | 0.1            | ms |

| 复位时间                     | $t_{reset}$     | —               | 10             | —              | ms |

注 a: 设计保证参数, 其值为理论典型值。

## 7 产品应用信息

## 7.1 参考原理图

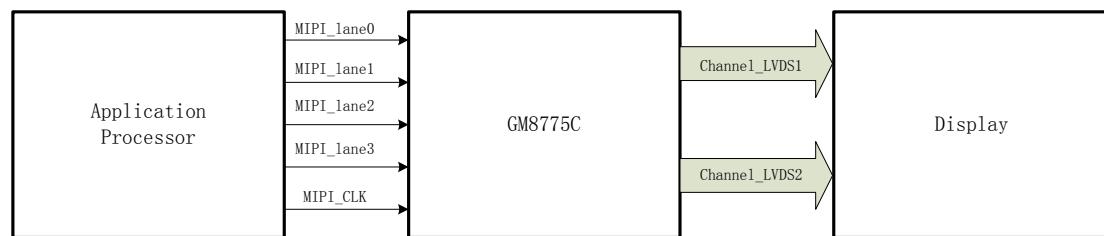

GM8775C 主要应用于前端视频应用处理器和后端显示设备之间, 用于做 DSI 到 LVDS 转换驱动输出功能。

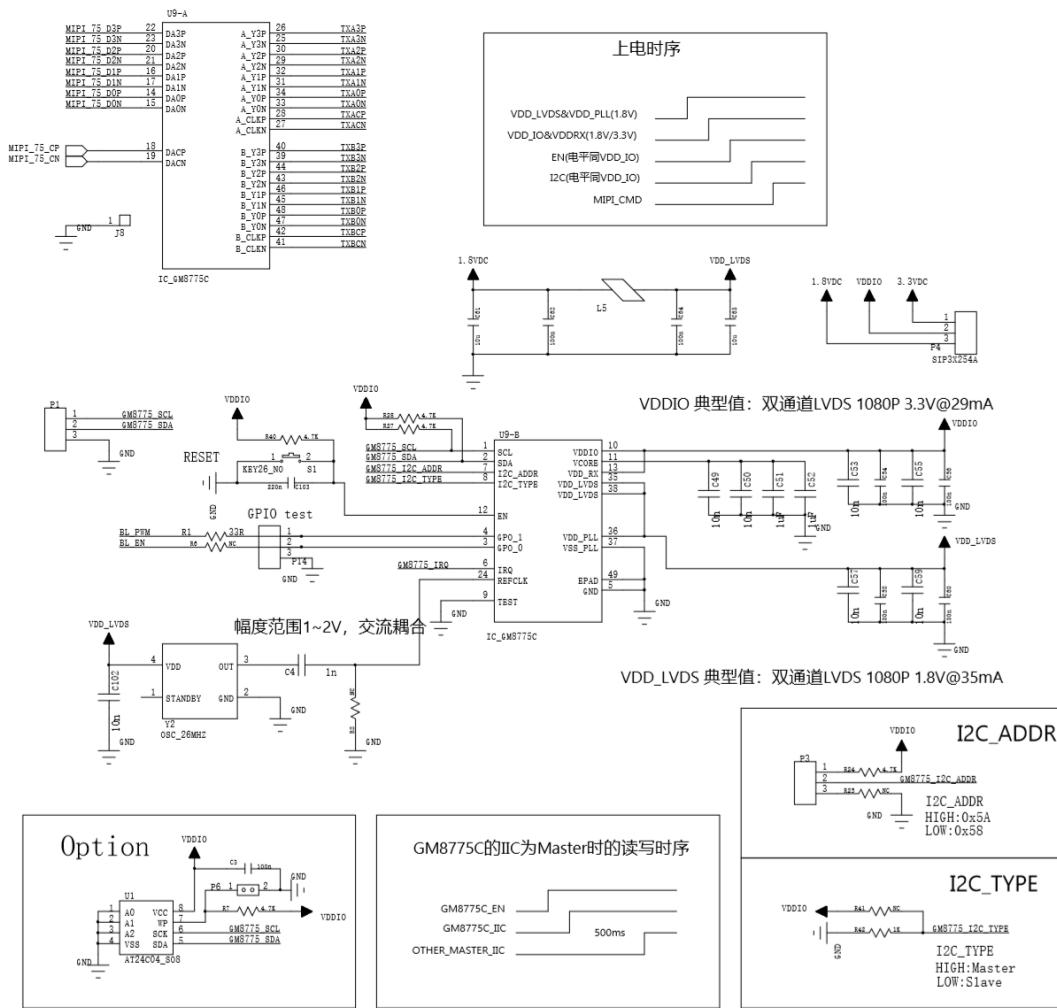

图 4 为其系统应用方式, 前端视频应用处理器输出 4lane DSI 数据, 并同步输出 1lane DSI 时钟信号。GM8775C 将该 DSI 信号转换成双通道 LVDS 差分信号输出, 驱动后级显示器完成转换、传输和显示功能。图 5 为 GM8775C 的参考原理图。

图 4 GM8775C 系统应用图

## DSI 转双通道 LVDS 发送器

GM8775C

图 5 GM8775C 参考原理图

## 7.2 应用说明

芯片应用中应注意以下几点：

- 1) 电源必须加滤波电容，推荐采用 0.1uF 和 1uF 的电容进行组合滤波，也可根据实际情况考虑；

- 2) 差分输入/输出信号保证差分匹配走线，同时保证通道间走线长度尽量等长，避免引入额外的通道时滞；

- 3) 应用过程中，芯片的电源电压、输入电压范围、测试温度以及测试条件等都需要严格遵守数据手册规定；

- 4) 用于测试和焊接的工作台面，测试仪器以及高低温箱等都必须具有防静电设施；

- 5) 测试和使用过程中，操作人员也必须带防静电腕带，在防静电台上进行操作，禁止直接手持芯片；

- 6) 测试和使用过程中出现异常现象时，应该注意保护芯片。

## DSI 转双通道 LVDS 发送器

GM8775C

## 7.3 产品包装信息与丝印信息

## 1) 产品包装信息

- a) 内包装采用定制编带包装，最小包装1000片；

- b) 外包装采用定制产品盒，并放置防震泡沫。

## 2) 产品丝印信息

芯片打标采用激光打标技术，内容包括公司 logo，产品型号：GM8775C；以及产品批号。

## 3) 注意事项

器件的处理、包装、运输和烘焙符合 IPC/JEDEC J-STD-033，湿敏等级为 4 级。

## DSI 转双通道 LVDS 发送器

GM8775C

## 附 1 芯片配置流程及推荐配置

## 1) 芯片初始化时序

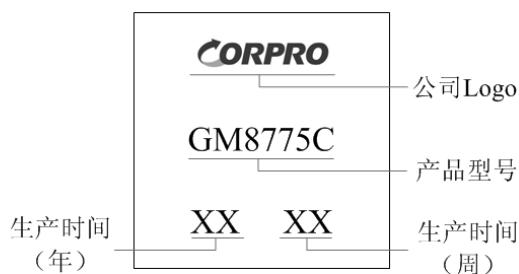

图 6 GM8775C 初始化时序图

## 2) 推荐配置字

video format: 1920x1080, pixel\_clk=148MHz, vesa, 8bit

total\_line=1125; vfp=4, vsw=5, vbp=36;

total\_pixel=2200,hfp=88,hsw=44, hbp=148

MIPI\_CLK:468MHz

推荐本产品按以下顺序进行初始化配置：

| 序号 | 地址   | 配置字  | 说明                                                           |

|----|------|------|--------------------------------------------------------------|

| 1  | 0x00 | AA   | PASSWORD                                                     |

| 2  | 0x48 | 0x02 | Mode control, Fixed configuration                            |

| 3  | 0xB6 | 0x20 | Mode control, Fixed configuration                            |

| 4  | 0x01 | 80   | HACTIVE[7:0],1980=0x780                                      |

| 5  | 0x02 | 38   | VACTIVE[7:0],1080=0x438                                      |

| 6  | 0x03 | 47   | {VACTIVE[11:8],HACTIVE[11:8]}                                |

| 7  | 0x04 | 58   | HFP_WIDTH[7:0],100=0x64                                      |

| 8  | 0x05 | 2C   | HSW_WIDTH[7:0],100=0x64                                      |

| 9  | 0x06 | 94   | HBP_WIDTH[7:0],120=0x78                                      |

| 10 | 0x07 | 00   | {VS_POL,HS_POL,HFP_WIDTH[9:8],HSW_WIDTH[9:8],HBP_WIDTH[9:8]} |

| 11 | 0x08 | 04   | VFP_WIDTH[7:0],10=0x0A                                       |

| 12 | 0x09 | 05   | VSW_WIDTH[7:0],10=0x0A                                       |

| 13 | 0x0A | 24   | VBP_WIDTH[7:0],15=0x0F                                       |

| 14 | 0x0B | 91   | {PLL_REFSEL[1:0],DSM_MN_EN, PLL_REFDIV[4:0]}                 |

| 15 | 0x0C | 13   | PLL_INT[7:0]                                                 |

| 16 | 0x0D | 01   | {RD_FIFO_DLY[11:8],PLL_INT[9:8],PLL_POST_DV[1:0]}            |

| 17 | 0x0E | 80   | RD_FIFO_DLY[7:0]                                             |

| 18 | 0x0F | 20   | MIN_HSW[7:0]                                                 |

| 19 | 0x10 | 20   | MIN_HFP[7:0]                                                 |

| 20 | 0x11 | 3B   | {MIPI_DATA_PN[3:0],MIPI_CLK_PN,1'b0,MIPI_LANE_NU}            |

## DSI 转双通道 LVDS 发送器

GM8775C

|    |      |    |                                                                                                                             |

|----|------|----|-----------------------------------------------------------------------------------------------------------------------------|

|    |      |    | M[1:0]                                                                                                                      |

| 21 | 0x12 | 1B | {MIPI_LANE0_SEL[1:0],MIPI_LANE1_SEL[1:0],<br>MIPI_LANE2_SEL[1:0],MIPI_LANE3_SEL[1:0]}                                       |

| 22 | 0x13 | 63 | {1'b0, DUAL_LINK_EN, LINK1_DATA_SEL,<br>LINK0_DATA_SEL,<br>LINK1_JEIDA_EN, LINK0_JEIDA_EN, LINK1_BIT_SEL,<br>LINK0_BIT_SEL} |

| 23 | 0x14 | 32 | {1'b0, LINK0_LANE0_SEL[2:0], 1'b0,<br>LINK0_LANE1_SEL[2:0]}                                                                 |

| 24 | 0x15 | 10 | {1'b0, LINK0_LANE2_SEL[2:0], 1'b0,<br>LINK0_LANE3_SEL[2:0]}                                                                 |

| 25 | 0x16 | 40 | {1'b0, LINK0_LANECK_SEL[2:0, 4'b0000]}                                                                                      |

| 26 | 0x17 | 00 | {3'b000,LINK0_PN_SWAP[4:0]}                                                                                                 |

| 27 | 0x18 | 32 | {1'b0, LINK1_LANE0_SEL[2:0], 1'b0,<br>LINK1_LANE1_SEL[2:0]}                                                                 |

| 28 | 0x19 | 10 | {1'b0, LINK1_LANE2_SEL[2:0], 1'b0,<br>LINK1_LANE3_SEL[2:0]}                                                                 |

| 29 | 0x1A | 40 | {1'b0, LINK1_LANECK_SEL[2:0, 4'b0000]}                                                                                      |

| 30 | 0x1B | 00 | {3'b000,LINK1_PN_SWAP[4:0]}                                                                                                 |

| 31 | 0x1E | 46 | {I2C_TYPE, MIPI_XOR, LVDS_XOR, DSM_XOR,<br>RST_FIFO_ADDR, VSW_MODE, HSW_MODE, 1'b0}                                         |

| 32 | 0x51 | 20 | {PLL_VCO_ISEL}                                                                                                              |

| 33 | 0x1F | 10 | {3'b000, CONFIG_FINISH, 3'b000,SOFT_RESET}                                                                                  |

## 8. 产品包装信息与丝印信息

## 8.1 产品包装信息

- 1) 内包装采用定制编带包装，最小包装1000片；

- 2) 外包装采用定制产品盒，并放置防震泡沫。

## 8.2 产品丝印信息

芯片打标采用激光打标技术，内容包括公司 logo，产品型号：GM8775C；以及产品批号。

## 8.3 注意事项

器件的处理、包装、运输和烘焙符合 IPC/JEDEC J-STD-033，湿敏等级为 4 级。