# 8 位微控制器

# KF8A100ENG 数据手册

## 产品订购信息

| 芯片型号    | 订货号        | 封装     | FLASH | RAM(Byte) | LFOSC(Hz) | 外部HFOSC(Hz)     | 8位定时器 | 16位定时器 | 8位PWM | 12位ADC | CMP | OP | 触摸按键 | USART | I2C | 内嵌参考电压   | H桥输出(V) |

|---------|------------|--------|-------|-----------|-----------|-----------------|-------|--------|-------|--------|-----|----|------|-------|-----|----------|---------|

| KF8A100 | KF8A100ENG | QFN-20 | 8Kx16 | 1040      | 16M       | 16M/<br>32.768k | 1     | 3      | 2     | 14     | 1   | 1  | 14   | 1     | 1   | 2V/3V/4V | 2.6~5.5 |

版权所有@

上海芯旺微电子有限公司

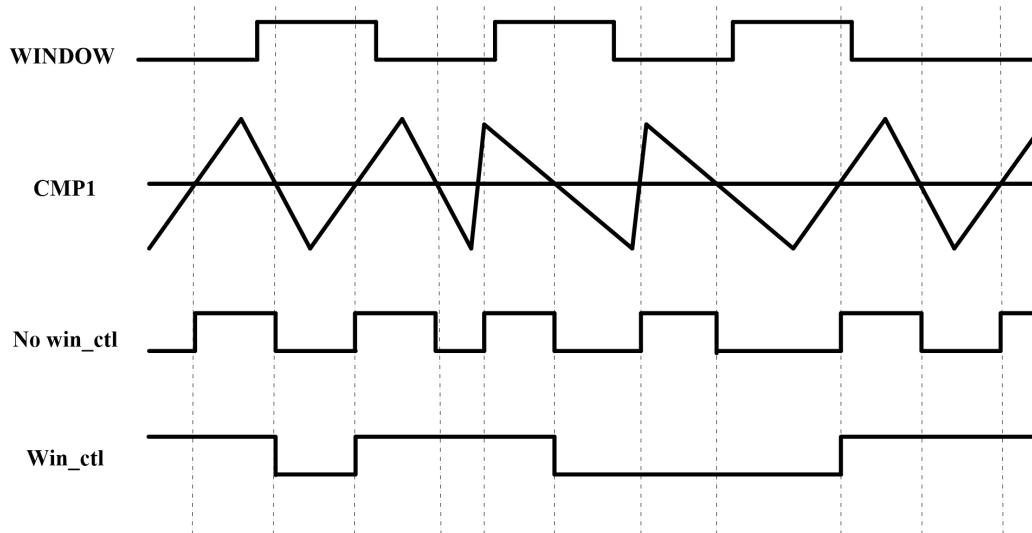

本文档为上海芯旺微电子有限公司在现有数据资料基础上慎重且力求准确无误编制而成.确保应用符合技术规范，是您自身应负的责任。上海芯旺微电子有限公司不作任何明示或暗示、书面或口头、法定或其他形式的声明或担保，包括但不限于针对其使用情况、质量、性能、适销性或特定用途的适用性的声明或担保。上海芯旺微电子有限公司对因这些信息及使用这些信息而引起的后果不承担任何责任。如果将芯旺微电子有限公司的芯片用于生命维持和或生命安全应用，一切风险由使用方自负。使用方同意在由此引发任何一切伤害、索赔、诉讼或费用时，会维护和保障上海芯旺微电子有限公司免于承担法律责任，并加以赔偿。

本文档中所述的器件应用信息及其他类似内容仅为您提供便利，可能有更新的信息所替代。上海芯旺微电子有限公司会不定期进行更新，恕不另行通知。使用方如需获得最新的产品信息，请及时访问上海芯旺微电子有限公司官网或与上海芯旺微电子有限公司联系。

## KF8A100ENG 芯片使用注意事项

### 芯片的 ESD 防护措施

KF8A100ENG 芯片提供高达 8KV 的 ESD 标准保护电路。建议用户根据芯片存储/应用的环境采取适当静电防护措施。应注意应用环境的湿度；建议避免使用容易产生静电的绝缘体；存放和运输应在抗静电容器、抗静电屏蔽袋或导电材料容器中；包括工作台在内的所有测试和测量工具必须保证接地；操作者应该佩戴静电消除手腕环手套，不能用手直接接触芯片等。

### 芯片的 EFT 防护措施

KF8A100ENG 芯片提供高达 4.2KV 的 EFT 标准保护电路。当 MCU 芯片应用在 PCB 系统时，需要遵守 PCB 相关设计要求，包括电源线、地线（包括数字/模拟电源分离，单点/多点接地等）、复位管脚保护电路、电源和地之间的去耦电容、高低频电路单独分别处理以及单/多层次板选择等。

### 芯片的 LATCH-UP 防护措施

为有效防护 LATCH-UP 损坏芯片，用户需保证在 VDD 引脚上不出现异常高压或者负压。建议用户在 VDD 和 VSS 之间并接两个 105 和 102 大小的电容，电容尽量靠近芯片的 VDD 引脚。

### 芯片的焊接

KF8A100ENG 芯片的焊接应按照工业标准的焊接要求，以免损坏芯片。手工焊接时注意焊接的温度和焊接时间。

### 芯片的上电/断电

KF8A100ENG 芯片提供独立电源管脚。当 KF8A100ENG 芯片应用在多电源供电系统时，应先对 MCU 芯片上电，再对系统其他部件上电；反之，断电时，先对系统其他部件断电，再对 MCU 芯片断电。若操作顺序相反则可能导致芯片内部元件过压或过流，从而导致芯片故障或元件退化。

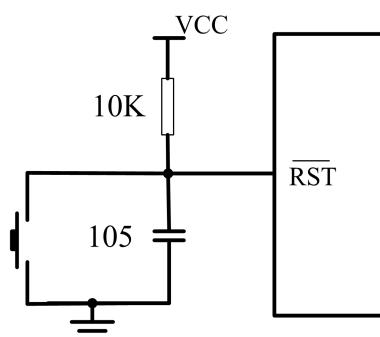

### 芯片的复位

KF8A100ENG 芯片提供内部上电复位。对于不同的快速上电/断电或慢速上电/断电系统，内部上电复位电路可能失效，建议用户使用外部复位、断电复位、看门狗复位等，确保复位电路正常工作。在系统设计时，若使用外部复位电路，建议采用三极管复位电路、RC 复位电路。若不使用外部复位电路，建议采用复位管脚接电阻到电源，或采取必要的电源抖动处理电路或其他保护电路。具体可参照芯片的数据手册说明。

### 芯片的内部时钟

KF8A100ENG 芯片提供内部时钟源。内部时钟源会随着温度、电压变化而偏移，可能会影响时钟源精度。具体可参照芯片的数据手册说明。

### 芯片的初始化

KF8A100ENG 芯片提供各种内部和外部复位。对于不同的应用系统，有必要对芯片寄存器、内存、功能模块等进行初始化，尤其是 I/O 管脚复用功能进行初始化，避免由于芯片上电以后，I/O 管脚状态的不确定情况发生。

### 芯片的管脚

KF8A100ENG 芯片提供宽范围的输入管脚电平，用户输入高电平应大于 VIH 的最小值，低电平应小于 VIL 的最大值，以免波动噪声进入芯片。对于未使用的输入/输出管脚，建议用户设为输入状态，并通过电阻上拉至电源或下拉至地，或设置为输出管脚，输出固定电平

并浮空。对未使用的管脚处理因应用系统而异，具体遵循应用系统的相关规定和说明。

VDD 和 VSS 之间需接 104 以上的电容，电容尽量靠近 MCU 芯片的 VDD 引脚。

### 芯片的低功耗设计

KF8A100ENG 芯片提供低功耗设计模式，用户在实际应用中可根据应用系统的要求采用各种不同的低功耗模式，包括系统工作时钟的选择和休眠模式的选择等等。

### 芯片的开发环境

KF8A100ENG 芯片提供完整的软/硬件开发环境，并受知识产权保护。选择上海芯旺微电子有限公司指定的的汇编器、编译器、编程器、硬件仿真器开发环境，必须遵循与芯片相关的规定和说明。

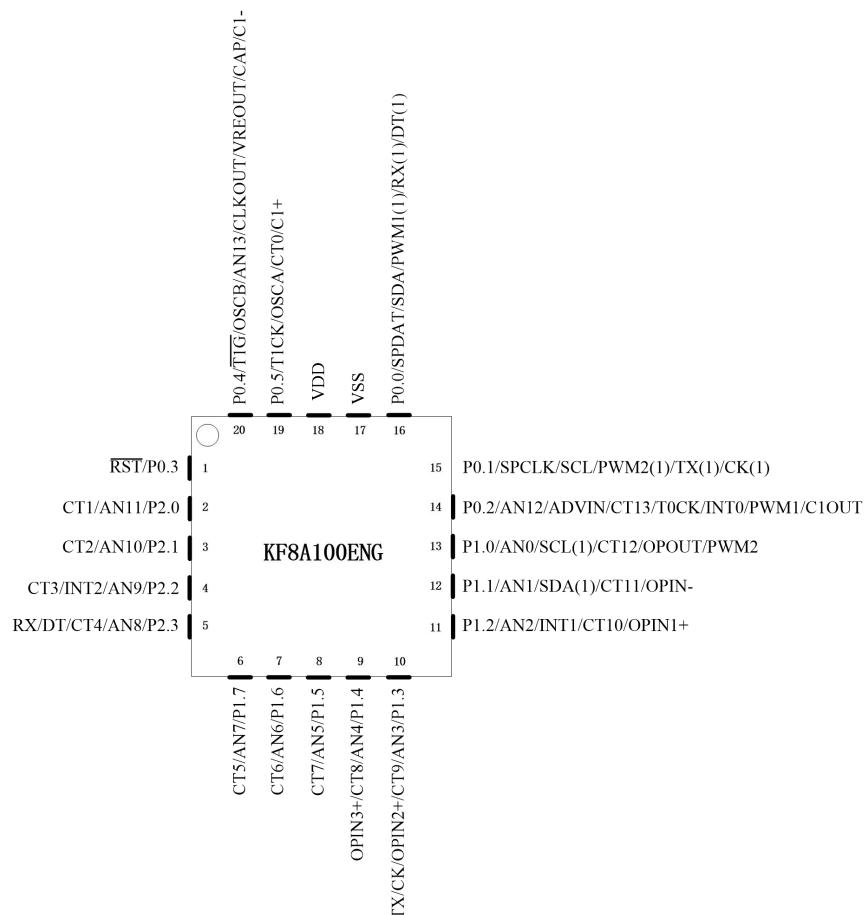

## 引脚示意图

**QFN-20 引脚示意图：**

注：用户在正常使用时，通常会有一些用不到的引脚，如果直接把这些管脚悬空，而不做其他处理可能使单片机功耗增大，因此建议将那些不用的引脚设置为数字输出模式，如果P0.3未用，应外接上拉电阻，并对地下拉一个电容。

## 引脚功能说明

| QFN-20 | I/O | 引脚功能   | 引脚说明                       |

|--------|-----|--------|----------------------------|

| 18     | P   | VDD    | 直流电源                       |

| 19     | I/O | P0.5   | 带上拉和电平变化中断功能的双向输入输出端口      |

|        |     | C1+    | 比较器 1 正输入端                 |

|        |     | T1CK   | T1 时钟输入                    |

|        |     | CT0    | 电容触摸通道 0                   |

|        |     | OSCA   | 外部振荡器输入引脚 A                |

| 20     | I/O | P0.4   | 带上拉和电平变化中断功能的双向输入输出端口      |

|        |     | C1-    | 比较器 1 负输入端                 |

|        |     | T1G    | T1 门控信号输入                  |

|        |     | OSCB   | 外部振荡器输入引脚 B                |

|        |     | VREOUT | 内部参考电压输出端                  |

|        |     | AN13   | ADC 输入通道 13                |

|        |     | CAP    | 触摸按键参考电容输入脚，接入范围为 0pF~10pF |

|        |     | CLKOUT | 系统时钟输出                     |

| 1      | I   | P0.3   | 带电平变化中断功能的输入端口             |

|        |     | RST    | 主复位信号输入                    |

| 2      | I/O | P2.0   | 带上拉功能的双向输入输出端口             |

|        |     | AN11   | ADC 输入通道 11                |

|        |     | CT1    | 电容触摸通道 1                   |

| 3      | I/O | P2.1   | 带上拉功能的双向输入输出端口             |

|        |     | AN10   | ADC 输入通道 10                |

|        |     | CT2    | 电容触摸通道 2                   |

| 4      | I/O | P2.2   | 带上拉功能的双向输入输出端口             |

|        |     | INT2   | 外部中断 2 输入端                 |

|        |     | AN9    | ADC 输入通道 9                 |

|        |     | CT3    | 电容触摸通道 3                   |

| 5      | I/O | P2.3   | 带上拉功能的双向输入输出端口             |

|        |     | RX     | 可配置 USART 全双工异步数据接收端       |

|        |     | DT     | 可配置 USART 半双工同步数据端         |

|        |     | AN8    | ADC 输入通道 8                 |

|        |     | CT4    | 电容触摸通道 4                   |

| 6      | I/O | P1.7   | 带上拉功能的双向输入输出端口             |

|        |     | CT5    | 电容触摸通道 5                   |

|        |     | AN7    | ADC 输入通道 7                 |

| 7      | I/O | P1.6   | 带上拉功能的双向输入输出端口             |

|        |     | CT6    | 电容触摸通道 6                   |

|        |     | AN6    | ADC 输入通道 6                 |

| 8      | I/O | P1.5   | 带上拉功能的双向输入输出端口             |

|        |     | CT7    | 电容触摸通道 7                   |

|        |     | AN5    | ADC 输入通道 5                 |

| 9      | I/O | P1.4   | 带上拉功能的双向输入输出端口             |

|        |     | OPIN3+ | 运算放大器正输入端 3                |

|        |     | CT8    | 电容触摸通道 8                   |

|    |     |         |                       |

|----|-----|---------|-----------------------|

|    |     | AN4     | ADC 输入通道 4            |

| 10 | I/O | P1.3    | 带上拉功能的双向输入输出端口        |

|    |     | TX      | 可配置 USART 全双工异步数据发送端  |

|    |     | CK      | 可配置 USART 半双工同步时钟端    |

|    |     | OPIN2+  | 运算放大器正输入端 2           |

|    |     | AN3     | ADC 输入通道 3            |

|    |     | CT9     | 电容触摸通道 9              |

| 11 | I/O | P1.2    | 带上拉功能的双向输入输出端口        |

|    |     | OPIN1+  | 运算放大器正输入端 1           |

|    |     | AN2     | ADC 输入通道 2            |

|    |     | INT1    | 外部中断 1 输入             |

|    |     | CT10    | 电容触摸通道 10             |

| 12 | I/O | P1.1    | 带上拉功能的双向输入输出端口        |

|    |     | OPIN-   | 运算放大器负输入端             |

|    |     | AN1     | ADC 输入通道 1            |

|    |     | SDA (1) | IIC 数据输入/输出           |

|    |     | CT11    | 电容触摸通道 11             |

| 13 | I/O | P1.0    | 带上拉功能的双向输入输出端口        |

|    |     | OPOUT   | 运算放大器输出               |

|    |     | AN0     | ADC 输入通道 0            |

|    |     | SCL (1) | IIC 时钟脚               |

|    |     | PWM2    | PWM2 输出端              |

|    |     | CT12    | 电容触摸通道 12             |

| 14 | I/O | P0.2    | 带上拉和电平变化中断功能的双向输入输出端口 |

|    |     | C1OUT   | 比较器 1 输出              |

|    |     | AN12    | ADC 输入通道 12           |

|    |     | ADVRIN  | AD 外部参考电压输入端          |

|    |     | T0CK    | T0 时钟输入               |

|    |     | INT0    | 外部中断 0 输入端            |

|    |     | PWM1    | PWM1 输出端              |

|    |     | CT13    | 电容触摸通道 13             |

| 15 | I/O | P0.1    | 带上拉和电平变化中断功能的双向输入输出端口 |

|    |     | TX      | 可配置 USART 全双工异步数据发送端  |

|    |     | CK      | 可配置 USART 半双工同步时钟端    |

|    |     | SCL     | I2C 时钟脚               |

|    |     | PWM2    | PWM2 输出端              |

|    |     | SPCLK   | 编程时钟输入                |

| 16 | I/O | P0.0    | 带上拉和电平变化中断功能的双向输入输出端口 |

|    |     | RX      | 可配置 USART 全双工异步数据接收端  |

|    |     | DT      | 可配置 USART 半双工同步数据端    |

|    |     | SDA     | IIC 数据输入/输出脚          |

|    |     | PWM1(1) | PWM1 输出端              |

|    |     | SPDAT   | 编程数据输入/输出             |

| 17 | P   | VSS     | 地, 0V 参考点             |

## 目录

|                                  |           |

|----------------------------------|-----------|

| 产品订购信息.....                      | 2         |

| KF8A100ENG 芯片使用注意事项.....         | 3         |

| 引脚示意图.....                       | 5         |

| 引脚功能说明.....                      | 6         |

| 目录.....                          | 8         |

| <b>1 系统概述.....</b>               | <b>16</b> |

| 1.1 芯片特征.....                    | 17        |

| 1.2 系统框图.....                    | 19        |

| 1.3 存储器.....                     | 20        |

| 1.4 系统时钟.....                    | 21        |

| 1.4.1 时钟模块相关寄存器.....             | 22        |

| 1.4.1.1 系统频率控制寄存器 OSCCTL.....    | 22        |

| 1.4.1.2 系统时钟标志寄存器 OSCSTA.....    | 23        |

| 1.4.2 上电延时.....                  | 23        |

| 1.4.3 内部高频时钟 INTHF.....          | 23        |

| 1.4.4 内部低频时钟 INTLF.....          | 23        |

| 1.4.5 外部高频时钟 EXTHF.....          | 24        |

| 1.4.6 外部低频时钟 EXTLF.....          | 24        |

| 1.4.7 时钟切换和时钟信号同步.....           | 24        |

| 1.4.8 双速启动模式.....                | 25        |

| 1.4.9 双速启动过程.....                | 26        |

| 1.4.10 外部时钟故障检测.....             | 26        |

| 1.4.11 时钟故障保护处理.....             | 27        |

| 1.5 芯片初始化.....                   | 28        |

| 1.6 配置位.....                     | 29        |

| 1.7 在线串行编程.....                  | 30        |

| <b>2 I/O 端口介绍.....</b>           | <b>31</b> |

| 2.1 I/O 端口的读写.....               | 31        |

| 2.2 I/O 端口数字输入电平类型.....          | 31        |

| 2.3 P0 口.....                    | 32        |

| 2.3.1 P0 口相关的寄存器.....            | 33        |

| 2.3.1.1 P0 口状态寄存器 (P0) .....     | 33        |

| 2.3.1.2 P0 口输出锁存寄存器 (POLR) ..... | 33        |

| 2.3.1.3 P0 口方向控制寄存器(TR0).....    | 33        |

| 2.3.1.4 P0 上拉功能控制寄存器(PUR0).....  | 34        |

| 2.3.1.5 电平变化中断控制寄存器(IOCL).....   | 34        |

| 2.3.2 P0 口各引脚内部原理功能框图.....       | 36        |

|                                  |           |

|----------------------------------|-----------|

| 2.4 P1 口.....                    | 37        |

| 2.4.1 P1 口相关的寄存器.....            | 38        |

| 2.4.1.1 P1 口状态寄存器(P1).....       | 38        |

| 2.4.1.2 P1 口输出锁存寄存器 (P1LR) ..... | 38        |

| 2.4.1.3 P1 口方向控制寄存器(TR1).....    | 38        |

| 2.4.1.4 P1 口上拉功能控制寄存器(PUR1)..... | 39        |

| 2.4.2 P1 口原理功能框图.....            | 40        |

| 2.5 P2 口.....                    | 41        |

| 2.5.1 P2 口相关的寄存器.....            | 41        |

| 2.5.1.1 P2 口状态寄存器(P2).....       | 41        |

| 2.5.1.2 P2 口输出锁存寄存器 (P2LR) ..... | 42        |

| 2.5.1.3 P2 口方向控制寄存器(TR2).....    | 42        |

| 2.5.1.4 P2 口上拉功能控制寄存器(PUR2)..... | 42        |

| 2.5.2 P2 口原理功能框图.....            | 43        |

| <b>3 存储器.....</b>                | <b>44</b> |

| 3.1 程序存储器(ROM)区.....             | 44        |

| 3.1.1 MOVP 指令.....               | 45        |

| 3.1.2 JMP、CALL 指令.....           | 46        |

| 3.2 数据存储器(RAM)区.....             | 46        |

| 3.2.1 通用寄存器区.....                | 47        |

| 3.2.2 特殊功能寄存器(SFR)区.....         | 48        |

| 3.3 FLASH 自写.....                | 49        |

| 3.3.1 寄存器 NVMDATAH/L.....        | 50        |

| 3.3.2 寄存器 NVMADDRH/L.....        | 50        |

| 3.3.3 写 Flash.....               | 50        |

| 3.3.4 读 Flash.....               | 52        |

| 3.4 寄存器组 RN.....                 | 52        |

| 3.5 ID 地址单元.....                 | 52        |

| <b>4 汇编指令及寻址方式.....</b>          | <b>53</b> |

| 4.1 寻址方式.....                    | 53        |

| 4.1.1 寄存器寻址.....                 | 53        |

| 4.1.2 直接寻址.....                  | 53        |

| 4.1.3 立即数寻址.....                 | 53        |

| 4.1.4 寄存器间接寻址.....               | 53        |

| 4.1.5 位寻址.....                   | 54        |

| 4.2 汇编指令.....                    | 54        |

| <b>5 中断.....</b>                 | <b>55</b> |

| 5.1 中断相关的寄存器.....                | 57        |

| 5.1.1 中断控制寄存器 INTCTL.....        | 57        |

| 5.1.2 中断使能寄存器 EIE1.....          | 58        |

| 5.1.3 中断使能寄存器 EIE2.....          | 58        |

|                                    |           |

|------------------------------------|-----------|

| 5.1.4 中断使能寄存器 EIE3.....            | 59        |

| 5.1.5 中断标志寄存器 EIF1.....            | 59        |

| 5.1.6 中断标志寄存器 EIF2.....            | 60        |

| 5.1.7 中断标志寄存器 EIF3.....            | 60        |

| 5.1.8 中断优先级控制寄存器 IP0.....          | 60        |

| 5.1.9 中断优先级控制寄存器 IP1.....          | 61        |

| 5.1.10 中断优先级控制寄存器 IP2.....         | 61        |

| 5.1.11 中断优先级控制寄存器 IP3.....         | 62        |

| 5.1.12 电源控制寄存器 PCTL.....           | 62        |

| 5.1.13 INT 中断沿选择寄存器 INTEDGCTL..... | 63        |

| 5.1.14 中断响应.....                   | 64        |

| 5.2 INT 中断.....                    | 65        |

| 5.2.1 INT0 中断.....                 | 65        |

| 5.2.2 INT1 中断.....                 | 65        |

| 5.2.3 INT2 中断.....                 | 65        |

| 5.3 定时器中断.....                     | 65        |

| 5.4 P0 口中断.....                    | 65        |

| 5.5 PWM 中断.....                    | 66        |

| 5.6 中断现场保护.....                    | 66        |

| <b>6 定时器/计数器.....</b>              | <b>67</b> |

| 6.1 定时器/计数器 T0.....                | 67        |

| 6.1.1 T0 原理框图.....                 | 67        |

| 6.1.2 T0 相关的寄存器.....               | 67        |

| 6.1.2.1 OPTR 选择寄存器.....            | 67        |

| 6.1.3 定时模式.....                    | 68        |

| 6.1.4 计数模式.....                    | 68        |

| 6.1.5 T0 的使用.....                  | 68        |

| 6.2 定时器/计数器 T1.....                | 69        |

| 6.2.1 T1 原理框图.....                 | 69        |

| 6.2.2 T1 时钟.....                   | 69        |

| 6.2.3 T1 相关的寄存器.....               | 69        |

| 6.2.3.1 T1 控制寄存器.....              | 70        |

| 6.2.4 定时模式.....                    | 71        |

| 6.2.5 计数模式.....                    | 71        |

| 6.2.6 T1 重载功能.....                 | 71        |

| 6.2.7 T1 在休眠模式下的运行.....            | 71        |

| 6.2.8 T1 分配给 PWM1/2.....           | 71        |

| 6.3 定时器 T3.....                    | 72        |

| 6.3.1 T3 原理框图.....                 | 72        |

| 6.3.2 T3 相关寄存器.....                | 72        |

| 6.3.2.1 T3 控制寄存器 T3CTL.....        | 72        |

| 6.3.2.2 电容触摸控制寄存器 0 (CTCTL0) ..... | 73        |

| 6.3.3 T3 中断.....                   | 73        |

|                                      |    |

|--------------------------------------|----|

| 6.3.4 T3 的使用 .....                   | 74 |

| 6.4 定时器/计数器 T4.....                  | 75 |

| 6.4.1 T4 原理框图.....                   | 75 |

| 6.4.2 T4 相关寄存器.....                  | 75 |

| 6.4.2.1 T4 控制寄存器.....                | 75 |

| 6.4.2.2 T4 预分频器.....                 | 76 |

| 6.4.2.3 T4 计数时钟选择.....               | 76 |

| 6.4.3 T4 重载功能.....                   | 76 |

| 6.4.4 T4 中断.....                     | 77 |

| 6.4.5 T4 工作在休眠模式.....                | 77 |

| 7 模数(A/D)转换模块.....                   | 78 |

| 7.1 与 A/D 相关的寄存器.....                | 78 |

| 7.1.1 A/D 控制寄存器 0(ADCCTL0).....      | 78 |

| 7.1.2 A/D 控制寄存器 1(ADCCTL1).....      | 79 |

| 7.1.3 模拟/数字口选择寄存器(ANSEL/H).....      | 80 |

| 7.2 通道的选择.....                       | 80 |

| 7.3 模拟输入口的配置.....                    | 80 |

| 7.4 A/D 转换参考电压的选择.....               | 80 |

| 7.5 内部参考电压 $V_{REF}$ .....           | 80 |

| 7.5.1 参考电压寄存器 (VRECTL) .....         | 81 |

| 7.6 转换时钟的选择.....                     | 81 |

| 7.7 输出格式.....                        | 81 |

| 7.8 A/D 转换的启动和完成.....                | 81 |

| 7.9 复位的影响.....                       | 82 |

| 7.10 使用 A/D 转换器的设置.....              | 82 |

| 8 PWM 模块.....                        | 83 |

| 8.1 工作原理.....                        | 83 |

| 8.2 PWM1/2 相关的寄存器.....               | 83 |

| 8.2.1 PWM1/2 控制寄存器.....              | 84 |

| 8.2.2 PWM1/2 周期.....                 | 84 |

| 8.2.3 PWM1/2 占空比.....                | 84 |

| 8.3 PWM1/2 分辨率.....                  | 84 |

| 8.4 PWM1/2 中断.....                   | 85 |

| 8.5 PWM1/2 输出引脚分配功能.....             | 85 |

| 8.6 休眠模式下的操作.....                    | 85 |

| 8.7 复位的影响.....                       | 85 |

| 8.8 PWM1/2 使用方法.....                 | 85 |

| 9 SSCI 模块.....                       | 86 |

| 9.1 概述.....                          | 86 |

| 9.2 SSCI 相关寄存器.....                  | 86 |

| 9.2.1 SSCI 控制寄存器 0 (SSCICCTL0) ..... | 86 |

|                                      |     |

|--------------------------------------|-----|

| 9.2.2 SSCI 控制寄存器 1 (SSCICCTL1) ..... | 87  |

| 9.2.3 SSCI 状态寄存器 (SSCICSTA) .....    | 88  |

| 9.2.4 SSCI 屏蔽寄存器 (SSCICMSK) .....    | 89  |

| 9.2.5 SSCI I2C 地址寄存器 (SSCIADD) ..... | 89  |

| 9.2.6 模拟/数字口选择寄存器(ANSEH).....        | 90  |

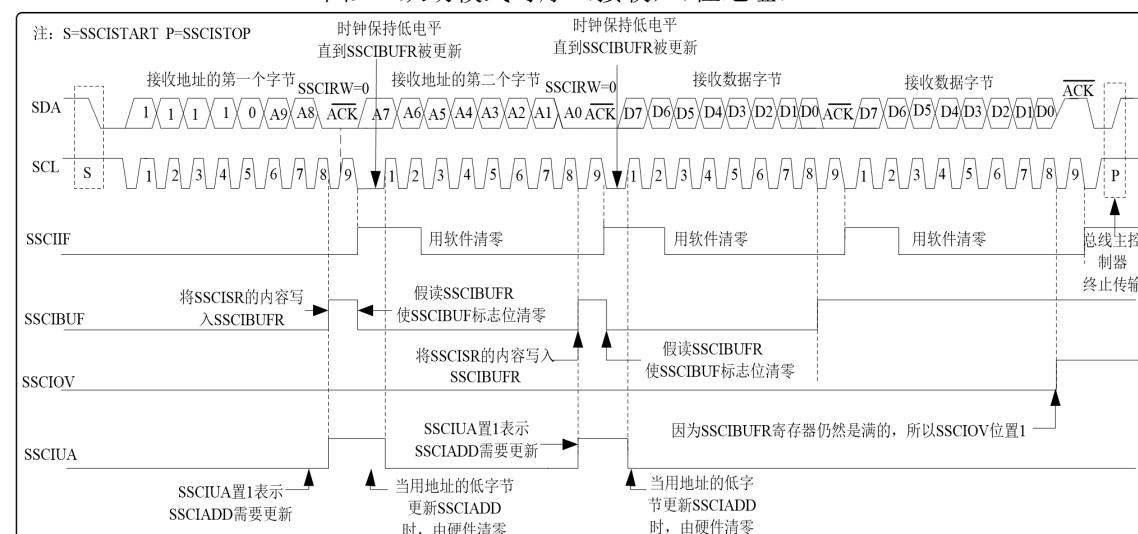

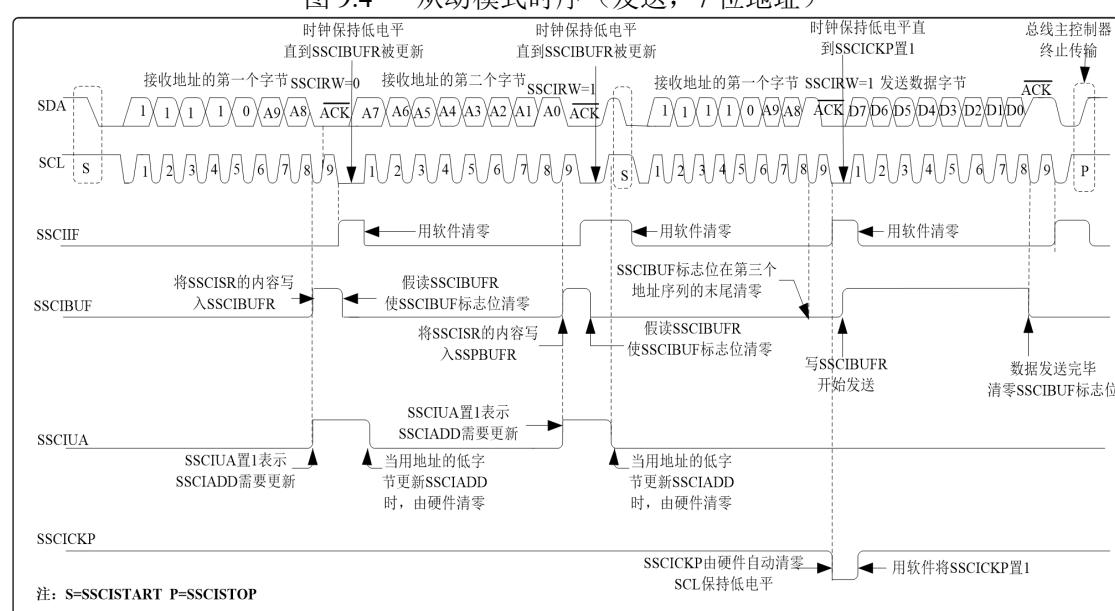

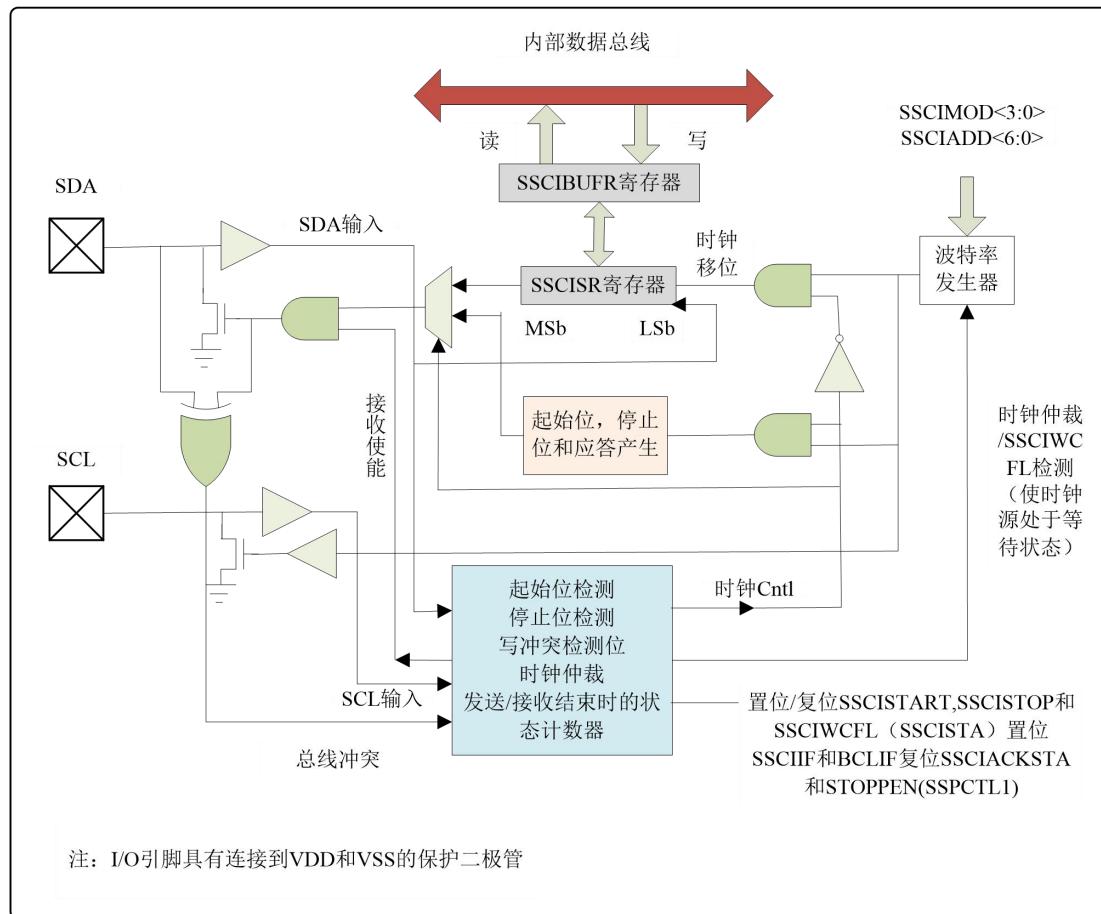

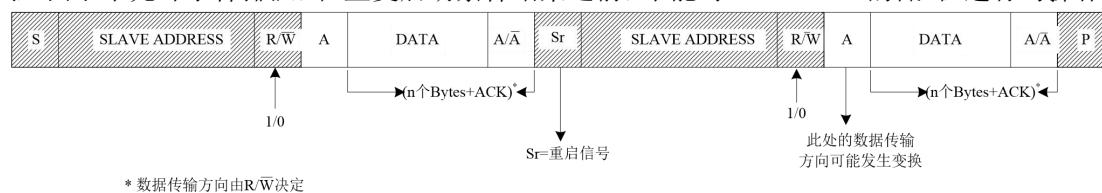

| 9.3 I2C 模式.....                      | 90  |

| 9.3.1 工作原理.....                      | 90  |

| 9.3.2 I2C 从动模式.....                  | 91  |

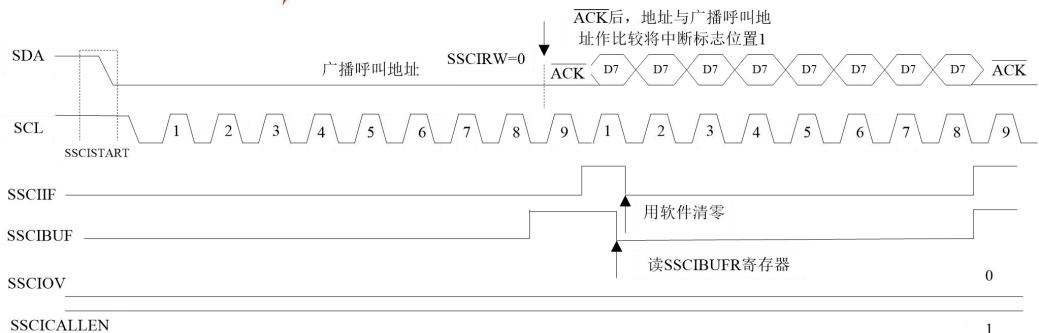

| 9.3.2.1 寻址.....                      | 92  |

| 9.3.2.2 接收.....                      | 93  |

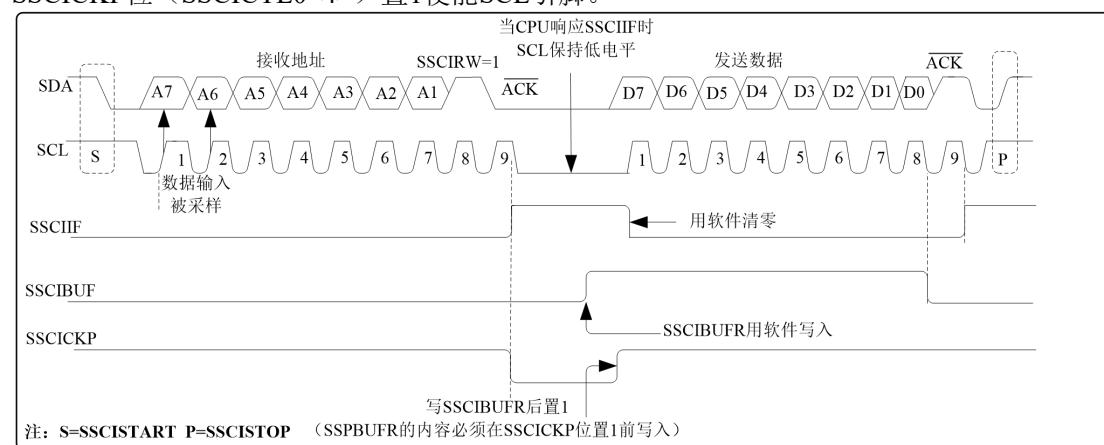

| 9.3.2.3 发送.....                      | 94  |

| 9.3.2.4 广播呼叫地址支持.....                | 95  |

| 9.3.3 I2C 主控模式.....                  | 97  |

| 9.3.3.1 主控模式支持.....                  | 97  |

| 9.3.3.2 I2C 主模式操作.....               | 98  |

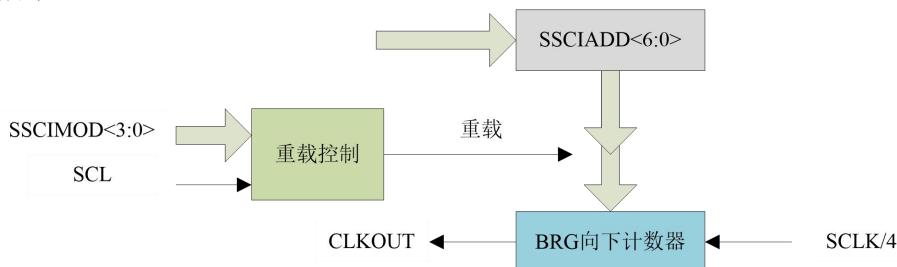

| 9.3.3.3 波特率发生器.....                  | 99  |

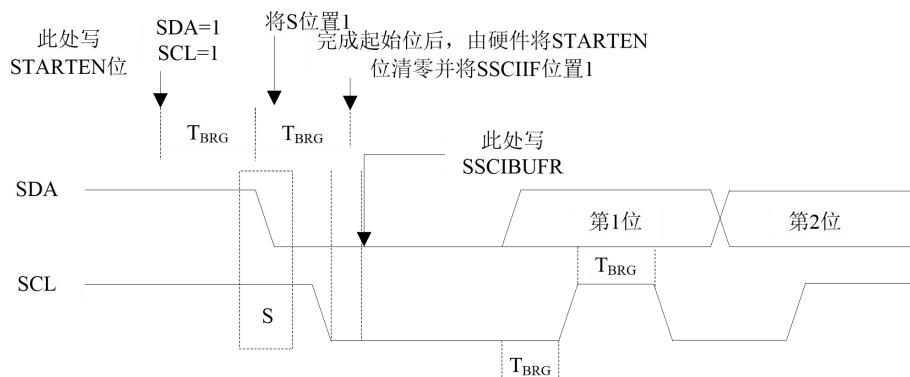

| 9.3.3.4 I2C 主控模式启动条件时序.....          | 100 |

| 9.3.3.5 I2C 主控模式重复启动条件时序.....        | 100 |

| 9.3.3.6 I2C 主控模式发送.....              | 101 |

| 9.3.3.7 I2C 主控模式接收.....              | 103 |

| 9.3.3.8 应答序列时序.....                  | 104 |

| 9.3.3.9 停止条件序列.....                  | 104 |

| 9.3.3.10 时钟仲裁.....                   | 105 |

| 9.3.4 多主控器模式.....                    | 106 |

| 9.3.4.1 多主机通信, 总线冲突与总线仲裁.....        | 106 |

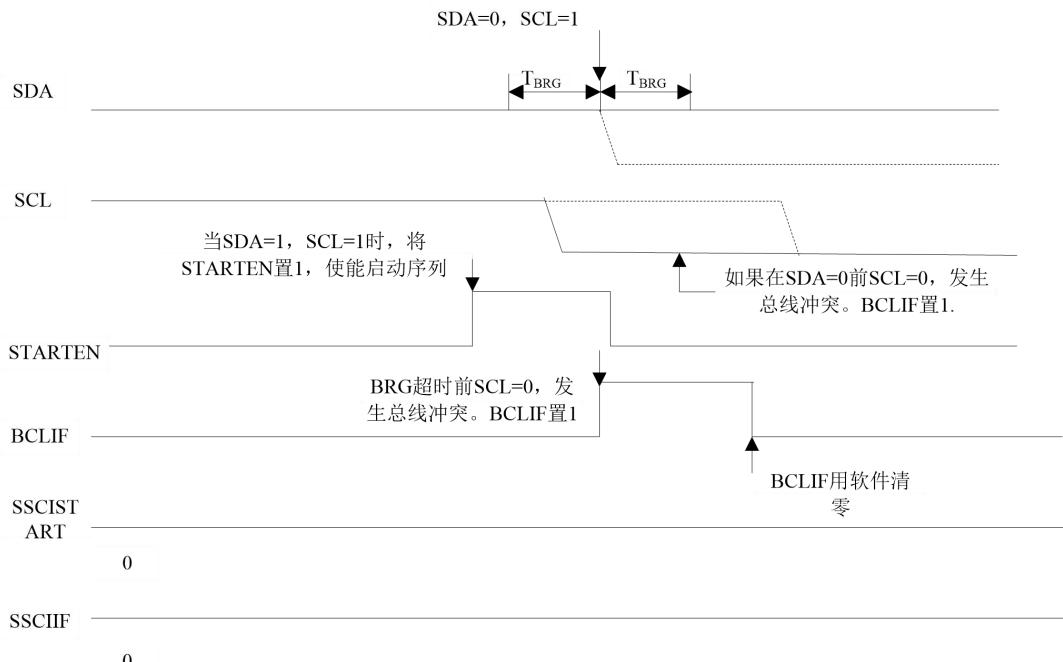

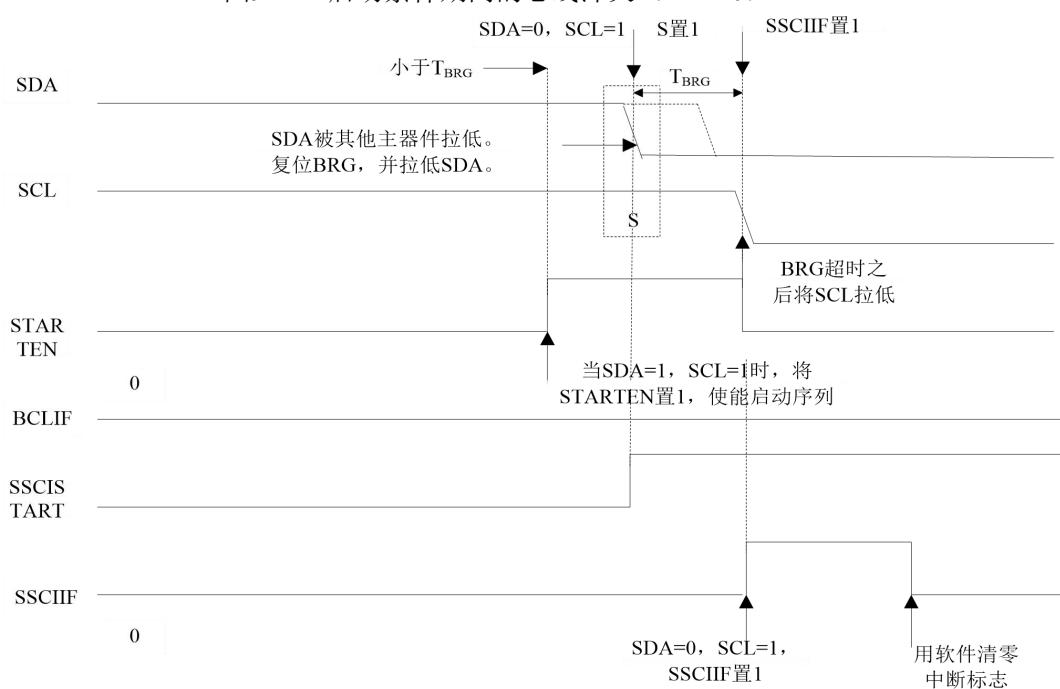

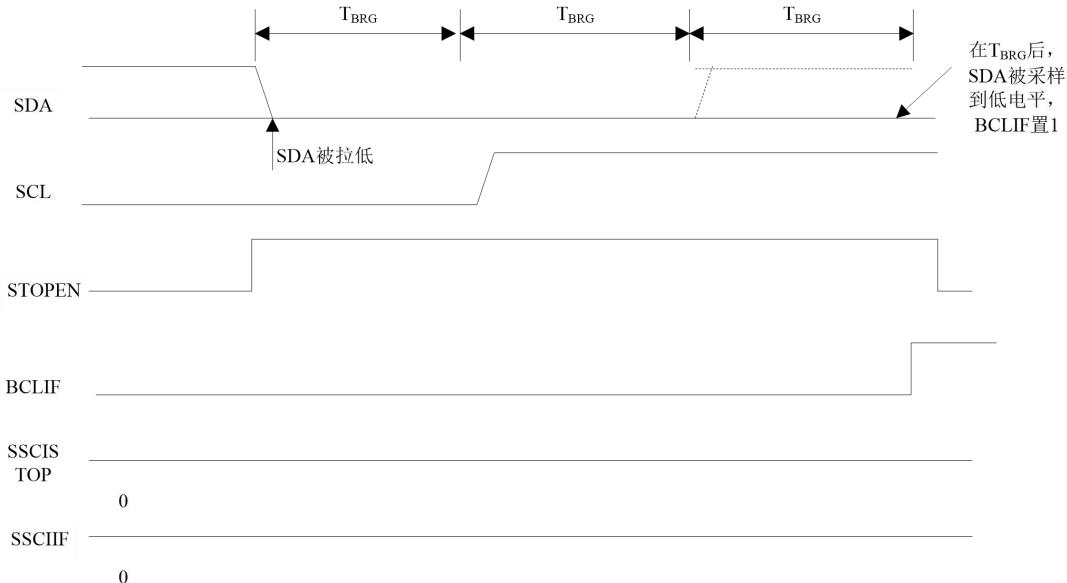

| 9.3.4.2 启动条件期间的总线冲突.....             | 107 |

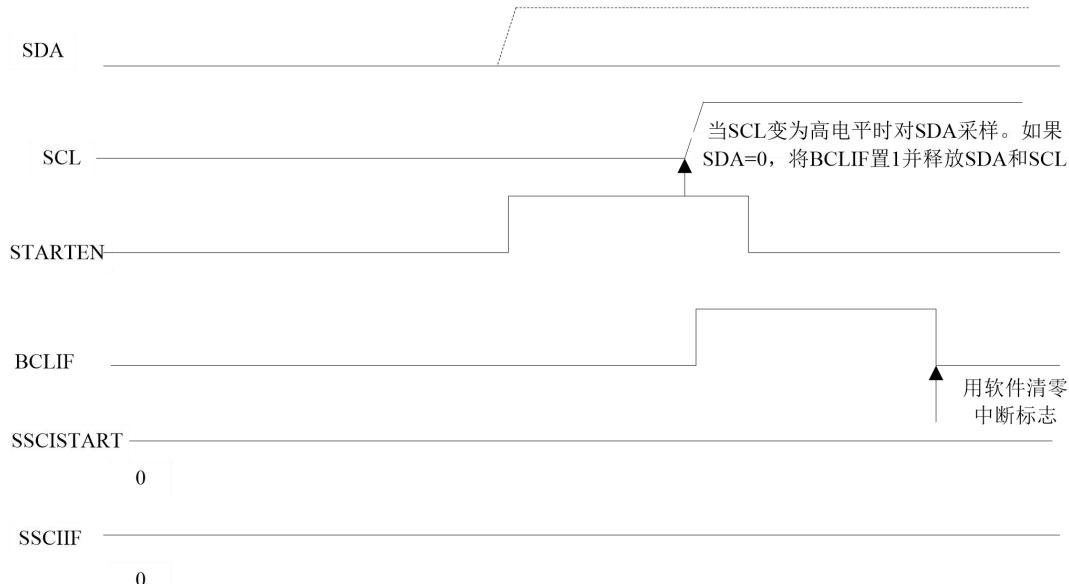

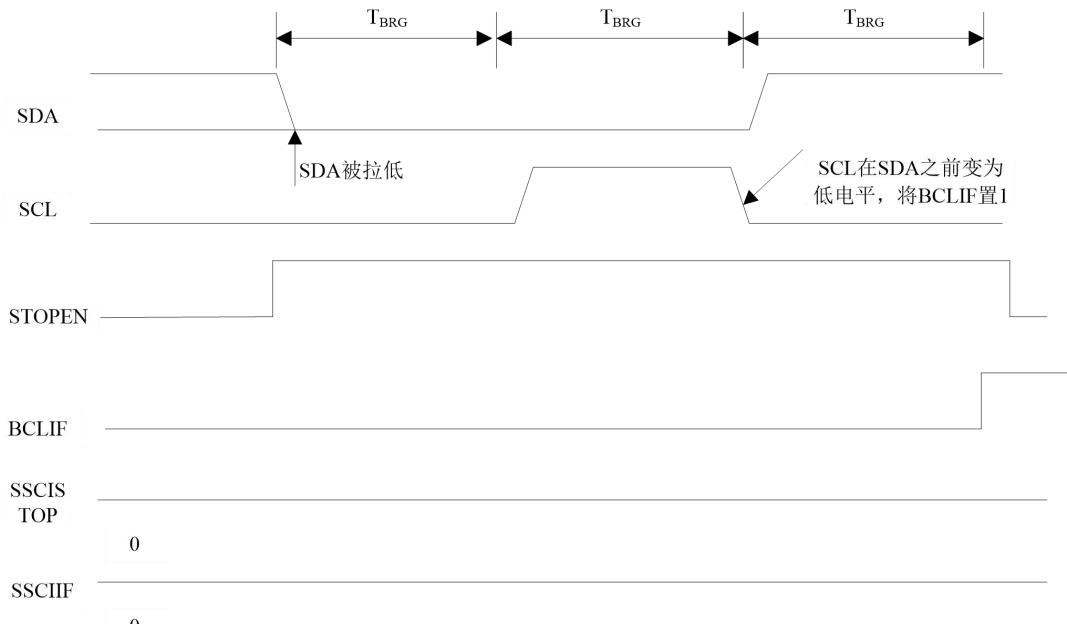

| 9.3.4.3 重复启动条件期间的总线冲突.....           | 109 |

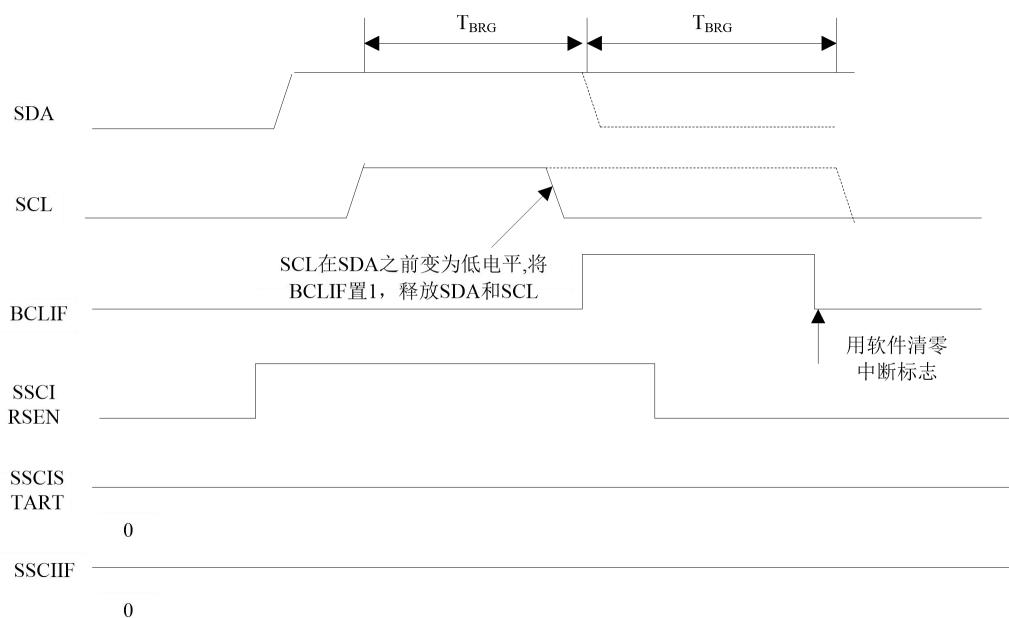

| 9.3.4.4 停止条件期间的总线冲突.....             | 110 |

| 9.3.4.5 SSCI 屏蔽寄存器.....              | 111 |

| 通用全双工/ 半双工收发器 (USART) .....          | 113 |

| 11.1 系统概述.....                       | 113 |

| 11.2 USART 功能引脚.....                 | 113 |

| 11.3 相关寄存器.....                      | 113 |

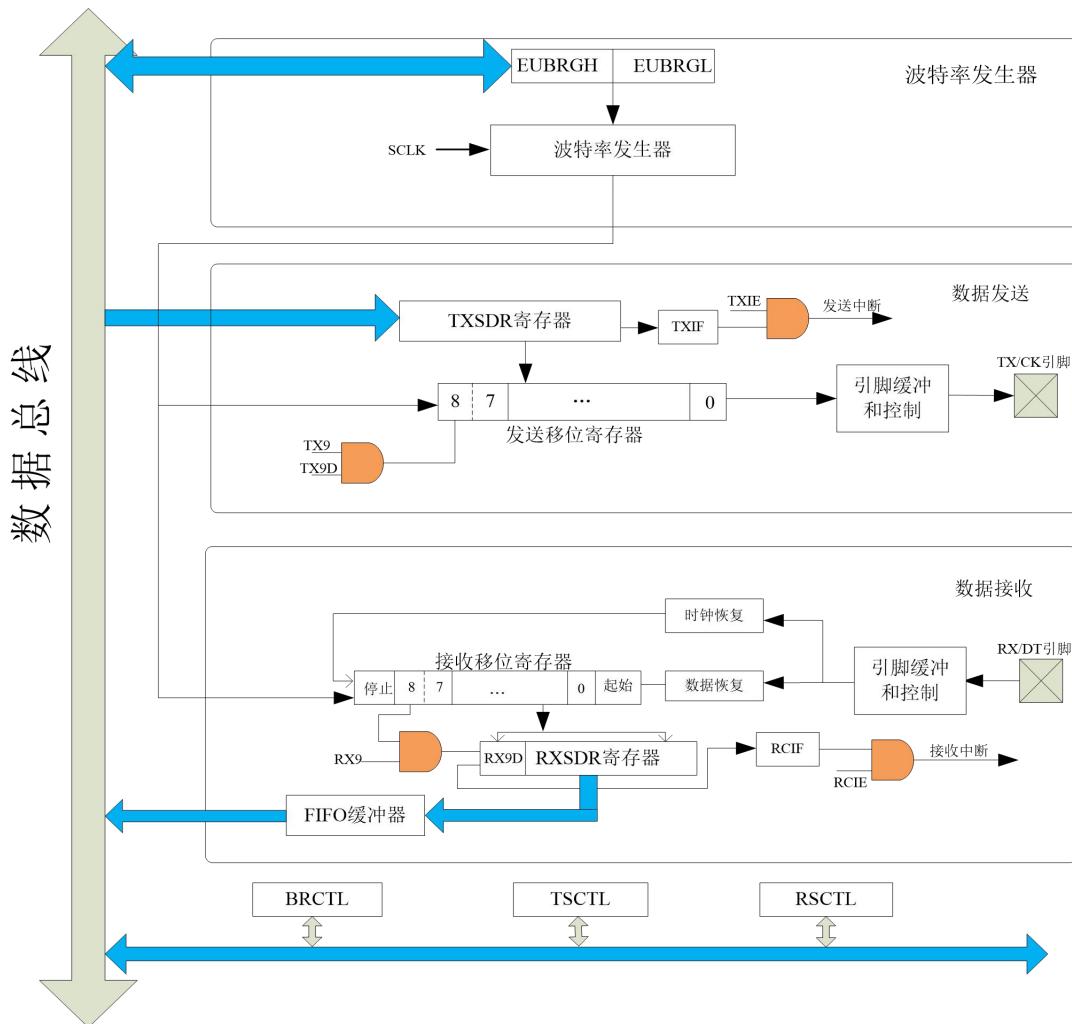

| 11.4 原理框图.....                       | 114 |

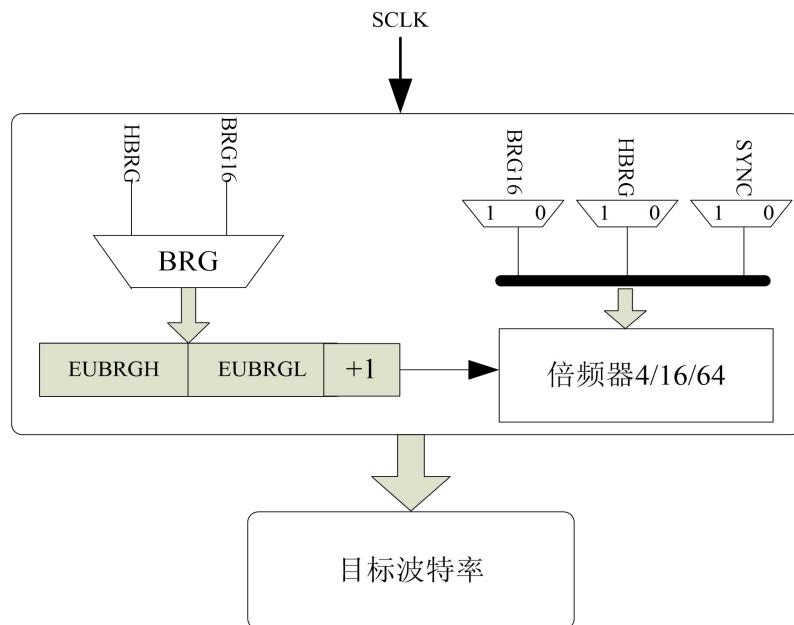

| 11.5 波特率发生器.....                     | 115 |

| 11.5.1 相关寄存器.....                    | 115 |

| 11.5.1.1 USART 波特率控制寄存器 BRCTL.....   | 115 |

| 11.5.2 波特率的选择.....                   | 116 |

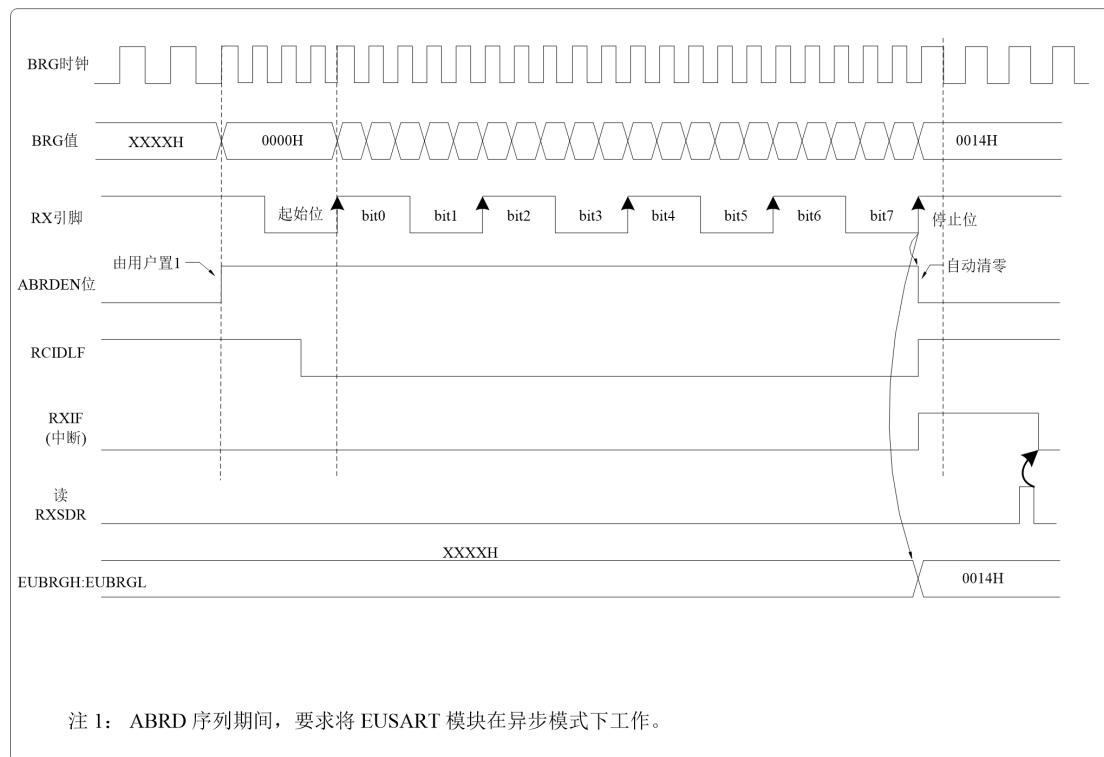

| 11.5.3 自动波特率检测.....                  | 118 |

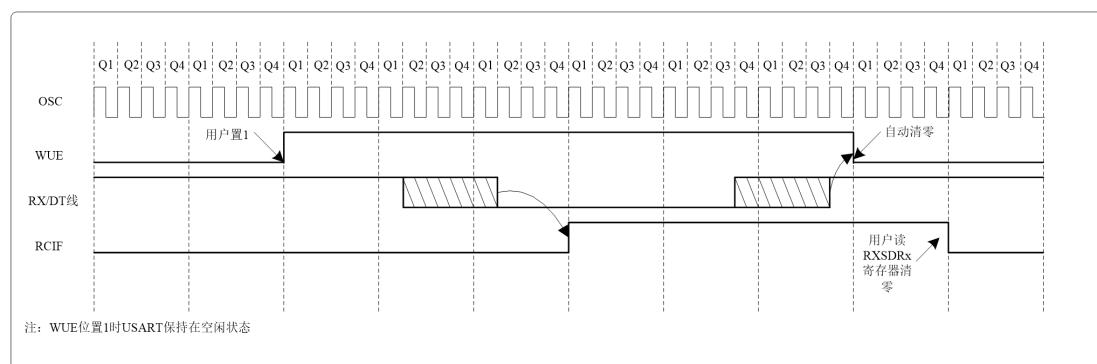

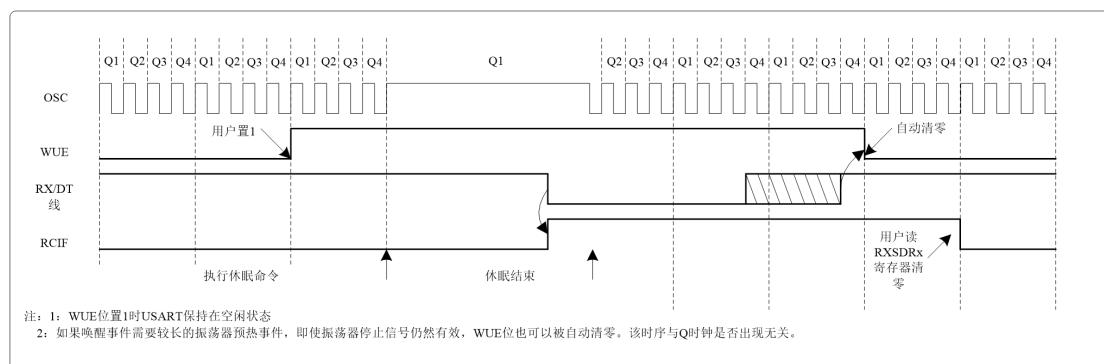

| 11.5.4 接收间隔字符时自动唤醒.....              | 119 |

| 11.5.5 兼容 LIN 总线的间隔符时序.....          | 121 |

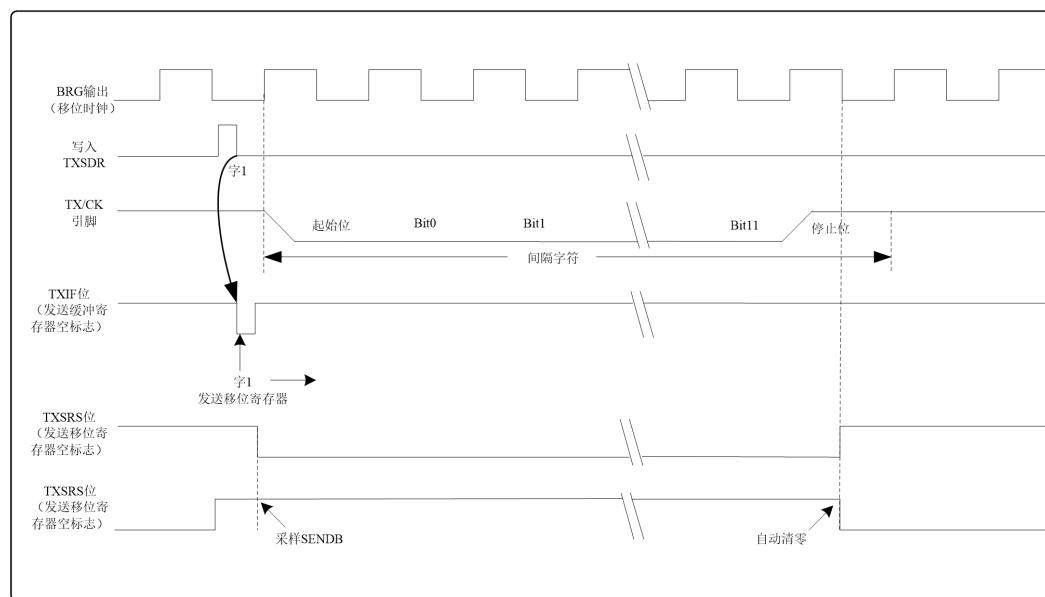

| 11.5.5.1 间隔和同步发送序列.....              | 121 |

| 11.5.5.2 接收间隔字符.....                 | 122 |

|                                   |            |

|-----------------------------------|------------|

| 11.6 USART 全双工模式.....             | 123        |

| 11.6.1 USART 全双工发送操作.....         | 124        |

| 11.6.1.1 发送状态和控制寄存器 TSCTL.....    | 124        |

| 11.6.1.2 发送数据.....                | 125        |

| 11.6.1.3 全双工发送的设置.....            | 125        |

| 11.6.2 USART 全双工接收操作.....         | 126        |

| 11.6.2.1 接收状态和控制寄存器 RSCTL.....    | 127        |

| 11.6.2.2 接收数据.....                | 128        |

| 11.6.2.3 接收错误.....                | 128        |

| 11.6.2.4 地址检测.....                | 129        |

| 11.6.2.5 全双工接收的设置.....            | 129        |

| 11.6.3 RS-485 发送/接收.....          | 130        |

| 11.6.3.1 RS-485 9 位地址检测模式设置.....  | 130        |

| 11.6.4 全双工操作时钟的精确性.....           | 131        |

| 11.7 USART 半双工模式.....             | 131        |

| 11.7.1 USART 半双工主控模式.....         | 131        |

| 11.7.1.1 半双工主控发送.....             | 131        |

| 11.7.1.2 半双工主控接收.....             | 133        |

| 11.7.2 USART 半双工从动模式.....         | 134        |

| 11.7.2.1 USART 半双工从动发送.....       | 135        |

| 11.7.2.2 USART 半双工从动接收.....       | 135        |

| 11.7.3 USART 半双工 RS-485 模式.....   | 136        |

| <b>10 电容触摸模块.....</b>             | <b>137</b> |

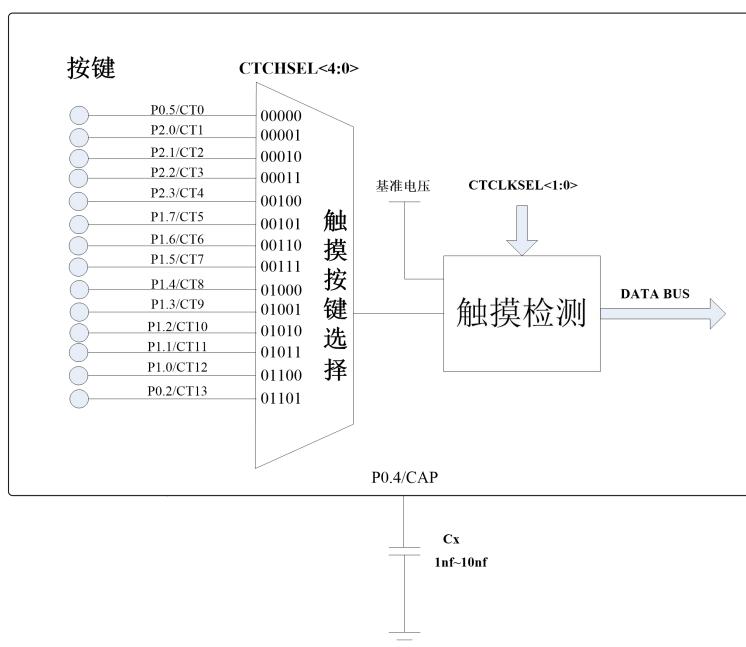

| 10.1 电容触摸的原理.....                 | 137        |

| 10.2 电容触摸相关寄存器.....               | 138        |

| 10.2.1 电容触摸控制寄存器 0 (CTCTL0) ..... | 138        |

| 10.2.2 电容触摸控制寄存器 1 (CTCTL1) ..... | 139        |

| 10.2.3 电容触摸控制寄存器 2 (CTCTL2) ..... | 140        |

| 10.2.4 电阻分压比 1 设置寄存器 (VDAC) ..... | 140        |

| 10.2.5 电阻分压比 2 设置寄存器 (VRES) ..... | 141        |

| 10.2.6 电阻分压源选择寄存器 (VDACS) .....   | 141        |

| 10.3 触摸中断.....                    | 141        |

| 10.4 伪随机序列.....                   | 141        |

| 10.5 触摸的使用.....                   | 141        |

| 10.5.1 单周期模式.....                 | 141        |

| 10.5.2 周期扫描模式.....                | 142        |

| <b>11 模拟比较器模块.....</b>            | <b>143</b> |

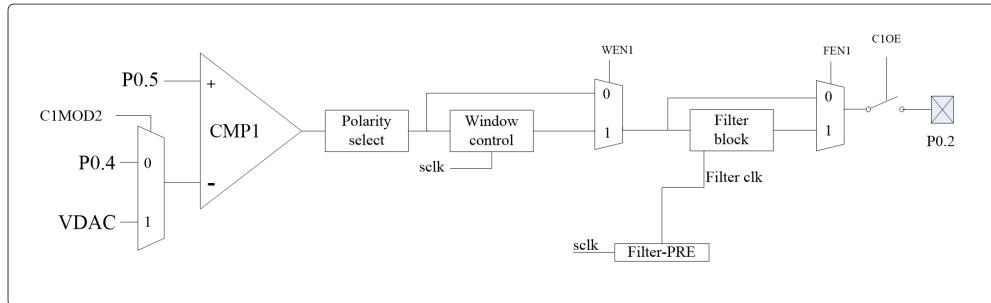

| 11.1 模拟比较器原理.....                 | 143        |

| 11.2 相关寄存器.....                   | 143        |

| 11.3 CMP1 相关寄存器.....              | 143        |

| 11.3.1 比较器 1 控制寄存器 C1CTL.....     | 143        |

| 11.3.2 比较器 1 校准寄存器 C1CAL.....     | 144        |

|                                       |            |

|---------------------------------------|------------|

| 11.3.3 滤波器 1 控制寄存器 C1FILTCTL.....     | 144        |

| 11.3.4 滤波器 1 采样时钟分频寄存器 C1FILTPRE..... | 145        |

| 11.4 极性选择.....                        | 145        |

| 11.5 范围控制功能.....                      | 145        |

| 11.6 滤波功能.....                        | 146        |

| 11.7 比较器中断.....                       | 146        |

| 11.8 比较器的校准步骤.....                    | 146        |

| 11.9 比较器使用.....                       | 147        |

| 11.10 复位的影响.....                      | 147        |

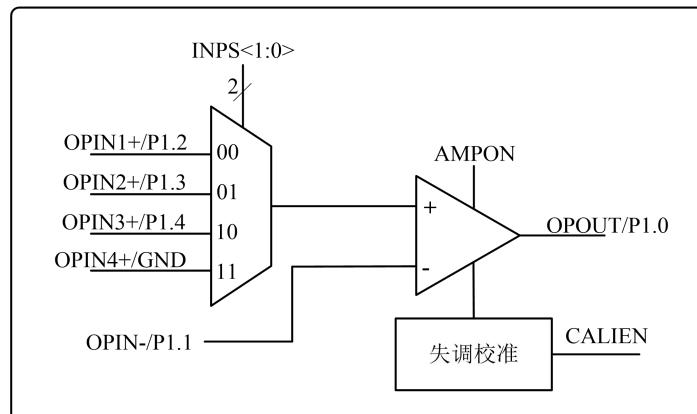

| <b>12 运算放大器模块.....</b>                | <b>148</b> |

| 12.1 与运放相关的寄存器.....                   | 148        |

| 12.1.1 运放控制寄存器.....                   | 148        |

| 12.1.2 运放校验寄存器.....                   | 149        |

| 12.2 运放使用方法.....                      | 149        |

| 12.2.1 校验方法.....                      | 149        |

| 12.2.2 使用方法.....                      | 150        |

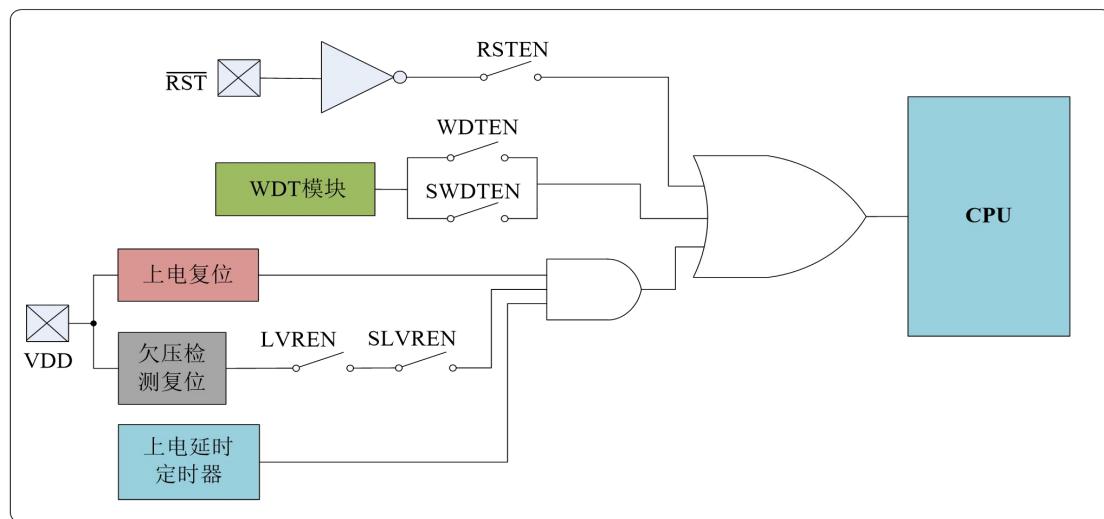

| <b>13 复位.....</b>                     | <b>151</b> |

| 13.1 电源控制状态寄存器(PCTL).....             | 151        |

| 13.2 上电复位(POR).....                   | 152        |

| 13.3 WDT 复位.....                      | 152        |

| 13.4 RST 复位.....                      | 152        |

| 13.5 欠压检测复位(LVR).....                 | 152        |

| 13.6 上电延时定时器.....                     | 153        |

| 13.7 不同复位条件下对寄存器的影响.....              | 154        |

| <b>14 休眠模式.....</b>                   | <b>156</b> |

| <b>15 看门狗定时器 WDT.....</b>             | <b>157</b> |

| 15.1 看门狗相关寄存器.....                    | 157        |

| 15.1.1 WDT 预分频选择寄存器.....              | 157        |

| 15.2 看门狗的开启关闭方式.....                  | 157        |

| 15.3 看门狗的清狗方式.....                    | 157        |

| 15.4 看门狗 WDT 的周期.....                 | 158        |

| <b>16 电气规范.....</b>                   | <b>159</b> |

| 16.1 极限参数值.....                       | 159        |

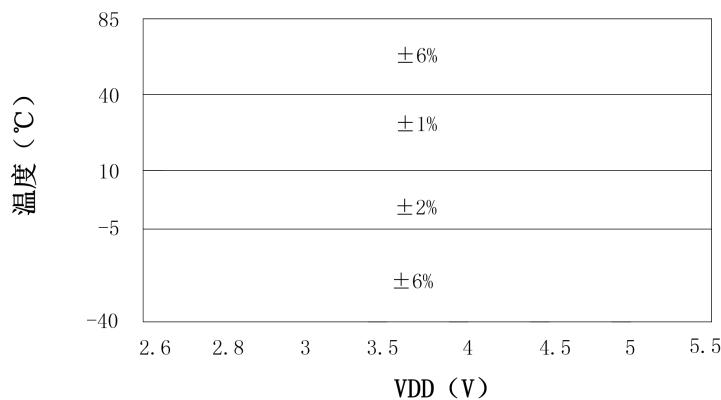

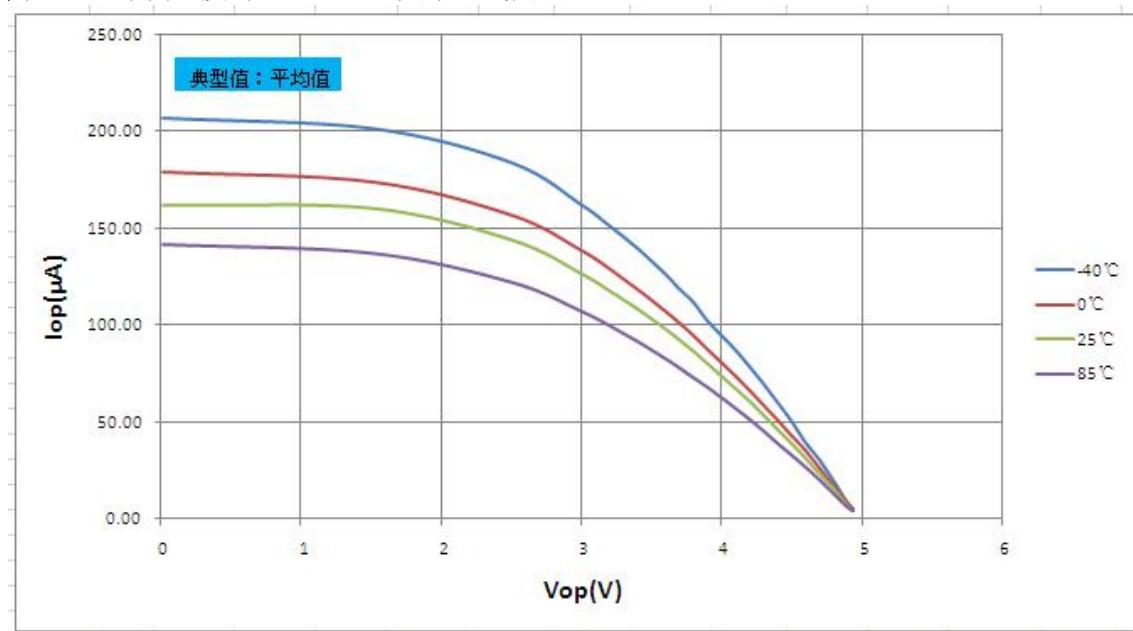

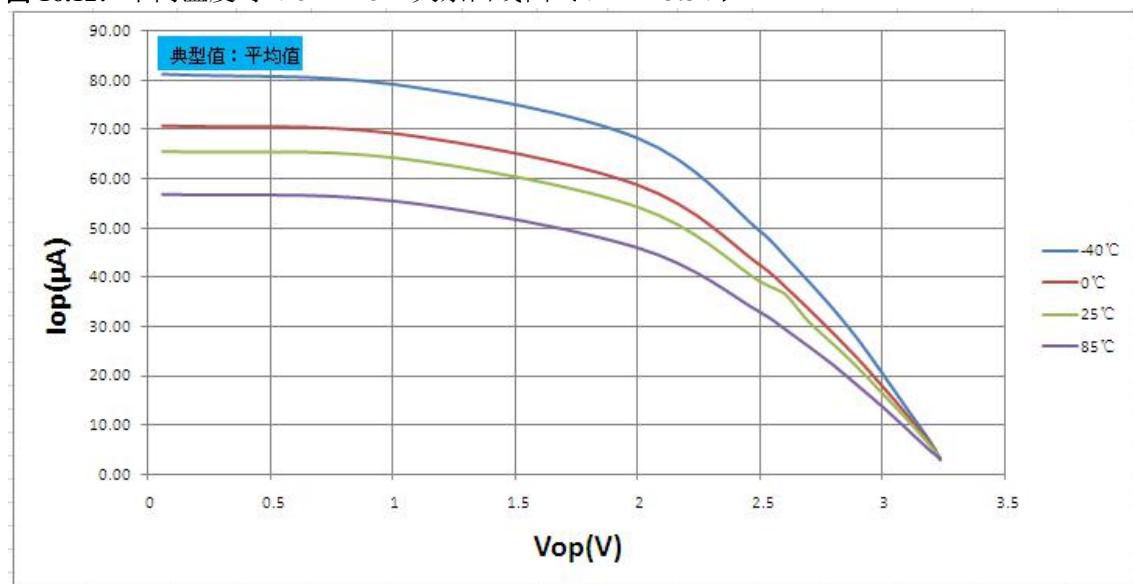

| 16.2 HFINT 的频率精度与器件 VDD 和温度之间的关系..... | 160        |

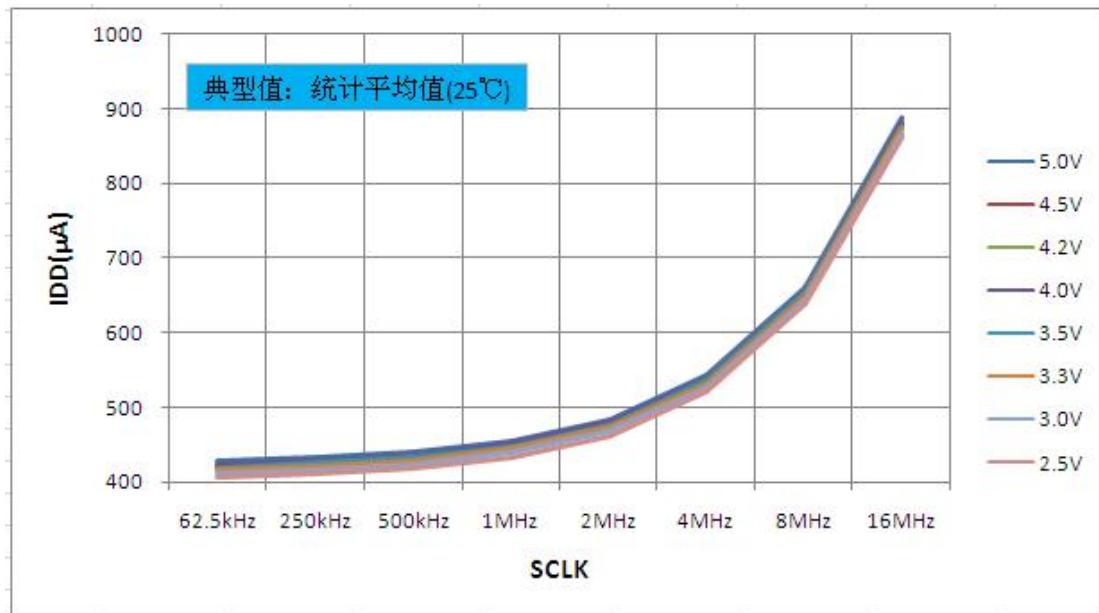

| 16.3 静态电流特性.....                      | 160        |

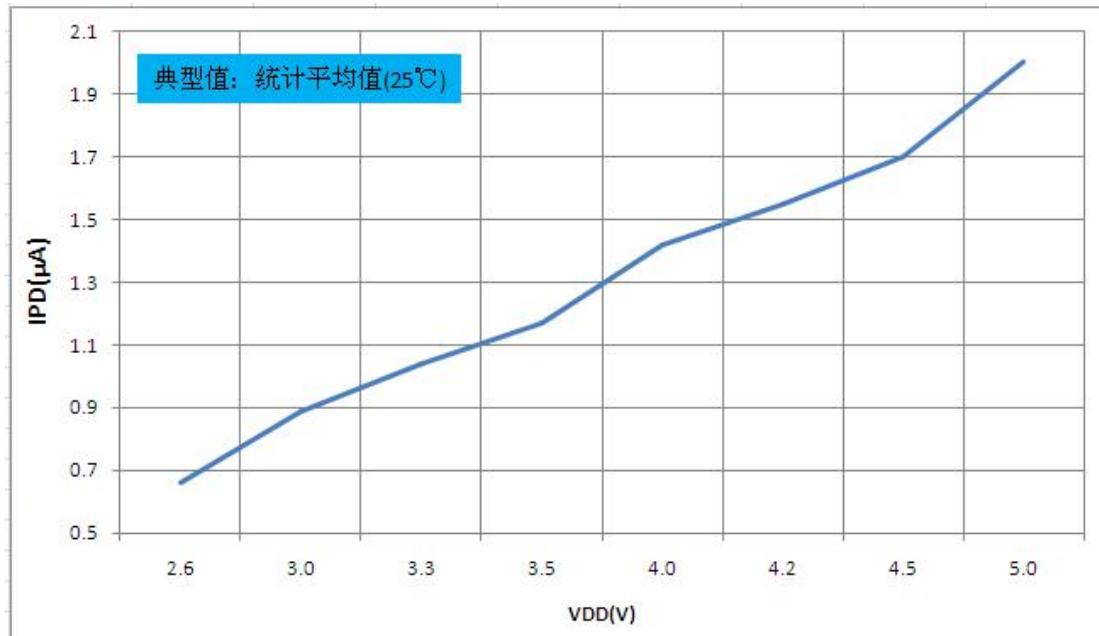

| 16.4 外设电流特性.....                      | 161        |

| 16.5 I/O 端口特性.....                    | 161        |

| 16.6 芯片供电电压特性.....                    | 162        |

| 16.7 A/D 转换器 (ADC) 特性.....            | 162        |

| 16.8 内部参考电压模块特性.....                  | 162        |

|                            |     |

|----------------------------|-----|

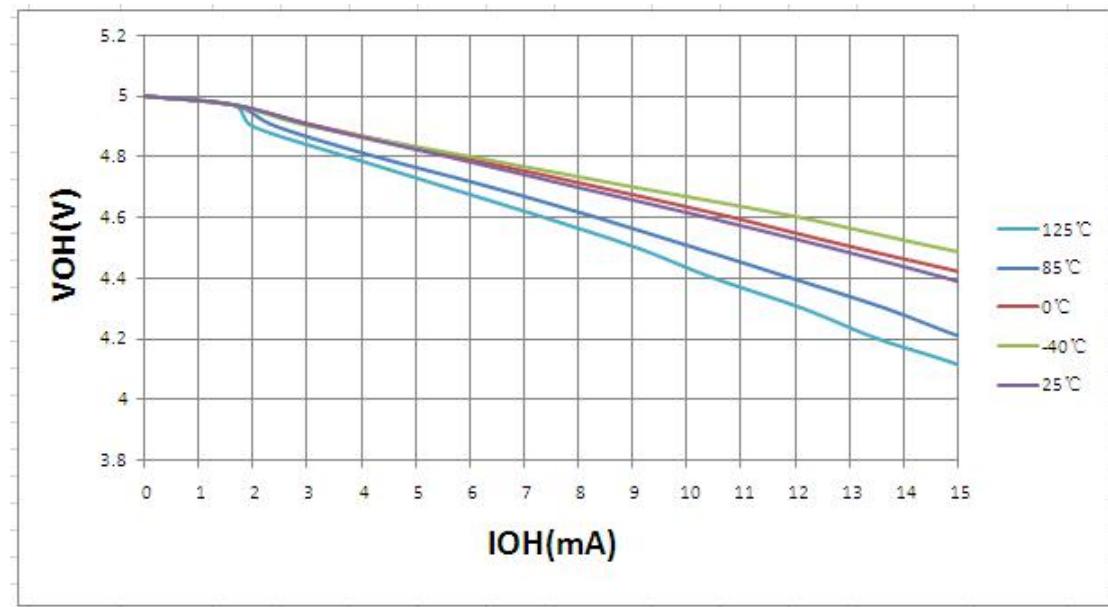

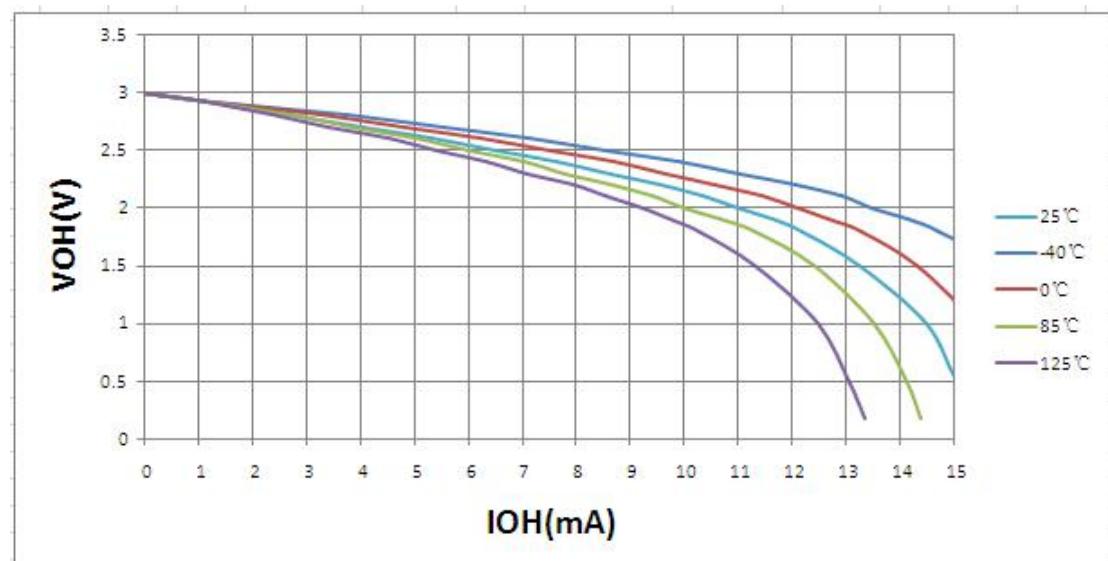

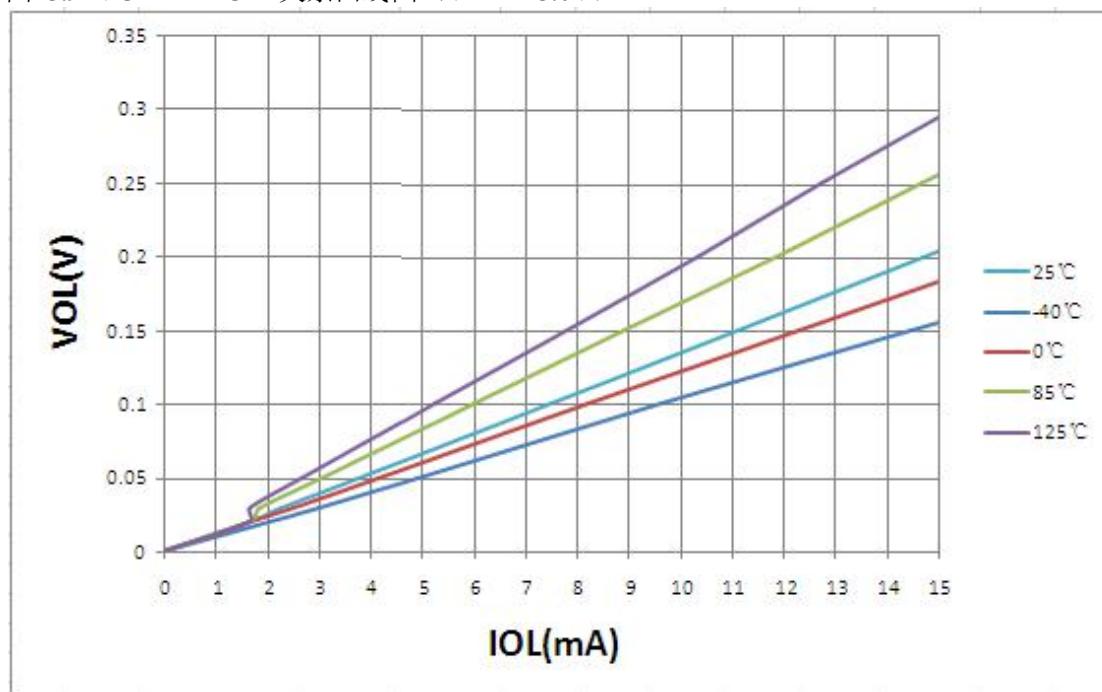

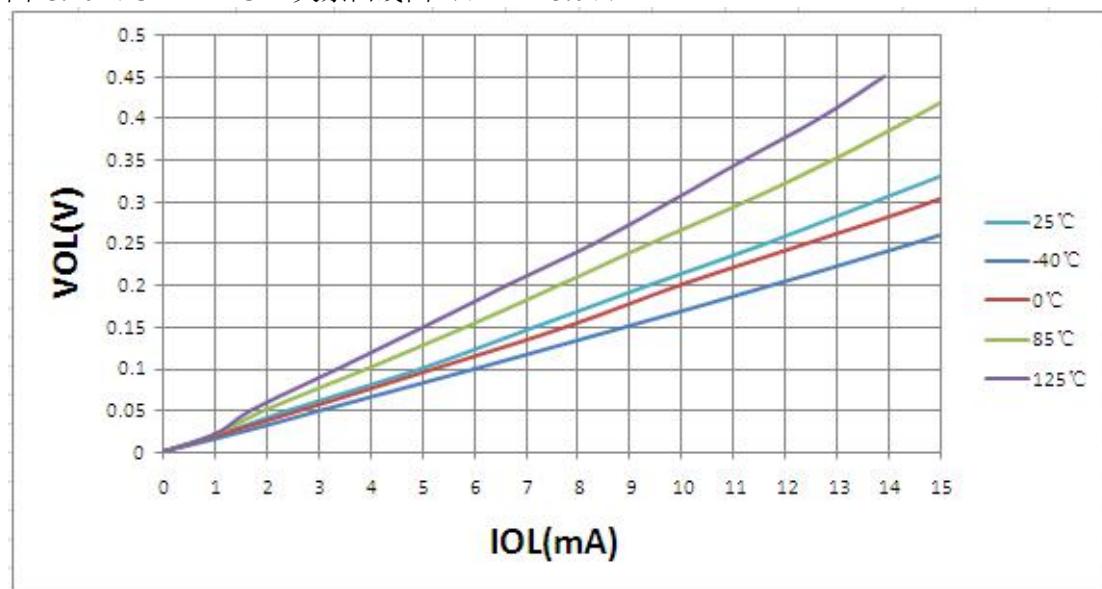

| 17 直流特性图表.....             | 163 |

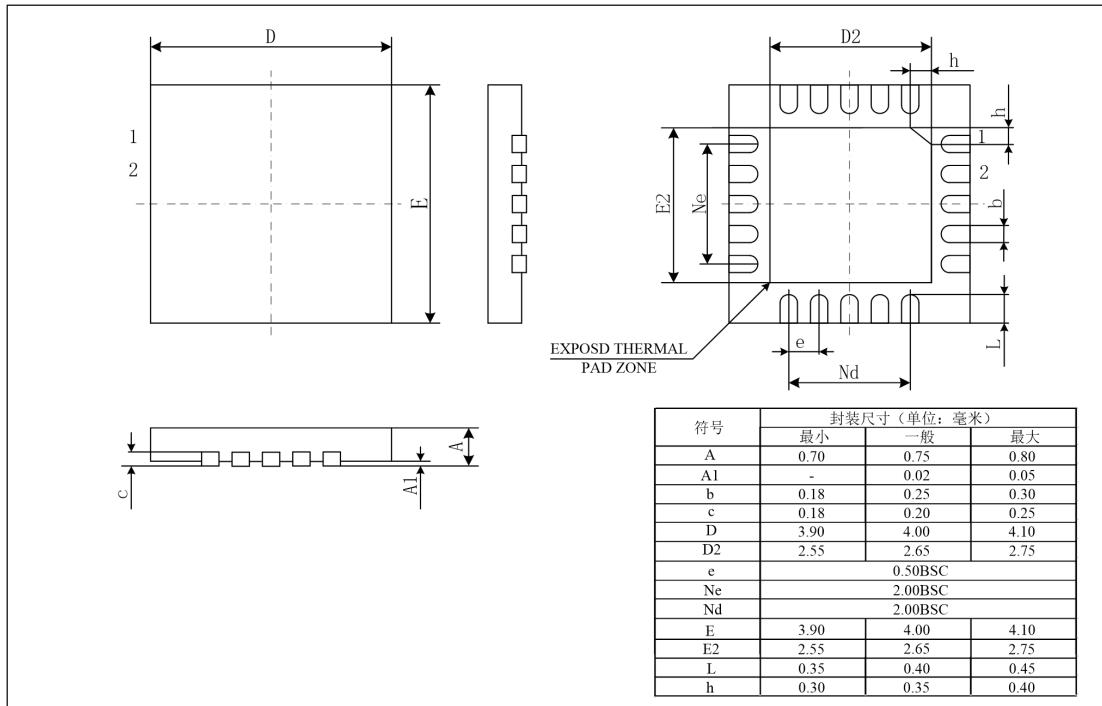

| 18 封装信息.....               | 169 |

| 附录 1 特殊功能寄存器（SFR）功能汇总..... | 170 |

| 附录 2 汇编指令集.....            | 172 |

| 附录 3 寄存器全称表.....           | 174 |

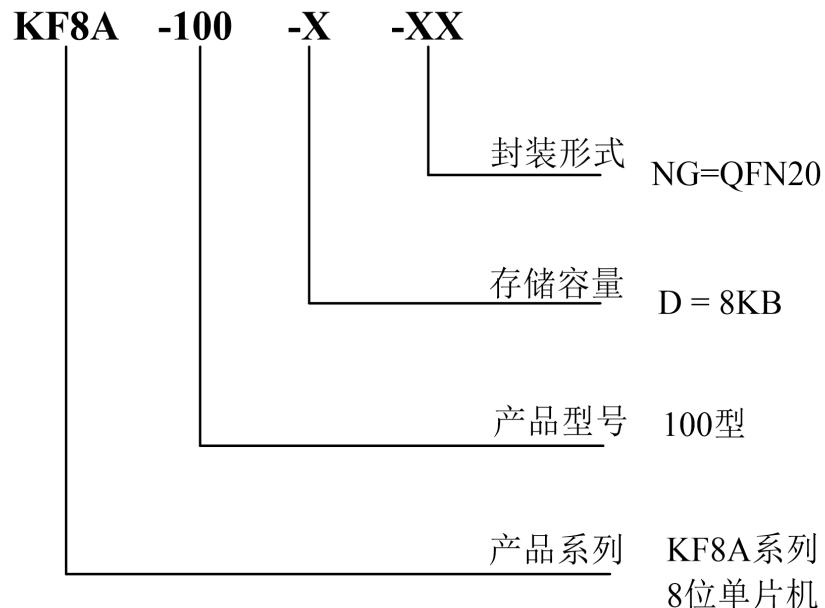

| 产品标识体系.....                | 176 |

| 版本说明.....                  | 177 |

| ROHS 认证.....               | 178 |

| 声明及销售网络.....               | 179 |

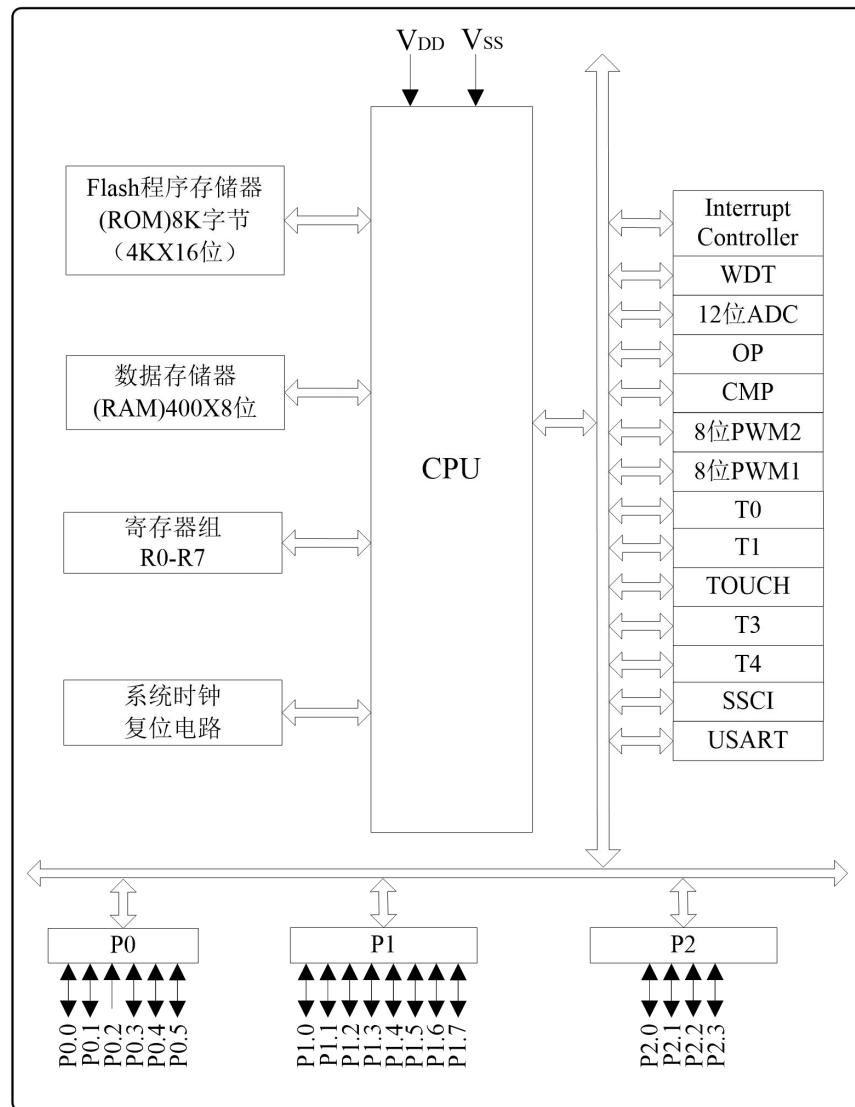

## 1 系统概述

KF8A100ENG 为哈佛结构的精简指令 CPU。在这种结构中，程序和数据总线是相互独立的。指令字节长度为 16 位，大多数指令能在一个机器周期内执行完成。一共有 73 条指令，效率高，容易进行指令扩展。

KF8A100ENG 芯片内集成了多种外设，包括 1 个 8 位定时器/计数器 T0、1 个 16 位定时器/计数器 T1、1 个 16 位的定时器 T3、一个 16 位定时/计数器 T4、1 个 12 位 14 通道 AD 模块、1 个比较器模块、1 个运算放大器模块、2 路 8 位的 PWM 模块、一个 14 通道电容触摸模块、1 个 I2C 模块、1 个 USART 模块、内部参考电压模块、硬件看门狗和低电压检测及低电压复位模块等。

芯片内集成了  $1040 \times 8$  位的用户数据存储器和  $8K \times 16$  位的程序存储器。

## 1.1 芯片特征

### ● CPU

- 高性能哈佛结构的 RISC CPU

- 73 条精简指令

- 支持中断优先级处理，共 16 个中断源

- 复位向量位于 0000H

- 两级中断可选，用不同的入口地址（高 0004H，低 0014H）

- 支持 16 级硬件堆栈

- 工作频率默认内部高频，内部高频范围 62.5kHz~16MHz，软件可选时钟源及分频

### ● 存储器

- 16K 字节（8K×16 位）FLASH 程序存储器

- (1024+16)×8 位的数据存储器

- 工作寄存器组 R0~R7

- FLASH 可经受 100 000 次写操作

### ● 特殊功能

- 内嵌上电复位电路

- 低电压检测及低电压复位

- 硬件看门狗

- 内部高频时钟精度 16MHz±1% (常温)

- 内部可校正低频 32kHz 时钟

- 2/3/4V 可选内部参考电压

- 支持在线串行编程

- 低功耗休眠模式

### ● I/O 口配置

- 输入输出口：除 P0.3 只能作为输入口外其它端口均为双向输入输出口

- 内置上拉功能：P0/P1/P2 口带有弱上拉功能(P0.3 除外)

- 电平变化中断：P0 口均有电平变化中断功能

- IO 口数字输入类型：P0/P1/P2 口为 SMIT 型

### ● 定时器/计数器

- 定时器 0：带有 8 位预分频器的 8 位定时器/计数器

- 定时器 1：带门控和预分频器的 16 位定时器/计数器

- 定时器 3：时钟源可选的 16 位定时器

- 定时器 4：带有重载功能、预分频及时钟源多选的的 16 位定时器/计数器

### ● 其它外设

- 2 路 8 位脉宽调制 PWM 模块

- 1 个 12 位 14 通道 ADC 模块

- 1 个带数字滤波和校准的比较器模块

- 1 个带校准的运算放大器模块

- 1 个 14 通道的触摸模块

1 个 I2C 模块

1 个 USART 模块

- AEC-Q100 认证

- 工作条件

工作电压: 2.6V~5.5V

工作温度范围: -40°C~+125°C

## 1.2 系统框图

### 1.3 存储器

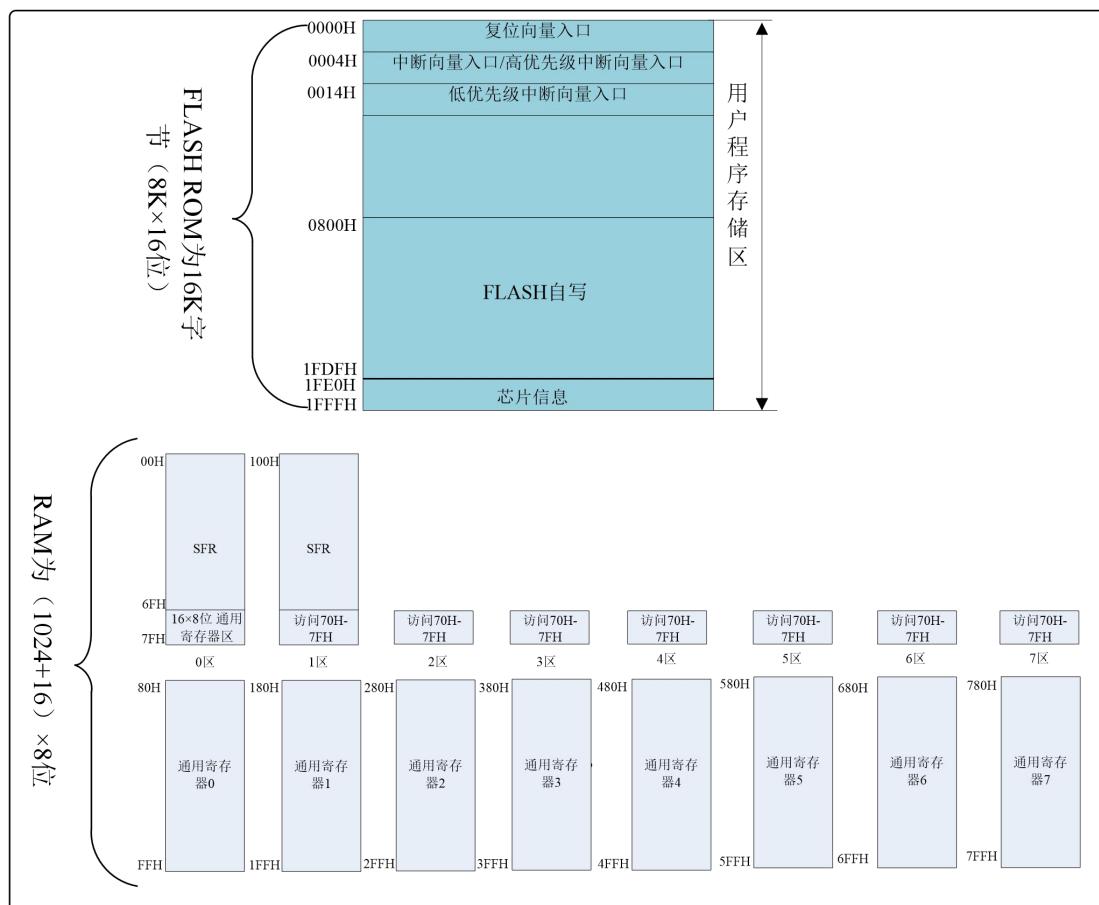

单片机的存储器包含:程序存储器(ROM)和数据存储器(RAM)。

程序存储器空间为 16K 字节 (8K×16 位), 寻址范围为 0000H~1FFFH, 可擦写次数为 10 万次。数据存储器分为特殊寄存器区(SFR)和通用存储器区, 其中通用存储器区包括通用存储器区 0 至通用存储器区 2。通用存储器区 0 至通用存储器区 2 均有 128×8 位的存储单元, 各区的地址请查阅第 3 章。

有关以上各种存储器的具体介绍请参考第 3 章。

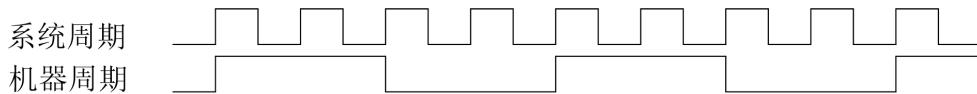

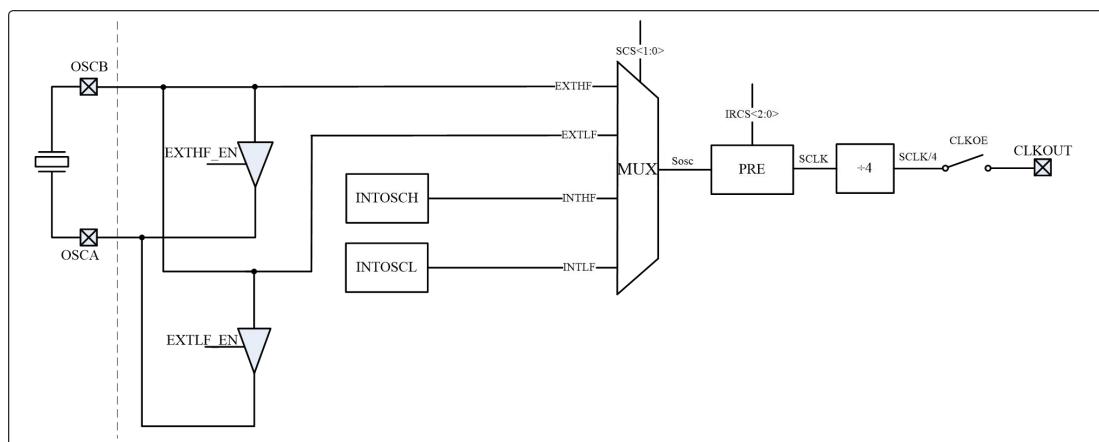

## 1.4 系统时钟

系统时钟是由系统时钟源分频而来。本芯片中一个机器周期等于四个系统周期，如图 1.1 所示。本芯片除执行部分跳转指令需要两个机器周期外，其余指令仅需要一个机器周期。

图 1.1 机器周期

单片机提供 4 个可选系统时钟源：

INTHF：以内部高频振荡器为系统时钟源；

INTLF：以内部低频振荡器为系统时钟源；

EXTHF：标准晶振、陶瓷谐振器或外接 16MHz~125kHz 的时钟源工作；

EXTLF：外接 32.768kHz 的钟表晶振作为系统时钟源。

图 1.2 时钟模块原理框图

系统时钟源可以配置为 EXTHF、EXTLF、INTHF 或者 INTLF。

外部高频时钟和外部低频时钟共用外部时钟引脚，不能同时使用两个外部时钟源。

表 1-1 与时钟有关的名词表述

| 名称                                  | 定义即描述         |

|-------------------------------------|---------------|

| Sosc                                | 振荡器时钟源        |

| SCLK                                | 系统时钟          |

| SCLK/4                              | 机器时钟          |

| T <sub>sys</sub> 或 T <sub>sys</sub> | 系统时钟周期        |

| T <sub>mc</sub> 或 T <sub>mc</sub>   | 机器周期          |

| INTOSCH(INTHF)                      | 内部高频振荡器（时钟源）  |

| T <sub>INTHF</sub>                  | 内部高频振荡器周期     |

| INTOSCL(INTLF)                      | 内部低频振荡器（时钟源）  |

| EXTOSCH(EXTHF)                      | 外部高频振荡器（时钟源）  |

| EXTOSCL(EXTLF)                      | 外部低频振荡器（时钟源）  |

| OSC                                 | 定义为 4 个振荡器的集合 |

## 1.4.1 时钟模块相关寄存器

| 地址  | 寄存器    | 位 7   | 位 6   | 位 5   | 位 4   | 位 3  | 位 2  | 位 1  | 位 0  |

|-----|--------|-------|-------|-------|-------|------|------|------|------|

| 2FH | OSCCTL | CLKOE | IRCS2 | IRCS1 | IRCS0 | SCS1 | SCS0 | IESO | FSCM |

| 28H | OSCSTA | -     | OSTS  | HTS   | LTS   | -    | -    | SCF1 | SCF0 |

### 1.4.1.1 系统频率控制寄存器 OSCCTL

寄存器1.2: OSCCTL系统频率控制寄存器(地址:2FH)

| 复位值       | bit7      | bit0      |

|-----------|-----------|-----------|

| 0010 0000 | CLKOE R/W | IRCS2 R/W |

CLKOE: 系统时钟输出使能位

1=使能系统时钟输出

0=禁止系统时钟输出

IRCS<2:0>: 时钟频率选择位

111=1:1 (选择内部高频时钟为 16MHz)

110=1:2 (选择内部高频时钟为 8MHz)

101=1:4 (选择内部高频时钟为 4MHz)

100=1:8 (选择内部高频时钟为 2MHz)

011=1:16 (选择内部高频时钟为 1MHz)

010=1:32 (默认, 选择内部高频时钟为 500kHz)

001=1:64 (选择内部高频时钟为 250kHz)

000=1:256 (选择内部高频时钟为 62.5kHz)

SCS<1:0>: 系统时钟选择位

00=选择内部高频时钟

01=选择内部低频时钟

10=选择外部低频时钟

11=选择外部高频时钟

IESO: 双速模式使能位

0=禁止双速功能

1=启动双速功能

FSCM: 外部时钟故障检测使能位

0=禁止故障检测功能

1=使能故障检测功能

图注: R=可读 W=可写 - =未用 U=未实现位

### 1.4.1.2 系统时钟标志寄存器 OSCSTA

OSCSTA系统时钟标志寄存器(地址:28H)

| 复位值<br>0110 -00 | bit7 |      |     |     |   |   |      | bit0 |  |

|-----------------|------|------|-----|-----|---|---|------|------|--|

|                 | -    | OSTS | HTS | LTS | - | - | SCF1 | SCF0 |  |

|                 | R    | R    | R   | R   | U | U | R    | R    |  |

OSTS: 内外时钟标志位

0=系统时钟为外部时钟

1=系统时钟为内部时钟

HTS: 内部高频时钟稳定位

0=内部高频时钟未稳定

1=内部高频时钟稳定

LTS: 内部低频时钟稳定位

0=内部低频时钟未稳定

1=内部低频时钟稳定

SCF<1:0>: 系统时钟源标志位

00=当前系统时钟源为内部高频时钟

01=当前系统时钟源为内部低频时钟

10=当前系统时钟源为外部低频时钟

11=当前系统时钟源为外部高频时钟

图注: R=可读 W=可写 -=未用 U=未实现位

### 1.4.2 上电延时

上电延时可以通过配置位  $\overline{PWRT}$  设置，上电延时计数时钟 PWRTCLK 为内部低频时钟。

当  $\overline{PWRT}=1$  时，上电延时关闭；

当  $\overline{PWRT}=0$  时，上电延时打开，延时时间如下:  $T_{pwrt} = \frac{2^{10}}{PWRTCLK}$ 。

### 1.4.3 内部高频时钟 INTHF

内部高频时钟由系统内部高频振荡器提供，时钟频率为 16MHz，精度为±1%(常温)。

### 1.4.4 内部低频时钟 INTLF

内部低频时钟 INTLF 由系统内部低频振荡器提供，其振荡器频率为 32KHz，它不仅可以为 SCLK 时钟提供时钟源，而且还可以独立作为时钟信号供外设模块（上电延时定时器、看门狗定时器等）使用。

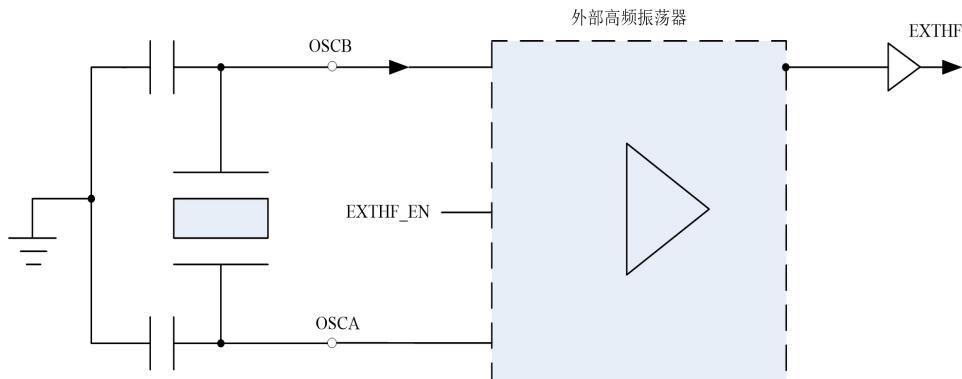

### 1.4.5 外部高频时钟 EXTHF

如图 1.3 所示，引脚 OSCA 和引脚 OSCB 可以接外部标准晶体、陶瓷谐振器或外接 16MHz~125kHz 的时钟为时钟源。EXTHF 可提供主系统时钟 SCLK。

图 1.3 EXTHF 原理图

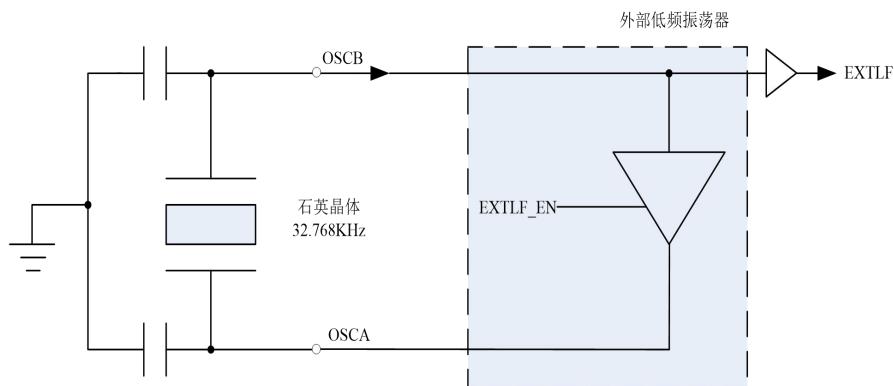

### 1.4.6 外部低频时钟 EXTLF

如图 1.4 所示，引脚 OSCA 和引脚 OSCB 接外部钟表石英晶体，主要是以 32.768kHz 的晶体提供时钟源。EXTLF 可提供主系统时钟 SCLK。

图 1.4 EXTLF 原理图

注：使用外部低频时钟首先要将 T1CTL 的 T1OSCEN 位置 1。

### 1.4.7 时钟切换和时钟信号同步

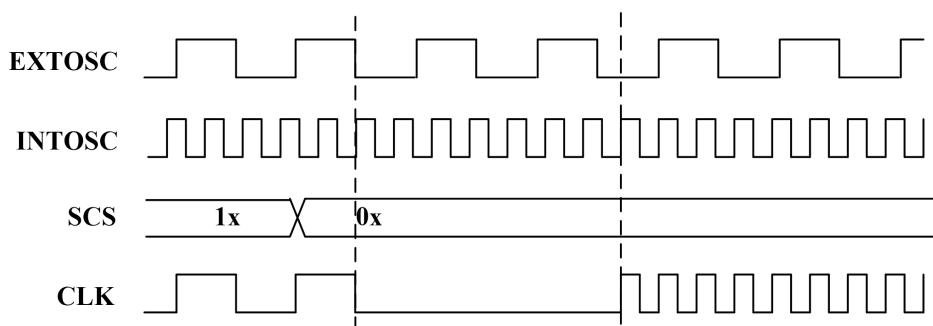

通过设置 OSCCTL 寄存器的 SCS<1:0>位可以选择不同的时钟源作为系统时钟。SCS 位复位为 00，即选择内部高频时钟源作为单片机的系统时钟。

当系统时钟由外部时钟源切换至内部时钟源时，系统时钟将在 SCS 配置后立即对时钟进行切换。

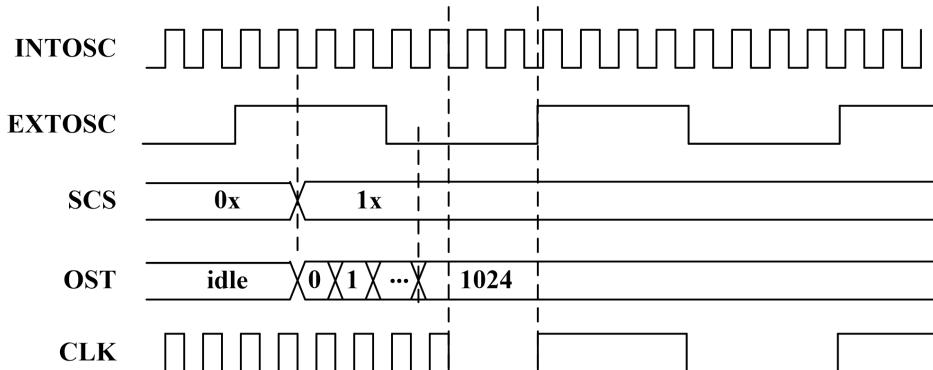

当配置 SCS 位将系统时钟切换至外部时钟源时（包括 EXTHF 和 EXTLF），振荡器起振定时器 OST 将启动，并以 SCS 位配置的外部时钟为计数时钟开始计数，OST 计数的时间内，系统仍以原来的时钟源作为系统时钟，直到 OST 计数器达到 1024 次计数，系统时钟源切换至 SCS 位配置的外部时钟。

图 1.5 时钟切换流程图

当系统时钟在一个时钟源切换到另一个时钟源时，切换必须同步以避免发生时间竞争。当选择一个新的时钟源，会发生以下过程。

- (1) 写 SCS 位改变时钟源；如切换至外部时钟源则须经过 OST 计数器 1024 计数；

- (2) 时钟切换电路等待当前时钟的下降沿；

- (3) 时钟 CLK 保持为低电平，时钟切换电路等待新的时钟的上升沿；

- (4) CLK 与新的时钟连接，完成时钟切换。

图 1.6 切换至内部时钟源时时钟信号同步时序图

图 1.7 切换至外部时钟源时时钟信号同步时序图

#### 1.4.8 双速启动模式

当系统时钟选择外部时钟进入休眠后，唤醒时，外部时钟需要经过 OST 计数器完成 1024 次计数后才会恢复系统时钟。

双速启动模式通过寄存器 OSCCTL 的 IESO 位设置，当使能双速模式时，MCU 会在唤醒后外部时钟进行 OST 计数期间，通过内部高频时钟作为系统时钟运行，当外部时钟完成 OST 计数后，MCU 会自动将系统时钟从内部高频时钟切换至外部时钟。

#### 1.4.9 双速启动过程

1. 从休眠状态唤醒;

2. 内部高频振荡器作为时钟源开始执行指令;

3. 使能 OST 计数器对外部时钟计数 1024 个时钟周期;

4. OST 超时, 等待内部时钟下降沿;

5. 系统时钟保持低电平直到新的时钟的下一个下降沿;

6. 系统时钟切换到外部时钟源。

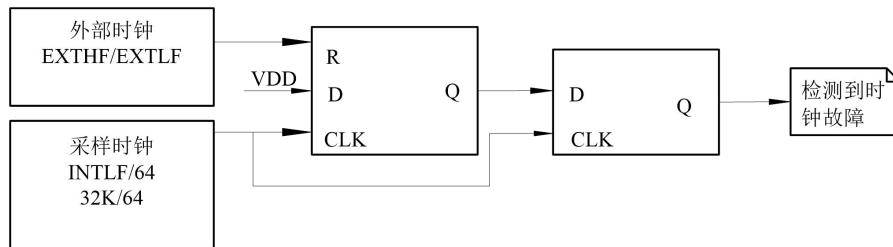

#### 1.4.10 外部时钟故障检测

故障保护时钟监视(FSCM)能使器件在振荡器发生故障时继续运行, 其可以检测出振荡器起振定时器(OST)延时结束后的任何时刻发生的振荡器故障。

将 OSCCTL 寄存器的 FSCM 位置 1 使能 FSCM, 适用于外部振荡器模式。

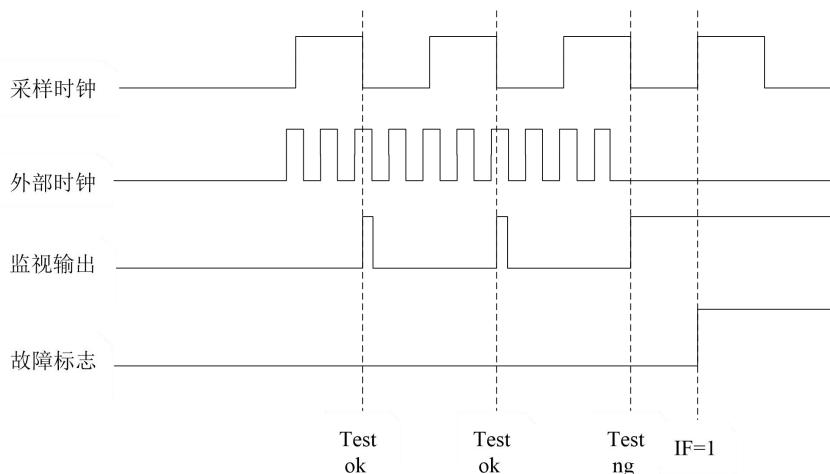

图 1.8 时钟故障检测原理图

FSCM 模块在采样时钟下降沿将第一个寄存器置 1, 在外部时钟下降沿将该寄存器复位为 0, 由于外部时钟频率远大于采样时钟频率, 所以当第一个寄存器刚被采样时钟置 1 不久就被外部时钟复位, 经过第二个寄存器(CLK 为采样时钟)后的 Q 值将保持为 0; 当发生外部时钟故障时, 第一个寄存器由于外部时钟故障而失去复位能力, 当采样时钟下降沿到达置 1 后, 将一直保持输出为 1, 检测到故障。

图 1.9 时钟故障检测时序

注: 系统时钟频率实际比采样时钟大很多, 图示为方便分析起见将频率差异减小。

### 1.4.11 时钟故障保护处理

检测到时钟故障后，系统时钟将自动切换至内部高频时钟源继续工作，分频值由OSCCTL寄存器的IRCS<2:0>设置，直到器件固件成功重启外部振荡器并使时钟重新切换到外部振荡器为止。

在切换至内部高频时钟源后，时钟故障标志位置1，如果打开时钟故障中断使能位，程序将进入中断行。

## 1.5 芯片初始化

用户需在初始化程序中，需要添加相关校准程序，以保证芯片稳定工作。初始化程序如例 1.1 所示。

### 例1.1 芯片初始化程序

```

CALL    0xFFFF

MOV    OSscal0, R0

NOPZ

NOPZ

CALL    0xFFE

MOV    OSscal1, R0

NOPZ

NOPZ

CALL    0xFFD

MOV    OSscal2, R0

NOPZ

NOPZ

CALL    0xFFC

MOV    OSscal3, R0

NOPZ

NOPZ

CALL    0xFFB

MOV    VRECAL1, R0

NOPZ

NOPZ

MOVB   #0X01          ;切换到存储区1区

CALL    0FFA

MOV    VRECAL2 , R0

NOPZ

NOPZ

CALL    0FF9

MOV    VRECAL3 , R0

NOPZ

NOPZ

MOVB   #0X00          ;读取相关校准值后需切换回存储器0区

```

## 1.6 配置位

如寄存器 1.2 所示，用户在烧写程序时，在编程器中通过对配置位进行设置，使单片机启用诸如看门狗、程序代码保护、欠压检测等功能。

CONFIG: 配置字

|       |    |    |    |    |              |        |      |              |       |       |             |       |    |    |      |

|-------|----|----|----|----|--------------|--------|------|--------------|-------|-------|-------------|-------|----|----|------|

| 保留    | 保留 | 保留 | 保留 | 保留 | <u>DEBUG</u> | SWRTEN | 保留   | <u>CODEP</u> | LVREN | RSTEN | <u>PWRT</u> | WDTEN | 保留 | 保留 | 保留   |

| bit15 |    |    |    |    |              |        | bit8 |              |       |       |             |       |    |    | bit0 |

DEBUG: 在线调试使能位

1 = 禁止在线调试

0 = 使能在线调试

SWRTEN: FLASH 自写保护使能位

1 = 使能写保护，此时 FLASH 不能写操作，(可读)

0 = 禁止写保护，此时 FLASH 可写，(可读)

CODEP: 代码保护使能位

1 = 禁止程序存储器代码保护

0 = 使能程序存储器代码保护

LVREN: 欠压检测功能使能位

1 = 使能欠压检查功能

0 = 禁止欠压检查功能

RSTEN: P0.3/RST 引脚功能选择

1 = P0.3/RST 引脚配置为外部复位输入

0 = P0.3/RST 引脚功能为数字输入口

PWRT: 上电延时使能位

0 = 使能上电延时

1 = 禁止上电延时

WDTEN: 看门狗定时器(WDT)使能位

1 = 使能 WDT

0 = 禁止 WDT

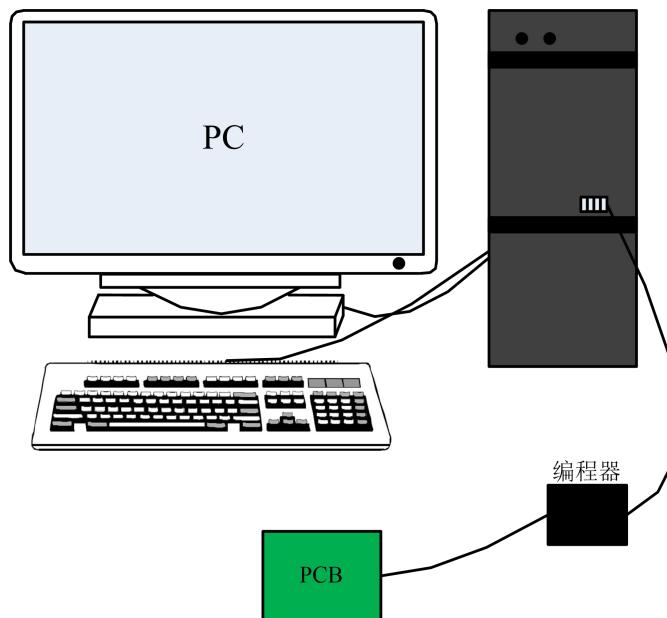

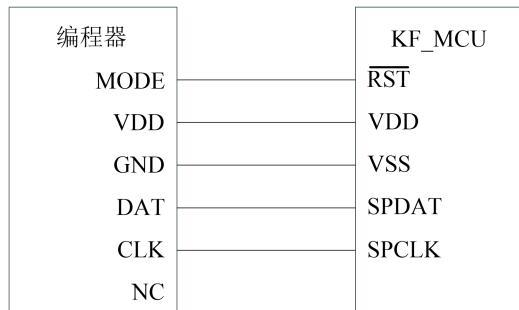

## 1.7 在线串行编程

如图 1.10 所示，在最终应用电路中可对 KF8A100ENG 单片机进行在线串行编程。实现编程需要五根线包括：复位线（RST）、时钟线(SPCLK)、数据线(SPDAT)、电源线(VDD)、地线(Vss)。

用户只需确保芯片与编程器按照图 1.11 所示连接方法，即可对其进行在线编程，调试等。

图 1.10 在线调试系统示意图

图 1.11 在线串行编程连接图

## 2 I/O 端口介绍

KF8A100ENG 单片机共有 20 个引脚，1 脚接电源正极，20 脚接电源负极，其余管脚均为 I/O 端口，包括 P0 口、P1 口和 P2 口。P0 口共有 P0.0~P0.5 六个引脚，P1 口共有 P1.0~P1.7 八个引脚，P2 口共有 P2.0~P2.3 四个引脚。

注：1、用户在正常使用时，通常会有一些用不到的引脚，如果直接把这些管脚悬空，而不做其他处理可能使单片机功耗增大，因此建议将那些不用的引脚设置为数字输出模式，如果 P0.3 未用，应外接上拉电阻，并对地接一个电容。

### 2.1 I/O 端口的读写

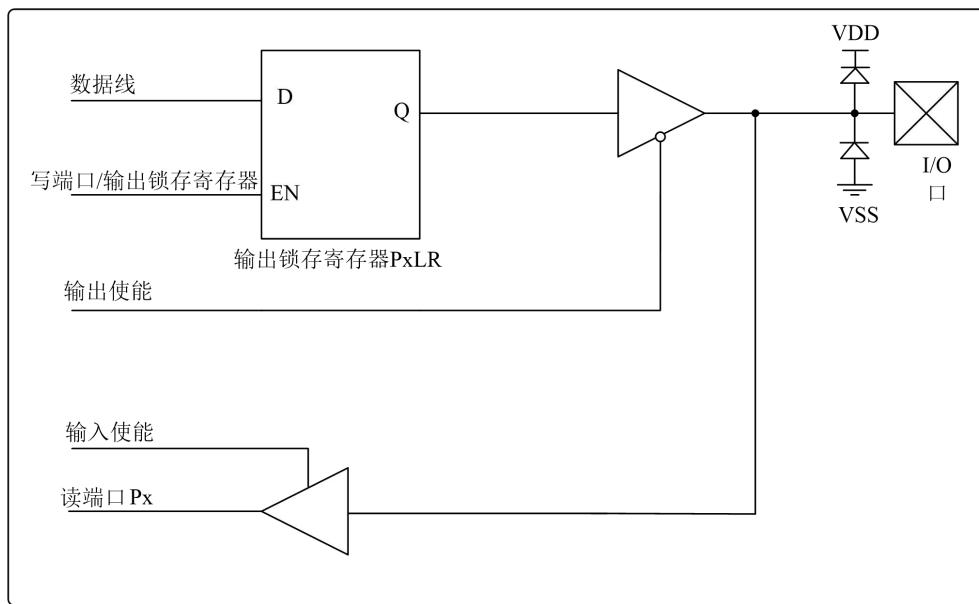

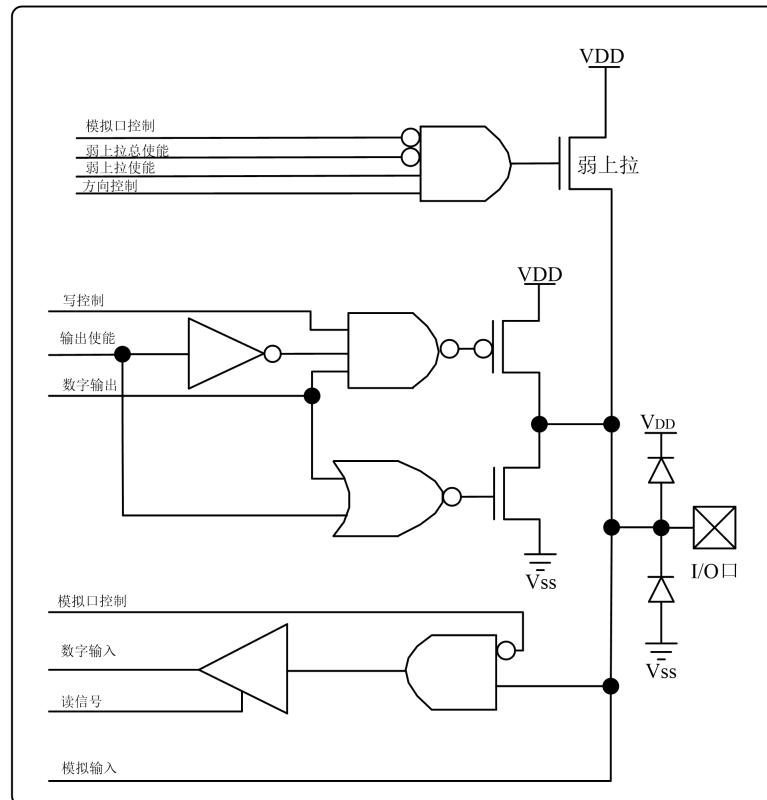

读 P0/P1/P2 口时实际为读端口电平，即读 Px ( $x=0/1/2$ )，其原理框图如图 2.1 所示：

图 2.1 I/O 口读写原理图

注：

- 1、I/O 默认为数字口，当外设需要作为模拟口时将自动切换为模拟口（AD 除外）；

- 2、I/O 端口作为 AD 通道时，需使能对应的 ANSx 位；

- 3、IO 端口作为输出时，可对 PxLR( $x=0/1/2$ )进行赋值(寄存器操作或位操作)，以避免读-修改-写指令造成的其它口误操作。

### 2.2 I/O 端口数字输入电平类型

KF8A100ENG 系列单片机的 I/O 端口数字输入电平类型如下：

| I/O 端口 | 数字输入电平类型 |

|--------|----------|

| P0     | SMIT     |

| P1     | SMIT     |

| P2     | SMIT     |

## 2.3 P0 口

如引脚示意图所示, P0 口共有 6 个引脚。在线编程时 P0 口的 SPCLK、SPDAT 作为编程脚使用。P0.3 只能作为输入口且没有上拉功能, 其它端口均可作为普通 I/O 口且带有上拉功能, P0 口所有引脚都有电平变化中断功能。各引脚功能表 2-1 所示。

表 2-1 P0 口各引脚功能介绍

|    |     |         |                             |

|----|-----|---------|-----------------------------|

| 2  | I/O | P0.5    | 带上拉和电平变化中断功能的双向输入输出端口       |

|    |     | C1+     | 比较器 1 正输入端                  |

|    |     | T1CK    | T1 时钟输入                     |

|    |     | CT0     | 电容触摸通道 0                    |

|    |     | OSCA    | 外部振荡器输入引脚 A                 |

| 3  | I/O | P0.4    | 带上拉和电平变化中断功能的双向输入输出端口       |

|    |     | C1-     | 比较器 1 负输入端                  |

|    |     | T1G     | T1 门控信号输入                   |

|    |     | OSCB    | 外部振荡器输入引脚 B                 |

|    |     | VREOUT  | 内部参考电压输出端                   |

|    |     | AN13    | ADC 输入通道 13                 |

|    |     | CAP     | 触摸按键参考电容输入脚, 接入范围为 0pF~10pF |

|    |     | CLKOUT  | 系统时钟输出                      |

| 4  | I   | P0.3    | 带电平变化中断功能的输入端口              |

|    |     | RST     | 主复位信号输入                     |

| 17 | I/O | P0.2    | 带上拉和电平变化中断功能的双向输入输出端口       |

|    |     | C1OUT   | 比较器 1 输出                    |

|    |     | AN12    | ADC 输入通道 12                 |

|    |     | ADVRIN  | AD 外部参考电压输入端                |

|    |     | T0CK    | T0 时钟输入                     |

|    |     | INT0    | 外部中断 0 输入端                  |

|    |     | PWM1    | PWM1 输出端                    |

|    |     | CT13    | 电容触摸通道 13                   |

| 18 | I/O | P0.1    | 带上拉和电平变化中断功能的双向输入输出端口       |

|    |     | SCL     | I2C 时钟脚                     |

|    |     | PWM2(1) | PWM2 输出端                    |

|    |     | SPCLK   | 编程时钟输入                      |

| 19 | I/O | P0.0    | 带上拉和电平变化中断功能的双向输入输出端口       |

|    |     | SDA     | I2C 数据输入/输出脚                |

|    |     | PWM1(1) | PWM1 输出端                    |

|    |     | SPDAT   | 编程数据输入/输出                   |

### 2.3.1 P0 口相关的寄存器

表 2-2 与 P0 端口相关的寄存器

| 地址  | 名称   | 位 7 | 位 6 | 位 5   | 位 4   | 位 3   | 位 2   | 位 1   | 位 0   |

|-----|------|-----|-----|-------|-------|-------|-------|-------|-------|

| 05H | P0   | -   | -   | P05   | P04   | P03   | P02   | P01   | P00   |

| 45H | POLR | -   | -   | POLR5 | POLR4 | -     | POLR2 | POLR1 | POLR0 |

| 25H | TR0  | -   | -   | TR05  | TR04  | TR03  | TR02  | TR01  | TR00  |

| 36H | IOCL | -   | -   | IOCL5 | IOCL4 | IOCL3 | IOCL2 | IOCL1 | IOCL0 |

| 35H | PUR0 | -   | -   | PUR05 | PUR04 | -     | PUR02 | PUR01 | PUR00 |

#### 2.3.1.1 P0 口状态寄存器 (P0)

寄存器 P0 各位对应 P0 口相应引脚当前的状态，如寄存器 2.1 所示：

寄存器2.1: P0: P0口状态寄存器(地址: 05H)

| bit7             |   |   |     |     |     |     |     | bit0 |     |

|------------------|---|---|-----|-----|-----|-----|-----|------|-----|

| 复位值<br>--XX XXXX | - | - | P05 | P04 | P03 | P02 | P01 | P00  |     |

|                  | U | U | R/W | R/W | R/W | R/W | R/W | R/W  | R/W |

zP0<5:0>: 读 P0 口各引脚电平

1 = 对应引脚为逻辑高电平

0 = 对应引脚为逻辑低电平

图注: R=可读 W=可写 -=未用 U=未实现位

注：读 P0 寄存器实际读 P0 引脚的电平状态。

#### 2.3.1.2 P0 口输出锁存寄存器 (POLR)

寄存器 POLR 是 P0 口输出锁存寄存器。在 P0 口作为输出时，通过写 POLR 寄存器来设置输出 P0 口的状态。

寄存器2.2: POLR: P0口输出锁存寄存器(地址: 45H)

| bit7             |     |     |       |       |     |       |       | bit0  |     |

|------------------|-----|-----|-------|-------|-----|-------|-------|-------|-----|

| 复位值<br>XXXX XXXX | -   | -   | POLR5 | POLR4 | -   | POLR2 | POLR1 | POLR0 |     |

|                  | R/W | R/W | R/W   | R/W   | R/W | R/W   | R/W   | R/W   | R/W |

POLR<5:4>: 写 P0 口输出状态

POLR<2:0>: 写 P0 口输出状态

1 = 对应引脚输出高电平

0 = 对应引脚输出低电平

注：P0.3 不能作输出用。

图注: R=可读 W=可写 -=未用 U=未实现位

#### 2.3.1.3 P0 口方向控制寄存器(TR0)

如寄存器 2.3 所示，TR0 为 P0 口方向控制寄存器，当 TR0 某位置 1 时，将该引脚设置为输入，此时引脚为三态(悬空)，TR0 某位清零，对应引脚设置为输出。

**寄存器2.3:** TR0: P0口方向控制寄存器(地址: 25H)

| 复位值<br>1111 1111 | -   | -   | TR05 | TR04 | TR03 | TR02 | TR01 | TR00 | bit0 |

|------------------|-----|-----|------|------|------|------|------|------|------|

|                  | R/W | R/W | R/W  | R/W  | R    | R/W  | R/W  | R/W  |      |

TR0<5:4>: P0 口各引脚方向控制位

TR0<2:0>: P0 口各引脚方向控制位

1 = 对应的引脚设置为输入

0 = 对应的引脚设置为输出

TR03: P0.3 引脚控制位, 始终为 1

图注: R=可读 W=可写 - =未用 U=未实现位

### 2.3.1.4 P0 上拉功能控制寄存器(PUR0)

KF8A100ENG 中除了 P0.3 口没有内部上拉功能外, 其它引脚均带有上拉功能, 可通过上拉功能控制寄存器和 OPTR 寄存器中的 PUPH 来控制上拉功能是否打开。

如果要将某引脚的上拉功能打开, 需要先将 PUPH (上拉功能总使能位)位清零, 允许 IO 端口上拉功能打开, 然后再将要打开上拉功能的引脚, 所对应的上拉功能控制位置 1 即可。寄存器 2.4 为上拉功能控制寄存器。

注: 只有将引脚设置为数字输入口时才可开启上拉电阻功能, 如果将某引脚设置为输出或者设置为模拟输入口时将会自动禁止该引脚的上拉电阻。

**寄存器2.4:** PUR0: P0口弱上拉控制寄存器(地址: 35H)

| 复位值<br>1111 -111 | -   | -   | PUR05 | PUR04 | - | PUR02 | PUR01 | PUR00 | bit0 |

|------------------|-----|-----|-------|-------|---|-------|-------|-------|------|

|                  | R/W | R/W | R/W   | R/W   | U | R/W   | R/W   | R/W   |      |

PUR0<5:4>: P0 上拉功能使能位

PUR0<2:0>: P0 上拉功能使能位

1 = 使能对应的端口上拉功能

0 = 禁止对应的端口上拉功能

图注: R=可读 W=可写 - =未用 U=未实现位

### 2.3.1.5 电平变化中断控制寄存器(IOCL)

P0 口每个引脚都具有电平变化中断功能, 当引脚的当前电平与上次读 P0 寄存器时的电平不匹配时将产生电平变化中断。如寄存器 2.5 所示, IOCL 为电平变化中断控制寄存器, 将 IOCL 某位置 1 将开启对应引脚的电平变化中断功能, 如果该引脚电平发生变化, 不管电平变化中断是否使能, 电平变化中断标志位(P0IF)都会置 1, 如果全局中断使能位(AIE)和电平变化中断使能位(P0IE)都已置 1, 则会响应中断进入中断服务子程序。P0 口所有引脚的电平变化中断共用一个标志位 P0IF。

注: 1. 只有将引脚设置为数字输入口时才可开启电平变化中断功能, 如果将某引脚设置为输出或者设置为模拟输入口时将会自动禁止该引脚的电平变化中断功能。

2. P0口各引脚的电平变化中断共用一个中断使能位和中断响应标志位。

寄存器2.5: IOCL: 电平变化中断控制寄存器(地址:36H)

| 复位值<br>0000 0000 | bit7 |     |       |       |       |       |       |       | bit0 |

|------------------|------|-----|-------|-------|-------|-------|-------|-------|------|

|                  | -    | -   | IOCL5 | IOCL4 | IOCL3 | IOCL2 | IOCL1 | IOCL0 |      |

|                  | R/W  | R/W | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |      |

IOCL<5:0>: P0 端口引脚电平变化中断使能控制位

1 = 使能对应引脚的电平变化中断

0 = 禁止对应引脚的电平变化中断

图注: R=可读 W=可写 -=未用 U=未实现位

注: P0 口电平变化中断是在引脚的当前电平与上次读 P0 寄存器时的电平不匹配时产生的, 所以每次中断标志位(P0IF)置 1 后都要更新 P0 寄存器的值。

#### 电平变化中断参考:

```

JNB      INTCTL,P0IF ;检测是否为P0电平变化中断

JMP      POINT

JMP      INT_RET       ;退出中断

POINT

MOV  P0 ;注意在处理电平变化中断前, 这里一定要更新锁存器锁存的值, 为了

;下一次电平变化中断处理,

...

;接下来为P0电平变化中断的处理

```

### 2.3.2 P0 口各引脚内部原理功能框图

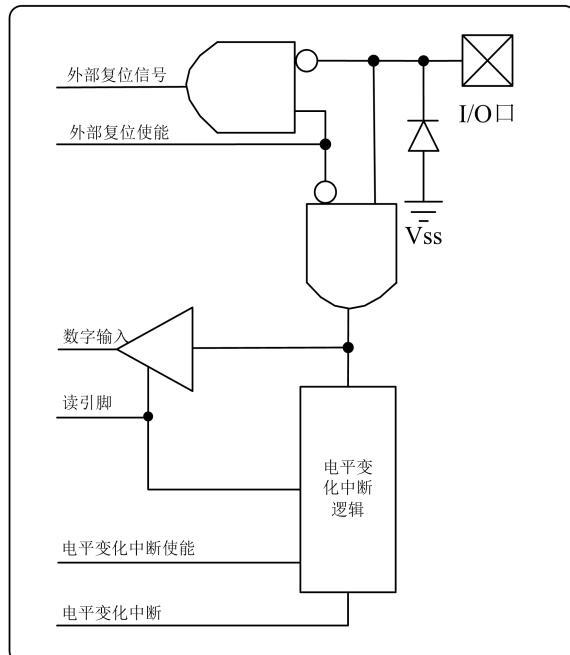

如图 2.2、2.3 所示，为 P0 口引脚原理功能框图。

图 2.2 引脚 P0.3 原理功能框图

图 2.3 P0.0~P0.2、P0.4~P0.5 口引脚原理框图

## 2.4 P1 口

如引脚示意图所示，P1 口具有 8 个引脚。所有管脚均可作为普通 I/O 口，部分引脚可作为 AD 输入通道、触摸输入通道等。引脚功能如表 2-3 所示。

表 2-3 P1 口各引脚功能

|    |     |         |                |

|----|-----|---------|----------------|

| 9  | I/O | P1.7    | 带上拉功能的双向输入输出端口 |

|    |     | CT5     | 电容触摸通道 5       |

|    |     | AN7     | ADC 输入通道 7     |

| 10 | I/O | P1.6    | 带上拉功能的双向输入输出端口 |

|    |     | CT6     | 电容触摸通道 6       |

|    |     | AN6     | ADC 输入通道 6     |

| 11 | I/O | P1.5    | 带上拉功能的双向输入输出端口 |

|    |     | CT7     | 电容触摸通道 7       |

|    |     | AN5     | ADC 输入通道 5     |

| 12 | I/O | P1.4    | 带上拉功能的双向输入输出端口 |

|    |     | OPIN3+  | 运算放大器正输入端 3    |

|    |     | CT8     | 电容触摸通道 8       |

|    |     | AN4     | ADC 输入通道 4     |

| 13 | I/O | P1.3    | 带上拉功能的双向输入输出端口 |

|    |     | OPIN2+  | 运算放大器正输入端 2    |

|    |     | AN3     | ADC 输入通道 3     |

|    |     | CT9     | 电容触摸通道 9       |

| 14 | I/O | P1.2    | 带上拉功能的双向输入输出端口 |

|    |     | OPIN1+  | 运算放大器正输入端 1    |

|    |     | AN2     | ADC 输入通道 2     |

|    |     | INT1    | 外部中断 1 输入      |

|    |     | CT10    | 电容触摸通道 10      |

| 15 | I/O | P1.1    | 带上拉功能的双向输入输出端口 |

|    |     | OPIN-   | 运算放大器负输入端      |

|    |     | AN1     | ADC 输入通道 1     |

|    |     | SDA (1) | I2C 数据输入/输出    |

|    |     | CT11    | 电容触摸通道 11      |

| 16 | I/O | P1.0    | 带上拉功能的双向输入输出端口 |

|    |     | OPOUT   | 运算放大器输出        |

|    |     | AN0     | ADC 输入通道 0     |

|    |     | SCL (1) | I2C 时钟脚        |

|    |     | PWM2    | PWM2 输出端       |

|    |     | CT12    | 电容触摸通道 12      |

### 2.4.1 P1 口相关的寄存器

表 2-4 与 P1 口相关的寄存器

| 地址  | 名称   | 位 7   | 位 6   | 位 5   | 位 4   | 位 3   | 位 2   | 位 1   | 位 0   |

|-----|------|-------|-------|-------|-------|-------|-------|-------|-------|

| 07H | P1   | P17   | P16   | P15   | P14   | P13   | P12   | P11   | P10   |

| 47H | P1LR | P1LR7 | P1LR6 | P1LR5 | P1LR4 | P1LR3 | P1LR2 | P1LR1 | P1LR0 |

| 27H | TR1  | TR17  | TR16  | TR15  | TR14  | TR13  | TR12  | TR11  | TR10  |

| 60H | PUR1 | PUR17 | PUR16 | PUR15 | PUR14 | PUR13 | PUR12 | PUR11 | PUR10 |

#### 2.4.1.1 P1 口状态寄存器(P1)

寄存器 P1 对应端口 P1 引脚作为普通 I/O 口时的状态。如寄存器 2.6 所示

寄存器2.6: P1: P1口状态寄存器(地址: 07H)

| 复位值       | P17 | P16 | P15 | P14 | P13 | P12 | P11 | P10 |

|-----------|-----|-----|-----|-----|-----|-----|-----|-----|

| XXXX XXXX | R/W |

P1<7:0>: 读 P1 口各引脚电平

- 1 = 对应引脚为逻辑高电平

- 0 = 对应引脚为逻辑低电平

图注: R=可读 W=可写 -=未用 U=未实现位

注: 读 P1 寄存器实际读 P1 引脚的电平状态。

#### 2.4.1.2 P1 口输出锁存寄存器 (P1LR)

寄存器 P1LR 是 P1 口输出锁存寄存器。在 P1 口作为输出时，通过写 P1LR 寄存器来设置输出 P1 口的状态。

寄存器2.7: P1LR: P1口输出锁存寄存器(地址: 47H)

| 复位值       | P1LR7 | P1LR6 | P1LR5 | P1LR4 | P1LR3 | P1LR2 | P1LR1 | P1LR0 |

|-----------|-------|-------|-------|-------|-------|-------|-------|-------|

| XXXX XXXX | R/W   |

P1LR<7:0>: 写 P1 口输出状态

- 1 = 对应引脚输出高电平

- 0 = 对应引脚输出低电平

图注: R=可读 W=可写 -=未用 U=未实现位

#### 2.4.1.3 P1 口方向控制寄存器(TR1)

如寄存器 2.8 所示，通过将寄存器 TR1 中的某位置 1，将对应管脚设置为输入口。清零设置为输出口，系统复位时，P1 口各引脚默认为输入口。

**寄存器2.8:** TR1: P1口方向控制寄存器(地址: 27H)

|                  | bit7  |      |      |      |      |      |      |      | bit0 |

|------------------|-------|------|------|------|------|------|------|------|------|

| 复位值<br>1111 1111 | PTR17 | TR16 | TR15 | TR14 | TR13 | TR12 | TR11 | TR10 |      |

|                  | R/W   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |      |

TR1<7:0>: P1 口引脚方向控制位

1 = P1 口对应引脚被配置为输入端口

0 = P1 口对应引脚被配置为输出端口

图注: R=可读 W=可写 -=未用 U=未实现位

#### 2.4.1.4 P1 口上拉功能控制寄存器(PUR1)

KF8A100ENG 中 P1 引脚均带有上拉功能, 可通过上拉功能控制寄存器和 OPTR 寄存器中的 PUPH 来控制上拉功能是否打开。

如果要将某引脚的上拉功能打开, 需要先将 PUPH(上拉功能总使能位)位清零, 允许 IO 端口上拉功能打开, 然后再将要打开上拉功能的引脚, 所对应的上拉功能控制位置 1 即可。寄存器 2.9 为上拉功能控制寄存器。

注: 只有将引脚设置为数字输入口时才可开启上拉电阻功能, 如果将某引脚设置为输出或者设置为模拟输入口时将会自动禁止该引脚的上拉电阻。

**寄存器2.9:** PUR1: P1口弱上拉控制寄存器(地址: 60H)

|                  | bit7  |       |       |       |       |       |       |       | bit0 |

|------------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| 复位值<br>1111 1111 | PUR17 | PUR16 | PUR15 | PUR14 | PUR13 | PUR12 | PUR11 | PUR10 |      |

|                  | R/W   |      |

PUR1<7:0>: P1 上拉功能使能位

1 = 使能对应的端口上拉功能

0 = 禁止对应的端口上拉功能

图注: R=可读 W=可写 -=未用 U=未实现位

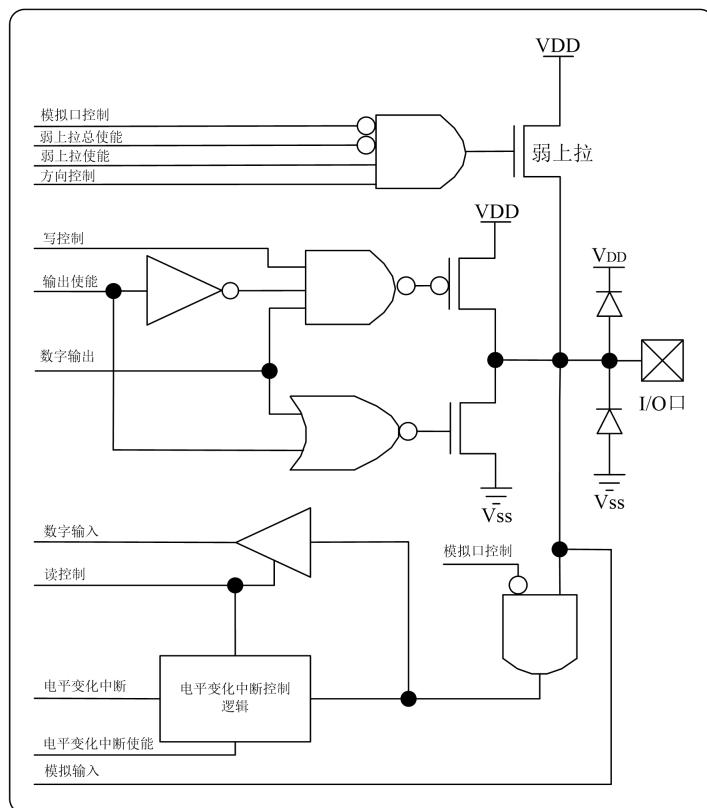

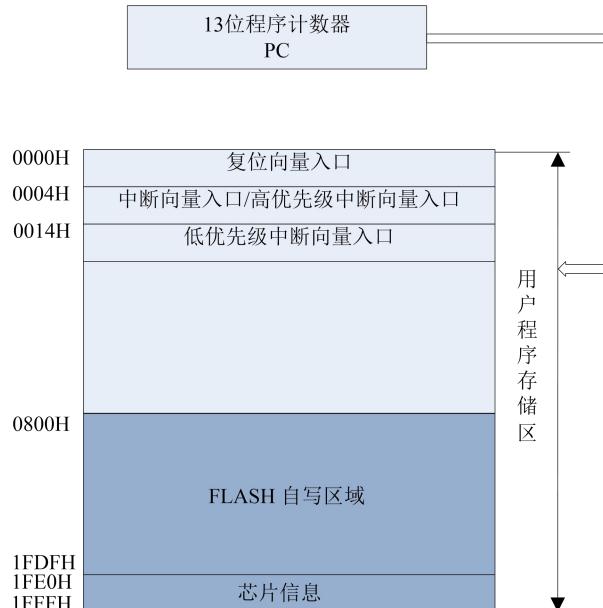

### 2.4.2 P1 口原理功能框图

P1 口引脚原理功能如图 2.4 所示：

图 2.4 P1 口引脚原理功能框图

## 2.5 P2 口

如引脚示意图所示，P2 口共有 4 个引脚。所有管脚均可作为普通 I/O 口、AD 输入通道和触摸输入口。

表 2-5 P2 口各引脚功能

|   |     |      |                |

|---|-----|------|----------------|

| 5 | I/O | P2.0 | 带上拉功能的双向输入输出端口 |

|   |     | AN11 | ADC 输入通道 11    |

|   |     | CT1  | 电容触摸通道 1       |

| 6 | I/O | P2.1 | 带上拉功能的双向输入输出端口 |

|   |     | AN10 | ADC 输入通道 10    |

|   |     | CT2  | 电容触摸通道 2       |

| 7 | I/O | P2.2 | 带上拉功能的双向输入输出端口 |

|   |     | INT2 | 外部中断 2 输入端     |

|   |     | AN9  | ADC 输入通道 9     |

| 8 | I/O | CT3  | 电容触摸通道 3       |

|   |     | P2.3 | 带上拉功能的双向输入输出端口 |

|   |     | AN8  | ADC 输入通道 8     |

|   |     | CT4  | 电容触摸通道 4       |

### 2.5.1 P2 口相关的寄存器

表 2-6 与 P2 口相关的寄存器

| 地址  | 名称   | 位 7 | 位 6 | 位 5 | 位 4 | 位 3   | 位 2   | 位 1   | 位 0   |

|-----|------|-----|-----|-----|-----|-------|-------|-------|-------|

| 06H | P2   | -   | -   | -   | -   | P23   | P22   | P21   | P20   |

| 46H | P2LR | -   | -   | -   | -   | P2LR3 | P2LR2 | P2LR1 | P2LR0 |

| 26H | TR2  | -   | -   | -   | -   | TR23  | TR22  | TR21  | TR20  |

| 61H | PUR2 | -   | -   | -   | -   | PUR23 | PUR22 | PUR21 | PUR20 |

#### 2.5.1.1 P2 口状态寄存器(P2)

寄存器 P2 各位对应端口 P2 口各引脚作为普通 I/O 口时的状态。如寄存器 2.10 所示

寄存器2.10:P2: P2口状态寄存器(地址: 06H)

| 复位值<br>---- XXXX | bit7 |   |   |   | bit0 |     |     |     |

|------------------|------|---|---|---|------|-----|-----|-----|

|                  | -    | - | - | - | P23  | P22 | P21 | P20 |

|                  | U    | U | U | U | R/W  | R/W | R/W | R/W |

P2<3:0>: 读 P2 口各引脚电平

1 = 对应引脚为逻辑高电平

0 = 对应引脚为逻辑低电平

图注: R=可读 W=可写 -=未用 U=未实现位

注: 读 P2 寄存器实际读 P2 引脚的电平状态。

### 2.5.1.2 P2 口输出锁存寄存器 (P2LR)

寄存器 P2LR 是 P2 口输出锁存寄存器。在 P2 口作为输出时，通过写 P2LR 寄存器来设置输出 P2 口的状态。

寄存器2.11: P2LR: P2口输出锁存寄存器(地址: 46H)

| 复位值<br>xxxx xxxx | bit7<br>- | bit6<br>- | bit5<br>- | bit4<br>- | bit3<br>P2LR3 | bit2<br>P2LR2 | bit1<br>P2LR1 | bit0<br>P2LR0 |

|------------------|-----------|-----------|-----------|-----------|---------------|---------------|---------------|---------------|

|                  | R/W       | R/W       | R/W       | R/W       | R/W           | R/W           | R/W           | R/W           |

P2LR<3:0>: 写 P2 口输出状态

- 1 = 对应引脚输出高电平

- 0 = 对应引脚输出低电平

图注: R=可读 W=可写 -=未用 U=未实现位

### 2.5.1.3 P2 口方向控制寄存器(TR2)

如寄存器 2.12 所示，通过将寄存器 TR2 中的某位置 1，将对应管脚设置为输入口。清零设置为输出口。

寄存器2.12: TR2: P2口方向控制寄存器(地址: 26H)

| 复位值<br>1111 1111 | bit7<br>- | bit6<br>- | bit5<br>- | bit4<br>- | bit3<br>TR23 | bit2<br>TR22 | bit1<br>TR21 | bit0<br>TR20 |

|------------------|-----------|-----------|-----------|-----------|--------------|--------------|--------------|--------------|

|                  | R/W       | R/W       | R/W       | R/W       | R/W          | R/W          | R/W          | R/W          |

TR2<3:0>: P2 口各引脚方向控制位

- 1 = P2 口对应引脚被配置为输入端口

- 0 = P2 口对应引脚被配置为输出端口

图注: R=可读 W=可写 -=未用 U=未实现位

### 2.5.1.4 P2 口上拉功能控制寄存器(PUR2)

KF8A100ENG 中 P2 引脚均带有上拉功能，可通过上拉功能控制寄存器和 OPTR 寄存器中的 PUPH 来控制上拉功能是否打开。

如果要将某引脚的上拉功能打开，需要先将 PUPH(上拉功能总使能位)位清零，允许 IO 端口上拉功能打开，然后再将要打开上拉功能的引脚，所对应的上拉功能控制位置 1 即可。寄存器 2.13 为上拉功能控制寄存器。

注：只有将引脚设置为数字输入口时才可开启上拉电阻功能，如果将某引脚设置为输出或者设置为模拟输入口时将会自动禁止该引脚的上拉电阻。

寄存器2.13: PUR2: P2口弱上拉控制寄存器(地址:61H)

| 复位值<br>1111 1111 | bit7<br>- | bit6<br>- | bit5<br>- | bit4<br>- | bit3<br>PUR23 | bit2<br>PUR22 | bit1<br>PUR21 | bit0<br>PUR20 |

|------------------|-----------|-----------|-----------|-----------|---------------|---------------|---------------|---------------|

|                  | R/W       | R/W       | R/W       | R/W       | R/W           | R/W           | R/W           | R/W           |

PUR2<3:0>: P2 上拉功能使能位

- 1 = 使能对应的端口上拉功能

- 0 = 禁止对应的端口上拉功能

图注: R=可读 W=可写 - =未用 U=未实现位

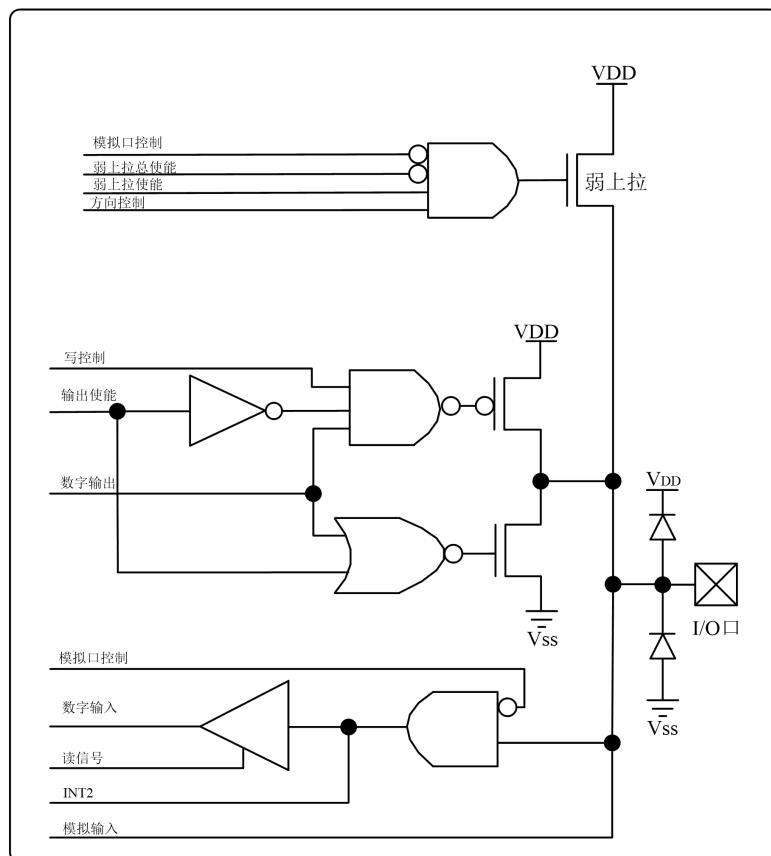

### 2.5.2 P2 口原理功能框图

如引脚示意图所示, P2 口共有 4 个引脚, P2 口引脚原理功能如图 2.5 所示:

图 2.5 P2 口引脚原理功能框图

### 3 存储器

KF8A100ENG 中存储器主要由程序存储器(ROM)和数据存储器(RAM)组成，程序存储器和数据存储器地址空间相互独立。

KF8A100ENG 单片机的数据存储器由特殊功能寄存器和通用寄存器组成，特殊功能寄存器空间均为  $256 \times 8$  位，KF8A100ENG 通用数据寄存器空间均为  $(1024+16) \times 8$  位。另外 KF8A100ENG 中还有一些其它存储器，包括：寄存器组 R0~R7、16 级硬件堆栈、ID 地址单元等。

图 3.1 KF8A100ENG 存储器组织图

#### 3.1 程序存储器(ROM)区

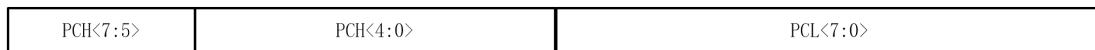

KF8A100ENG 有一个 13 位的程序计数器，最大可寻址  $8K \times 16$  位的程序存储空间，KF8A100ENG 程序存储空间地址为  $0000H \sim 1FFFH$ ，复位向量入口地址均为  $0000H$ ，中断向量有两级入口地址，高为  $0004H$ ，低为  $0014H$ 。

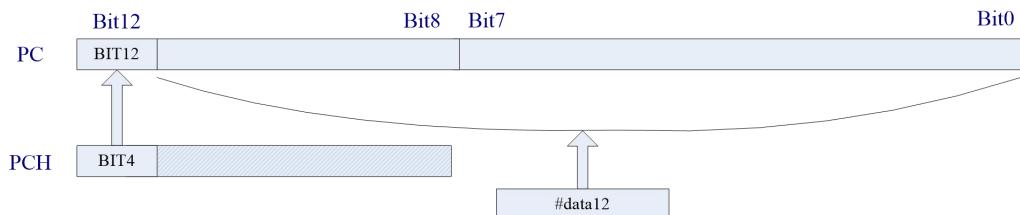

如图 3.2 所示，程序计数器(PC)的低 8 位( $PC<7:0>$ )来自特殊功能寄存器 PCL，高 5 位( $PC<12:8>$ )来自 PCH 寄存器。在任何复位发生后 PC 值将被清零。在有任何未屏蔽中断发生后 PC 值将指向  $0004H$  或  $0014H$  地址。图 3.3 为程序存储器区的地址映射图。

在用户的程序中，每当执行一条汇编指令 PC 值会自动加 1，指向下一条要执行的指令。当有子程序调用或响应中断时，CPU 会将 PC+1 后的值压入堆栈进行保存，然后将子程序或中断入口地址送到 PC 中，CPU 根据 PC 的值跳转到对应的地址执行命令。

图 3.2 程序计数器 (PC)

图 3.3 KF8A100ENG 程序存储器映射

### 3.1.1 MOVP 指令

当需要改变程序计数器到固定地址（包括跳页）时，可以通过写 PCH 寄存器确定高 5 位地址（写 PCH 寄存器不会改变 PC 的值），当写低 8 位地址数据到 PCL 寄存器时，程序计数器的 13 位地址数据将更新，变为 PCH 寄存器和 PCL 寄存器的数据，如例 3.1 所示。

#### 例3.1 程序计数器从0000H开始执行跳转程序到1F55H

| PC   | 指令            | 备注                                   |

|------|---------------|--------------------------------------|

| 0000 | MOVP #0X1F    | 将 1FH 写入 PCH 寄存器                     |

| 0001 | MOV R0, #0X55 | 将 55H 赋给 R0                          |

| 0002 | MOV PCL, R0   | 将 R0 内数据写入 PCL，PC 内容变为 PCH/PCL 寄存器的值 |

| 1F55 | ...           | ...                                  |

### 3.1.2 JMP、CALL 指令

KF8A100ENG 系列单片机的 JMP、CALL 指令编码如下：

JMP #data12 1100\_kkkk\_kkkk\_kkkk

CALL #data12 1101\_kkkk\_kkkk\_kkkk

在执行 JMP 或者 CALL 指令时，程序计数器（PC）的值将变为 PCH.bit4 以及指令所带立即数（#data12），如图 3.6 所示。

图 3.5 执行 JMP、CALL 指令时 PC 的变化图

执行 JMP 指令时将更新 PC；而执行 CALL 指令在更新 PC 的同时，将 CALL 指令的下一条地址入栈，栈地址加 1；在执行 RETURN 指令（IRET、RRET、CRET）时，将之前入栈的地址数据出栈并更新到 PC，栈地址减 1，PCH 寄存器不受出栈入栈的影响。

## 3.2 数据存储器(RAM)区

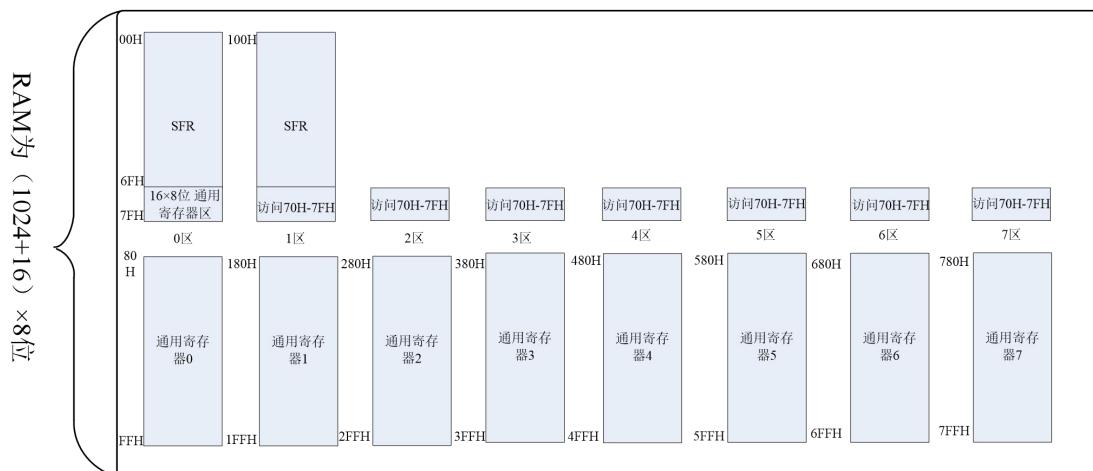

如图 3.6 所示，KF8A100ENG 中的数据存储器均由 10 个区组成。每个区的空间都是 128 字节，其中 2 个区用作特殊功能寄存器区(SFR)使用；另外的存储器区为通用寄存器区，由用户支配。SFR 地址空间为 00H~6FH、100H~17FH；而 70H~7FH 有 16 个字节为通用寄存器共用区，即当用户访问其他 BANK 区 70H~7FH 的存储单元时，均是对 BANK 0 区的 70H~7FH 操作。

图 3.6 KF8A100ENG 数据存储器地址映射图

### 3.2.1 通用寄存器区

如图 3.6 所示，通用寄存器的空间为 1024 字节，0 区至 7 区通过 BANK 寄存器中的 PR3~PR0 位进行选择，如表 3-1 所示。

**寄存器3.1：BANK: 通用寄存器选区寄存器**

| 复位值       | bit7 | - | - | - | PR3 | PR2 | PR1 | bit0<br>PR0 |

|-----------|------|---|---|---|-----|-----|-----|-------------|

| ---- 0000 | -    | - | - | - | R/W | R/W | R/W | R/W         |

**表 3-1 KF8A100ENG 通用寄存区地址**

| PR<3:0> | 通用寄存器区    | 地址        |

|---------|-----------|-----------|

| 0000    | 通用寄存器 0 区 | 80H~FFH   |

| 0001    | 通用寄存器 1 区 | 180H~1FFH |

| 0010    | 通用寄存器 2 区 | 280H~2FFH |

| 0011    | 通用寄存器 3 区 | 380H~3FFH |

| 0100    | 通用寄存器 4 区 | 480H~4FFH |

| 0101    | 通用寄存器 5 区 | 580H~5FFH |

| 0110    | 通用寄存器 6 区 | 680H~6FFH |

| 0111    | 通用寄存器 7 区 | 780H~7FFH |

图注：R=可读 W=可写 -=未用 U=未实现位

切换通用寄存区的指令如例 3.2 所示：

**例3.2 切换BANK寄存器存储区**

|            |           |

|------------|-----------|

| MOVB #0X01 | ;切换到存储区1区 |

| MOVB #0X02 | ;切换到存储区2区 |

### 3.2.2 特殊功能寄存器(SFR)区

KF8A100ENG 内部的 I/O 口控制、定时/计数器、PWM、运放、中断等各种控制寄存器和状态寄存器都称为特殊功能寄存器。附录 1 列出 SFR 的地址映射及复位初始值等。

**状态字寄存器(PSW):** 如寄存器 3.1 所示, PSW 的低三位是算术运算标志位, 在进行加、减等运算时对它们产生影响(具体请参考汇编指令部分)。 $\overline{\text{TO}}$  和  $\overline{\text{PD}}$  是复位状态位, 当单片机有复位或看门狗超时、执行休眠等指令时, 会对这两位产生影响。

寄存器3.1: PSW: 状态字寄存器(地址: 03H)

|                  | bit7 |   |   |                        |                        |   |    | bit0 |

|------------------|------|---|---|------------------------|------------------------|---|----|------|

| 复位值<br>0001 1xxx | -    | - | - | $\overline{\text{TO}}$ | $\overline{\text{PD}}$ | Z | DC | CY   |

$\overline{\text{TO}}$ : 超时标志位

1 = 在上电复位、CWDT 指令或 IDLE 指令执行之后

0 = WDT 超时被清零

$\overline{\text{PD}}$ : 上电复位标志位

1 = 上电复位或执行 CWDT 指令后

0 = 执行 IDLE 指令后被清零

Z: 零状态标志位

1 = 算术运算或者逻辑运算的运行结果为 0

0 = 算术运算或者逻辑运算的运行结果不为 0

DC: 辅助进/借位标志位

1 = 执行结果的低 4 位向高 4 位有进位(加指令)或没有借位(减指令)

0 = 执行结果的低 4 位向高 4 位没有进位(加指令)或有借位(减指令)

CY: 进位/借位标志位

1 = 执行结果(8 位)向高位有进位时(加指令)或没有借位(减指令)

0 = 执行结果(8 位)向高位无进位时(加指令)或有借位(减指令)

图注: R=可读 W=可写 -=未用 U=未实现位

注: 对于借位的情况, 当指令执行后, 低四位(或高四位)向高位有借位时, DC(或CY)标志为0, 当没有借位时其值为1。关于对标志位是否产生影响的指令请参考“汇编指令集”部分。

### 3.3 FLASH 自写

KF8A100ENG 在程序存储区开辟了一个  $6112 \times 16$  位的自写区域，地址范围从  $800H\sim1FDFH$ 。FLASH 自写区域在正常工作期间是可读写的，它并没有直接映射到寄存器空间，而是通过特殊功能寄存器间接寻址。有 6 个特殊功能寄存器用于访问该区域。

表 3-2 与 FLASH 相关的寄存器

| 地址  | 寄存器      | 位 7 | 位 6 | 位 5 | 位 4 | 位 3 | 位 2 | 位 1 | 位 0        |

|-----|----------|-----|-----|-----|-----|-----|-----|-----|------------|

| 3AH | NVMADDRH | -   | -   | -   |     |     |     |     | 地址指针高 5 位  |

| 3BH | NVMADDRL |     |     |     |     |     |     |     | 地址指针低 8 位  |

| 3CH | NVMCTL0  |     |     |     |     |     |     |     | 控制寄存器 1    |

| 3DH | NVMCTL1  |     |     |     |     |     |     |     | 控制寄存器 2    |

| 39H | NVMDATAL |     |     |     |     |     |     |     | 数据寄存器低 8 位 |

| 38H | NVMDATAH |     |     |     |     |     |     |     | 数据寄存器高 8 位 |

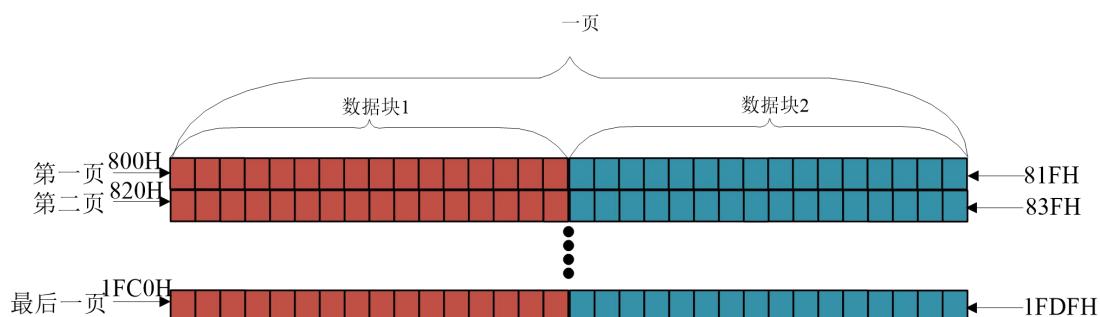

如图 3.9 所示，写 FLASH 时，FLASH 中所有内存单元以连续的 16 个地址为一个数据块，2 个数据块为一页。

图 3.9 Flash 自写区域地址映射图

图 3.10 写操作

如图 3.10 所示，在写 Flash 时，有 16 个 16 位的缓冲寄存器，用来临时存放要写入 Flash 中的数据。

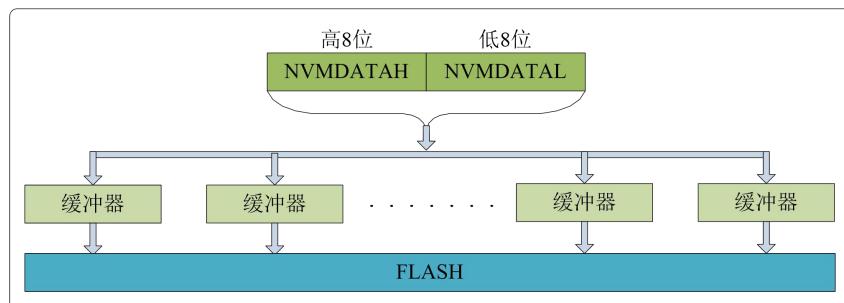

### 3.3.1 寄存器 NVMDATAH/L

CPU 读写 Flash 时，NVMDATAL/H 用来存放要写入或者读出 Flash 的数据，NVMDATAL 存放数据的低 8 位，NVMDATAH 存放数据的高 8 位。

### 3.3.2 寄存器 NVMADDRH/L

如寄存器 3.1 所示，NVMADDRH/L 地址位于特殊功能寄存器区的 3AH/3BH。用来存放要写入 Flash 的 13 位的地址信息，NVMADDRH 存放地址的高 5 位，NVMADDRL 存放地址的低 8 位。

NVMCTL0/NVMCTL1 为写 Flash 控制寄存器，地址位于特殊功能寄存器区的 3CH/3DH。

用户在写 Flash 时，将 NVMDATAH/L 中送入要写入的数据，NVMADRRH/L 中送入要写入的地址，然后通过向 NVMCTL0 和 NVMCTL1 送入固定的写命令，将要写入块的数据存到对应的缓冲寄存器中。

在读 Flash 时，将要读的地址送到 NVMADDRH/L 中，然后向 NVMCTL0 写入固定的读命令，把要读的数据送到 NVMDATAH/L 中。

### 3.3.3 写 Flash

写 Flash 时，只能对 Flash 成块写入数据，不允许跨区操作。不能单独将一个字节(或字)的数据写入某块的一个字节(或字)中，如果实际上写入 Flash 中的数据没有 16 个字或不能被 16 整除(例如要写入一组 15 个字的数据)，需要将块中不需要写入数据的单元写入 0 或者其它值，否则可能会导致写入的数据出错。如果原来的 Flash 保存有数据，现在需要修改原数据中的一个字或者几个字，其它单元的值不变，则需要先将其对应块中其它数据读出来保存，然后再根据实际情况将需要修改的值和之前读出的值写入即可。

在写 Flash 时，必须先对每个页的第一块进行写操作，以擦除本页的数据，如果没有对第一块进行写操作，直接写后面块则本页的所有数据都不会被擦除。即只有对每个页的第一块进行写操作才会擦除本页的数据，对其它块写操作不会擦除本页数据，可能导致写入数据出错。

- 注：1.写Flash时，从Flash自写首800H地址开始处，连续的16个字作为一个数据块，连续的2个数据块作为一个页。

2.写Flash时，不管其存储单元是否有数据，都要先执行一次擦除操作，且擦除操作只有在写每页的第一个数据块时才会执行，将本页所有单元数据擦除。而对每页的其他数据块写操作时不会有擦除操作发生。

3.将各页第一个数据块写完后，CPU将停止6ms执行擦除和写操作，写其他块时，停止3ms执行写操作。

4.配置位的SWRTEN需配置为0，才能对Flash进行写操作。

在写 FLASH 时，将要写入的数据送到 NVMDATAL/H，地址送到 NVMADDRH/L 后，通过执行以下指令完成写操作：

```

MOV R5, BANK           ;保存当前寄存器存储区

CLR BANK               ;切换到Bank0区

MOV DATA_BANK, R5     ;该样例要求DATA_BANK在0区,否则添加切区

MOV R5, INTCTL        ;保存当前的中断状态

MOV DATA_INTCTL, R5   ;该样例要求DATA_INTCTL 在0区,否则添加切区

CLR INTCTL, 7          ;关闭总中断

JNB INTCTL, 7

JMP $-2

MOV R5, OSCCTL        ;保存当前的时钟状态

MOV DATA_OSCCTL, R5   ;该样例要求DATA_OSCCTL在0区,否则添加切区

MOV R5, #0X10          ;切换到250kHz

MOV OSCCTL, R5

;;以下时序不可更改

MOV R5, #0X84

MOV NVMCTL0, R5

MOV R5, #0X69

MOV NVMCTL1, R5

MOV R5, #0X96

MOV NVMCTL1, R5

SET NVMCTL0, 1

NOPZ

NOPZ

NOPZ

NOPZ

NOPZ

NOPZ

NOPZ

NOPZ

NOPZ

MOV R5, #0X80          ;关闭Flash的写操作, 防止意外写

MOV NVMCTL0, R5

MOV R5, DATA_OSCCTL   ;恢复时钟状态

MOV OSCCTL, R5

JNB DATA_INTCTL, 7    ;恢复中断状态

SET INTCTL, 7

MOV R5, DATA_BANK      ;BANK区还原

MOV BANK, R5

```

以上指令中的立即数 0X80, 0X84, 0X69, 0X96 是固定不变的。如果未完全按照上述顺序（先将 0X69 写入 NVMCTL1，再将 0X96 写入 NVMCTL1，最后将 NVMCTL0.1 位置 1）执行指令，将不会启动写操作。

#### 写 FLASH 的步骤为：

1. 将要写入的数据的送到 NVMDATAH/L；

2. 将对应的 FLASH 地址送到 NVMADDRH/L；

3. 执行上面的写命令，此时，CPU 将要写入数据的一个字保存到 FLASH 的数据缓冲器中；

4. 重复执行步骤 1、2、3 十六次，此时 CPU 自动将要写入第一块的数据分别存入对应的 FLASH 的数据缓冲器中；

5. 当上边第 16 次写命令执行完后，CPU 自动发出擦除本页的命令，将本页原来的数据全部擦除，擦除完毕后，将数据缓冲器中的数据送到对应的地址中。在这个过程中 CPU 停止其它工作 6ms 用来执行擦除和写入数据的命令。

6. 重复执行步骤 1、2、3 十六次，将数据写入本页的第二块。当执行完第 16 次写命令后，因本次写的是页的第一块，CPU 不会执行擦除命令，仅将数据缓冲器中的数据写入对应的存储单元，写操作耗时 3ms。

### 3.3.4 读 Flash

在读 FLASH 时，将要读取的地址送到 NVMADDRH/L 后，通过执行以下操作完成读操作：

```

MOV R5,#0X81

MOV NVMCTL0,R5

NOPZ

NOPZ

```

上面指令中的立即数 0X81 是固定不变的。此时该地址的数据高 8 位被送 NVMDATAH，低 8 位送到 NVMDATAL。无论配置位 SWRTEN 为何值都不影响读 FLASH。

读 FLASH 是逐字读取的，不要求一块一块的读。读 FLASH 时通过向 NVMCTL0 写入 0X81 来执行读命令。

**读 FLASH 的步骤如下：**

1. 将要读的数据单元的地址送到 NVMADDRH/L 中；

2. 向 NVMCTL0 写入读命令；

3. 两个指令周期后该单元的数据被送到 NVMDATAH/L。

## 3.4 寄存器组 R<sub>n</sub>

KF8A100ENG 芯片中有一个工作寄存器组 R0~R7，可用做间接寻址的中间寄存器，存放操作数的地址；隐含目的操作数的指令中，默认 R0 作为目的操作数(如: RRCR 0X81)；在读晶振校准值和参考电压校准值时，默认将读到的值送到 R0 中。

## 3.5 ID 地址单元

KF8A100ENG 的程序存储器空间的最后 32 个地址单元被指定为 ID 地址单元，用于存放芯片校准信息，地址分别为 0FE0H~0FFFH 和 1FE0H~1FFFH。

## 4 汇编指令及寻址方式

### 4.1 寻址方式

KF8A100ENG 机提供 5 种寻址方式，分别为：寄存器寻址、直接寻址、立即数寻址、寄存器间接寻址和位寻址。KF8A100ENG 的指令可以没有操作数、一个操作数、两个操作数。

#### 4.1.1 寄存器寻址

采用这种寻址方式的指令中的操作数为寄存器组 R0-R7 的一个。

例：

CLR R0 ; R0←0 将寄存器 R0 清零

只有一个操作数(R0 的值)，寻址方式为寄存器寻址。

ADD R0, R1

两个操作数 (R0 和 R1)，寻址方式为寄存器寻址。

#### 4.1.2 直接寻址

在指令中的操作数为某个寄存器的直接地址，该地址指出其参与运算的数据所在的地址。直接寻址可以是：特殊功能寄存器、通用数据存储器。

例：

MOV R0,0X81 ; R0←(81H) 将 81H 单元的数据送到 R0 中指令中，源操作数寻址方式为直接寻址，目的操作数为寄存器寻址。

INC 0X3B ; 3BH←(3BH)+1 将地址 3BH 里的值加 1。

指令中含有一个操作数，寻址方式为直接寻址。

#### 4.1.3 立即数寻址

在指令中的操作数为立即数。

例：

MOV R0,#0X20 ; R0←0X20 将立即数 0X20 送到寄存器 R0 中

ADD R0,#0X20 ; R0←(R0)+0X20 寄存器 R0 的值与 0X20 相加结果送到 R0

AND R0,#0X20 ; R0←(R0)&0X20 寄存器 R0 的值与 0X20 相与结果送到 R0

以上三条指令中源操作数都是#0X20，为立即数寻址，目的操作数为寄存器寻址。

#### 4.1.4 寄存器间接寻址

这种寻址方式中，寄存器的内容指定操作数的地址，即寄存器中存放的是操作数的地址。间接寻址只有两条指令 LD 和 ST。

例：

LD R0, [R1] ; R0←((R1)) 将 R1 的内容所指地址单元的数据送到 R0

指令中源操作数的寻址方式为寄存器间接寻址，目的操作数为寄存器寻址。

ST [R0], R1 ; (R0)←(R1) 将 R1 的内容送到 R0 的内容所指向的地址单元

指令中目的操作数的寻址方式为寄存器间接寻址，源操作数为寄存器寻址。

#### 4.1.5 位寻址

指令中的操作数是寄存器的某位，这样的寻址方式称为位寻址。

例：

CLR INTCTL,1 ; 将 INTCTL 的第 1 位清零

CLR 0X80,1 ; 将 80H 的第 1 位清零

JNB 0X80,1 ; 如果 80H 的第 1 位为 0 则跳过下一条指令执行后面的程序

### 4.2 汇编指令

KF8A100ENG 系列单片机汇编指令共有 73 条，除子程序调用、子程序返回、中断返回、部分跳转指令为双周期指令外，其余指令均为单周期指令。所有指令都占两个字节。

按照指令的功能可将其分为：数据传送指令、算术运算指令、逻辑运算指令、位操作指令和转移指令和特殊指令。具体指令集请参考附录 2。

## 5 中断

KF8A100ENG 单片机的中断源有:

- INT0/1/2

- T0 溢出中断

- T1/3/4 中断

- P0 口引脚电平变化中断

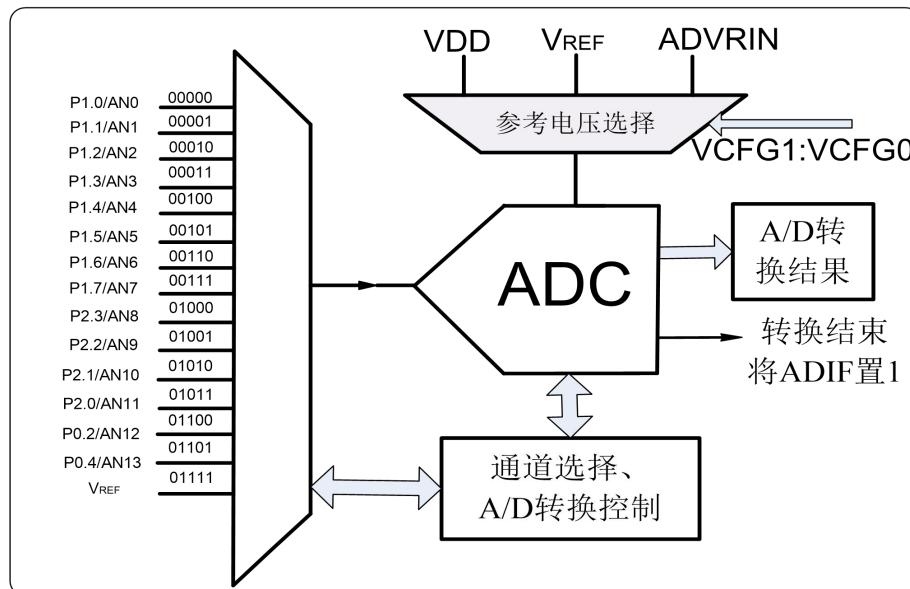

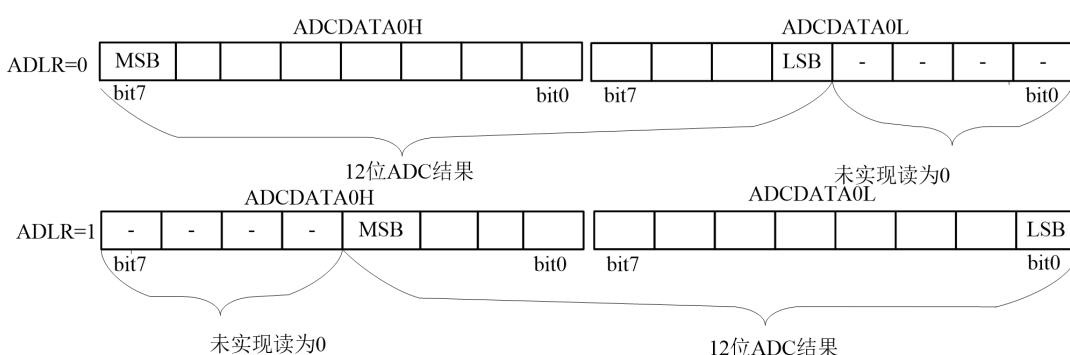

- A/D 中断

- PWM1/2 中断

- I2C 中断

- 电容触摸（CT）中断

- SSCI 模块 I2C 总线冲突（BCL）中断

- 外部时钟故障（OSCFAIL）中断

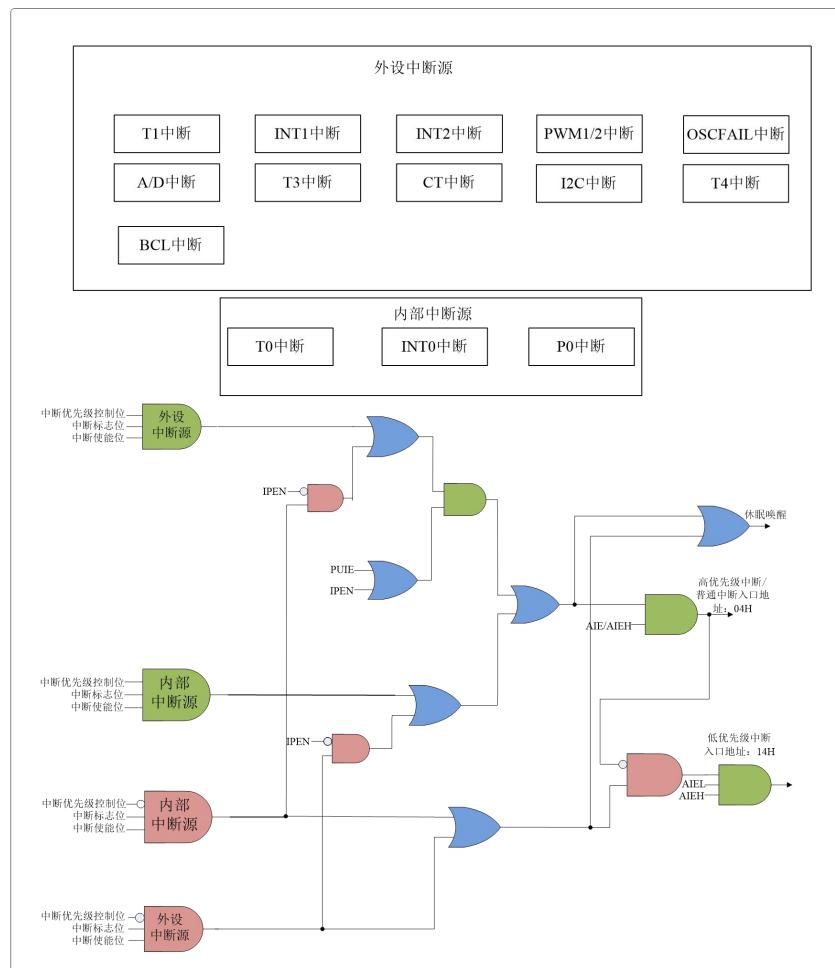

在本单片机中有两个中断优先级，其中高优先级向量位于 0X0004H，低优先级向量位于 0X0014H。在中断服务程序里可通过 PCTL 的 IPEN(PCTL<3>)进行中断优先级设置。在中断服务子程序中通过检测相应的中断标志位来确定具体是哪个中断源触发发生。

KF8A100ENG 中的 INT1/2、T1、T3、T4、ADC、PWM1/2、I2C、BCL、CT 和 OSCFAIL 都属于外设，因此对应的中断称作外设中断，其它中断源产生的中断属于内部中断。中断逻辑如图 5.2 所示。在中断逻辑框图中，每个中断源有 3 个位用于控制其操作。这些位的功能分别是：

- ☞ 标志位表明发生了中断事件；

- ☞ 中断允许位允许程序跳转到中断向量地址处执行；

- ☞ 中断优先级位用于选择高优先级及还是低优先级；

通过将 IPEN 位 (PCTL<3>) 置 1，可使能中断优先级功能。

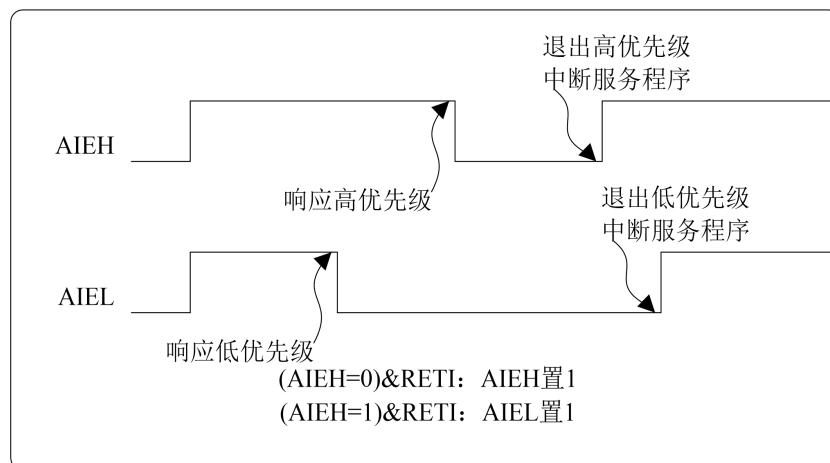

当 IPEN 置 1 时，有两个中断允许位，分别是 AIEH 和 AIEL。将 AIEH (INTCTL<7>) 置 1，可允许所有中断优先级位已置 1 的中断，即高优先级的中断。将 AIEL (INTCTL<6>) 置 1，可允许所有中断优先级位已清零的中断，即低优先级的中断。当中断标志位、中断允许位和中断优先级位都被置 1 时，中断将根据设置的中断优先级立即跳转到地址 0x0004H 或者 0x0014H。进低优先级中断时清零 AIEL，退出中断时置 1 AIEL；进高优先级中断时清零 AIEH，退出中断时置 1 AIEH。（AIEH=0 时禁止所有中断）。高优先级中断事件可以中断正在处理的低优先级中断事件。

其原理框图如图 5.1 下:

图 5.1 中断优先级工作原理图

当 IPEN 位清零时，就会禁止中断优先级，即为普通模式。所有中断都跳转到 0x0004H 开始执行。在普通模式下，没有中断优先级，各个中断源的中断优先级控制寄存器 IP0、IP1 和 IP2 均无效。AIE(INTCTL<7>)为全局中断使能位，PUIE(INTCTL<6>)为外设中断使能位。

图 5.2 中断逻辑

## 5.1 中断相关的寄存器

表 5-1 与中断相关的寄存器

| 地址  | 寄存器       | 位 7      | 位 6       | 位 5       | 位 4    | 位 3  | 位 2    | 位 1        | 位 0        |

|-----|-----------|----------|-----------|-----------|--------|------|--------|------------|------------|

| 0BH | INTCTL    | AIE/AIEH | PUIE/AIEL | TOIE      | INT0IE | POIE | TOIF   | INT0IF     | POIF       |

| 2CH | EIE1      | -        | ADIE      | INT2IE    | INT1IE | -    | PWM2IE | -          | T1IE       |

| 2DH | EIE2      | T3IE     | -         | RCIE      | TXIE   | -    | -      | BCLIE      | SSCIIE     |

| 4AH | EIE3      | T4IE     | -         | OSCFAILIE | -      | -    | -      | -          | -          |

| 0CH | EIF1      | -        | ADIF      | INT2IF    | INT1IF | -    | PWM2IF | -          | T1IF       |

| 0DH | EIF2      | T3IF     | -         | RCIF      | TXIF   | -    | -      | BCLIF      | SSCIIF     |

| 4BH | EIF3      | T4IF     | -         | OSCFAILIF | -      | -    | -      | -          | -          |

| 22H | IP0       | -        | -         | -         | -      | -    | PT0    | PINT0      | PP0        |

| 23H | IP1       | -        | PADC      | PINT2     | PINT1  | -    | PPWM2  | -          | PT1        |

| 24H | IP2       | PT3      | -         | PRC       | PTX    | -    | -      | PBCL       | PSSCI      |

| 29H | IP3       | PT4      | -         | POSCFAIL  | -      | -    | -      | -          | -          |

| 2EH | PCTL      | -        | -         | -         | SLVREN | IPEN | SWDTEN | <u>POR</u> | <u>BOD</u> |

| 67H | INTEDGCTL | INT2SE   | INT1SE    | -         | -      | -    | -      | -          | T1CLKEN    |

### 5.1.1 中断控制寄存器 INTCTL

普通模式下，AIE 为全局中断使能位，当其被清零时，禁止所有中断。PUIE 为外设中断使能位，当其被清零时禁止所有外设中断。具体的中断逻辑如图 5.1 所示。

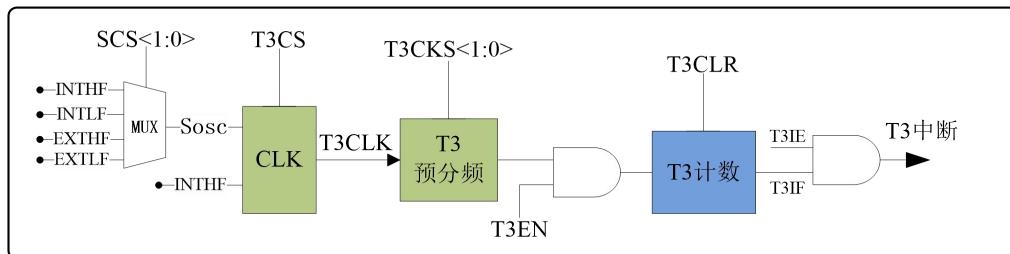

在优先级中断中，AIEH 为全局优先级中断使能位，当其被清零时，禁止所有中断。AIEL 为低优先级中断使能位，当其被清零时禁止所有低优先级中断。具体的中断逻辑如图 5.1 所示。

注：1. 当中断条件满足时，无论相应的中断使能位或者全局中断使能位AIE的状态如何，中断标志位将被硬件置1。

2. 中断条件满足时，中断标志位通过硬件置1，而清零则需要软件完成。

寄存器5.1: INTCTL: 中断控制寄存器(地址: 0BH)

| 复位值<br>0000 0000 | bit7            |                  |             |               |             |             |               |             | bit0<br>R/W |

|------------------|-----------------|------------------|-------------|---------------|-------------|-------------|---------------|-------------|-------------|

|                  | AIE/AIEH<br>R/W | PUIE/AIEL<br>R/W | TOIE<br>R/W | INT0IE<br>R/W | POIE<br>R/W | TOIF<br>R/W | INT0IF<br>R/W | POIF<br>R/W |             |

AIE/AIEH: 全局中断使能位/优先级中断使能位

当 IPEN=0

1=使能所有未屏蔽的中断

0=禁止所有中断

当 IPEN=1

1=允许所有高优先级的中断

0=禁止所有中断

PUIE/AIEL: 外设中断使能位/低优先级中断使能位

当 IPEN=0

1=使能所有未屏蔽的外设中断

0=禁止所有外设中断

当 IPEN=1

1=允许所有低优先级的中断

0=禁止所有低优先级的中断

TOIE: T0 溢出中断使能位

|         |                                                                           |

|---------|---------------------------------------------------------------------------|

|         | 1=使能 T0 中断                                                                |

|         | 0=禁止 T0 中断                                                                |

| INT0IE: | INT0 中断使能位<br>1=使能 INT0 中断<br>0=禁止 INT0 中断                                |

| POIE:   | P0 口电平变化中断使能位<br>1=使能 P0 口电平变化中断<br>0=禁止 P0 口电平变化中断                       |

| T0IF:   | T0 溢出中断标志位<br>1=T0 寄存器溢出<br>0=T0 寄存器未溢出                                   |

| INT0IF: | INT0 中断标志位<br>1=INT0/P0.2 产生外部中断<br>0=INT0/P0.2 未产生外部中断                   |

| POIF:   | P0 口电平变化中断标志位<br>1=引脚 P0.0~P0.5 至少有一个电平状态发生变化<br>0=引脚 P0.0~P0.5 电平状态未发生变化 |

图注: R=可读 W=可写 -=未用 U=未实现位

### 5.1.2 中断使能寄存器 EIE1

寄存器5.2: EIE1: 中断使能寄存器(地址: 2CH)

| 复位值       | bit7 |      |        |        |     |        |     |      | bit0 |

|-----------|------|------|--------|--------|-----|--------|-----|------|------|

|           | -    | ADIE | INT2IE | INT1IE | -   | PWM2IE | -   | T1IE |      |

| 0000 0000 | R/W  | R/W  | R/W    | R/W    | R/W | R/W    | R/W | R/W  |      |

|         |                                                |

|---------|------------------------------------------------|

| ADIE:   | AD 中断使能位<br>1 = 使能 AD 中断<br>0 = 禁止 AD 中断       |

| INT2IE: | INT2 中断使能位<br>1 = 使能 INT2 中断<br>0 = 禁止 INT2 中断 |

| INT1IE: | INT1 中断使能位<br>1 = 使能 INT1 中断<br>0 = 禁止 INT1 中断 |

| PWM2IE: | PWM2 中断使能位<br>1 = 使能 PWM2 中断<br>0 = 禁止 PWM2 中断 |

| T1IE:   | T1 中断使能位<br>1 = 使能 T1 中断<br>0 = 禁止 T1 中断       |

图注: R=可读 W=可写 -=未用 U=未实现位

### 5.1.3 中断使能寄存器 EIE2

寄存器5.3: EIE2: 中断使能寄存器(地址: 2DH)

| 复位值       | bit7 |     |      |      |     |     |       |       | bit0 |

|-----------|------|-----|------|------|-----|-----|-------|-------|------|

|           | T3IE | -   | RCIE | TXIE | -   | -   | BCLIE | SSCIE |      |

| 0000 0000 | R/W  | R/W | R/W  | R/W  | R/W | R/W | R/W   | R/W   |      |

|         |                   |  |

|---------|-------------------|--|

| T3IE:   | T3 中断使能位/触摸中断使能位  |  |

|         | 1 = 允许 T3 中断/触摸中断 |  |

|         | 0 = 禁止 T3 中断/触摸中断 |  |

| RCIE:   | USART 接收中断使能位     |  |

|         | 1 = 允许 USART 接收中断 |  |

|         | 0 = 禁止 USART 接收中断 |  |

| TXIE:   | USART 发送中断使能位     |  |

|         | 1 = 允许 USART 发送中断 |  |

|         | 0 = 禁止 USART 发送中断 |  |

| BCLIE:  | BCL 中断使能位         |  |

|         | 1 = 允许 BCL 中断     |  |

|         | 0 = 禁止 BCL 中断     |  |

| SSCIIE: | I2C 中断使能位         |  |

|         | 1= 允许 I2C 中断      |  |

|         | 0= 禁止 I2C 中断      |  |

图注: R=可读 W=可写 -=未用 U=未实现位

### 5.1.4 中断使能寄存器 EIE3

寄存器5.4: EIE3: 中断使能寄存器(地址: 4AH)

| 复位值<br>000- ---- | bit7 |     |               |   |   |   |   |   | bit0 |

|------------------|------|-----|---------------|---|---|---|---|---|------|

|                  | T4IE | -   | OSCFAIL<br>IE | - | - | - | - | - | -    |

|                  | R/W  | R/W | R/W           | U | U | U | U | U | U    |

T4IE: T4 中断使能位

1 = 允许 T4 中断

0 = 禁止 T4 中断

OSCFAILIE: 外部时钟故障中断使能位

1 = 允许外部时钟故障中断

0 = 禁止外部时钟故障中断

图注: R=可读 W=可写 -=未用 U=未实现位

### 5.1.5 中断标志寄存器 EIF1

寄存器5.5: EIF1: 外设中断标志寄存器(地址0CH)

| 复位值<br>0000 0000 | bit7 |      |        |        |     |        |     |      | bit0 |

|------------------|------|------|--------|--------|-----|--------|-----|------|------|

|                  | -    | ADIF | INT2IF | INT1IF | -   | PWM2IF | -   | T1IF |      |

|                  | R/W  | R/W  | R/W    | R/W    | R/W | R/W    | R/W | R/W  | R/W  |

ADIF: AD 完成中断标志位

1 = AD 转换完成

0 = AD 转换没有完成

INT2F: INT2 中断标志位

1 = INT2/P1.3 产生外部中断

0 = INT2/P1.3 未产生外部中断

INT1IF: INT1 中断标志位

1 = INT1/P1.2 产生外部中断

0 = INT1/P1.2 未产生外部中断

PWM2IF: PWM2 中断标志位

1 = PWM2 使能时, T1H 和 PP2 匹配

0 = PWM2 使能时, T1H 和 PP2 不匹配

T1IF: T1 寄存器溢出标志位

1 = T1 寄存器溢出

0 = T1 寄存器未溢出

图注: R=可读 W=可写 -=未用 U=未实现位

### 5.1.6 中断标志寄存器 EIF2

寄存器5.6: EIF2: 外设中断标志寄存器(地址: 0DH)

| 复位值       |      |   |      |      |     |     |       |      |

|-----------|------|---|------|------|-----|-----|-------|------|

|           | bit7 | - | RCIF | TXIF | -   | -   | BCLIF | bit0 |

| 0000 0000 | T3IF | - | R    | R    | R/W | R/W | R/W   | R/W  |

T3IF: T3 中断标志位/触摸中断标志位

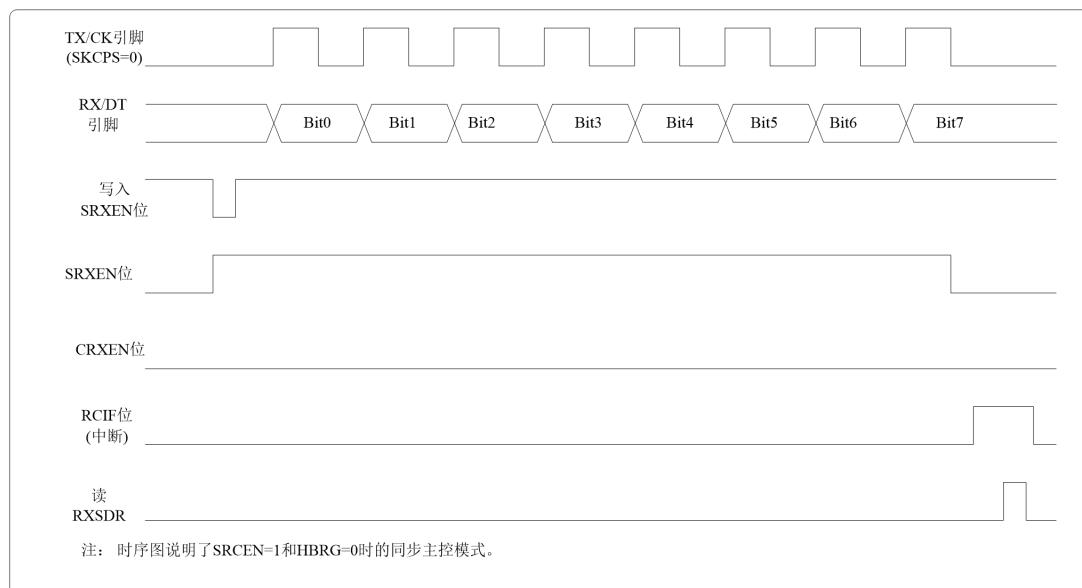

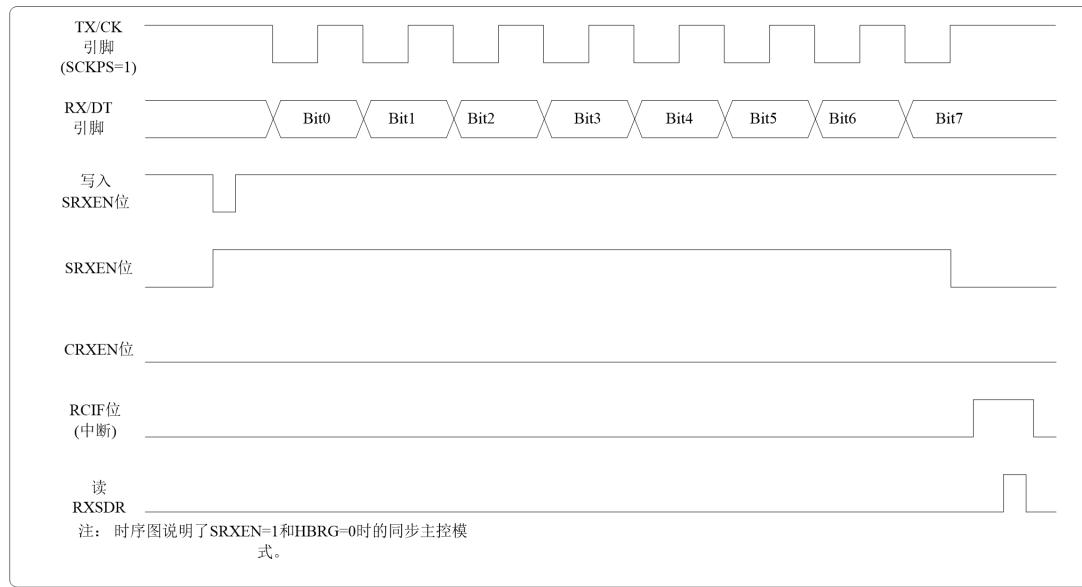

1 = T3 溢出/触摸产生了中断

0 = T3 未溢出/触摸未产生中断

RCIF: USART 接收中断标志位

1 = USART 接收缓冲器满 (通过 RXSDR 清 0)

0 = USART 接收缓冲器空

TXIF: USART 发送中断标志位

1 = USART 发送缓冲器满 (通过 TXSDR 清 0)

0 = USART 发送缓冲器空

BCLIF: BCL 中断标志位

1 = BCL 产生了中断

0 = BCL 未产生中断

SSCIIIF: SSCI 中断标志位

1 = I2C 产生了中断

0 = I2C 未产生中断

图注: R=可读 W=可写 -=未用 U=未实现位

### 5.1.7 中断标志寄存器 EIF3

寄存器5.7: EIF3: 中断标志寄存器(地址: 4BH)

| 复位值       |      |   |               |     |   |   |   |   |

|-----------|------|---|---------------|-----|---|---|---|---|

|           | bit7 | - | OSCFAIL<br>IF | -   | - | - | - | - |

| 000- ---- | T4IF | - | R/W           | R/W | U | U | U | U |

T4IF: T4 中断标志位

1 = T4 溢出后产生了中断

0 = T4 未产生中断

OSCFAILIF: 外部时钟故障中断标志位

1 = 外部时钟发生故障

0 = 外部时钟未发生故障

图注: R=可读 W=可写 -=未用 U=未实现位

### 5.1.8 中断优先级控制寄存器 IP0

当 IPEN=1 时, 中断优先级控制寄存器 IP0 才有效。

**寄存器5.8: IP0: 中断优先级控制寄存器0(地址: 22H)**

| 复位值       | bit7 | - | - | - | - | - | PT0 | PINT0 | PP0 | bit0 |

|-----------|------|---|---|---|---|---|-----|-------|-----|------|

| ---- -000 |      | U | U | U | U | U | R/W | R/W   | R/W |      |

PT0: T0 中断优先级控制位

1 = T0 中断为高优先级

0 = T0 中断为低优先级

PINT0: INT0 中断优先级控制位

1 = INT0 中断为高优先级

0 = INT0 中断为低优先级

PP0: P0 电平变化中断优先级控制位

1 = P0 电平变化中断为高优先级

0 = P0 电平变化中断为低优先级

图注: R=可读 W=可写 -=未用 U=未实现位

### 5.1.9 中断优先级控制寄存器 IP1

当 IPEN=1 时, 中断优先级控制寄存器 IP1 才有效。

**寄存器5.9: IP1: 中断优先级控制寄存器1(地址: 23H)**

| 复位值       | bit7 | -   | PADC | PINT2 | PINT1 | -   | PPWM2 | -   | PT1 | bit0 |

|-----------|------|-----|------|-------|-------|-----|-------|-----|-----|------|

| 0000 0000 |      | R/W | R/W  | R/W   | R/W   | R/W | R/W   | R/W | R/W |      |

PADC: AD 中断高优先级控制位

1 = AD 中断为高优先级

0 = AD 中断为低优先级

PINT2: INT2 中断高优先级控制位

1 = INT2 中断为高优先级

0 = INT2 中断为低优先级

PINT1: INT1 中断高优先级控制位

1 = INT1 中断为高优先级

0 = INT1 中断为低优先级

PPWM2: PWM2 中断高优先级控制位

1 = PWM2 中断为高优先级

0 = PWM2 中断为低优先级

PT1: T1 中断高优先级控制位

1 = T1 中断为高优先级

0 = T1 中断为低优先级

图注: R=可读 W=可写 -=未用 U=未实现位

### 5.1.10 中断优先级控制寄存器 IP2

当 IPEN=1 时, 中断优先级控制寄存器 IP2 才有效。

**寄存器5.10: IP2: 中断优先级控制寄存器2(地址: 24H)**

| 复位值       | bit7 | PT3 | -   | PRC | PTX | -   | -   | PBCL | PSSCI | bit0 |

|-----------|------|-----|-----|-----|-----|-----|-----|------|-------|------|

| 0000 0000 |      | R/W  | R/W   |      |

PT3: T3 中断高优先级控制位/触摸中断高优先级控制位

|        |                          |

|--------|--------------------------|

|        | 1 = T3 中断为高优先级/触摸中断为高优先级 |

|        | 0 = T3 中断为低优先级/触摸中断为低优先级 |

| PRC:   | USART 接收中断优先级控制位         |

|        | 1 = USART 接收中断为高优先级      |

|        | 0 = USART 接收中断为低优先级      |

| PTX:   | USART 发送中断优先级控制位         |

|        | 1 = USART 发送中断为高优先级      |

|        | 0 = USART 发送中断为低优先级      |

| PBCL:  | BCL 中断高优先级控制位            |

|        | 1 = BCL 中断为高优先级          |

|        | 0 = BCL 中断为低优先级          |

| PSSCI: | SSCI 中断高优先级控制位           |

|        | 1 = I2C 中断为高优先级          |

|        | 0 = I2C 中断为低优先级          |

图注: R=可读 W=可写 -=未用 U=未实现位

### 5.1.11 中断优先级控制寄存器 IP3

当 IPEN=1 时，中断优先级控制寄存器 IP3 才有效。

寄存器5.11: IP3: 中断优先级控制寄存器3(地址: 29H)

|                  | bit7 | PT4 | -   | POSCFA<br>IL | - | - | - | - | bit0 |

|------------------|------|-----|-----|--------------|---|---|---|---|------|

| 复位值<br>000- ---- |      | R/W | R/W | R/W          | U | U | U | U | U    |

|      |                |

|------|----------------|

| PT4: | T4 中断高优先级控制位   |

|      | 1 = T4 中断为高优先级 |

|      | 0 = T4 中断为低优先级 |

|           |                     |

|-----------|---------------------|

| POSCFAIL: | OSCFAIL 中断高优先级控制位   |

|           | 1 = OSCFAIL 中断为高优先级 |

|           | 0 = OSCFAIL 中断为低优先级 |

图注: R=可读 W=可写 -=未用 U=未实现位

### 5.1.12 电源控制寄存器 PCTL

寄存器5.12:PCTL: 电源控制寄存器(地址:2EH)

|                  | bit7 | - | - | - | SLVREN | IPEN | SWDTEN | POR | bit0 |

|------------------|------|---|---|---|--------|------|--------|-----|------|

| 复位值<br>---1 000x | -    | U | U | U | R/W    | R/W  | R/W    | R/W | R/W  |

|         |                       |

|---------|-----------------------|

| SLVREN: | 软件欠压检测使能位             |

|         | 1 = 使能欠压检测            |

|         | 0 = 禁止欠压检测            |

| IPEN:   | 中断优先级控制位              |

|         | 1 = 使能中断优先级功能，即为优先级模式 |

|         | 0 = 禁止中断优先级，即为普通模式    |

| SWDTEN: | 软件看门狗定时器使能位           |

|         | 当配置字的 WDTEN=0 时       |

|         | 1 = 软件使能看门狗定时器        |

|         | 0 = 软件禁止看门狗定时器        |

当配置字的 WDTEN=1 时，为无关位

POR: 上电复位状态位

1 = 未发生上电复位

0 = 发生了上电复位

LVR: 欠压复位状态位

1 = 未发生欠压复位

0 = 已发生欠压复位

图注: R=可读 W=可写 -=未用 U=未实现位

### 5.1.13 INT 中断沿选择寄存器 INTEDGCTL

寄存器**5.13:INTEDGCTL:INT中断沿选择寄存器 (67H)**

| 复位值<br>11--00 | bit7<br>INT2SE | bit6<br>INT1SE | - | - | - | - | - | bit0<br>T1CLKEN |

|---------------|----------------|----------------|---|---|---|---|---|-----------------|

|               | R/W            | R/W            | U | U | U | U | U | R/W             |

INT2SE: INT2 触发脉冲边沿选择位

1 = 上升沿触发

0 = 下降沿触发

INT1SE: INT1 触发脉冲边沿选择位

1 = 上升沿触发

0 = 下降沿触发

T1CLKEN: T1 定时模式时钟源选择位

当 T1CS=0 时:

1 = T1 时钟为内部高频振荡器时钟 INTHF

0 = T1 时钟为系统时钟 4 分频 SCLK/4

当 T1CS=1 时, 为计数模式, T1CLKEN 位不起作用, T1 时钟为外部时钟

图注: R=可读 W=可写 -=未用 U=未实现位

### 5.1.14 中断响应

当 IPEN=1 时，为优先级模式，中断被响应后：

1. 返回地址压入堆栈；

2. 中断入口地址载入 PC；

3. 在中断被响应前，AIEH 和 AIEL 位的设置会影响到中断响应的过程：

- 将 AIEH 和 AIEL 均置 1，可进入高优先级或优先级中断。进入的是高或低优先级中断时，AIEH 或 AIEL 由硬件自动清零，执行高或低优先级中断服务程序，执行指令 IRET 退出高或低优先级中断，硬件自动将 AIEH 或 AIEL 置 1；

- 只将 AIEH 置 1，则直接进入高优先级中断，AIEH 由硬件自动清零，继续执行中断服务子程序，执行指令 IRET 退出中断服务子程序并由硬件自动将 AIEH 置 1，重新使能未屏蔽的中断；

4. 跳转到中断发生处继续执行下面的程序。

注：中断的响应有一定的响应时间：

1. 如果已经进入了低优先级中断，再有高优先级中断，此时为中断嵌套；

2. 如果还没有进入低优先级中断，同时有高优先级中断产生，则直接进入高优先级中断，相当于两个中断同时产生。

当 IPEN=0 时，为普通模式，中断被响应后：

1. 返回地址压入堆栈；

2. 中断入口地址载入 PC；

3. AIE 位将被硬件清零以禁止其它中断；

4. 执行该中断服务子程序；

5. 执行指令 IRET 退出中断服务子程序，同时硬件自动将 AIE 置 1，重新使能未屏蔽的中断；

6. 跳转到中断发生处继续执行下面的程序。

- 7.

进入中断服务程序后，首先保存 PSW 和其它寄存器的值，然后通过查询中断标志位确定中断源。在重新使能中断之前，应在软件中将相应的中断标志位清零，以避免出错。

注 1：中断条件满足时，无论相应的中断使能位或AIE位的状态为何，中断标志位都将被置1。

2：当执行一条清除AIE位的指令后，任何在下一周期等待响应的中断都将被忽略。当AIE位重新置1时，被忽略的中断请求将继续等待被响应。

3：当对中断进行响应，进入中断服务子程序的时候硬件会将AIE位清零关闭总中断，当中断程序执行完，中断返回指令跳出中断子程序时，硬件将AIE位置1打开总中断。

## 5.2 INT 中断

INT 中断有三个中断源: INT0、INT1 和 INT2, 都采用边沿触发方式, 如果触发边沿选择位(INTxSE)置 1, 则采用上升沿触发; 如果触发边沿选择位清零, 则采用下降沿触发。

### 5.2.1 INT0 中断

INT0 中断通过寄存器 INTCTL 中的 INT0IE 位置 1 使能 INT0 中断。通过 OPTR 中的 INT0SE 位设置触发边沿, INT0SE 置 1, 将 INT0 设置为上升沿触发, 清零设置为下降沿触发。INTCTL 中的 INT0IF 为 INT0 的中断标志位。如果 IPEN 和 PINT0 位均置 1, 则 INT0 为高优先级中断。

INT0 引脚有触发脉冲时, INT0IF 被自动置 1, 如果 INT0IE 和 AIE 位为 1, 则响应 INT0 中断。

### 5.2.2 INT1 中断

INT1 中断通过寄存器 EIE1 中的 INT1IE 位置 1 使能 INT1 中断。通过 INTEDGCTL 中的 INT1SE 位设置触发边沿, INT1SE 置 1, 将 INT1 设置为上升沿触发, 清零设置为下降沿触发。EIF1 中的 INT1IF 为 INT1 的中断标志位。如果 IPEN 和 PINT1 位均置 1, 则 INT1 为高优先级中断。

INT1 引脚有触发脉冲时, INT1IF 被自动置 1, 如果 INT1IE、PUIE 和 AIE 位为 1, 则响应 INT1 中断。

### 5.2.3 INT2 中断

INT2 中断通过寄存器 EIE1 中的 INT2IE 位置 1 使能 INT2 中断。通过 INTEDGCTL 中的 INT2SE 位设置触发边沿, INT2SE 置 1, 将 INT2 设置为上升沿触发, 清零设置为下降沿触发。EIF1 中的 INT2IF 为 INT2 的中断标志位。如果 IPEN 和 PINT2 位均置 1, 则 INT2 为高优先级中断。

INT2 引脚有触发脉冲时, INT2IF 被自动置 1, 如果 INT2IE、PUIE 和 AIE 位为 1, 则响应 INT2 中断。

#### 使用 INT 中断时的设置:

1. 将对应的 INTx 引脚设置为数字输入口。

2. 选择触发脉冲边沿是上升沿还是下降沿(INT0/1/2SE 置 1 为上升沿触发);

3. 将相应的外部中断使能位置 1(IN-), 如果为高优先级, 则 IPEN 和 PINTx 均置 1。

注:x=0/1/2

## 5.3 定时器中断

T0/1/4 寄存器发生溢出时, T0IF/T1IF/T4IF 位将会被置 1。通过将 T0IE/T1IE/T4IE 位置 1/清零可使能/禁止该中断。T3 与触摸模块共用中断使能位 T3IE、中断标志位 T3IF 和中断优先级位 PCT。有关定时/计数器模块的操作, 请参考定时/计数器部分。

## 5.4 P0 口中断

P0 口引脚的输入电平变化将使 P0IF(INTCTL.0)位置 1。通过设置/清除 P0IE(INTCTL.3)位, 可使能/禁止该中断。且该端口各引脚可通过 IOCL 寄存器来对每个引脚进行配置。当

IPEN 和 PP0 均置 1 时，P0 口中断配置为高优先级中断。

有关 P0 口的操作，请参考 P0 口部分。

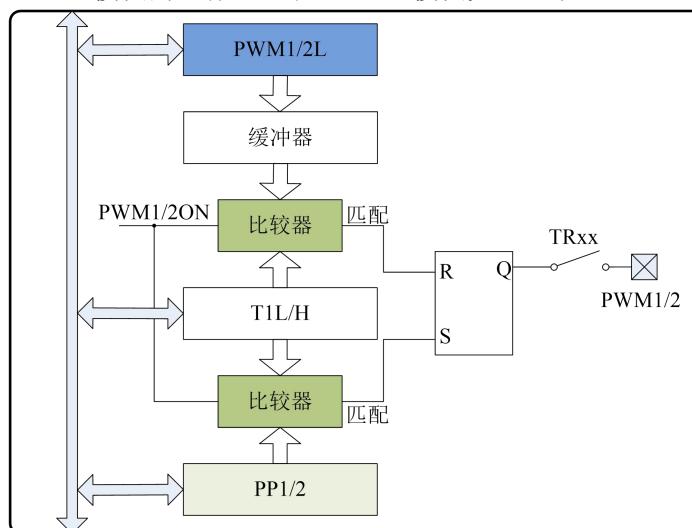

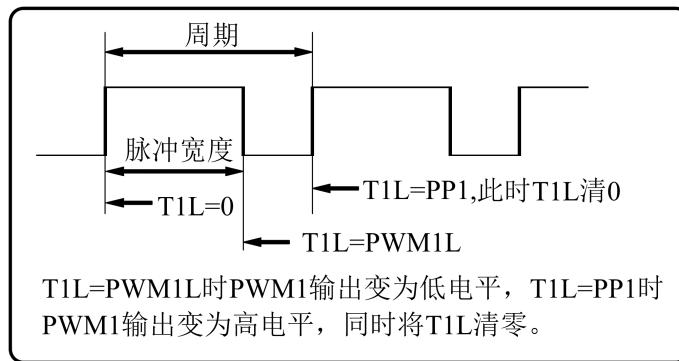

## 5.5 PWM 中断

使能 PWM1/2 后，T1L 分配给 PWM1 进行计数，T1H 分配给 PWM2 进行计数，当 T1L/H 与 PP1/2 匹配时，会触发相应的中断标志位 T1IF 和 PWM2IF。如果使能 T1IE 或者 PWM2IE，则会触发中断（AIE、PUIE 置 1）。当 IPEN 和 PT1 均置 1 时，PWM1 中断配置为高优先级中断。当 IPEN 和 PPWM2 均置 1 时，PWM2 中断配置为高优先级中断。

详见 PWM 部分。

## 5.6 中断现场保护

在中断响应时，硬件会把当前 PC 值加 1 入栈保存，中断结束后，硬件在将本次中断入栈时的值弹出载入 PC，继续执行后面的程序。通常，用户可能希望在中断时对一些关键寄存器的内容进行保存（例如，Rn 和 PSW），这些都需通过软件方式实现。

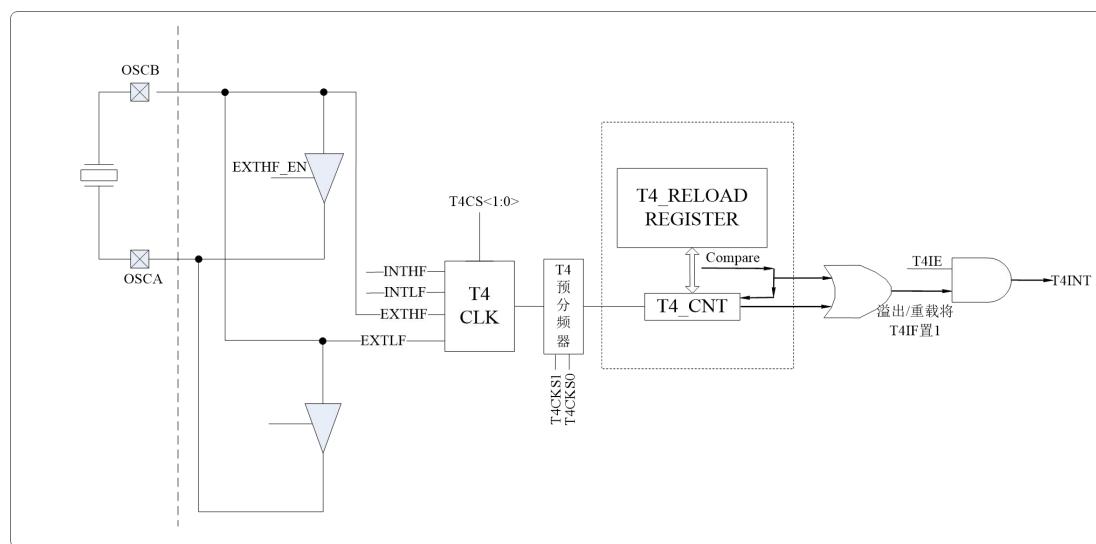

## 6 定时器/计数器

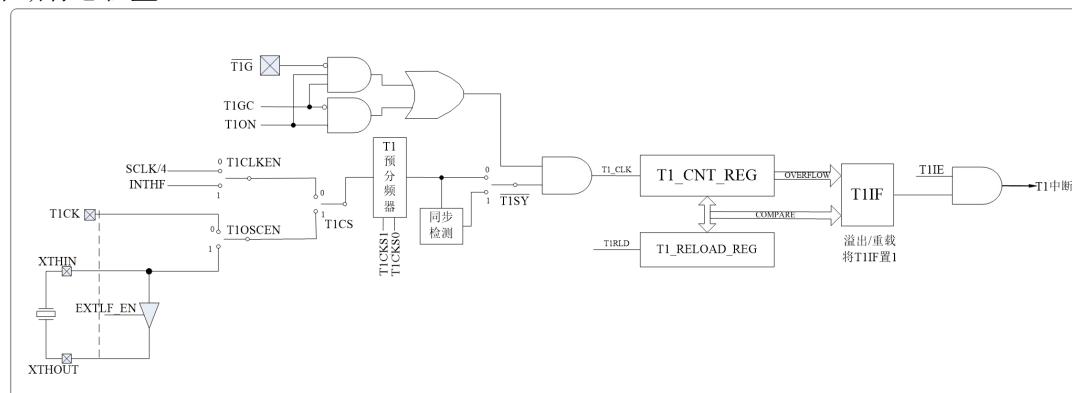

KF8A100ENG 单片机提供一个 8 位的定时器/计数器 T0、1 个 16 位的定时器/计数器 T1、1 个 16 位定时器 T3 和 1 个 16 位定时器/计数器 T4。

### 6.1 定时器/计数器 T0

T0 是一个 8 位的定时器/计数器，当 T0 寄存器值加到 255 时，再加 1，则会产生溢出，T0 寄存器的值返回到 0 开始重新计数。

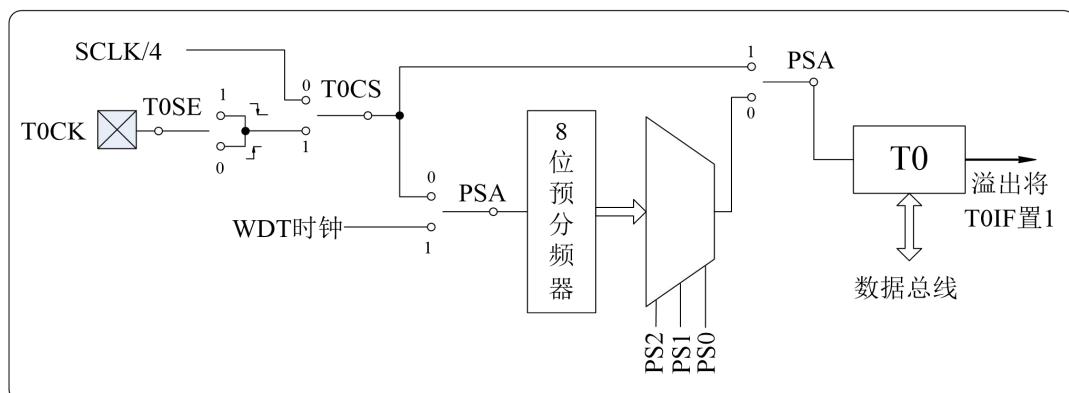

#### 6.1.1 T0 原理框图

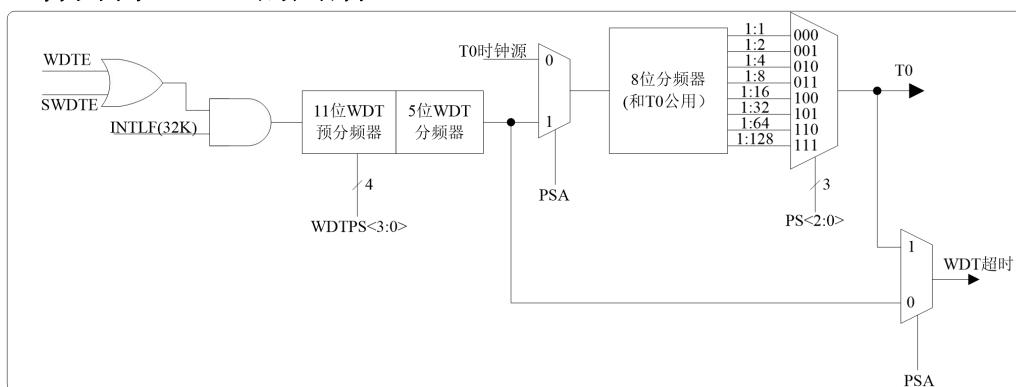

图 6.1 为 T0 的结构框图。T0 模块使用一个 8 位计数器作为预分频器，如寄存器 6.1 所示，通过软件设定 PSA 位(OPTR.3)的状态可对预分频器的分配进行控制，PSA 位清零可将预分频器分配给 T0 模块。通过设置 PS<2:0>位可选择预分频器的分频比。预分频器是不可读写的。

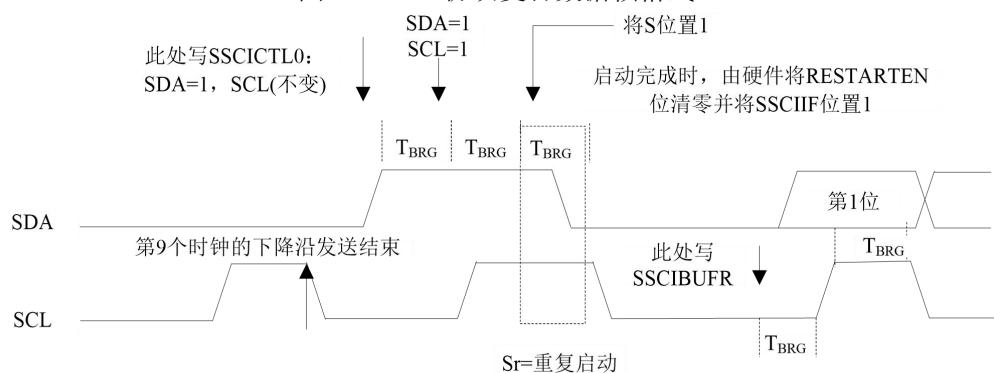

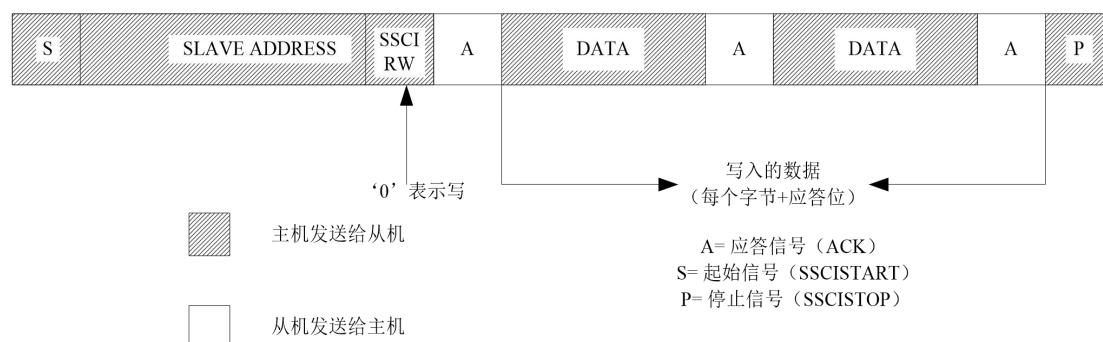

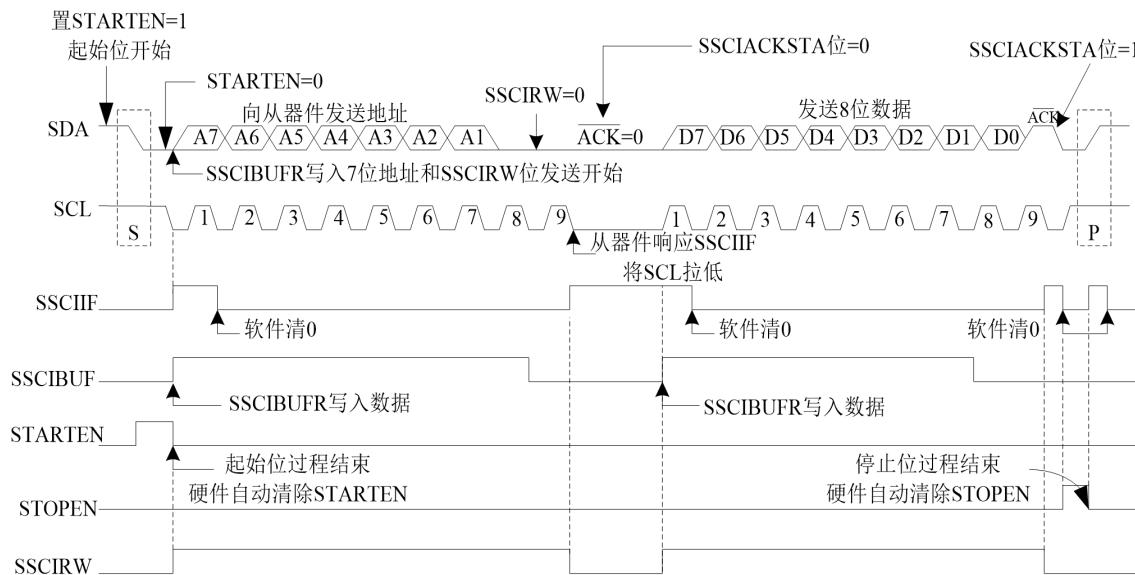

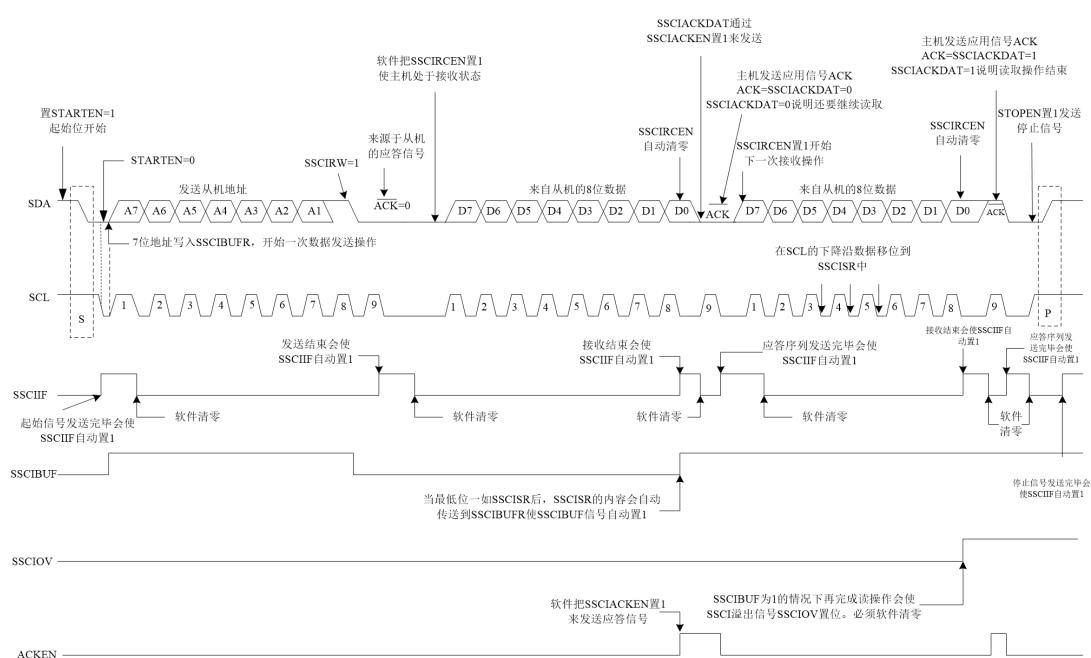

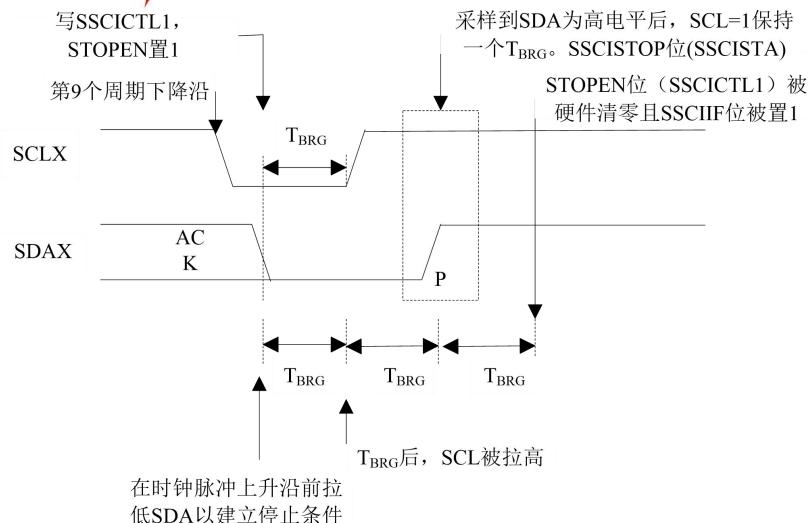

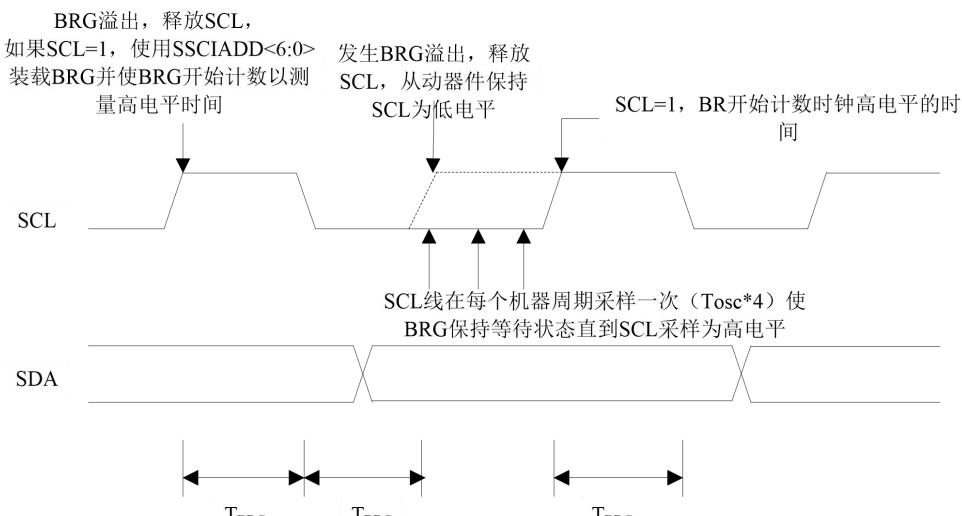

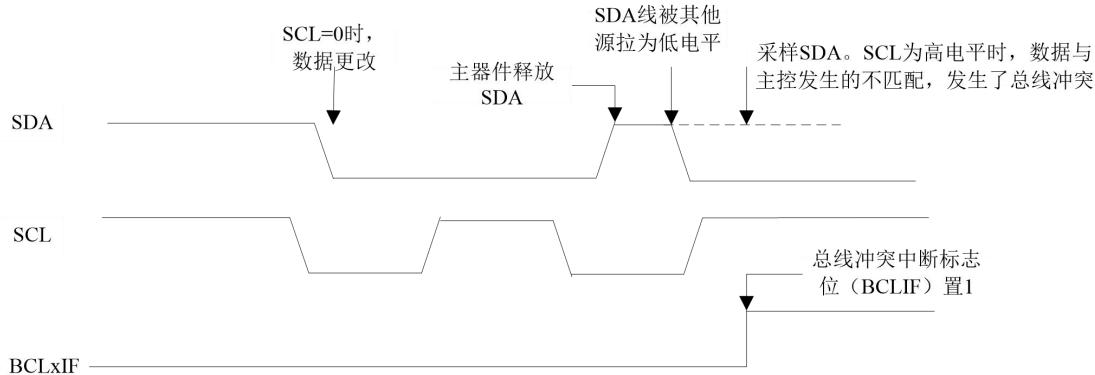

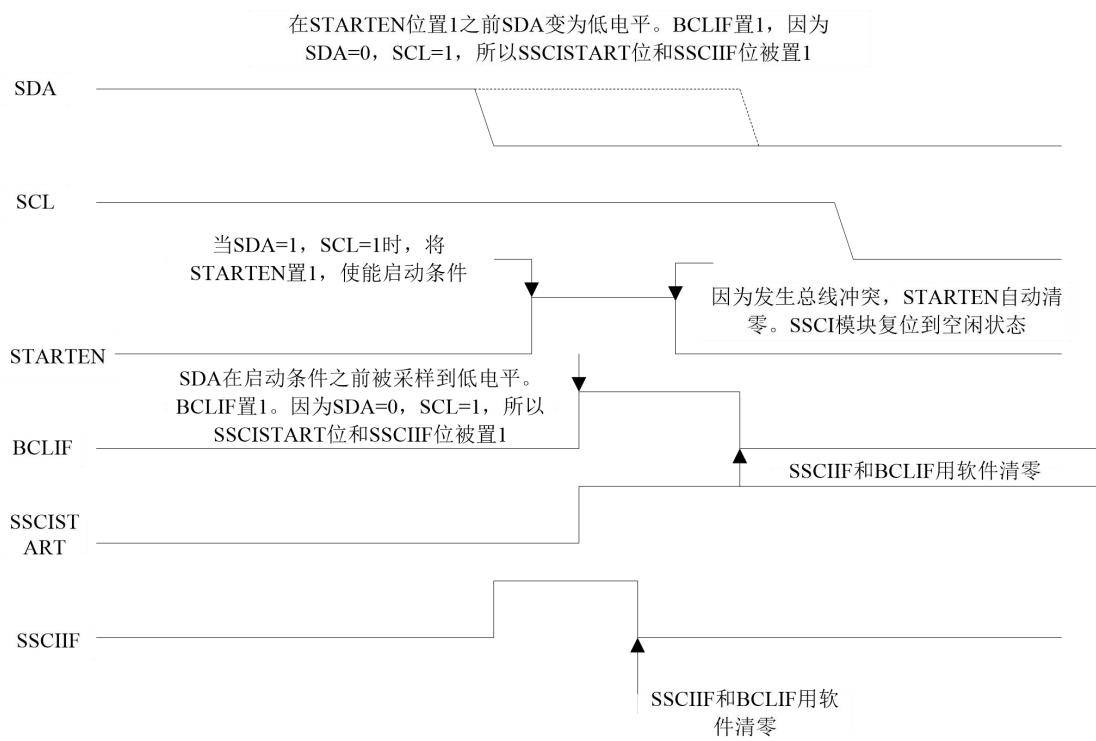

图 6.1 原理框图