# FR801xH Specification

Bluetooth Low Energy SoC

Rev V1.0

#### **General Description**

FR801xH is a single-chip low power Bluetooth (BLE) solution. It has the characteristics of low cost, low power consumption and less peripheral components.

The FR801xH supports a flexible memory architecture for storing Bluetooth profiles and custom application code, which can be updated over the air (OTA). The qualified Bluetooth Smart protocol stack is stored in a dedicated ROM. All software runs on the enhanced 32bit RISC CPU processor via a simple scheduler.

#### The FR801xH comes in 3 different versions:

| Device   | Package                     |              |           | Features                                              |

|----------|-----------------------------|--------------|-----------|-------------------------------------------------------|

|          | Туре                        | Size         | Shipment  | reatures                                              |

| FR8012HB | COD 16                      | 10x3.9x1.5mm | Tubo      | 256KB flash, 7 GPIOs, UART, IIC, SPI, PWM, ADC, I2S,  |

| FR8U12HB | SOP 16                      | 1.27mm pitch | Tube      | LDO                                                   |

| ED901CHA | OEN 22                      | 4x4x0.75mm   | Tananal   | 512KB flash, 15 GPIOs, UART, IIC, SPI, PWM, ADC, I2S, |

| FROUTOHA | FR8016HA QFN 32 0.4mm pitch |              | Tape reel | LDO, Li-Charger, Audio CODEC                          |

| FR8018HA | QFN 48                      | 6x6x0.75mm   | T         | 512KB flash, 31 GPIOs, UART, IIC, SPI, PWM, ADC, I2S, |

| LKOUISHA |                             | 0.4mm pitch  | Tape reel | LDO, Li-Charger, Audio CODEC                          |

#### **Features:**

- Complies with Bluetooth V5.0

- -94 dBm sensitivity in 1 Mbps BLE mode

- -98 dBm sensitivity in 125 Kbps BLE mode (long range)

- +10 dBm TX power (down to -20 dBm)

- Data rates: 2 Mbps, 1 Mbps, 500 Kbps and 125 Kbps

- Single-ended antenna output (Integrated balun)

- 8 mA peak current in TX (0 dBm)

- 9.7 mA peak current in RX

- RISC 32bit processor

- Configurable frequency: 12MHz, 24MHz, 48MHz

- support XIP (eXecute In Place)

- SWD debug

- 8K cache

- Flexible power management

- 1.8V-4.3V supply voltage range

- Integrated Buck DC-DC converter and LDO regulators with modes

- Fast wake-up using 32kHz internal oscillator

- 2.7 uA at 3V in System OFF mode, no RAM retention, wake on GPIO or Timer

- 6.1 uA at 3V in System ON mode, 48K RAM retention, wake on GPIO or Timer

- 128KB ROM, 48KB RAM and 256KB or 512KB

FLASH depends on different part number

- Hardware AES-128 cryptographic engine

- TRUE Random Number Generator (TRNG)

- Digital interfaces

- Up to 32 General Purpose I/Os

- 4-channel 10-bit ADC

- 2x UARTs with max 921600 baud rate

- 2x IIC controllers at up to 1MHz

- SPI master controllers at up to 24Mbps

- I2S master interface

- PDM interface with HW sample rate converter

- 6-channel PWM output

- 2x timer with 16 bit counter

- 16-bit audio codec with max 50mW PA out

- 16 x external interrupt source

- Power management unit

- 20 row x 8 column Matrix keyboard scanner with debouncing

- Watchdog

- 2 x RTC alarm with 32 bit counter

- 1 x Quadrature decoder

- 3-channel PMU PWM output

- Battery charge module, with max 258mA charge current

- Analog LDO output with max 120mA driver current

- Friendly development environment with provided SDK

- Embedded multi-protocols and profiles in ROM

#### Applications:

- Advanced computer peripherals

- Mouse

- Keyboard

- Advanced wearable devices

- Health/fitness sensor and monitor devices

- Internet of things (IOT)

- Smart home sensors and controllers

- Industrial IOT sensors and controllers

- Interactive entertainment devices

- Remote controllers

- Gaming controllers

#### **CONTENTS**

| 1 System  | Overview                                        | 6 -    |

|-----------|-------------------------------------------------|--------|

|           | 1.1 Functional Block Diagram                    | 6 -    |

|           | 1.2 System Blocks                               | 6 -    |

|           | 1.3 Power Domains and Modes                     | 8 -    |

|           | 1.3.1 Power Domains                             | 8 -    |

|           | 1.4 Power Modes                                 | 9 -    |

| 2 Packag  | e and Pin Information                           | 10 -   |

|           | 2.1 Package                                     | 10 -   |

|           | 2.2 Package Physical Dimensions                 | 11 -   |

|           | 2.3 Pins Description                            | 13 -   |

| 3 Power   | Management                                      | 17 -   |

|           | 3.1 Overview                                    | 17 -   |

|           | 3.2 PMU Controller                              | 17 -   |

|           | 3.3 PMU Interrupt Controller                    | 17 -   |

|           | 3.4 Sleep and Wakeup Timing                     | 18 -   |

|           | 3.4.1 Timeout Wakeup                            | 18 -   |

|           | 3.4.2 Asynchronous Event Wakeup                 | 19 -   |

|           | 3.5 Reference Block Description                 | 20 -   |

| 4 Clock g | eneration and Reset                             | 21 -   |

|           | 4.1 Clock Tree                                  | 21 -   |

|           | 4.2 Oscillators                                 | 22 -   |

| 5 UART    |                                                 | 23 -   |

|           | 5.1 General description                         | 23 -   |

|           | 5.2 Feature list                                | 23 -   |

|           | 5.3 Description of design                       | 24 -   |

|           | 5.3.1 Block diagram                             | 24 -   |

|           | 5.3.2 Block details                             | 24 -   |

|           | 5.4 Register description                        | 26 -   |

|           | 5.4.1 Register and memory mapping summary table | 26 -   |

|           | 5.4.2 Register                                  | 26 -   |

|           | 5.4.3 Configuration program flow                | 31 -   |

| 6 SSP     |                                                 | 32 -   |

|           | 6.1 Overview                                    | 32 -   |

|           | 6.2 Feature list                                | 32 -   |

|           | 6.3 Functional description                      | 32 -   |

|           | 6.3.1 Block diagram                             | 32 -   |

|           | 6.3.2 Block details                             | 33 -   |

|           | 6.3.3 SSP operation                             | 35 -   |

|           | 6.4 Register                                    | 37 -   |

|           | 6.4.1 Register summary table                    | 37 -   |

|           | 6.4.2 Register description                      | 37 -   |

| 7 IIC     |                                                 | 40 -   |

|           | 7.1 Overview                                    | - 40 - |

|          | 7.2 Feature list                             | 40 -   |

|----------|----------------------------------------------|--------|

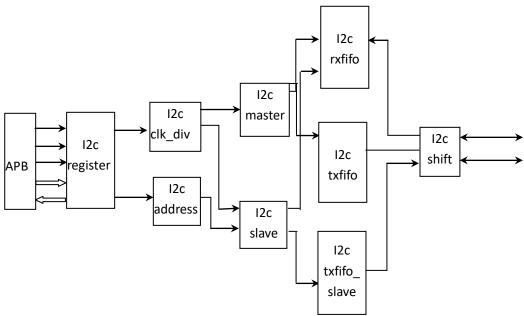

|          | 7.3 Block diagram                            | 40 -   |

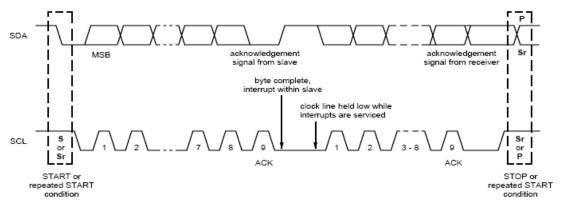

|          | 7.4 IIC protocols                            | 40 -   |

|          | 7.4.1 Byte format and timing                 | 40 -   |

|          | 7.4.2 7-bit Addressing                       | 41 -   |

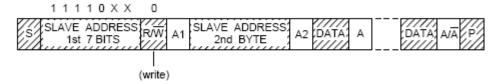

|          | 7.4.3 10-bit Addressing                      | 42 -   |

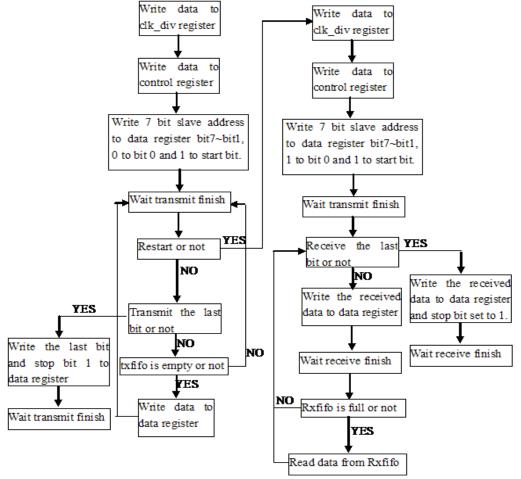

|          | 7.4.4 Operation description                  | 43 -   |

|          | 7.5 Register                                 | 44 -   |

|          | 7.5.1 Register summary table                 | 44 -   |

|          | 7.5.2 Register description                   | 44 -   |

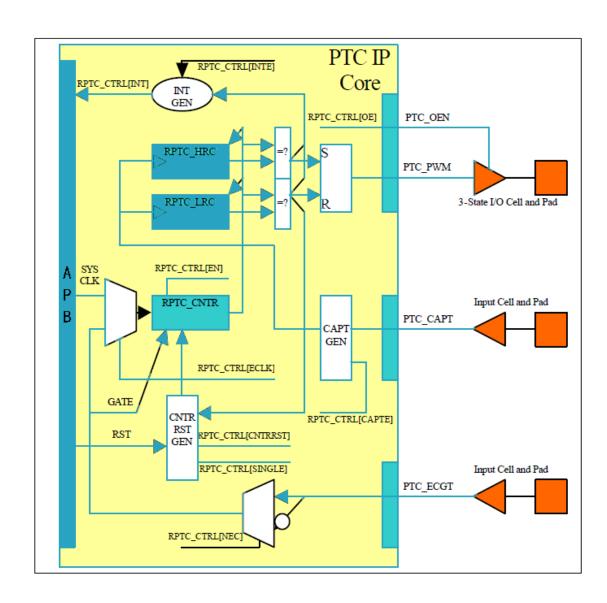

| 8 PWM .  |                                              | 48 -   |

|          | 8.1 Feature list                             | 48 -   |

|          | 8.2 Block diagram                            | 48 -   |

|          | 8.3 Register                                 | 49 -   |

|          | 8.3.1 Register summary table                 | 49 -   |

|          | 8.3.2 Register description                   | 49 -   |

|          | 8.4 PWM mode and operation                   | 50 -   |

|          | 8.4.1 PWM mode                               | 50 -   |

| 9 SARAD  | )C                                           | 51 -   |

|          | 9.1 Feature list                             | 51 -   |

|          | 9.2 Register                                 | 51 -   |

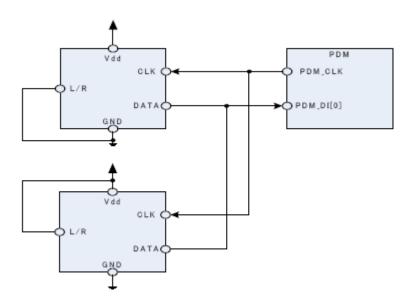

| 10 PDM   |                                              | 54 -   |

|          | 10.1 Overview                                | 54 -   |

|          | 10.2 Feature list                            | 54 -   |

|          | 10.3 Module operation                        | 54 -   |

|          | 10.4 Register                                | 55 -   |

| 11 I2S   |                                              | 58 -   |

|          | 11.1 Overview                                | 58 -   |

|          | 11.2 Feature list                            | 58 -   |

|          | 11.3 Operations                              | 58 -   |

|          | 11.3.1 Mode                                  | 58 -   |

|          | 11.3.2 BCLK                                  | 58 -   |

|          | 11.3.3 Frame Clock                           | 59 -   |

|          | 11.3.4 Audio Interface Timing                | 59 -   |

|          | 11.4 Register                                | 60 -   |

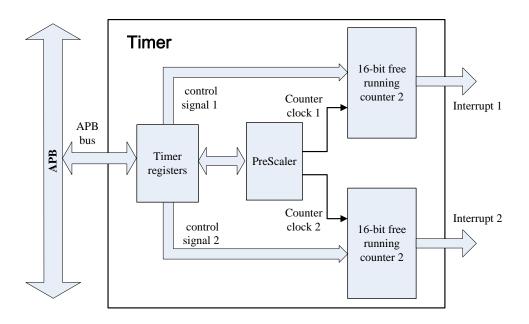

| 12 TIMEI | R                                            | 63 -   |

|          | 12.1 Overview                                | 63 -   |

|          | 12.2 Feature list                            | 63 -   |

|          | 12.3 Timer Block Diagram                     | 63 -   |

|          | 12.4 Register                                | 63 -   |

|          | 12.5 Operation Description                   | 64 -   |

| 13 EFUSI | E                                            |        |

|          | 13.1 Register                                | 65 -   |

| 14 FRSDI | IM(freg-chin designed spi master controller) | - 67 - |

| 15 PMU    | (Power management unit)                                 | 68 -    |

|-----------|---------------------------------------------------------|---------|

|           | 15.1 PIN Configuration                                  | 68 -    |

|           | 15.2 Clock and Reset                                    | 71 -    |

|           | 15.3 Interrupt                                          | 72 -    |

|           | 15.4 Debounce(Anti-Shake)                               | 75 -    |

|           | 15.5 Watchdog                                           | 77 -    |

|           | 15.6 RTC                                                | 77 -    |

|           | 15.7 Matrix Keyboard                                    | 79 -    |

|           | 15.8 Quadrature decoder                                 | 81 -    |

|           | 15.9 Calibration                                        | 84 -    |

|           | 15.10 PWM                                               | 86 -    |

| 16 CODE   | C                                                       | 89 -    |

|           | 16.1 Overview                                           | 89 -    |

|           | 16.2 Feature list                                       | 89 -    |

|           | 16.3 Register                                           | 89 -    |

| 17 SYSTE  | M REGS                                                  | 97 -    |

|           | 17.1 Register                                           | 97 -    |

|           | 17.2 Port IO MUX                                        | 103 -   |

| 18 GPIO   |                                                         | 104 -   |

|           | 18.1 General purpose ports                              | 104 -   |

|           | 18.2 Register                                           | 104 -   |

|           | 18.3 GPIO output                                        | 105 -   |

|           | 18.4 GPIO input                                         | 106 -   |

| 19 EXTI(  | external interrupt)                                     | 107 -   |

|           | 19.1 Register                                           | 107 -   |

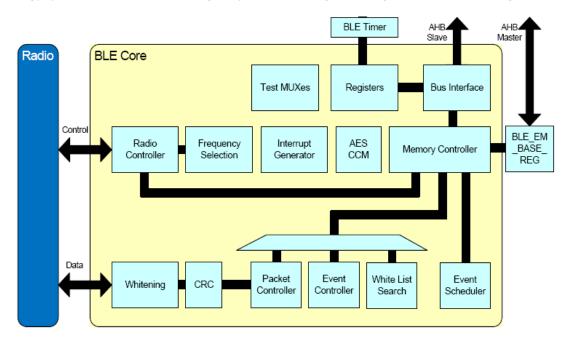

| 20 BLE C  | ore                                                     | 110 -   |

| 21 Mem    | ory Map                                                 | 111 -   |

| 22 Electi | rical Characteristics                                   | 112 -   |

|           | 22.1 Absolute Maximum Ratings                           | 112 -   |

|           | 22.2 Recommended Operating Conditions                   | 112 -   |

|           | 22.3 IO Input/Output Electrical Logical Characteristics | 112 -   |

|           | 22. 4 Internal Resistor Characteristics                 | 113 -   |

|           | 22.5 Audio CODEC                                        | 113 -   |

|           | 22.6 Crystal oscillator                                 | 113 -   |

|           | 22.7 BT Characteristics                                 | 114 -   |

|           | 22.8 Power Consumption                                  |         |

| 22 Povis  | ion History                                             | _ 115 _ |

# 1 System Overview

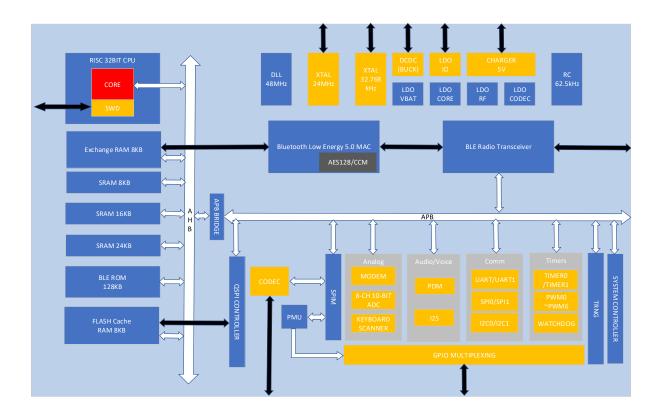

### 1.1 Functional Block Diagram

### 1.2 System Blocks

The FR801xH contains the following blocks:

**RISC CPU**. The processor has a 32-bit instruction set that implements a superset of 16 and 32-bit instructions to maximize code density and performance. It is used for implementing the higher layers of the Bluetooth Low Energy protocol. It is accompanied by a powerful cache controller which can minimize flash wait states when fetching instructions.

**BLE 5.0 Core**. This is the baseband hardware accelerator for the Bluetooth Low Energy protocol.

**ROM**. This is a 128KB ROM containing the Bluetooth Low Energy protocol stack as well as the boot code sequence.

Exchange RAM. This is a 8KB SRAM used for data exchange between firmware and the BLE baseband.

**SRAM**. This is a 48KB SRAM used for data storage.

**Flash Cache RAM**. This is a 8KB data RAM used primarily by the cache controller. The cache controller executes directly from external QSPI FLASH, thus reducing accesses to FLASH.

UART. Asynchronous serial interface with a FIFO of 32 bytes depth, baud rate vary from 4800 to 921600.

SPI. Serial peripheral interface with a FIFO of 128 bytes depth and 8-bit wide. Max bus frequency is 24MHz.

**I2C**. This is Master I2C interfaces used for sensors and/or host MCU communication. It includes a RX FIFO of 8-bit width, 8 bytes depth and a TX FIFO of 8-bit width, 10 bytes depth. Max bus frequency is 2MHz.

**QSPI Controller**. Interface to a Quad SPI FLASH device, with max 24MHz bus frequency.

**SARADC**. Differential successive approximation register analog-to-digital converter. It supports up to eight external analog input channels, 10-bit width and 1MHz sample rate.

Radio transceiver. This block implements the RF part of the Bluetooth Low Energy protocol at 2.4GHz.

**Clock generator**. This block is responsible for the clocking of the system. It contains a 24MHz crystal oscillators which is used for the active mode of the system. There is also a 62.5 kHz oscillator (RC62.5K) with precision (< 300 ppm). The RCX oscillator can be used as a sleep clock to improve the power dissipation, while reducing the bill of materials of the system.

Timers. 2 separate 16-bit counter Timer.

**PWM.** PWM module circuit implements pulse width modulation wave output. 6-channels digital PWM output module with super high up to (1/48M) resolution. Also there are another 3–channels PMU PWM output module, which has 1/(PMU system clk) resolution.

**Keyboard scanner**. This circuit implements scanning and debouncing of a keyboard matrix and generates an interrupt upon a configurable action without the need of CPU.

AHB/APB bus. Implements the AMBA Lite version of the AHB and APB specifications.

**I2S and PDM port**. This part enables audio streaming by means of a Pulse Density Modulation (PDM) and Inter-IC Sound (I2S) interface. It supports a digital microphone, an analog microphone and MONO speaker using PDM interface and internal codec block.

I2S interface is with 64 16-bit width FIFO depth, max 24MHz bus speed, and 16 kHz/8kHz, 16-bit sample rates. PDM interface is with 64 16-bit width FIFO depth, 1MHz/2MHz bus speed and 16 kHz/ 8kHz, 16-bit sample rates.

**Audio codec**, It consists 1-ch 16bit  $\sum \triangle$  ADC, 1-ch 16bit  $\sum \triangle$  DAC, which samples rate is up to 48kHz. And there are internal microphone bias equal to 0.9\*CODEC power voltage, input PGA amplifier -17.25dB - 30dB gain range, output earphone PA which output power is up to 50mW inside the audio codec block.

**Power management**. A sophisticated power management circuit with a Buck DC-DC converter and several LDOs that can be turned on/off via PMU block. Extra pins are provided for supplying external devices, even when the FR801xH is in sleep/deep sleep mode.

It also comprises a Constant Current/Constant Voltage (CCCV) charger for the battery charging and a state-of-charge fuel gauge circuit. And the CCCV charger current varies from 48mA to 258mA.

This block also include one LDO output with max 125mA drive capability, and  $1.8\sim3.5$ V output voltage range. Pin pad drive capability is 12mA. The total drive capability of all pads is equal to LDO output driver capacity, which is 125mA.

A more detailed description of each of the components of the FR801xH is presented in the following sections.

#### 1.3 Power Domains and Modes

#### 1.3.1 Power Domains

The FR801xH comprises several different power domains, these are controlled by power switching elements, thus eliminating leakage currents by totally powering them down.

- PD Domain, power down in sleep mode

- Option PK Domain, power down or not depending on the configuration in PMU register

- PK Domain, always on domain

An illustration of the power domains on the chip block diagram is presented as below.

#### 1.4 Power Modes

The FR801xH has four main power modes, which are distinguished by the power domains and clocks that are active:

- Active Mode, all analog blocks turn on, all clocks are available and all memories are powered up and accessible.

- Light Sleep Mode, all analog blocks turn off, all digital block's power is switched on, but some block's clocks can be switched off according to the Clock-Gating.

- Deep Sleep Mode, all analog blocks turn off, all digital block is power off except partial retention SRAM. The system can be waked up by the external interrupt or internal timer.

- Shutdown Mode, all analog and digital block is off. The system can be waked up by PMU due to the special pin (onkey) interrupt.

# 2 Package and Pin Information

### 2.1 Package

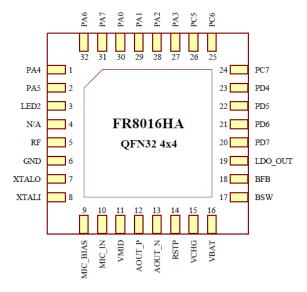

• The FR8016HA comes in a 4\*4mm QFN package with 32 pins. The pin assignment is shown as below.

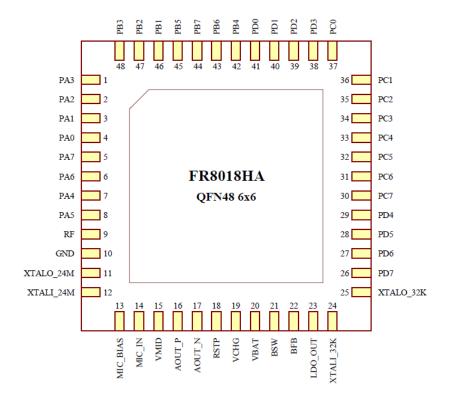

• The FR8018HA comes in a 6\*6mm QFN package with 48 pins. The pin assignment is shown as below.

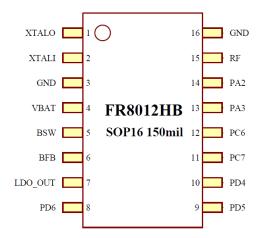

• The FR8012HB comes in a SOP package with 16 pins. The pin assignment is shown as below.

### 2.2 Package Physical Dimensions

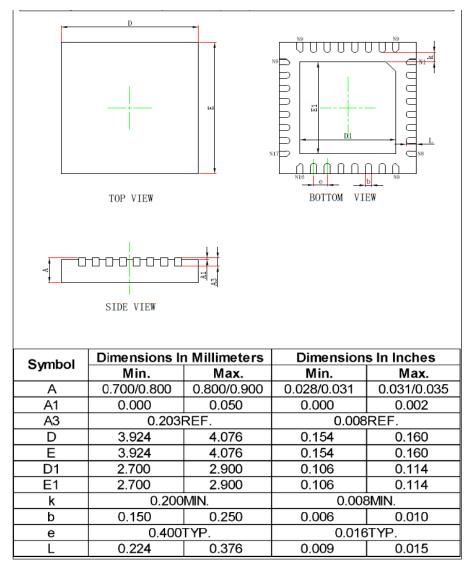

QFN32 - 4x4 mm package outline

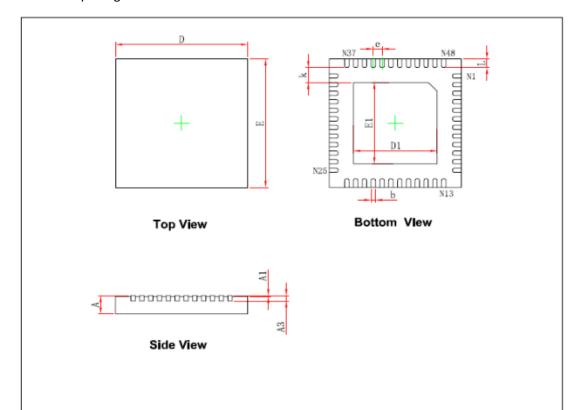

#### • QFN48 - 6x6 mm package outline

| Symbol | Dimensions I | n Millimeters | Dimensions In Inches |             |  |

|--------|--------------|---------------|----------------------|-------------|--|

| Symbol | Min.         | Max.          | Min.                 | Max.        |  |

| Α      | 0.700/0.800  | 0.800/0.900   | 0.028/0.031          | 0.031/0.035 |  |

| A1     | 0.000        | 0.050         | 0.000                | 0.002       |  |

| A3     | 0.203        | REF.          | 0.008                | REF.        |  |

| D      | 5.924        | 6.076         | 0.233                | 0.239       |  |

| E      | 5.924        | 6.076         | 0.233                | 0.239       |  |

| D1     | 3.700        | 3.900         | 0.146                | 0.154       |  |

| E1     | 3.700        | 3.900         | 0.146                | 0.154       |  |

| k      | 0.200        | OMIN.         | 0.008MIN.            |             |  |

| b      | 0.150        | 0.250         | 0.006                | 0.010       |  |

| е      | 0.400        | TYP.          | 0.016                | TYP.        |  |

| L      | 0.324        | 0.476         | 0.013                | 0.019       |  |

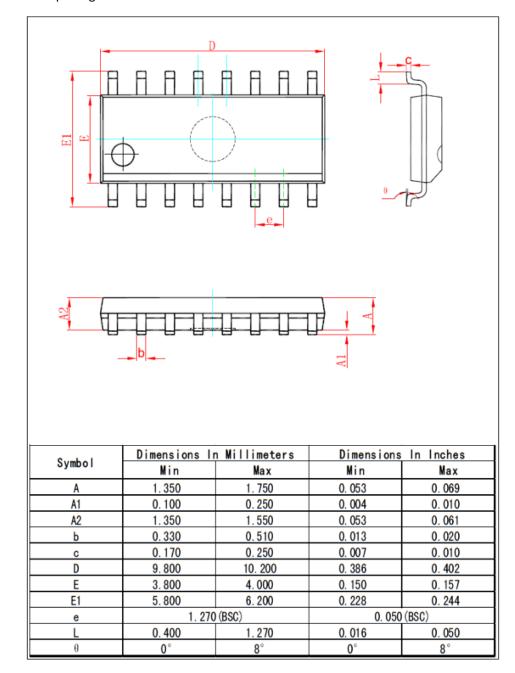

#### SOP16 - 150mil package outline

## 2.3 Pins Description

FR801xH is a CMOS device. Floating level on input signals will cause unstable device operation and abnormal current consumption. Pull-up or Pull-down resistors should be used appropriately for input or bidirectional pins.

| Notation | Description    |

|----------|----------------|

| 1        | Digital Input  |

| 0        | Digital Output |

| Al  | Analog input           |

|-----|------------------------|

| AO  | Analog output          |

| Ю   | Bidirectional(digital) |

| OD  | Open Drain             |

| PWR | Power                  |

| GND | Ground                 |

| Pin number |          | r        |           |      |                                                             |

|------------|----------|----------|-----------|------|-------------------------------------------------------------|

| FR8018HA   | FR8016HA | FR8012HB | Pin name  | Туре | Description                                                 |

| 1          | 27       | 13       | PA3       | DIO  | SDA1/I2SDIN/PWM3/SSPDIN/UTXD0/UTXD1/ANTCTL1/PD MDAT/PWM2    |

| 2          | 28       | 14       | PA2       | DIO  | SCL1/I2SDOUT/PWM2/SSPDOUT/URXD0/URXD1/ANTCTL0 /PDMCLK/PWM3  |

| 3          | 29       | -        | PA1       | DIO  | SDA0/I2SFRM/PWM1/SSPCSN/UTXD0/UTXD1/ANTCTL0/P<br>DMDAT/PWM0 |

| 4          | 30       | -        | PA0       | DIO  | SCL0/I2SCLK/PWM0/SSPCLK/URXD0/URXD1/CLKOUT/PD MCLK/PWM1     |

| 5          | 31       | -        | PA7       | DIO  | SDA1/I2SDIN/PWM1/SSPDIN/UTXD0/UTXD1/ANTCTL0/PD MDAT/PWM0    |

| 6          | 32       | -        | PA6       | DIO  | SCL1/I2SDOUT/PWM0/SSPDOUT/URXD0/URXD1/CLKOUT/PDMCLK/PWM1    |

| 7          | 1        | -        | PA4       | DIO  | SCL0/I2SCLK/PWM4/SSPCLK/URXD0/URXD1/CLKOUT/PD MCLK/PWM5     |

| 8          | 2        | -        | PA5       | DIO  | SDA0/I2SFRM/PWM5/SSPCSN/UTXD0/UTXD1/ANTCTL1/P DMDAT/PWM4    |

| -          | 3        | -        | LED2      | DO   | LED2 control output                                         |

| -          | 4        | -        | N/A       | -    | Not applicable                                              |

| 9          | 5        | 15       | RF        | AIO  | RF input and output                                         |

| 10         | 6        | 3, 16    | GND       | GND  | Ground                                                      |

| 11         | 7        | 1        | XTALO_24M | AO   | 24MHz Crystal oscillator output                             |

| 12         | 8        | 2        | XTALI_24M | Al   | 24MHz Crystal oscillator input                              |

| 13         | 9        | -        | MIC_BIAS  | AO   | Microphone bias output                                      |

| 14         | 10       | -        | MIC_IN    | Al   | Microphone input                                            |

| 15         | 11       | -        | VMID      | Al   | Common mode voltage                                         |

| 16         | 12       | -        | AOUT      | AO   | Speaker output positive                                     |

| 17         | 13       | -        | AOUT      | AO   | Speaker output negative                                     |

| 18         | 14       | -        | RSTP      | Al   | Global reset (high active)                                  |

| 19         | 15       | -        | VCHG      | PWR  | Charger supply input                                        |

| 20         | 16       | 4        | VBAT      | PWR  | Battery positive supply input                               |

| 21         | 17       | 5        | BSW       | AO   | DC/DC output terminal                                       |

| 22         | 18       | 6        | BFB       | Al   | DC/DC feedback input terminal                               |

| •  |    | •  |           |     |                                                |

|----|----|----|-----------|-----|------------------------------------------------|

| 23 | 19 | 7  | LDO_OUT   | AO  | Analog linear regulator output                 |

| 24 | -  | -  | XTALI_32K | Al  | 32KHz Crystal oscillator input                 |

| 25 | -  | 1  | XTALO_32K | AO  | 32KHz Crystal oscillator output                |

| 26 | 20 | -  | PD7       | DIO | SDA1/I2SDIN/PWM1/SSPDIN/UTXD0/UTXD1/ANTCTL1/PD |

|    |    |    |           |     | MDAT/PWM0/ADC3                                 |

| 27 | 21 | 8  | PD6       | DIO | SCL1/I2SDOUT/PWM0/SSPDOUT/URXD0/URXD1/CLKOUT/  |

|    |    |    |           |     | PDMCLK/PWM1/ADC2                               |

| 28 | 22 | 9  | PD5       | DIO | SDA0/I2SFRM/PWM5/SSPCSN/UTXD0/UTXD1/ANTCTL0/P  |

|    |    |    |           |     | DMDAT/PWM4/ADC1                                |

| 29 | 23 | 10 | PD4       | DIO | SCL0/I2SCLK/PWM4/SSPCLK/URXD0/URXD1/ANTCTL0/PD |

|    |    |    |           |     | MCLK/PWM5/ADC0                                 |

| 30 | 24 | 11 | PC7       | DIO | SDA1/I2SDIN/PWM5/SSPDIN/UTXD0/UTXD1/SWDIO/PD   |

|    |    |    |           |     | MDAT/PWM4                                      |

| 31 | 25 | 12 | PC6       | DIO | SCL1/I2SDOUT/PWM4/SSPDOUT/URXD0/URXD1/SWTCK/   |

|    |    |    |           |     | PDMCLK/PWM5                                    |

| 32 | 26 | -  | PC5       | DIO | SDA0/I2SFRM/PWM5/SSPCSN/UTXD0/UTXD1/SWV/PDM    |

|    |    |    |           |     | DAT/PWM4                                       |

| 33 | -  | -  | PC4       | DIO | SCL0/I2SCLK/PWM4/SSPCLK/URXD0/URXD1/ANTCTL1/PD |

|    |    |    |           |     | MCLK/PWM5                                      |

| 34 | -  | -  | PC3       | DIO | SDA1/I2SDIN/PWM3/SSPDIN/UTXD0/UTXD1/SWV/PDMD   |

|    |    |    |           |     | AT/PWM2                                        |

| 35 | -  | =  | PC2       | DIO | SCL1/I2SDOUT/PWM2/SSPDOUT/URXD0/URXD1/SWV/PD   |

|    |    |    |           |     | MCLK/PWM3                                      |

| 36 | -  | -  | PC1       | DIO | SDA0/I2SFRM/PWM1/SSPCSN/UTXD0/UTXD1/SWV/PDM    |

|    |    |    |           |     | DAT/PWM0                                       |

| 37 | -  | -  | PC0       | DIO | SCL0/I2SCLK/PWM0/SSPCLK/URXD0/URXD1/SWV/PDMCL  |

|    |    |    |           |     | K/PWM1                                         |

| 38 | -  | -  | PD3       | DIO | SDA1/I2SDIN/PWM3/SSPDIN/UTXD0/UTXD1/WLANRX/PD  |

|    |    |    |           |     | MDAT/PWM2                                      |

| 39 | -  | -  | PD2       | DIO | SCL1/I2SDOUT/PWM2/SSPDOUT/URXD0/URXD1/WLANTX   |

|    |    |    |           |     | /PDMCLK/PWM3                                   |

| 40 | -  | -  | PD1       | DIO | SDA0/I2SFRM/PWM1/SSPCSN/UTXD0/UTXD1/BLERX/PD   |

|    |    |    |           |     | MDAT/PWM0                                      |

| 41 | -  | -  | PD0       | DIO | SCL0/I2SCLK/PWM0/SSPCLK/URXD0/URXD1/BLETX/PDMC |

|    |    |    |           |     | LK/PWM1                                        |

| 42 | -  | -  | PB4       | DIO | SCL0/I2SCLK/PWM4/SSPCLK/URXD0/URXD1/CLKOUT/PD  |

|    |    |    |           |     | MCLK/PWM5                                      |

| 43 | -  | -  | PB6       | DIO | SCL1/I2SDOUT/PWM2/SSPDOUT/URXD0/URXD1/ANTCTL1  |

|    |    |    |           |     | /PDMCLK/PWM3                                   |

| 44 | -  | -  | PB7       | DIO | SDA1/I2SDIN/PWM3/SSPDIN/UTXD0/UTXD1/CLKOUT/PD  |

|    |    |    |           |     | MDAT/PWM2                                      |

| 45 | -  | -  | PB5       | DIO | SDA0/I2SFRM/PWM5/SSPCSN/UTXD0/UTXD1/ANTCTL0/P  |

|    |    |    |           |     | DMDAT/PWM4                                     |

|    |    |    | 1         |     |                                                |

### FR801xH Specification

| 46 | - | - | PB1 | DIO | SDA0/I2SFRM/PWM1/SSPCSN/UTXD0/UTXD1/BLERX/PD MDAT/PWM0    |

|----|---|---|-----|-----|-----------------------------------------------------------|

| 47 | - | - | PB2 | DIO | SCL1/I2SDOUT/PWM2/SSPDOUT/URXD0/URXD1/WLANTX /PDMCLK/PWM3 |

| 48 | - | - | PB3 | DIO | SDA1/I2SDIN/PWM3/SSPDIN/UTXD0/UTXD1/WLANRX/PD MDAT/PWM2   |

# 3 Power Management

#### 3.1 Overview

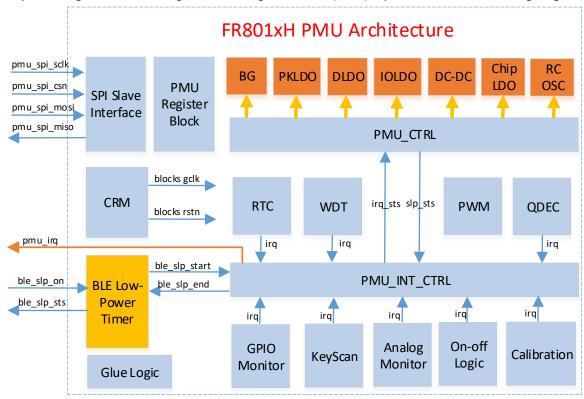

The FR801xH has a complete integrated power management unit (PMU) which comprises a Single Inductance Single Output (SISO) DC-DC converter, various LDOs for the different power domains of the system, a Constant Current Constant Voltage (CCCV) charger for battery recharging, a charge detection Circuit, an interrupt controller, on-off logic, BLE sleep counter, RTC, watch dog, keyscan, QDEC, PWM, calibration block and GPIO monitor.

The system diagram of the analog Power Management Unit (PMU) is presented in the following diagram.

### 3.2 PMU Controller

This block controls the DC-DC converter, RC OSC, backup Voltage, various LDO and interrupt status from PMU interrupt controller. The Block generates timing logic according to the actual analog on-off timing. The timing information can be set by the PMU Register.

### 3.3 PMU Interrupt Controller

This block is used to enable or disable interrupt for asynchronous event and output interrupt status signal. Also, this block can generate 'VBAT\_OK', 'VBATOR' and analog 'ON-KEY' signals based on the first power-on event on

VBAT. Furthermore, It generates first power-on signal, power-off interrupt signal and power-on signal in shutdown mode.

The PMU interrupt controller includes following interrupt source:

- Calibration: calibration done interrupt

- Wakeup\_lp: BLE sleep timer wakeup interrupt (also in baseband sleep interrupt)

- RTC\_ALARMA: RTC alarm A interrupt

- RTC\_ALARMB: RTC alarm B interrupt

- KEYSCAN: Keyscan block valid key pressed or released

- Onkey on/off: Onkey power on/off interrupt

- WDT: Watchdog interrupt

- Charger: Plug in, pull off charger, battery full and insufficient power interrupt

- Ulvd\_off: Ultra low power poweroff interrupt

- GPIO: GPIO interrupt if GPIO is controlled by the PMU

- QDEC: Quadrature decoder interrupt

- OTP: Over-temperature interrupt

Above-mentioned interrupt can be forbidden or cleared through related PMU registers. Details about the PMU interrupt can be found in **PMU register** section.

### 3.4 Sleep and Wakeup Timing

In FR801xH, Sleep and wakeup function is realized by BLE baseband timer. In order to reduce power consumption, BLE baseband clock is in PD domain, and be woke up by RC clock. When the system enter sleep, baseband, CPU and digital logic are switched off; retention memory stores the SOC registers. BLE baseband sleep timing also support BLE event schedule and asynchronous interrupt wakeup.

Main feature about the baseband sleep timing is shown as below:

- Baseband clock retention before sleep

- Baseband clock resume when wake up

- Support asynchronous interrupt wakeup

- Generate Power control signals

There are two modes based on BLE sleep timing, Timeout wakeup and Asynchronous event wakeup. The details are described in the following sections.

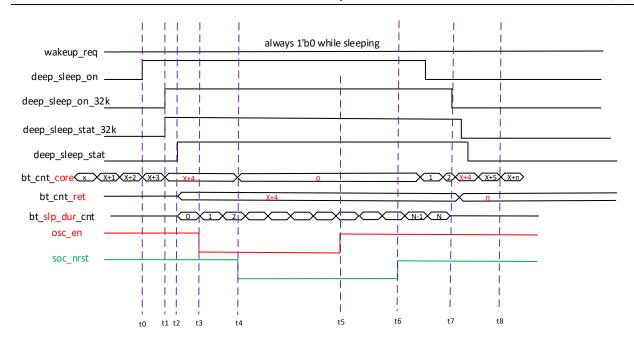

### 3.4.1 Timeout Wakeup

Before the system goes to sleep, it should set sleep time, and then start the BLE sleep timer. When the timer is reached, the PMU will generate sleep end signal to trigger wakeup interrupt. Actually, PMU will output 'OSC\_EN' signal and power up related analog block before it generate sleep end signal.

The timing diagram is shown as below:

ble sleep model:timer reached

#### Note:

- At t5, start recover system power

- At t7, stop sleep timer, resume BLE clock

- At t8, process the timeout interrupt triggered at t7, compensate the BLE clock according to real sleep time 'N'

- TWOSC = t7- t5, analog power on preparing time

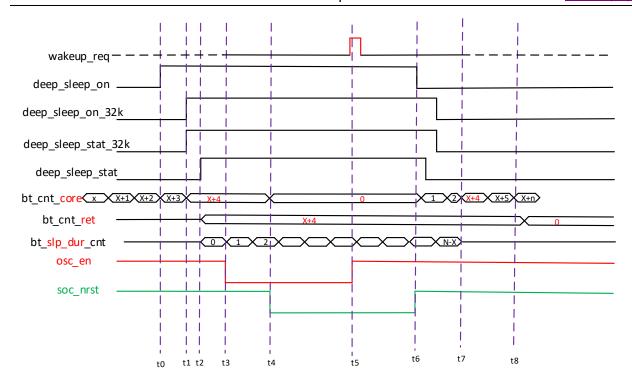

### 3.4.2 Asynchronous Event Wakeup

The PMU block will power on the analog block if there is an asynchronous wakeup event triggered in the sleep mode. When it happens, the BLE sleep timer will keep accumulating until additional TWEXT lowpow clock passed. Then it will generate sleeping ending signal used to trigger wakeup interrupt.

ble sleep mode2: wakeup req

#### Note:

- At t5, wakeup\_req event which will trigger system to power on

- At t7, stop BLE sleep timer and resume the BLE clock

- At t8, process the timeout interrupt triggered at t7, compensate the BLE clock according to real sleep time 'N X'

- TWEXT = t7-t5, analog power on preparing time

### 3.5 Reference Block Description

The PMU controller blocks like WDT, QDEC, PWM, KEYSCAN, RTC and so on. These blocks are described in the **PMU register** section and can be controlled by corresponding registers.

# 4 Clock generation and Reset

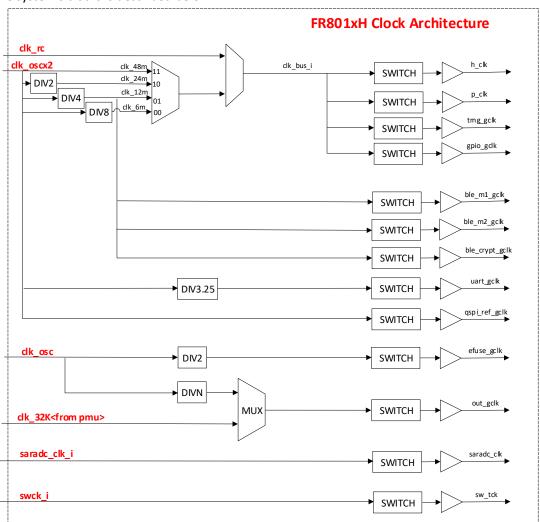

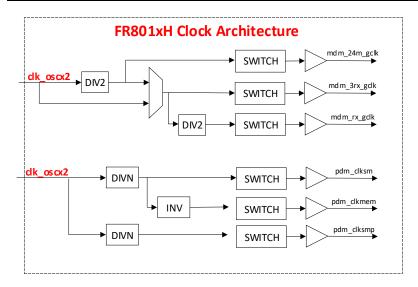

#### 4.1 Clock Tree

The system's clocks is described below.

The above diagrams depict all possible clock sources and all different divisions and multiplexing paths for each block's clock. Most of logic blocks are driven by 48MHz clock. CLK\_OSC (24MHz) is for fixed frequency logic block.

#### 4.2 Oscillators

#### **Crystal oscillators:**

For facility design, the external crystal oscillator is fixed at 24MHz.Base on it, another 48MHz clock is generated for higher soc running frequency. By the way, for lower system power, there is no PLL inside.

#### **RC** oscillators:

The RC oscillator is designed for system sleep & shutdown mode. Its frequency is 62.5KHz. Calibration should be done before use it as BLE sleep clock counter.

### **5 UART**

The FR801xH contains two uart block, UARTO and UART1 without flow control.

### **5.1** General description

This block performs serial to parallel conversion of data received from a peripheral to processor, and also parallel to serial conversion of a processor data for transmitting to a peripheral. It's an APB slave device.

### 5.2 Feature list

- > Full compatibility with UART industry standard 16550

- ➤ 32-Byte depth FIFOs for both Rx/Tx

- Programmable baud rate generator, baud rate range varies from 4800 to 921600

- > Independently receiver clock input

- Prioritized and independently controlled interrupts

- > Fully programmable serial interface characteristics:

- 5-,6-,7- or 8-bit characters

- Even-, Odd-, or No-Parity bit generation and detection

- 1-,1.5- or 2-Stop bit generation

### 5.3 Description of design

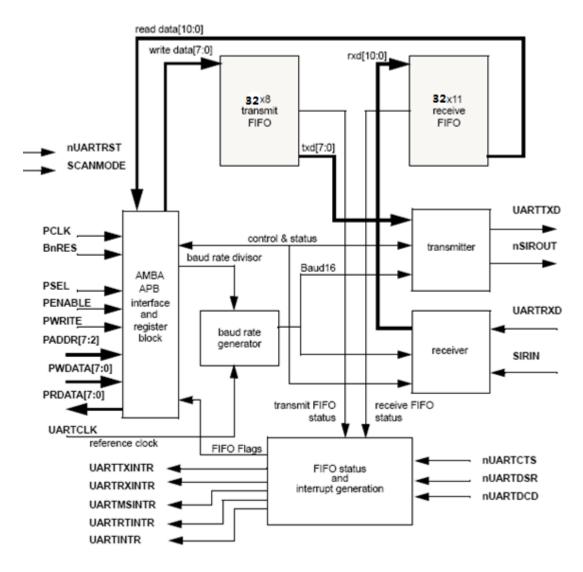

### 5.3.1 Block diagram

Note: test logic not represented for clarity

#### 5.3.2 Block details

#### **AMBA APB interface**

The AMBA APB interface generates read and write decodes for accesses to status/control registers and transmit/receive FIFO memories. The AMBA APB is a local secondary bus which provides a low-power extension to the higher bandwidth *Advanced High-performance Bus* (AHB), or *Advanced System Bus* (ASB), within the AMBA system hierarchy. The AMBA APB groups narrow-bus peripherals to avoid loading the system bus and provides an interface using memory mapped registers which are accessed under programmed control.

#### **Register block**

The register block stores data to be written or read across the AMBA APB interface.

#### **Baud rate generator**

The baud rate generator contains free-running counters which generate the baud rate x16 clocks, Baud16, and the IrLPBaud16 signal. Baud16 provides timing information for UART transmit and receive control. Baud16 is a stream of pulses with a width of one UARTCLK clock period and a frequency of sixteen times the baud rate. IrLPBaud16provides timing information to generate the pulse width of the IrDA encoded transmit bit stream when in low-power mode.

#### **Transmit FIFO**

The transmit FIFO is an 8-bit wide, 32-byte depth, first-in, first-out memory buffer. CPU data written across the APB interface is stored in the FIFO until read out by the transmit logic. The transmit FIFO can be disabled to act as a one-byte holding register.

#### **Receive FIFO**

The receive FIFO is an 11-bit wide, 32-byte depth, first-in, first-out memory buffer. Received data, and corresponding error bits, are stored in the receive FIFO by the receive logic until read out by the CPU across the APB interface. The FIFO can be disabled to act as a one-byte holding register.

#### **Transmit logic**

The transmit logic performs parallel-to-serial conversion on the data read from the transmit FIFO. Control logic outputs the serial bit streams beginning with a start bit, data bits, least significant bit (LSB) first, followed by parity bit, and then stop bits according to the programmed configuration in control registers.

#### **Receive logic**

The receive logic performs serial-to-parallel conversion on the received bit stream after a valid start pulse has been detected. Parity, frame error checking and line break detection are also performed, and the data with associated parity, framing and break error bits is written to the receive FIFO.

#### Interrupt generation logic

Four individual maskable active HIGH interrupts can be generated by the UART, and a combined interrupt output will be generated as an OR function of the individual interrupt requests. The single combined interrupt may be used with a system interrupt controller, it allows use of modular device drivers which will always know where to find the interrupt source control register bits.

The individual interrupt requests could also be used with a system interrupt controller that provides masking for the outputs of each peripheral. In this way, a global interrupt service routine would be able to read the entire set of sources from one wide register in the system interrupt controller. This is attractive because the time to read from the peripheral registers is significant in a real-time system.

The peripheral supports both the above methods, since the overhead is small. The transmit and receive dataflow interrupts, UARTRXINTR and UARTTXINTR, are separated from the status interrupts so that they may be used

independently by a Direct Memory Access (DMA) controller.

#### Synchronizing registers and logic

The UART supports both asynchronous and synchronous operation of the clocks, PCLK and UARTCLK. Synchronization registers and handshaking logic have been implemented, and are active at all times. This has a minimal impact on performance or area. Synchronization of control signals is performed on both directions of data flow, that is from the PCLK to the UARTCLK domain and vice versa.

### **5.4 Register description**

### 5.4.1 Register and memory mapping summary table

| Name | Offset | Width | Access | Description                       |

|------|--------|-------|--------|-----------------------------------|

| RBR  | 0x00   | 8     | RO     | Receiver Buffer Register          |

| THR  | 0x00   | 8     | WO     | Transmitter Holding Register      |

| DLL  | 0x00   | 8     | R/W    | Divisor Latch LSB                 |

| IER  | 0x04   | 4     | W/R    | Interrupt Enable Register         |

| DLM  | 0x04   | 8     | R/W    | Divisor Latch MSB                 |

| IIR  | 0x08   | 8     | RO     | Interrupt Identification Register |

| FCR  | 0x08   | 8     | WO     | FIFO Control Register             |

| LCR  | 0x0C   | 8     | R/W    | Line Control Register             |

| MCR  | 0x10   | 6     | R/W    | Modem Control Register            |

| LSR  | 0x14   | 8     | R      | Line Status Register              |

| MSR  | 0x18   | 8     | R      | Modem Status Register             |

| SCR  | 0x1c   | 8     | R/W    | Scratch Register                  |

### 5.4.2 Register

#### Receiver Buffer Register – RBR (offset 00h)

| Bit | Name    | Туре | Default Description |                                                                   |

|-----|---------|------|---------------------|-------------------------------------------------------------------|

|     |         |      |                     | Accessed only if LCR[7]=0                                         |

| 7:0 | RX_DATA | R    | 0x00                | If FIFOs Enable (FIFO Mode): RBR indicates Receiver FIFO          |

|     |         |      |                     | If FIFOs Disable (Non-FIFO Mode): RBR indicates a 8-bit register. |

#### Transmitter Holding Register - THR(offset 00h)

| Bit | Name        | Туре | Default | Description                                                      |

|-----|-------------|------|---------|------------------------------------------------------------------|

|     |             |      |         | Accessed only if LCR[7]=0                                        |

| 7:0 | 7:0 TX_DATA | W    | 0x00    | If FIFO Enable (FIFO Mode): RBR indicates Transmitter FIFO,      |

|     |             |      |         | If FIFO Disable (Non-FIFO Mode): RBR indicates a 8-bit register. |

### Divisor Latch LSB -DLL(offset 00h)

| Bit | Name | Туре | default | Description                                                     |

|-----|------|------|---------|-----------------------------------------------------------------|

| 7.0 |      |      |         | Accessed only if LCR[7] = 1                                     |

|     | DII  | R/W  | 00      | This register is programmed for baud rate generator. Divisor    |

| 7:0 | DLL  | K/VV | 00      | latch MSB and LSB are concatenated to form 16 bit divisor value |

|     |      |      |         | signal                                                          |

### Interrupt Enable Register – IER(offset 04h)

| Bit | Name   | Туре    | default | Description                                          |

|-----|--------|---------|---------|------------------------------------------------------|

| 7:4 | REV    | R       | 0       | These bits are always cleared (Reserved bits).       |

| 3   | EMSI   | R/W     | 0       | "1": Enable Modem Status Interrupt (EMSI)            |

| 3   | EIVISI | K/VV    | 0       | "0": Disable EMSI                                    |

| 2   | EDI CI | R/W     | 0       | "1": Enable Receive Line Status Interrupt (ERLSI)    |

| 2   | ERLSI  |         |         | "0": Disable ERLSI                                   |

| 1   | ETI    | R/W     | 0       | "1": Enable THR Empty Interrupt (ETI)                |

| 1   | E11    |         |         | "0": Disable ETI                                     |

| 0   | - FDD1 | D // // | 0       | "1": Enable Received Data Available Interrupt (ERDI) |

| U   | ERDI   | R/W     |         | "0": Disable ERDI                                    |

#### Divisor Latch MSB -DLM(offset 04h)

| Bit | Name    | Туре | default | Description                                                     |

|-----|---------|------|---------|-----------------------------------------------------------------|

|     | 7:0 DLM | R/W  | 00      | Accessed only if LCR[7] = 1                                     |

| 7.0 |         |      |         | This register is programmed for baud rate generator. Divisor    |

| 7:0 |         |      |         | latch MSB and LSB are concatenated to form 16 bit divisor value |

|     |         |      |         | signal                                                          |

#### Interrupt Identification Register -IIR(offset 08h)

| Bit | Name    | Туре | Default | Description                                          |

|-----|---------|------|---------|------------------------------------------------------|

| 7:4 | REV     | R    | 0       | Reserved                                             |

|     |         |      |         | Interrupt ID.                                        |

|     |         |      |         | 011 Receiver line status 010 Receiver data available |

| 3:1 | INT ID  | D    | 3'b000  |                                                      |

| 3.1 | INT_ID  | R    | 3 0000  | 110 Character time-out indication                    |

|     |         |      |         | 001 THR empty                                        |

|     |         |      |         | 000 Idle status                                      |

|     | INIT CT |      | 4/1-4   | 0= interrupt is pending;                             |

| 0   | INT_ST  | R    | 1'b1    | 1= no interrupt is pending                           |

#### FIFO Control Register -FCR(offset 08h)

|     | •              | -    | -       |                                                            |

|-----|----------------|------|---------|------------------------------------------------------------|

| Bit | Name           | Туре | Default | Description                                                |

|     |                |      |         | Indicate the trigger level for the receiver FIFO interrupt |

| 7.6 | 7:6 RX_TRIGGER | w    | 2'b00   | 00 1 character in the FIFO                                 |

| 7.0 |                | VV   | 2 000   | 01 FIFO 1/4 full                                           |

|     |                |      |         | 10 FIFO 1/2 full                                           |

|     |             |     |       | 11 FIFO 1/8 less full                                               |

|-----|-------------|-----|-------|---------------------------------------------------------------------|

|     |             |     |       | Indicate the trigger level for the transmit FIFO interrupt.         |

|     |             |     |       | 00 Empty FIFO                                                       |

| 5:4 | TX_TRIGGER  | W   | 2'b00 | 01 2 character in the FIFO                                          |

|     |             |     |       | 10 FIFO 1/4 full                                                    |

|     |             |     |       | 11 FIFO 1/2 full                                                    |

|     |             | 147 | 0     | 0= TXRDYN,RXRDYN signal work in DMA mode 0                          |

| 3   | DMA_MOD     | W   |       | 1= TXRDYN,RXRDYN signal work in DMA mode 1                          |

|     | TV FIFO DCT | 147 | 0     | When this bit is set, transmitter FIFO reset. The logic one         |

| 2   | TX_FIFO_RST | W   |       | written to this bit is self clearing.                               |

| 4   | DV FIEO DCT | 147 | 0     | When this bit is set, receiver FIFO reset. The logic one written to |

| 1   | RX_FIFO_RST | W   |       | this bit is self clearing                                           |

|     | FIFO. FNI   | 147 | V 0   | 1= Enables transmitter and receiver FIFO                            |

| 0   | FIFO_EN     | W   |       | 0= Disable and clear the Tx/Rx FIFO                                 |

### Line Control Register -LCR(offset 0Ch)

| Bit | Name         | Туре   | Default | Description                                                   |

|-----|--------------|--------|---------|---------------------------------------------------------------|

|     | 7 DLA R      |        |         | Divisor Registers Access.                                     |

| 7   |              | R/W    | 0       | Bit 7 must be set to access the divisor latches(LSB&MSB) of   |

| '   |              | K/VV   | 0       | baud generator.                                               |

|     |              |        |         | Bit 7 must be cleared to access buffers(THR or IER)           |

| 6   | -            |        | 0       | Reserved                                                      |

|     |              |        |         | Stick Parity Bit .                                            |

| 5   | 5 SP         | D /\\/ | 0       | If bits[5:3] are 111, parity bit is checked as 0.             |

| 3   | 34           | R/W    | 0       | If bits[5:3] are 101, parity bit is checked as 1.             |

|     |              |        |         | If bit5 is 0, stick parity is disabled                        |

|     |              |        |         | Even Parity Enable                                            |

| 4   | EVENARITY    | R/W    | 0       | 1: even parity is selected.                                   |

|     |              |        |         | 0: odd parity is selected.                                    |

|     |              |        |         | Parity Enable Bit                                             |

| 3   | PARITY_EN    | R/W    | 0       | 1: parity check enable                                        |

|     |              |        |         | 0: parity check disable                                       |

|     |              |        |         | Stop Bits                                                     |

|     |              |        |         | 0= one stop bit after data bits                               |

|     |              | R/W    |         | 1=                                                            |

| 2   | STOP_BIT_SEL |        | 0       | 1.5 stop bit for a 5-bit data character,                      |

| 2   | STOP_BIT_SEE | IN/ VV | 0       | OR 2 stop bits for a 6-,7-,or 8-bit character.                |

|     |              |        |         |                                                               |

|     |              |        |         | The receiver checks the first stop bit only regardless of the |

|     |              |        |         | number of stop bits selected                                  |

|     |              |        |         | Word Length                                                   |

| 1:0 | WORD LEN     | R/W    | 2'b00   | 00: 5 bits                                                    |

| 1.0 | WORD_LEN F   | 11/ VV |         | 01: 6 bits                                                    |

|     |              |        |         | 10: 7 bits                                                    |

|  |  | 11: 8 bits  |

|--|--|-------------|

|  |  | 1 11. 0 010 |

### Modem Control Register – MCR(offset 10h)

| Bit | Name | Туре   | default | Description                                                     |

|-----|------|--------|---------|-----------------------------------------------------------------|

| 7:6 | RSVD | 00     | 00      | These bits are always cleared (Reserved bits).                  |

|     |      |        |         | Auto Flow control Enable                                        |

| 5   | AFE  | R/W    | 0       | "1": Enable AFE                                                 |

|     |      |        |         | "0": Disable AFE                                                |

|     |      |        | , 0     | Loop Back Mode                                                  |

| 4   | LOOD | D /\A/ |         | 1: enable local loop back feature for diagnostic testing of the |

| 4   | LOOP | R/W    | 0       | UART.                                                           |

|     |      |        |         | 0: disable local loop back feature                              |

| 3:0 | -    | -      | 3'b00   | Reserved                                                        |

### Line Status Register – LSR(offset 14h)

| Bit | Name       | Туре | Default | Description                                                     |

|-----|------------|------|---------|-----------------------------------------------------------------|

|     |            |      |         | Error Flag                                                      |

|     |            |      |         | In No-FIFO mode, LSR[7] is always 0.                            |

| 7   | 7 ERR_FLAG | R    | 0       | In FIFO mode, LSR[7] is 1 when there is at least one parity,    |

|     |            |      |         | framing or break error in the FIFO.                             |

|     |            |      |         | It is cleared after LSR is read                                 |

|     |            |      |         | Transmitter Empty Indicator                                     |

| 6   | 6 T_EMT    | R    | 1       | TEMT is set when the both THR and TSR are empty.                |

| "   | ''         |      | *       | TEMT is cleared when either THR or TSR contains a data          |

|     |            |      |         | character.                                                      |

|     |            |      |         | Transmitter Holding Register Empty Indicator                    |

| 5   | T_HRE      | R    | 1       | THRE is set when the THR is empty.                              |

|     |            |      |         | THRE is set when the THR contains at least a data character     |

|     |            |      | 0       | Break Interrupt Indicator                                       |

|     |            | R    |         | When BI is set, it indicates that received data input was held  |

|     |            |      |         | in the low state for longer than the full transmission time.    |

| 4   | BI         |      |         | BI is cleared every time the CPU reads the contents of the LSR. |

|     |            |      |         | In FIFO mode it indicates the BI status of the character on     |

|     |            |      |         | the top of the FIFO.                                            |

|     |            |      |         | Full Transmission Time = Start + Data + Parity + Stop bits      |

|     |            |      |         | Framing Error indicator                                         |

|     |            |      |         | When FE is set it indicates that received character does not    |

| 3   | FE         | R    | 0       | have a valid stop bit.                                          |

|     | -          |      |         | FE is cleared every time CPU reads thecontents of the LSR.      |

|     |            |      |         | In FIFO mode it indicates the FE status of the character on top |

|     |            |      |         | of the FIFO.                                                    |

|     |            |      |         | Parity Error                                                    |

| 2   | PE         | R    | 0       | When PE is set it indicates that parity of received character   |

|     |            |      |         | does not match the parity selected in LCR[4].                   |

| 1 | OE | R | 0 | PE is cleared every time the CPU reads the contents of LSR. In FIFO mode it indicates the parity of the character on the top of the FIFO  Overrun Error Indicator  When OE is set, it indicates that before the character in the reg RBR was read, it was overwritten by the next character transferred into the register.  OE is cleared every time the CPU reads the contents of the LSR. In FIFO mode, overrun error occurs only after the FIFO is full and the next character has been completely received in the shift register.  Note: The character in the shift register is overwritten, but it is not transferred to the FIFO. |

|---|----|---|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 | DR | R | 0 | Data Ready Indicator  DR is set when the complete incoming character is received and transferred into RBR or the FIFO.  It is cleared by reading all data in the FIFO or RBR.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

### Modem Status Register - MSR(offset 18)

| Bit | Name | Туре | Default | Description                                                     |

|-----|------|------|---------|-----------------------------------------------------------------|

|     |      |      |         | Data Carrier Detect                                             |

| 7   | DCD  | R    | 0       | When the UART is in the diagnostic test mode(LOOP),this bit is  |

|     |      |      |         | equal to the MCR bit 3(OUT2).                                   |

|     |      |      |         | Ring Indicator                                                  |

| 6   | RI   | R    | 0       | When the UART is in diagnostic test mode, this bit is equal to  |

|     |      |      |         | MCR bit 2(RI).                                                  |

|     |      |      |         | Data Send Request                                               |

| 5   | DSR  | R    | 0       | When the UART is in diagnostic test node, this bit is equal to  |

|     |      |      |         | MCR bit 0(DSR).                                                 |

|     |      |      |         | Clear To Send                                                   |

| 4   | CTS  | R    | 0       | When UART is in diagnostic test mode, this bit is equal to MCR  |

|     |      |      |         | bit1                                                            |

|     |      |      |         | DCD Changed                                                     |

| 3   | DCD  | R    | 0       | It indicates that dcd has changed since it was last read by the |

|     |      |      |         | CPU.                                                            |

|     |      |      |         | RI Rising Edge                                                  |

| 2   | TERI | R    | 0       | When TERI is set and the modem status interrupt is enabled, a   |

|     |      |      |         | modem status interrupt is generated                             |

|     |      |      |         | DSR Changed                                                     |

| 1   | DSR  | R    | 0       | It indicates that DSR has changed states since last time it was |

|     |      |      |         | read by the CPU.                                                |

|     |      |      |         | CTS Changed                                                     |

| 0   | CTS  | R    | 0       | It indicates the CTS has changed states since last time it was  |

|     |      |      |         | Read by the CPU.                                                |

#### Scratch Register -SCR(offset 1Ch)

| Bit | Name    | Туре | default | Description                                            |

|-----|---------|------|---------|--------------------------------------------------------|

| 7:0 | TMP_VAL | R/W  | FF      | User temporary data                                    |

|     |         |      |         | This register can be used by user as a temporary value |

### 5.4.3 Configuration program flow

Below following is only an example for configure UART to receive and transmitter data:

#### **Example for Receiver Program Flow (Interrupt FIFO Mode):**

- 1. Program the baud rate (Write FCR[7]=1 first, then program the DLL and DLM).

- 2. Write the LCR to program Line Control Information (word length, parity, stop and etc.)

- 3. Write the FCR to enable FIFO and program the Rx Trigger Level.

- 4. Write the Interrupt Enable Register to enable the corresponding interrupt

- 5. Wait for receive data from Serial Line

- 6. If interrupt, read the Interrupt Identification Register to judge the error interrupt or Rx Trigger Level interrupt. If error interrupt, there have error on Receive Line Data

- 7. If Rx Trigger Level interrupt, MCU transfer (read) the data from Rx FIFO (Read RBR)

- 8. If character timeout interrupt, MCU read remain data in the Rx FIFO till empty (Read Line Status Register to confirm the Rx FIFO empty or not, LSR[0]).

#### **Example for Transmitter Data Program Flow (Interrupt FIFO mode)**

- 1. Program the baud rate.

- 2. Write the LCR to program line control information

- 3. Write the FCR to enable FIFO and program Tx trigger level.

- 4. Write the IER to enable interrupt.

- 5. Wait for interrupt

- 6. If THRE interrupt, then write transmitter data into FIFO (Write THR)

- 7. Then go to 5, wait for interrupt and write Tx data into FIFO.

### 6 SSP

The SSP is a master interface that enables synchronous serial communication witch slave peripherals.

### 6.1 Overview

The SSP performs serial-to-parallel conversion on data received from a peripheral device. The CPU accesses data, control, and status information through the AMBA APB interface. The transmit and receive paths are buffered with internal FIFO memories enabling up to 128 8-bit values to be stored independently in both transmit and receive modes. Serial data is transmitted on **SSPTXD** and received on **SSPRXD**.

The SSP includes a programmable bit rate clock divider and prescaler to generate the serial output clock, **SSPCLKOUT**, from the input clock, **SSPCLK**. Bit rates are supported up to 24MHz, subject to choice of frequency for **SSPCLK**, and the maximum bit rate is determined by peripheral devices.

You can use the control registers SSPCR0 to program the SSP operating mode, frame format, and size.

#### 6.2 Feature list

- Master operation.

- > Programmable clock bit rate and prescale. Bus speed varies from 500kHz to 24Mhz.

- > Separate transmit and receive FIFOs with 8 bits wide, 128 locations depth.

- Independent masking of transmit FIFO, receive FIFO, and receive overrun interrupts.

- Programmable data frame size from 4 to 8 bits.

### 6.3 Functional description

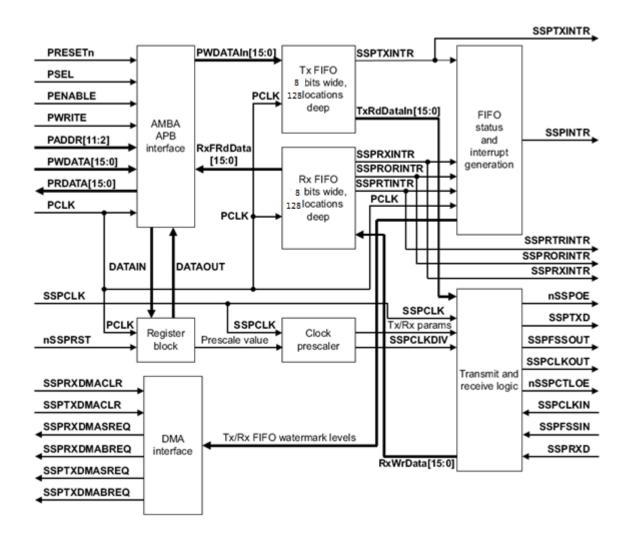

### 6.3.1 Block diagram

#### 6.3.2 Block details

#### **AMBA APB interface**

The AMBA APB interface generates read and write decodes for accesses to status and control registers, and transmit and receive FIFO memories. The AMBA APB is a local secondary bus that provides a low-power extension to the higher bandwidth AMBA *Advanced High-performance Bus* (AHB) within the AMBA system hierarchy. The AMBA APB groups narrow-bus peripherals to avoid loading the system bus and provides an interface using memory-mapped registers, that are accessed under programmed control.

#### Register block

The register block stores data written, or to be read, across the AMBA APB interface.

#### **Clock prescaler**

When configured as a master, an internal prescaler, comprising two free-running reloadable serially linked counters, provides the serial output clock SSPCLKOUT. You can program the clock prescaler, using the SSPCPSR register, to divide SSPCLK by a factor of 2-254 in steps of two. By not utilizing the least significant bit of the SSPCPSR register, division by an odd number is not possible and this ensures that a symmetrical, equal mark space ratio, clock is generated. The output of the prescaler is divided again by a factor of 1-256, by

programming the SSPCRO control register, to give the final master output clock SSPCLKOUT.

#### **Transmit FIFO**

The common transmit FIFO is a 8-bit wide, 128-locations deep, *First-In*, *First-Out* (FIFO) memory buffer. CPU data written across the AMBA APB interface are stored in the buffer until read out by the transmit logic. When configured as a master, parallel data is written into the transmit FIFO prior to serial conversion, and transmission to the attached slave, through the SSPTXD pin.

#### **Receive FIFO**

The common receive FIFO is a 8-bit wide, 128-locations deep, first-in, first-out memory buffer. Received data from the serial interface are stored in the buffer until read out by the CPU across the AMBA APB interface. When configured as a master, serial data received through the SSPRXD pin is registered prior to parallel loading into the attached slave-receive FIFO respectively.

#### Transmit and receive logic

When configured as a master, the clock to the attached slaves is derived from a divided-down version of SSPCLK through the prescaler operations that previous sections describe. The master transmit logic successively reads a value from its transmit FIFO and performs parallel to serial conversion on it. Then, the serial data stream and frame control signal, synchronized to SSPCLKOUT, are output through the SSPTXD pin to the attached slaves. The master receive logic performs serial to parallel conversion on the incoming synchronous SSPRXD data stream, extracting and storing values into its receive FIFO, for subsequent reading through the APB interface.

#### Interrupt generation logic

The SSP generates four individual maskable, active-HIGH interrupts. A combined interrupt output is also generated as an OR function of the individual interrupt requests. You can use the single combined interrupt with a system interrupt controller that provides another level of masking on a per-peripheral basis. This enables use of modular device drivers that always know where to find the interrupt source control register bits. You can also use the individual interrupt requests with a system interrupt controller that provides masking for the outputs of each peripheral. In this way, a global interrupt controller service routine can read the entire set of sources from one wide register in the system interrupt controller. This is attractive where the time to read from the peripheral registers is significant compared to the CPU clock speed in a real-time system.

The peripheral supports both the above methods. The transmit and receive dynamic data-flow interrupts, SSPTXINTR and SSPRXINTR, are separated from the status interrupts so that data can be read or written in response to the FIFO trigger levels.

#### Synchronizing registers and logic

The SSP supports both asynchronous and synchronous operation of the clocks, PCLK and SSPCLK. Synchronization registers and handshaking logic have been implemented, and are active at all times. This has a minimal impact on performance or area. Synchronization of control signals is performed on both directions of data flow, that is:

- from the PCLK to the SSPCLK domain

- from the SSPCLK to the PCLK domain.

### 6.3.3 SSP operation

#### **Enable SSP operation**

You can either prime the transmit FIFO, by writing up to 128 8-bit values when the SSP is disabled, or permit the transmit FIFO service request to interrupt the CPU. Once enabled, transmission or reception of data begins on the transmit, **SSPTXD**, and receive, **SSPRXD**, pins.

#### **Clock ratios**

There is a constraint on the ratio of the frequencies of **PCLK** to **SSPCLK**. The frequency of **SSPCLK** must be less than or equal to that of **PCLK**. This ensures that control signals from the **SSPCLK** domain to the **PCLK** domain are guaranteed to get synchronized before one frame duration:

FSSPCLK <= FPCLK.

The setup and hold times on **SSPRXD**, with reference to SSPCLKIN, must be more conservative to ensure that it is at the right value when the actual sampling occurs within the SSPMS. To ensure correct device operation, **SSPCLK** must be at least 12 times faster than the maximum expected frequency of SSPCLKIN.

The frequency selected for SSPCLK must accommodate the desired range of bit clock rates. The ratio of minimum SSPCLK frequency to SSPCLKOUT maximum frequency for the master mode, it is two.

To generate a maximum bit rate of 24Mbps in the master mode, the frequency of **SSPCLK** must be at least 48MHz. With an **SSPCLK** frequency of 48MHz, the SSPCPSR register must be programmed with a value of 2, and the SCR[7:0] field in the SSPCR0 register must be programmed with a value of 0.

The minimum frequency of **SSPCLK** is governed by the following equations, both of which must be satisfied: FSSPCLK(min) => 2 x FSSPCLKOUT(max), for master mode

The maximum frequency of **SSPCLK** is governed by the following equations, both of which must be satisfied: FSSPCLK(max) <= 254 x 256 x FSSPCLKOUT(min), for master mode

#### **Programming the SSPCRO Control Register**

The SSPCR0 register is used to:

- program the serial clock rate

- select one of the three protocols

- select the data word size, where applicable

The *Serial Clock Rate* (SCR) value, in conjunction with the SSPCPSR clock prescale divisor value, CPSDVSR, is used to derive the SSP transmit and receive bit rate from the external **SSPCLK**. The frame format is programmed through the FRF bits, and the data word size through the DSS bits. Bit phase and polarity, applicable to Motorola SPI format only, are programmed through the SPH and SPO bits.

To configure the SSP as a master, clear the SSPCRO register master or slave selection bit, MS, to 0. This is the default value on reset. To enable the operation of the SSP, set the *Synchronous Serial Port Enable* (SSE) bit to 1.

#### Bit rate generation

The serial bit rate is derived by dividing down the input clock, **SSPCLK**. The clock is first divided by an even prescale value CPSDVSR in the range 2-254, and is programmed in SSPCPSR. The clock is divided again by a value in the range 1-256, that is 1 + SCR, where SCR is the value programmed in SSPCRO. The following equation defines the frequency of the output signal bit clock, **SSPCLKOUT**:

$$F_{\text{SSPCLKOUT}} = \frac{F_{SSPCLK}}{CPSDVR \times (1 + SCR)}$$

For example, if SSPCLK is 48MHz, and CPSDVSR = 2, then SSPCLKOUT has a frequency range from 93.75kHz-24MHz.

#### Frame format

Each data frame is between 4-8 bits long, depending on the size of data programmed, and is transmitted starting with the MSB. You can select the following basic frame types:

- Texas Instruments synchronous serial

- Motorola SPI

- National Semiconductor Microwire.

For all formats, the serial clock, **SSPCLKOUT**, is held inactive while the SSP is idle, and transitions at the programmed frequency only during active transmission or reception of data. The idle state of **SSPCLKOUT** is utilized to provide a receive timeout indication that occurs when the receive FIFO still contains data after a timeout period.

For Motorola SPI and National Semiconductor Microwire frame formats, the serial frame, **SSPFSSOUT**, pin is active-LOW, and is asserted, pulled-down, during the entire transmission of the frame.

For Texas Instruments synchronous serial frame format, the **SSPFSSOUT** pin is pulsed for one serial clock period, starting at its rising edge, prior to the transmission of each frame. For this frame format, both the SSP and the off-chip slave device drive their output data on the rising edge of **SSPCLKOUT**, and latch data from the other device on the falling edge.

Unlike the full-duplex transmission of the other two frame formats, the National Semiconductor Microwire format uses a special master-slave messaging technique, that operates at half-duplex. In this mode, when a frame begins, an 8-bit control message is transmitted to the off-chip slave. During this transmit, the SSP receives no incoming data. After the message has been sent, the off-chip slave decodes it and, after waiting one serial clock after the last bit of the 8-bit control message has been sent, responds with the requested data.

#### Motorola SPI frame format

The Motorola SPI interface is a four-wire interface where the **SSPFSSOUT** signal behaves as a slave select. The main feature of the Motorola SPI format is that you can program the inactive state and phase of the **SSPCLKOUT** signal using the SPO and SPH bits of the SSPSCRO control register.

#### SPO, clock polarity

When the SPO clock polarity control bit is LOW, it produces a steady state LOW value on the **SSPCLKOUT** pin. If the SPO clock polarity control bit is HIGH, a steady state HIGH value is placed on the **SSPCLKOUT** pin when data is not being transferred.

#### SPH, clock phase

The SPH control bit selects the clock edge that captures data and enables it to change state. It has the most impact on the first bit transmitted by either permitting or not permitting a clock transition before the first data capture edge.

When the SPH phase control bit is LOW, data is captured on the first clock edge transition.

When the SPH clock phase control bit is HIGH, data is captured on the second clock edge transition.

## **6.4 Register**

## 6.4.1 Register summary table

| Name    | Offset | Туре | Reset  | Width | Description                          |

|---------|--------|------|--------|-------|--------------------------------------|

| SSPCR0  | 0x00   | RW   | 0x0000 | 16    | Control register 0                   |

| SSPDR   | 0x08   | RW   | 0x00   | 8     | Data register                        |

| SSPSR   | 0x0c   | RO   | 0x03   | 5     | Status register                      |

| SSPCPSR | 0x10   | RW   | 0x00   | 8     | Clock prescale register              |

| SSPIMSC | 0x14   | RW   | 0x00   | 4     | Interrupt mask set or clear register |

| SSPRIS  | 0x18   | RO   | 0x08   | 4     | Raw interrupt status register        |

| SSPMIS  | 0x1c   | RO   | 0x00   | 4     | Masked interrupt status register     |

| SSPICR  | 0x20   | WO   | 0x00   | 2     | Interrupt clear register             |

## 6.4.2 Register description

#### Control register -SSPCR (offset 00'h)

| Bits   | Name | Function                                                                          |  |  |

|--------|------|-----------------------------------------------------------------------------------|--|--|

|        |      | Serial clock rate. The value SCR is used to generate the transmit and receive bit |  |  |

|        |      | rate of the SSP. The bit rate is:                                                 |  |  |

| [15:8] | SCR  | $\frac{F_{SSPCLK}}{CPSDVR \times (1 + SCR)}$                                      |  |  |

|        |      | where CPSDVSR is an even value from 2-254, SCR is a value from 0-255.             |  |  |

| [7]    | SPH  | SSP_CLK phase, applicable to Motorola SPI frame format only.                      |  |  |

| [6]    | SPO  | SSP_CLK polarity, applicable to Motorola SPI frame format only.                   |  |  |

|        |      | Frame format:                                                                     |  |  |

|        |      | 00 Motorola SPI frame format.                                                     |  |  |

| [5:4]  | FRF  | 01 TI synchronous serial frame format.                                            |  |  |

|        |      | 10 National Microwire frame format.                                               |  |  |

|        |      | 11 Reserved.                                                                      |  |  |

| [3:0]  | DSS  | Data Size Select:                                                                 |  |  |

| 0000 Reserved.   |

|------------------|

| 0001 Reserved.   |

| 0010 Reserved.   |

| 0011 4-bit data. |

| 0100 5-bit data. |

| 0101 6-bit data. |

| 0110 7-bit data. |

| 0111 8-bit data. |

| Other, Reserved. |

#### Data register -SSPDR (offset 08'h)

| Bits   | Name | Function                                               |  |  |

|--------|------|--------------------------------------------------------|--|--|

| [45.0] | DATA | Transmit/Receive FIFO:                                 |  |  |

|        |      | For a data size which is less than 16 bits.            |  |  |

| [15:0] |      | Unused bits at the top are ignored by transmit logic.  |  |  |

|        |      | Data is automatically right-justifies by receive logic |  |  |

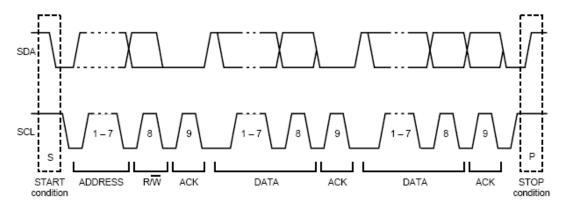

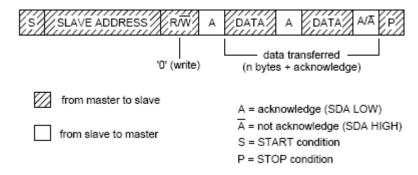

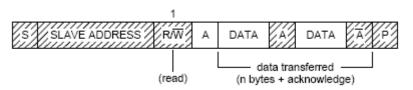

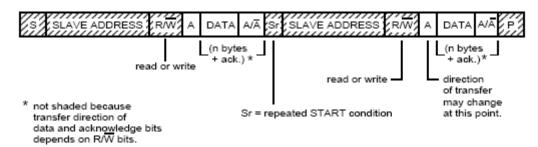

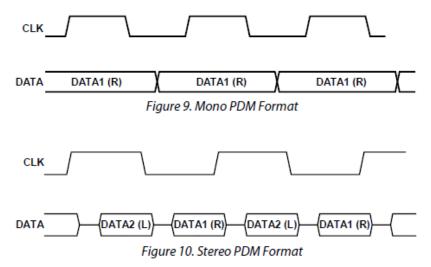

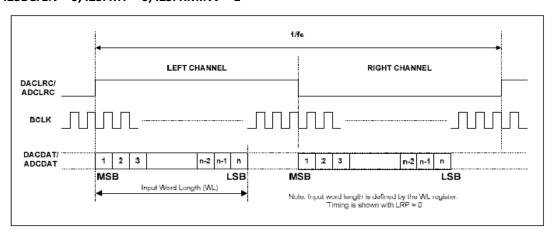

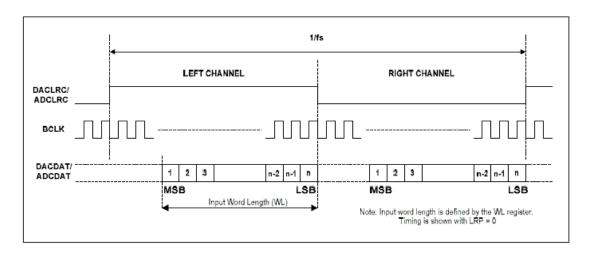

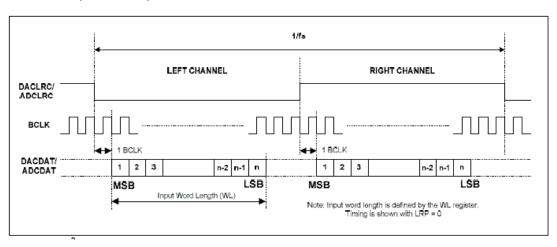

### Status register -SSPSR (offset 0C'h)