# **Bi-CMOS IC**

# Low power consumption and highefficiency Step-down Switching Regulator

# ON Semiconductor®

http://onsemi.com

SOIC10

### Overview

LV5980MD is 1ch DCDC converter with built-in power Pch MOSFET.

The recommended operating range is 4.5V to 23V.

The maximum current is 3A. The operating current is about  $63\mu A$ , and low power consumption is achieved.

# **Features and Functions**

- 1ch SBD rectification DCDC converter IC with built-in power Pch MOSFET

- Typical value of light load mode current is 63µA

- 4.5V to 23V Operating input voltage range

- 100mΩ High-side switch

- Output voltage adjustable to 1.235V

- The oscillatory frequency is 370kHz

- ON/OFF Function

- built-in OCP circuit with P-by-P method

- When P-by-P is generated continuously, it shifts to the HICCUP operation

- External capacitor Soft-start

- Under voltage lock-out, thermal shutdown

# DVD/Blu-ray™ drivers and HDD

• Office Equipment

- LCD monitors and TVs

- POS System

# **Applications**

- Set top boxes

- Point of load DC/DC converters

- White Goods

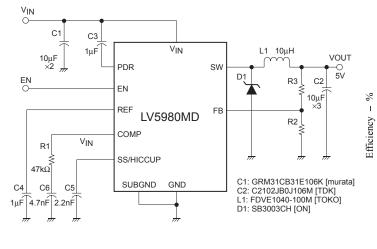

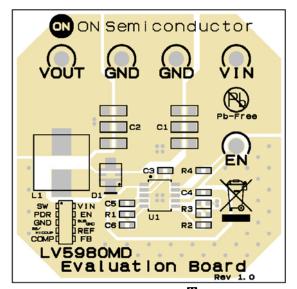

# **Application Circuit Example**

### ORDERING INFORMATION

See detailed ordering and shipping information on page 20 of this data sheet.

# **Specifications**

**Absolute Maximum Ratings** at Ta = 25°C

| Parameter                   | Symbol               | Conditions             | Ratings     | Unit |

|-----------------------------|----------------------|------------------------|-------------|------|

| Input voltage               | V <sub>IN</sub> max  |                        | 25          | V    |

| Allowable pin voltage       | V <sub>IN</sub> -SW  |                        | 30          | V    |

|                             | EN                   |                        | VIN         |      |

|                             | V <sub>IN</sub> -PDR |                        | 6           | V    |

|                             | REF                  |                        | 6           | V    |

|                             | SS/HICCUP            |                        | REF         | ٧    |

|                             | FB                   |                        | REF         | V    |

|                             | COMP                 |                        | REF         | ٧    |

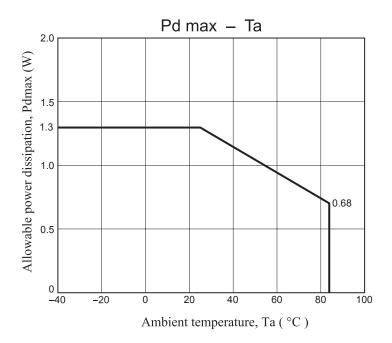

| Allowable power dissipation | Pd max               | Specified substrate *1 | 1.3         | W    |

| Operating temperature       | T <sub>OPR</sub>     |                        | -40 to +85  | °C   |

| Storage temperature         | T <sub>STG</sub>     |                        | -55 to +150 | °C   |

$<sup>^{\</sup>star}1$  Specified substrate: 50.0 mm  $\times$  50.0 mm  $\times$  1.6 mm, fiberglass epoxy printed circuit board, 4 layers

Caution 2) Even when the device is used within the range of absolute maximum ratings, as a result of continuous usage under high temperature, high current, high voltage, or drastic temperature change, the reliability of the IC may be degraded. Please contact us for the further details.

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

# **Recommended Operating Conditions** at Ta = 25°C

| Parameter           | Symbol          | Conditions | Ratings   | Unit |

|---------------------|-----------------|------------|-----------|------|

| Input voltage range | V <sub>IN</sub> |            | 4.5 to 23 | V    |

# Electrical Characteristics at Ta=25°C, VIN=15V

| Characteristic                      | Symbol               | Conditions                                              | Min.                    | Тур.                    | Max.                    | Units |

|-------------------------------------|----------------------|---------------------------------------------------------|-------------------------|-------------------------|-------------------------|-------|

| [Reference Voltage]                 |                      |                                                         |                         |                         |                         |       |

| Internal Reference Voltage          | $V_{REF}$            |                                                         | 1.210                   | 1.235                   | 1.260                   | V     |

| Pch Drive Voltage                   | $V_{PDR}$            | I <sub>OUT</sub> =0 ~ -5mA                              | V <sub>IN</sub><br>-5.5 | V <sub>IN</sub><br>-5.0 | V <sub>IN</sub><br>-4.5 | V     |

| [Saw Wave Oscillator]               |                      | •                                                       | •                       |                         |                         |       |

| Oscillatory Frequency               | Fosc                 |                                                         | 310                     | 370                     | 430                     | kHz   |

| [ON/OFF Circuit]                    | ·                    | •                                                       |                         |                         |                         |       |

| IC startup voltage (EN PIN)         | V <sub>CNT</sub> ON  |                                                         | 2.0                     |                         | V <sub>IN</sub>         | V     |

| Disable voltage (EN PIN)            | V <sub>CNT</sub> OFF |                                                         |                         |                         | 0.3                     | ٧     |

| [Soft Start Circuit]                |                      |                                                         |                         |                         |                         |       |

| Soft Start • Source Current         | I <sub>SS_SC</sub>   |                                                         | 1.2                     | 1.8                     | 2.4                     | uA    |

| Soft Start • Sink Current           | I <sub>SS_SK</sub>   | V <sub>IN</sub> = 3V, EN > 2V<br>V <sub>SS</sub> = 0.4V |                         | 300                     |                         | uA    |

| [UVLO Circuit]                      | -1                   | 1 - 33                                                  |                         | Į.                      |                         |       |

| UVLO Release Voltage                | V <sub>UVLON</sub>   | FB = COMP                                               | 3.3                     | 3.7                     | 4.1                     | V     |

| UVLO Lock Voltage                   | V <sub>UVLOF</sub>   | FB = COMP                                               | 3.02                    | 3.42                    | 3.82                    | V     |

| [Error Amplifier]                   | ·                    | •                                                       |                         |                         |                         |       |

| Input Bias Current                  | I <sub>EA_IN</sub>   |                                                         | -100                    | -10                     |                         | nA    |

| Error amplifier gain                | G <sub>EA</sub>      |                                                         | 100                     | 220                     | 380                     | uA/V  |

| Output Sink Current                 | I <sub>EA_OSK</sub>  | FB = 1.75V                                              | -30                     | -17                     | -8                      | uA    |

| Output Source Current               | I <sub>ES_OSC</sub>  | FB = 0.75V                                              | 8                       | 17                      | 30                      | uA    |

| [Over Current Limit Circuit]        |                      |                                                         |                         |                         |                         |       |

| Current Limit Peak                  | I <sub>CL</sub>      | *2 Test circuit                                         | 3.5                     | 4.7                     | 6.2                     | Α     |

| HICCUP Timer Start-up Cycle         | N <sub>CYC</sub>     |                                                         |                         | 15                      |                         | cycle |

| HICCUP Comparator Threshold Voltage | V <sub>tHIC</sub>    |                                                         |                         | 0.15                    |                         | V     |

| HICCUP Timer Discharge Current      | I <sub>HIC</sub>     |                                                         |                         | 0.25                    |                         | uA    |

Continued on next page.

Caution 1) Absolute maximum ratings represent the values which cannot be exceeded for any length of time.

| Continued from preceding page.         |                     |                     |      |      |      |       |

|----------------------------------------|---------------------|---------------------|------|------|------|-------|

| Characteristic                         | Symbol              | Conditions          | Min. | Тур. | Max. | Units |

| [PWM Comparator]                       |                     | •                   |      |      |      |       |

| Maximum On-Duty                        | D <sub>MAX</sub>    |                     | 94   |      |      | %     |

| [Output]                               |                     |                     |      |      |      |       |

| Output On Resistance                   | R <sub>ON</sub>     | Io = 0.5A           |      | 100  |      | mΩ    |

| [The entire device]                    | [The entire device] |                     |      |      |      |       |

| Standby current                        | I <sub>ccs</sub>    | EN < 0.3V           |      |      | 1    | uA    |

| Light Load Mode Consumption<br>Current | I <sub>SLEEP</sub>  | No switching        |      | 63   | 83   | uA    |

| Thermal Shutdown                       | TSD                 | *3 Design guarantee |      | 170  |      | ů     |

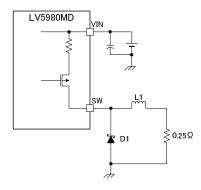

<sup>\*2</sup> Test circuit

\*3 Design guarantee: Signifies target value in design. These parameters are not tested in an independent IC.

# Pdmax - Ta

# Specified substrate

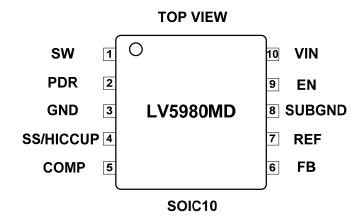

# **Pin Connections**

# **Pin Function Description**

| Pin | Pin Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | SW        | High-side Pch MOSFET drain Pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2   | PDR       | Pch MOSFET gate drive Voltage. The bypass capacitor is necessarily connected between this pin and Vin.                                                                                                                                                                                                                                                                                                                                                                            |

| 3   | GND       | Ground Pin. Ground pin voltage is reference voltage                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4   | SS/HICCUP | Capacitor connection pin for soft start and setting re-startup cycle in HICCUP mode. About 1.8uA current charges the soft start capacitor.                                                                                                                                                                                                                                                                                                                                        |

| 5   | COMP      | Error Amplifier Output Pin.  The phase compensation network is connected between GND pin and COMP pin.  Thanks to current-mode control, comp pin voltage would tell you the output current amplitude. Comp pin is connected internally to an Init.comparator which compares with 0.9V reference. If comp pin voltage is larger than 0.9V, IC operates in "continuous mode". If comp pin voltage is smaller than 0.9V, IC operates in "discontinuous mode (low consumption mode)". |

| 6   | FB        | Error amplifier reverse input pin. ICs make its voltage keep 1.235V. Output voltage is divided by external resistances and it across FB.                                                                                                                                                                                                                                                                                                                                          |

| 7   | REF       | Reference voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8   | SUBGND    | Short-circuited and use 3pin and 8pin as GND                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 9   | EN        | ON/OFF Pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 10  | VIN       | Supply voltage pin. It is observed by the UVLO function. When its voltage becomes 3.7V or more, ICs startup in soft start.                                                                                                                                                                                                                                                                                                                                                        |

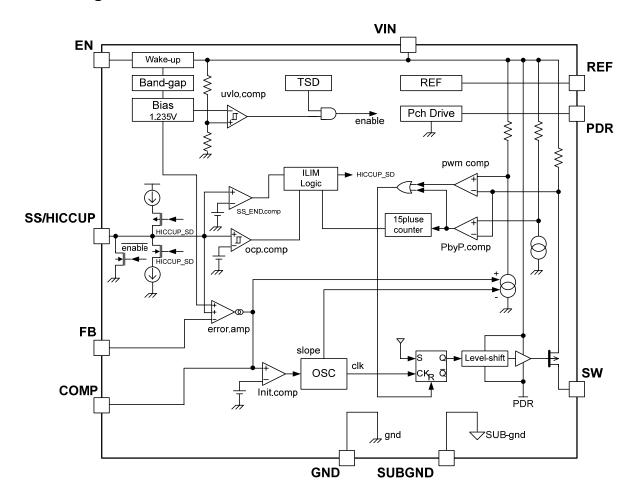

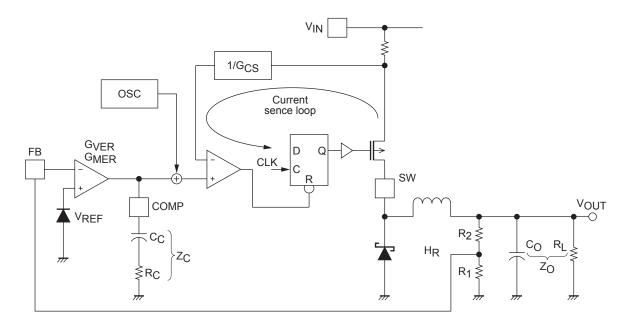

# **Block Diagram**

Pin Equivalent Circuit

| Pin No. | Pin Name  | Equivalent Circuit                       |

|---------|-----------|------------------------------------------|

| 1       | sw        | VIN<br>\$ 22m<br>SW                      |

| 2       | PDR       | 1.3M \$ 1.5M \$ 10k \$ PDR 10k \$ GND    |

| 3       | GND       | VIN ———————————————————————————————————— |

| 4       | SS/HICCUP | SS/HICCUP                                |

To the next page

From the previous page

| Pin No. | Pin Name | Equivalent Circuit                                |  |

|---------|----------|---------------------------------------------------|--|

| 5       | СОМР     | COMP \$1k                                         |  |

| 6       | FB       | VIN 10k 1k Tk |  |

| 7       | REF      | VIN — 10 — 10 — 10 — 10 — 10 — 10 — 10 — 1        |  |

| 8       | SUBGND   | SUBGND                                            |  |

To the next page

| Pin No. | Pin Name | Equivalent Circuit                       |  |

|---------|----------|------------------------------------------|--|

|         |          | VIN *                                    |  |

| 9       | EN       | EN 4.8M  GND                             |  |

| 10      | VIN      | VIN ———————————————————————————————————— |  |

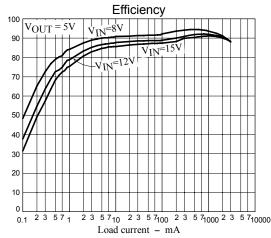

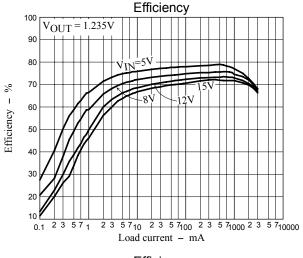

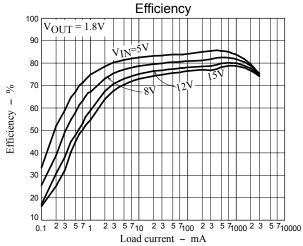

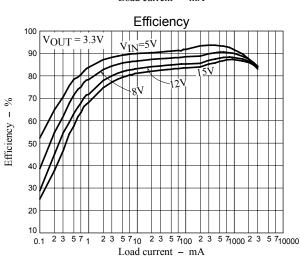

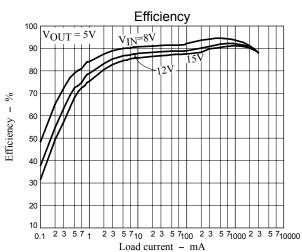

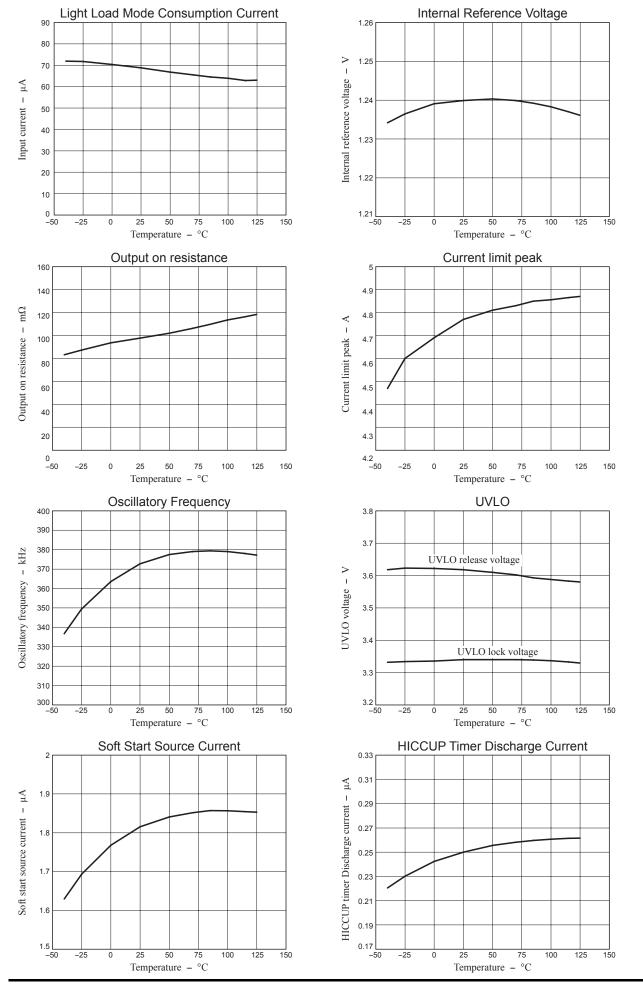

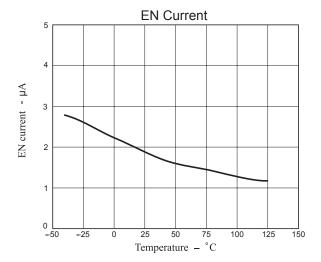

# Typical Performance Characteristics **Application Curves** at Ta = 25°C

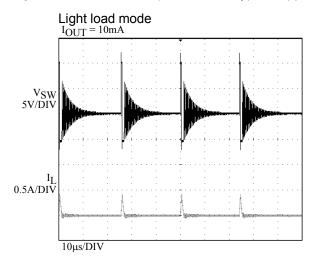

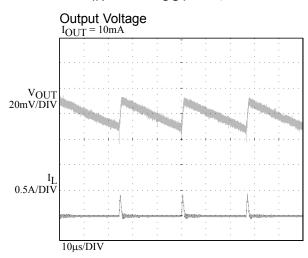

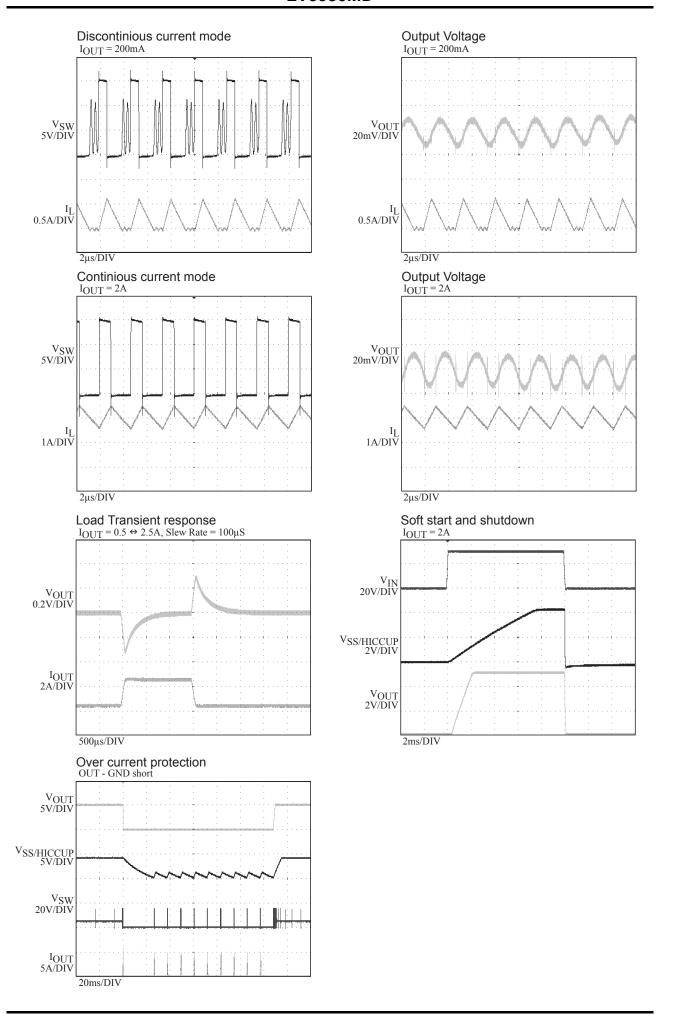

# Operation Waveforms (Circuit from Typical Application, Ta = 25°C, V<sub>IN</sub> = 15V, V<sub>OUT</sub> = 5V)

# Characterization Curves at Ta = 25°C, V<sub>IN</sub> = 15V

### **Detailed Description**

### **Power-save Feature**

The LV5980MC has Power-saving feature to enhance efficiency when the load is light. By shutting down unnecessary circuits, operating current of the IC is minimized and high efficiency is realized.

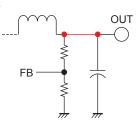

# **Output Voltage Setting**

Output voltage (V<sub>OUT</sub>) is configurable by the resistance R3 between V<sub>OUT</sub> and FB and the R2 between FB and GND. V<sub>OUT</sub> is given by the following equation (1).

$$V_{OUT} = (1 + \frac{R3}{R2}) \times V_{REF} = (1 + \frac{R3}{R2}) \times 1.235 \text{ [V]}$$

(1)

### **Soft Start**

Soft start time (TSS) is configurable by the capacitor (C5) between SS/HICCUP and GND. The setting value of TSS is given by the equation (2).

$$T_{SS} = C5 \times \frac{V_{REF}}{I_{SS}} = C5 \times \frac{1.235}{1.8 \times 10^{-6}}$$

[ms] (2)

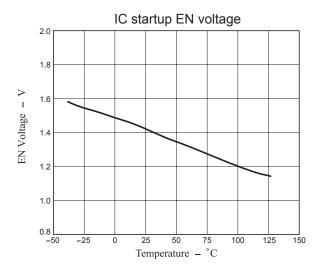

### **Hiccup Over-Current Protection**

Over-current limit (I $_{\rm CL}$ ) is set to 4.7A in the IC. When the peak value of inductor current is higher than 4.7A for 15 consecutive times, the protection deems it as over current and stops the IC. Stop period ( $T_{\rm HIC}$ ) is defined by the discharging time of the SS/HICCUP. When SS/HICCUP is lower than 0.15V, the IC starts up. When SS/HICCUP is higher than 0.3V and then over current is detected, the IC stops again. And when SS/HICCUP is higher than 1.235V, the discharge starts again. When the protection does not detect over-current status, the IC starts up again.

The IC starts up when SS/HICCUP is lower than 0.15V.

•The IC stops when SS/HICCUP is higher than 0.3V and overcurrent is detected.

•The IC starts up again if no overcurrent is

# **Design Procedure**

### **Inductor Selection**

When conditions for input voltage, output voltage and ripple current are defined, the following equations (3) give inductance value

$$L = \frac{V_{IN} - V_{OUT}}{\Delta I_R} \times T_{ON}$$

$$T_{ON} = \frac{1}{\{((V_{IN} - V_{OUT}) \div (V_{OUT} + V_F)) + 1\} \times F_{OSC}}$$

$$F_{OSC} : Oscillatory Frequency$$

$$VF : Forward voltage of Schottky Barrier diode$$

$$V_{IN} : Input voltage$$

$$V_{OUT} : Output voltage$$

• Inductor current: Peak value (IRP)

Current peak value (IRP) of the inductor is given by the equation (4).

$$I_{RP} = I_{OUT} + \frac{V_{IN} - V_{OUT}}{2L} \times T_{ON}$$

(4)

Make sure that rating current value of the inductor is higher than a peak value of ripple current.

Inductor current: ripple current (ΔI<sub>R</sub>)

Ripple current (ΔI<sub>R</sub>) is given by the equation (5).

$$\Delta I_{R} = \frac{V_{IN} - V_{OUT}}{I} \times T_{ON}$$

(5)

When load current (IQUT) is less than 1/2 of the ripple current, inductor current flows discontinuously.

# **Output Capacitor Selection**

Make sure to use a capacitor with low impedance for switching power supply because of large ripple current flows through output capacitor.

This IC is a switching regulator which adopts current mode control method. Therefore, you can use capacitor such as ceramic capacitor and OS capacitor in which equivalent series resistance (ESR) is exceedingly small.

Effective value is given by the equation (6) because the ripple current (AC) that flows through output capacitor is saw tooth wave.

$$I_{C\_OUT} = \frac{1}{2\sqrt{3}} \times \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{L \times F_{OSC} \times V_{IN}} \quad [Arms]$$

(6)

### **Input Capacitor Selection**

Ripple current flows through input capacitor which is higher than that of the output capacitors.

Therefore, caution is also required for allowable ripple current value.

The effective value of the ripple current flows through input capacitor is given by the equation (7).

$$I_{C_{IN}} = \sqrt{D(1 - D)} \times I_{OUT} \quad [Arms]$$

$$D = \frac{T_{ON}}{T} = \frac{V_{OUT}}{V_{IN}}$$

(7)

In (7), D signifies the ratio between ON/OFF period. When the value is 0.5, the ripple current is at a maximum. Make sure that the input capacitor does not exceed the allowable ripple current value given by (7). With (7), if  $V_{IN}=15V$ ,  $V_{OUT}=5V$ ,  $I_{OUT}=1.0A$  and  $F_{OSC}=370$  kHz, then  $I_{C\ IN}$  value is about 0.471Arms.

In the board wiring from input capacitor,  $\overline{V}_{IN}$  to GND, make sure that wiring is wide enough to keep impedance low because of the current fluctuation. Make sure to connect input capacitor near output capacitor to lower voltage bound due to regeneration current. When change of load current is excessive ( $I_{OUT}$ : high  $\Rightarrow$  low), the power of output electric capacitor is regenerated to input capacitor. If input capacitor is small, input voltage increases. Therefore, you need to implement a large input capacitor. Regeneration power changes according to the change of output voltage, inductance of a coil and load current.

### Selection of external phase compensation component

This IC adopts current mode control which allows use of ceramic capacitor with low ESR and solid polymer capacitor such as OS capacitor for output capacitor with simple phase compensation. Therefore, you can design long-life and high quality step-down power supply circuit easily.

# **Frequency Characteristics**

The frequency characteristic of this IC is constituted with the following transfer functions.

(1) Output resistance breeder

:  $H_R$

(2) Voltage gain of error amplifier

:  $G_{VEA}$

Current gain

:  $G_{MEA}$

(3) Impedance of phase compensation external element

:  $Z_C$

(4) Current sense loop gain

:  $G_{CS}$

(5) Output smoothing impedance  $: Z_O$

Closed loop gain is obtained with the following formula (8).

$$G = H_R \cdot G_{MER} \cdot Z_C \cdot G_{CS} \cdot Z_O$$

$$= \frac{V_{REF}}{V_{OUT}} \cdot G_{MER} \cdot \left( R_{C} + \frac{1}{SC_{C}} \right) \cdot G_{CS} \cdot \frac{R_{L}}{1 + SC_{O} \cdot R_{L}}$$

(8)

Frequency characteristics of the closed loop gain is given by pole fp1 consists of output capacitor  $C_O$  and output load resistance  $R_L$ , zero point fz consists of external capacitor  $C_C$  of the phase compensation and resistance  $R_C$ , and pole fp2 consists of output impedance  $Z_{ER}$  of error amplifier and external capacitor of phase compensation  $C_C$  as shown in formula (8). fp1, fz, fp2 are obtained with the following equations (9) to (11).

$$fp1 = \frac{1}{2\pi \cdot C_O \cdot R_L}$$

(9)

$$fz = \frac{1}{2\pi \cdot C_C \cdot R_C}$$

(10)

$$fp2 = \frac{1}{2\pi \cdot Z_{ER} \cdot C_C}$$

(11)

### Calculation of external phase compensation constant

Generally, to stabilize switching regulator, the frequency where closed loop gain is 1 (zero-cross frequency fZC) should be 1/10 of the switching frequency (or 1/5). Since the switching frequency of this IC is 370kHz, the zero-cross frequency should be 37kHz. Based on the above condition, we obtain the following formula (12).

$$\frac{V_{REF}}{V_{OUT}} \bullet G_{MER} \bullet \left[ R_{C} + \frac{1}{SC_{C}} \right] \bullet G_{CS} \bullet \frac{R_{L}}{1 + SC_{O} \bullet R_{L}} = 1$$

(12)

As for zero-cross frequency, since the impedance element of phase compensation is  $RC \gg 1/SC_C$ , the following equation (13) is obtained.

$$\frac{V_{REF}}{V_{OUT}} \cdot G_{MER} \cdot R_{C} \cdot G_{CS} \cdot \frac{R_{L}}{1 + 2\pi \cdot f_{ZC} \cdot C_{O} \cdot R_{L}} = 1$$

(13)

Phase compensation external resistance can be obtained with the following formula (14), the variation of the formula (13). Since  $2\pi \cdot f_{ZC} \cdot C_O \cdot R_L >> 1$  in the equation (14), we know that the external resistance is independent of load resistance.

$$R_{C} = \frac{V_{OUT}}{V_{REF}} \cdot \frac{1}{G_{MER}} \cdot \frac{1}{G_{CS}} \cdot \frac{1 + 2\pi \cdot f_{ZC} \cdot C_{O} \cdot R_{L}}{R_{L}}$$

(14)

When output is 5V and load resistance is  $5\Omega$  (1A load), the resistances of phase compensation are as follows.  $G_{CS} = 2.7 \text{A/V}$ ,  $G_{MER} = 220 \mu \text{A/V}$ ,  $f_{ZC} = 37 \text{kHz}$

$$R_{C} = \frac{5}{1.235} \times \frac{1}{220 \times 10^{-6}} \times \frac{1}{2.7} \times \frac{1 + 2 \times 3.14 \times (37 \times 10^{3}) \times (30 \times 10^{-6}) \times 5}{5} = 48.898... \times 10^{3}$$

$$=48.90 [k\Omega]$$

If frequency of zero point fz and pole fp1 are in the same position, they cancel out each other. Therefore, only the pole frequency remains for frequency characteristics of the closed loop gain.

In other words, gain decreases at -20dB/dec and phase only rotates by 90° and this allows characteristics where oscillation never occurs.

fp1 = fz

$$\frac{1}{2\pi \cdot C_{O} \cdot R_{L}} \cdot \frac{1}{2\pi \cdot C_{O} \cdot R_{C}}$$

$$C_{C} = \frac{R_{L} \cdot C_{O}}{R_{C}} \cdot \frac{5 \times (30 \times 10^{-6})}{48.9 \times 10^{3}} = 3.067... \times 10^{-9}$$

$$= 3.07 [nF]$$

The above shows external compensation constant obtained through ideal equations. In reality, we need to define phase constant through testing to verify constant IC operation at all temperature range, load range and input voltage range. In the evaluation board for delivery, phase compensation constants are defined based on the above constants. The zero-cross frequency required in the actual system board, in other word, transient response is adjusted by external compensation resistance. Also, if the influence of noise is significant, use of external phase compensation capacitor with higher value is recommended.

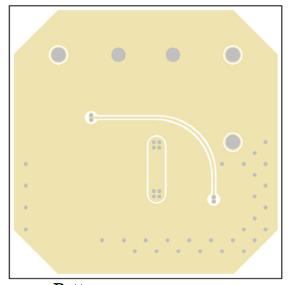

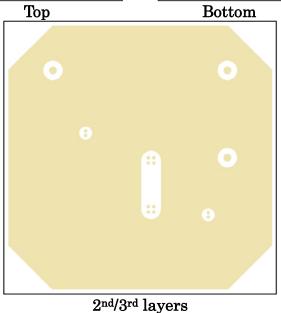

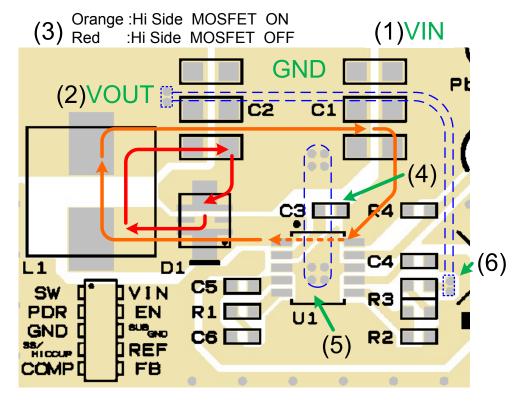

# Caution in pattern design

Pattern design of the board affects the characteristics of DC-DC converter. This IC switches high current at a high speed. Therefore, if inductance element in a pattern wiring is high, it could be the cause of noise. Make sure that the pattern of the main circuit is wide and short.

- (1) Pattern design of the input capacitor

- Connect a capacitor near the IC for noise reduction between  $V_{IN}$  and the GND. The change of current is at the largest in the pattern between an input capacitor and  $V_{IN}$  as well as between GND and an input capacitor among all the main circuits. Hence make sure that the pattern is as fat and short as possible.

- (2) Pattern design of an inductor and the output capacitor

High electric current flows into the choke coil and the output capacitor. Therefore this pattern should also be as fat and short as possible.

- (3) Pattern design with current channel into consideration

Make sure that when High side MOSFET is ON (red arrow) and OFF (orange arrow), the two current channels runs through the same channel and an area is minimized.

- (4) Pattern design of the capacitor between V<sub>IN</sub>-PDR Make sure that the pattern of the capacitor between V<sub>IN</sub> and PDR is as short as possible.

- (5) Pattern design of the small signal GND

The GND of the small signal should be separated from the power GND.

- (6) Pattern design of the FB-OUT line Wire the line shown in red between FB and OUT to the output capacitor as near as possible. When the influence of noise is significant, use of feedback resistors R2 and R3 with lower value is recommended.

Fig: FB-OUT Line

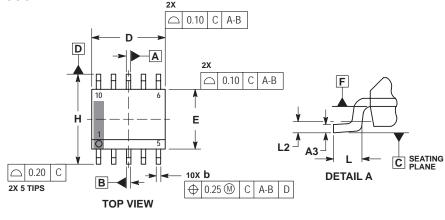

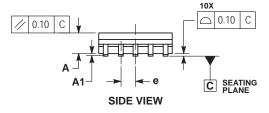

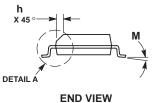

# **PAKAGE DIMENSIONS**

### **SOIC-10NB**

CASE 751BQ-01 **ISSUE A**

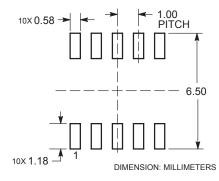

# **RECOMMENDED SOLDERING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. DIMENSION b DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE PROTRUSION SHALL BE 0.10mm TOTAL IN EXCESS OF 'b' AT MAXIMUM MATERIAL CONDITION.

4. DIMENSIONS D AND E DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS. MOLD FLASH, PROTRUSIONS, OR GATE BURRS SHALL NOT EXCEED 0.15mm PER SIDE. DIMENSIONS D AND E ARE DETERMINED AT DATUM F.

- TERMINED AT DATUM F.

DIMENSIONS A AND B ARE TO BE DETERM-INED AT DATUM F.

- AT IS DEFINED AS THE VERTICAL DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT ON THE PACKAGE BODY.

|     | MILLIMETERS |      |  |

|-----|-------------|------|--|

| DIM | MIN         | MAX  |  |

| Α   | 1.25        | 1.75 |  |

| A1  | 0.10        | 0.25 |  |

| A3  | 0.17        | 0.25 |  |

| b   | 0.31        | 0.51 |  |

| D   | 4.80        | 5.00 |  |

| E   | 3.80        | 4.00 |  |

| е   | 1.00        | BSC  |  |

| Н   | 5.80        | 6.20 |  |

| h   | 0.37 REF    |      |  |

| L   | 0.40 1.2    |      |  |

| L2  | 0.25 BSC    |      |  |

| M   | 0° 8°       |      |  |

# **GENERIC MARKING DIAGRAM\***

XXXXX = Specific Device Code

= Assembly Location Α

= Wafer Lot L = Year

= Work Week W = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G", may or not be present.

# ORDERING INFORMATION

| Device      | Package                            | Shipping (Qty / Packing) |

|-------------|------------------------------------|--------------------------|

| LV5980MD-AH | SOIC10<br>(Pb-Free / Halogen Free) | 2500 / Tape & Reel       |

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equa