# **Target**

# 8Gb LPDDR3 SDRAM

178FBGA, 11x11.5 256M x32 (32M x32 x 8banks)

This document and all information provided herein (collectively, "Information") is provided on an "AS-IS" basis and remains the sole and exclusive property of Samsung Electronics. You must keep all Information in strict confidence and trust, and must not, directly or indirectly, in any way, disclose, make accessible, post on the internet, reveal, report, publish, disseminate or transfer any Information to any third party. You must not reproduce or copy Information, without first obtaining express written permis sion from Samsung Electronics. You must not use, or allow use of, any Information in any manner whatsoever, except to internally evaluate the Information. You must restrict access to Information to those of your employees who have a bonafide need -to-know for such purpose and are bound by obligations at least as restrictive as this clause. In order to receive Information, you must agree to the foregoing and to indemnify Samsung for any failure to strictly comply therewith. If you do not agree, please do not accept any receipt of Information.

# judy.huang@samsung.com datasheet

SAMSUNG ELECTRONICS RESERVES THE RIGHT TO CHANGE PRODUCTS, INFORMATION AND SPECIFICATIONS WITHOUT NOTICE.

Products and specifications discussed herein are for reference purposes only. All information discussed herein is provided on an "AS IS" basis, without warranties of any kind.

This document and all information discussed herein remain the sole and exclusive property of Samsung Electronics. No license of any patent, copyright, mask work, trademark or any other intellectual property right is granted by one party to the other party under this document, by implication, estoppel or otherwise.

Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similar applications where product failure could result in loss of life or personal or physical harm, or any military or defense application, or any governmental procurement to which special terms or provisions may apply.

For updates or additional information about Samsung products, contact your nearest Samsung office.

All brand names, trademarks and registered trademarks belong to their respective owners.

© 2015 Samsung Electronics Co., Ltd. All rights reserved.

# **Revision History**

| Revision No. | <u>History</u>                            | <u>Draft Date</u> | <u>Remark</u> | <u>Editor</u> |  |

|--------------|-------------------------------------------|-------------------|---------------|---------------|--|

| 0.0          | - First version for target specification. | 9th Mar, 2015     | Target        | J.Y.Bae       |  |

judy.huang@samsung.com

# Table Of Contents 8Gb LPDDR3 SDRAM

| 1.0 COMPARISION BETWEEN LPDDR2 AND LPDDR3                                                                                                                                                                                                                                                                                                                                                                                                                           | 5                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 2.0 KEY FEATURE                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 7                          |

| 3.0 ORDERING INFORMATION                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7                          |

| 4.0 PACKAGE DIMENSION & PIN DESCRIPTION 4.1 LPDDR3 SDRAM Package Dimension 4.2 LPDDR3 SDRAM Package Ballout 4.3 LPDDR3 Pad Definition and Description                                                                                                                                                                                                                                                                                                               | 8<br>9                     |

| 5.0 FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                          | 11                         |

| 6.0 LPDDR3 SDRAM ADDRESSING                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12<br>13                   |

| 7.0 TRUTH TABLES 7.1 Command truth table 7.2 CKE Truth Table 7.3 State Truth Table 7.4 Data mask truth table                                                                                                                                                                                                                                                                                                                                                        | 20<br>22<br>23             |

| 8.0 ABSOLUTE MAXIMUM RATINGS                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |

| 9.0 AC & DC OPERATING CONDITIONS  9.1 Recommended DC Operating Conditions  9.2 Input Leakage Current  9.3 Operating Temperature Range                                                                                                                                                                                                                                                                                                                               | 27<br>27                   |

| 10.0 AC AND DC INPUT MEASUREMENT LEVELS                                                                                                                                                                                                                                                                                                                                                                                                                             | 28<br>28<br>28             |

| 10.3 Vref Tolerances  10.4 Input Signal  10.5 AC and DC Logic Input Levels for Differential Signals  10.5.1 Differential signal definition  10.5.2 Differential swing requirements for clock (CK_t - CK_c) and strobe (DQS_t - DQS_c)  10.5.3 Single-ended requirements for differential signals  10.6 Differential Input Cross Point Voltage  10.7 Slew Rate Definitions for Single-Ended Input Signals  10.8 Slew Rate Definitions for Differential Input Signals | 30<br>31<br>32<br>33<br>34 |

| 11.0 AC AND DC OUTPUT MEASUREMENT LEVELS                                                                                                                                                                                                                                                                                                                                                                                                                            | 36<br>36<br>37             |

| 12.0 OUTPUT BUFFER CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |

| 13.0 RONPU AND RONPD RESISTOR DEFINITION                                                                                                                                                                                                                                                                                                                                                                                                                            | 41<br>42<br>43<br>44<br>46 |

| 14.0 INPUT/OUTPUT CAPACITANCE                                                                                                                                                                                                                                                                                                                                                                                                                                       |                            |

| 15.0 IDD SPECIFICATION PARAMETERS AND TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                               | 48                         |

| 15.3 IDD Spec Table                                              | 53 |

|------------------------------------------------------------------|----|

| 6.0 ELECTRICAL CHARACTERISTICS AND AC TIMING                     | 55 |

| 16.1 Clock Specification                                         | 55 |

| 16.1.1 Definition for tCK(avg) and nCK                           | 55 |

| 16.1.2 Definition for tCK(abs)                                   |    |

| 16.1.3 Definition for tCH(avg) and tCL(avg)                      | 55 |

| 16.1.4 Definition for tJIT(per)                                  |    |

| 16.1.5 Definition for tJIT(cc)                                   | 56 |

| 16.1.6 Definition for tERR(nper)                                 | 56 |

| 16.1.7 Definition for duty cycle jitter tJIT(duty)               |    |

| 16.1.8 Definition for tCK(abs), tCH(abs) and tCL(abs)            |    |

| 16.2 Period Clock Jitter                                         | 58 |

| 16.2.1 Clock period jitter effects on core timing parameters     | 58 |

| 16.2.1.1 Cycle time de-rating for core timing parameters         |    |

| 16.2.1.2 Clock Cycle de-rating for core timing parameters        | 58 |

| 16.2.2 Clock jitter effects on Command/Address timing parameters | 58 |

| 16.2.3 Clock jitter effects on Read timing parameters            | 59 |

| 16.2.3.1 tRPRE                                                   | 59 |

| 16.2.3.2 tLZ(DQ), tHZ(DQ), tDQSCK, tLZ(DQS), tHZ(DQS)            | 59 |

| 16.2.3.3 tQSH, tQSL                                              | 59 |

| 16.2.3.4 tRPST                                                   |    |

| 16.2.4 Clock jitter effects on Write timing parameters           | 59 |

| 16.2.4.1 tDS, tDH                                                | 59 |

| 16.2.4.2 tDSS, tDSH                                              | 59 |

| 16.2.4.3 tDQSS                                                   | 60 |

| 16.3 LPDDR3 Refresh Requirements by Device Density               | 60 |

| 16.4 AC Timing                                                   | 61 |

| 16.5 CA and CS_n Setup, Hold and Derating                        | 66 |

| 16.6 Data Setup, Hold and Slew Rate Derating                     | 72 |

| CARACILLO                                                        |    |

|                                                                  |    |

|                                                                  |    |

|                                                                  |    |

iudv.huang@samsung.com

# 1.0 COMPARISION BETWEEN LPDDR2 AND LPDDR3

|                                       | Items                              | LPDDR2                                                | LPDDR3                     |  |

|---------------------------------------|------------------------------------|-------------------------------------------------------|----------------------------|--|

|                                       | CLK scheme                         | Differential (CLK/CLKB)                               | ←                          |  |

|                                       | Data scheme                        | DDR Single-ended,<br>Bi-Directional                   | <b>←</b>                   |  |

|                                       | DQS scheme                         | Differential (DQS/DQSB),<br>Bi-Directional            | <b>←</b>                   |  |

|                                       | ADD / CMD scheme                   | DDR                                                   | ←                          |  |

|                                       | State Diagram                      | As is                                                 | Refer to the Datasheet     |  |

|                                       | Command Truth Table                | As is                                                 | No support BST             |  |

|                                       | State for bank n to Bank n/m       | As is                                                 | No support BST / Interrupt |  |

| Feature                               | Data mask Truth Table              | As is                                                 | <b>←</b>                   |  |

|                                       | I/O Interface                      | HSUL_12                                               | <b>←</b>                   |  |

|                                       | Burst Length                       | 4(Default), 8, 16                                     | 8                          |  |

|                                       | Burst Type                         | Sequential, Interleave                                | Sequential                 |  |

|                                       | No Wrap                            | Support (BL4)                                         | No support                 |  |

|                                       | # of Bank                          | 8                                                     | 8                          |  |

|                                       | Organization                       | ×16/×32                                               | <b>←</b>                   |  |

|                                       | Data Mask                          | Support (Write)                                       | <b>←</b>                   |  |

|                                       | Refresh mode                       | All Bank Refresh / Per Bank Refresh /<br>Self Refresh | <b>←</b>                   |  |

|                                       | Row                                |                                                       |                            |  |

| Address size of (20)                  | Column                             | Defeate the Detector                                  | Pofor to the Detached      |  |

| Addressing(x32)                       | Bank                               | Refer to the Datasheet                                | Refer to the Datasheet     |  |

|                                       | Refresh Requirements               |                                                       |                            |  |

|                                       | Speed bin [Mbps]                   | 667/800/1066                                          | 1600/1866/2133             |  |

|                                       | Read/Write latency                 |                                                       |                            |  |

| AC Parameter                          | Core Parameters                    | a Camelina c                                          | 0.00                       |  |

| AC Parameter                          | IO Parameters                      | Refer to the Datasheet                                | Refer to the Datasheet     |  |

|                                       | CA / CS_n / Setup / Hold / Deratin |                                                       |                            |  |

|                                       | Data Setup / Hold / Deratin        |                                                       |                            |  |

|                                       | PASR                               | Support                                               | <b>←</b>                   |  |

|                                       | TCSR                               | Support                                               | <b>←</b>                   |  |

|                                       | Deep Power Down                    | Support                                               | No Support                 |  |

| On a sight Formation                  | Configurable D/S                   | Support                                               | <b>←</b>                   |  |

| Special Function                      | ZQ Calibration                     | Support                                               | <b>←</b>                   |  |

|                                       | DQ Calibration                     | Support                                               | <b>←</b> 1)                |  |

|                                       | CA Calibration                     | N/A                                                   | Support                    |  |

|                                       | Write Leveling                     | N/A                                                   | Support                    |  |

|                                       | VDD1 [V]                           | 1.70 ~ 1.95                                           | <b>←</b>                   |  |

| <u> </u>                              | VDD2 [V]                           | 1.14 ~ 1.30                                           | <b>←</b>                   |  |

| Power Supply                          | VDDQ [V]                           | 1.14 ~ 1.30                                           | <b>←</b>                   |  |

|                                       | VDDCA [V]                          | 1.14 ~ 1.30                                           | <b>←</b>                   |  |

| IDD Specification Parameters and Test | IDD Measurement Conditions         | As is                                                 | <b>←</b>                   |  |

| Conditions                            | IDD Specification                  | As is                                                 | <b>←</b>                   |  |

|                                       | General [°C]                       | -25 ~ 85                                              | <b>←</b> -                 |  |

| Temperature                           | Extended [°C]                      | -25 ~ 105                                             | ←                          |  |

|                                       |                                    |                                                       |                            |  |

|                             |                                                   | Items                               | LPDDR2                                     | LPDDR3                                                                                            |  |

|-----------------------------|---------------------------------------------------|-------------------------------------|--------------------------------------------|---------------------------------------------------------------------------------------------------|--|

|                             |                                                   | General                             | As is                                      | <b>←</b>                                                                                          |  |

|                             |                                                   |                                     | Support                                    | MR0 DI <sup>2)</sup>                                                                              |  |

|                             |                                                   |                                     | Support                                    | MR1 BL/WC/nWR <sup>2)</sup>                                                                       |  |

|                             |                                                   | -                                   | Support                                    | MR2 RL & WL, nWRE <sup>2)</sup>                                                                   |  |

|                             |                                                   | Modified                            |                                            |                                                                                                   |  |

| Mod                         | e Register Set                                    | Woulled                             | Support                                    | MR3 DS <sup>2)</sup>                                                                              |  |

| Mode Register Set           |                                                   |                                     | Support                                    | MR4 Refresh Rate<br>(0.5×tREFI) <sup>2)</sup>                                                     |  |

|                             |                                                   |                                     | Support                                    | MR8 I/O width, Type <sup>2)</sup>                                                                 |  |

|                             |                                                   | Autolia                             | N/A                                        | MR41/42/48                                                                                        |  |

|                             |                                                   | Adding                              | N/A                                        | MR2 OP7(Write Leveling)                                                                           |  |

|                             |                                                   | w/ ZQ Calibration                   | As is                                      | ←                                                                                                 |  |

| DON/DO                      | Nort Objective                                    | w/o ZQ Calibration                  | As is                                      | ←                                                                                                 |  |

| RONpu/RC                    | ONpd Characteristics                              | Temperature and Voltage Sensitivity | As is                                      | <b>←</b>                                                                                          |  |

|                             |                                                   | RZQI-V Curve                        | As is                                      | <b>←</b>                                                                                          |  |

|                             | Input/Output (                                    | Capacitance <sup>3)</sup>           | As is                                      | <b>←</b>                                                                                          |  |

|                             |                                                   | VDD1 [V]                            | -0.4 ~ 2.3                                 | ←                                                                                                 |  |

|                             |                                                   | VDD2 [V]                            | -0.4 ~ 1.6                                 | · ←                                                                                               |  |

| Absolute maximum DC ratings |                                                   | VDDQ [V]                            | -0.4 ~ 1.6                                 | · ←                                                                                               |  |

|                             |                                                   | VDDCA [V]                           | -0.4 ~ 1.6                                 | · ←                                                                                               |  |

| ,                           | go                                                | VIN/VOUT [V]                        | -0.4 ~ 1.6                                 | · ←                                                                                               |  |

|                             |                                                   | Tstg [°C]                           | -55 ~ 125                                  | · ←                                                                                               |  |

|                             |                                                   | Input leakage                       | As is                                      | · ←                                                                                               |  |

|                             |                                                   | CA and CS_n pins                    | AC : VREF +/- 0.22V<br>DC : VREF +/- 0.13V | AC: VREF ± 0.150V / ±0.135V<br>(1600/1866,2133)<br>DC: VREF ± 0.10V / ± 0.10V<br>(1600/1866,2133) |  |

|                             | AC/DC Logic Input Levels for Single-ended Signals | CKE pin                             | 0.2×VDDCA ~ 0.8×VDDCA                      | ←                                                                                                 |  |

|                             |                                                   | DQ pins                             | AC : VREF +/- 0.22V<br>DC : VREF +/- 0.13V | AC: VREF ± 0.15V/<br>±0.135V(1600/1866,2133)<br>DC: VREF ± 0.10V/0.10V<br>(1600/1866,2133)        |  |

|                             |                                                   | VREF_CA/DQ tolerance                | 0.49×VDDQ ~ 0.51×VDDQ                      | ←                                                                                                 |  |

|                             | AC/DC Logic Input Lev-                            | VIHdiff/VILdiff (AC/DC) tDVAC       | As is                                      | <b>←</b>                                                                                          |  |

|                             | els for Differential                              | VSEH/VSEL(AC)                       | As is                                      | <b>←</b>                                                                                          |  |

| Input/Output                | Differential Input Cross<br>Point Voltage         | VIXCA/VIXDQ                         | As is                                      | <b>←</b>                                                                                          |  |

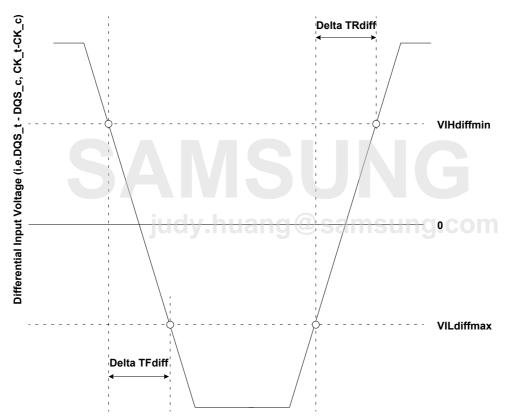

| Operating con-<br>dition    | Slew Rate definitions for<br>Differential         | VILdiff /VIHdiff<br>(Max/Min)       | As is                                      | ←                                                                                                 |  |

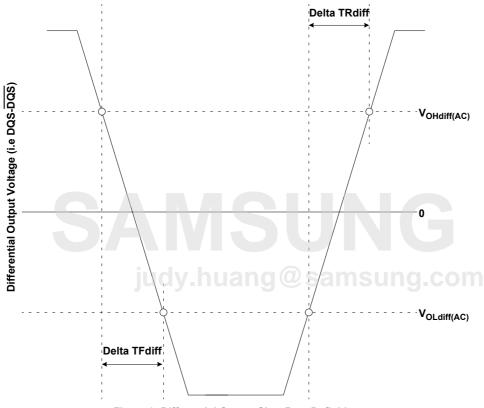

|                             | 10/000 1 11 1 6                                   | VOHdiff / VOLdiff (AC)              | As is                                      | ←                                                                                                 |  |

|                             | AC/DC Output levels for<br>Differential           | IOZ                                 | As is                                      | ←                                                                                                 |  |

|                             | Billororida                                       | MMPUPD                              | As is                                      | ←                                                                                                 |  |

|                             | AC/DC Output levels for<br>Differential           | VOHdiff / VOLdiff (AC)              | As is                                      | <b>←</b>                                                                                          |  |

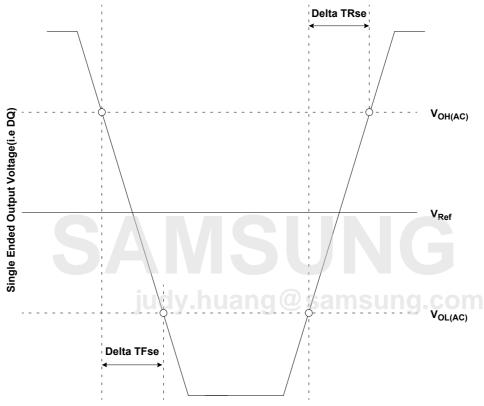

|                             | Signal ended output                               | VOH/VOL(AC/DC)                      | As is                                      | ←                                                                                                 |  |

|                             | Slew Rate                                         | SROse                               | As is                                      | <b>←</b>                                                                                          |  |

|                             | Differential Output Slew                          | VOHdiff/VOLdiff(AC)                 | As is                                      | <b>←</b>                                                                                          |  |

|                             | Rate                                              | SRQdiff                             | As is                                      | <b>←</b>                                                                                          |  |

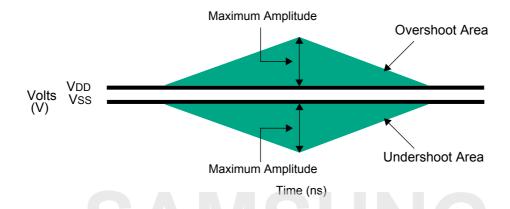

|                             | Overshoot / Undershoot                            | Maximum Amplitude                   | As is                                      | ←                                                                                                 |  |

|                             | Overshoot / Undershoot                            | Maximum Area                        | As is                                      | VDD/VSS : 0.1 [V-ns]                                                                              |  |

| 1                           | HSUL_                                             | 12 Driver Output Timing             | As is                                      | <b>←</b>                                                                                          |  |

- 1) DQ out data are same in a byte.

2) These items are modified from LPDDR2 sepcification. Please refer to Mode Register Definition.

3) The parameter applies to both die and package.

# LPDDR3 SDRAM SPECIFICATION

8G = 256M x 32 (32M x 32 x 8 banks), 178FBGA\_11x11.5

# 2.0 KEY FEATURE

- Double-data rate architecture; two data transfers per clock cycle

- Bidirectional data strobes (DQS\_t, DQS\_c), These are transmitted/received with data to be used in capturing data at the receiver

- Differential clock inputs (CK\_t and CK\_c)

- Differential data strobes (DQS\_t and DQS\_c)

- Commands & addresses entered on both positive and negative CK edges; data and data mask referenced to both edges of DQS

- 8 internal banks for concurrent operation

- · Data mask (DM) for write data

- Burst Length: 8

- · Burst Type: Sequential

- Read & Write latency : Refer to Table 45 LPDDR3 AC Timing Table

- · Auto Precharge option for each burst access

- · Configurable Drive Strength

- · All Bank Refresh, Per Bank Refresh and Self Refresh

- Partial Array Self Refresh and Temperature Compensated Self Refresh

- Write Leveling

- CA Calibration

- HSUL\_12 compatible inputs

- VDD1/VDD2/VDDQ/VDDCA

- : 1.8V/1.2V/1.2V / 1.2V

- · No DLL: CK to DQS is not synchronized

- · Edge aligned data output, center aligned data input

- Operating Temperature : -25 ~ 85°C

- On Die Termination using ODT pin

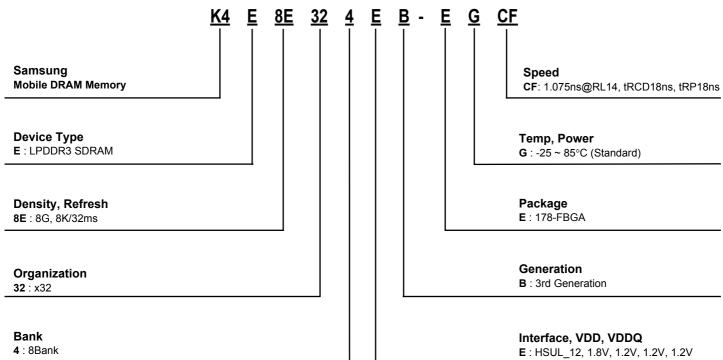

# 3.0 ORDERING INFORMATION

| Part No.        | Org. | Package         | Temperature     | Max Frequency          | Interface |

|-----------------|------|-----------------|-----------------|------------------------|-----------|

| K4E8E324EB-EGCF | x32  | 178FBGA_11x11.5 | Tc = -25 ~ 85°C | 1866Mbps (tCK=1.075ns) | HSUL_12   |

|                 |      | judy.hu         | ang@sai         | msung.com              |           |

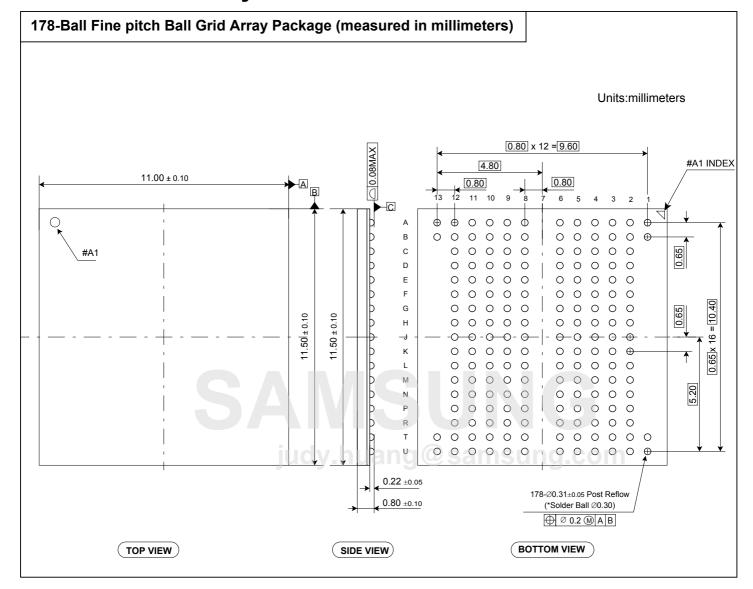

# 4.0 PACKAGE DIMENSION & PIN DESCRIPTION

# 4.1 LPDDR3 SDRAM Package Dimension

# 4.2 LPDDR3 SDRAM Package Ballout

|   |     |       |       |              |      | 178Ba        | II FBGA |                   |      |        |              |      |     |

|---|-----|-------|-------|--------------|------|--------------|---------|-------------------|------|--------|--------------|------|-----|

|   | 1   | 2     | 3     | 4            | 5    | 6            | 7       | 8                 | 9    | 10     | 11           | 12   | 13  |

| Α | DNU | DNU   | VDD1  | VDD1         | VDD1 | VDD1         | NB      | VDD2              | VDD2 | VDD1   | VDDQ         | DNU  | DNU |

| В | DNU | VSS   | ZQ    | NC           | VSS  | VSSQ         | NB      | DQ31              | DQ30 | DQ29   | DQ28         | VSSQ | DNU |

| С |     | CA9   | VSSCA | NC           | VSS  | VSSQ         | NB      | DQ27              | DQ26 | DQ25   | DQ24         | VDDQ |     |

| D |     | CA8   | VSSCA | VDD2         | VDD2 | VDD2         | NB      | DM3               | DQ15 | DQS3_t | DQS3_c       | VSSQ |     |

| E |     | CA7   | CA6   | VSS          | VSS  | VSSQ         | NB      | VDDQ              | DQ14 | DQ13   | DQ12         | VDDQ |     |

| F |     | VDDCA | CA5   | VSSCA        | VSS  | VSSQ         | NB      | DQ11              | DQ10 | DQ9    | DQ8          | VSSQ |     |

| G |     | VDDCA | VSSCA | VSSCA        | VDD2 | VSSQ         | NB      | DM1               | VSSQ | DQS1_t | DQS1_c       | VDDQ |     |

| н |     | VSS   | VDDCA | VRef(C<br>A) | VDD2 | VDD2         | NB      | VDDQ              | VDDQ | VSSQ   | VDDQ         | VDD2 |     |

| J |     | CK_c  | CK_t  | VSSCA        | VDD2 | VDD2         | NB      | ODT <sup>1)</sup> | VDDQ | VDDQ   | VRef(D<br>Q) | VSS  |     |

| K |     | VSS   | CKE   | NC           | VDD2 | VDD2         | NB      | VDDQ              | NC   | VSSQ   | VDDQ         | VDD2 |     |

| L |     | VDDCA | CS_n  | NC           | VDD2 | V <b>S</b> S | NB      | DM0               | VSSQ | DQS0_t | DQS0_c       | VDDQ |     |

| М |     | VDDCA | CA4   | VSSCA        | VSS  | VSSQ         | NB      | DQ4               | DQ5  | DQ6    | DQ7          | VSSQ |     |

| N |     | CA2   | CA3   | VSS          | VSS  | VSSQ         | NB      | VDDQ              | DQ1  | DQ2    | DQ3          | VDDQ |     |

| Р |     | CA1   | VSSCA | VDD2         | VDD2 | VDD2         | NB      | DM2               | DQ0  | DQS2_t | DQS2_c       | VSSQ |     |

| R |     | CA0   | NC    | VSS          | VSS  | VSSQ         | NB      | DQ20              | DQ21 | DQ22   | DQ23         | VDDQ |     |

| т | DNU | VSS   | VSS   | VSS          | VSS  | VSSQ         | NB      | DQ16              | DQ17 | DQ18   | DQ19         | VSSQ | DNU |

| U | DNU | DNU   | VDD1  | VDD1         | VDD1 | VDD1         | NB      | VDD2              | VDD2 | VDD1   | VDDQ         | DNU  | DNU |

[Top View]

| Power | Ground |

|-------|--------|

| ODT   | NB     |

| ZQ    | DNU/NC |

1) In case ODT function is not used, ODT pin should be considerd as NC.

ODT will be connected to rank 0. The ODT Input to rank 1 (if 2nd rank is present) will be connected to Ground in the package.

# 4.3 LPDDR3 Pad Definition and Description

## [Table 1] Pad Definition and Description

| Name                                                                               | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK_t, CK_c                                                                         | Input  | Clock: CK_t and CK_c are differential clock inputs. All Double Data Rate (DDR) CA inputs are sampled on both positive and negative edge of CK. Single Data Rate (SDR) inputs, CS_n and CKE, are sampled at the positive Clock edge. Clock is defined as the differential pair, CK_t and CK_c. The positive Clock edge is defined by the crosspoint of a rising CK_t and a falling CK_c. The negative Clock edge is defined by the crosspoint of a falling CK_t and a rising CK_c.                                                                                                              |

| CKE                                                                                | Input  | Clock Enable: CKE HIGH activates and CKE LOW deactivates internal clock signals and therefore device input buffers and output drivers. Power savings modes are entered and exited through CKE transitions. CKE is considered part of the command code. See Command Truth table for command code descriptions. CKE is sampled at the positive Clock edge.                                                                                                                                                                                                                                       |

| CS_n                                                                               | Input  | <b>Chip Select:</b> CS_n is considered part of the command code. See Command Truth table for command code descriptions. CS_n is sampled at the positive Clock edge.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CA0 - CA9                                                                          | Input  | DDR Command/Address Inputs: Uni-directional command/address bus inputs. CA is considered part of the command code. See Command Truth table for command code descriptions.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DQ0 - DQ15<br>(x16)<br>DQ0 - DQ31<br>(x32)                                         | I/O    | Data Inputs/Outputs: Bi-directional data bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DQS0_t-DQS1_t<br>DQS0_c-DQS1_c<br>(x16)<br>DQS0_t-DQS3_t<br>DQS0_c-DQS3_c<br>(x32) | I/O    | Data Strobes (Bi-directional, Differential): The data strobe is bi-directional (used for read and write data) and differential (DQS_t and DQS_c). It is output with read data and input with write data. DQS is edge-aligned to read data and centered with write data.  For x16, DQS0_t and DQS0_c correspond to the data on DQ0 - DQ7; DQS1_t and DQS1_c to the data on DQ8 - DQ15. For x32, DQS0_t and DQS0_c correspond to the data on DQ0 - DQ7, DQS1_t and DQS1_c to the data on DQ8 - DQ15, DQS2_t and DQS2_c to the data on DQ16 - DQ23, DQS3_t and DQS3_c to the data on DQ24 - DQ31. |

| DM0 - DM1<br>(x16)<br>DM0 - DM3<br>(x32)                                           | Input  | Input Data Mask: DM is the input mask signal for write data. Input data is masked when DM is sampled HIGH coincident with that input data during a Write access. DM is sampled on both edges of DQS. Although DM is for input only, the DM loading shall match the DQ and DQS_t (or DQS_c).  For x16 and x32 devices, DM0 is the input data mask signal for the data on DQ0-7, DM1 is the input data mask signal for the data on DQ8-15.  For x32 device, DM2 is the input data mask signal for the data on DQ16-23 and DM3 is the input data mask signal for the data on DQ24-31.             |

| ODT                                                                                | Input  | On Die Termination: This signal enables and disables termination on the DRAM DQ bus according to the specified mode register settings.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| $V_{\mathrm{DD1}}$                                                                 | Supply | Core Power Supply 1: Core power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $V_{\mathrm{DD2}}$                                                                 | Supply | Core Power Supply 2: Core power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $V_{\mathrm{DDCA}}$                                                                | Supply | Input Receiver Power Supply: Power supply for CA0-9, CKE, CS_n, CK_t, and CK_c input buffers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| $V_{\mathrm{DDQ}}$                                                                 | Supply | I/O Power Supply: Power supply for Data input/output buffers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| V <sub>REF (CA)</sub>                                                              | Supply | Reference Voltage for CA Command and Control Input Receiver: Reference voltage for all CA0-9, CKE, CS_n, CK_t, and CK_c input buffers.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| V <sub>REF (DQ)</sub>                                                              | Supply | Reference Voltage for DQ Input Receiver: Reference voltage for all data input buffers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| $V_{\rm SS}$                                                                       | Supply | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| V <sub>SSCA</sub>                                                                  | Supply | Ground for Input Receivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| $V_{\rm SSQ}$                                                                      | Supply | I/O Ground: Ground for data input/output buffers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ZQ                                                                                 | I/O    | Reference Pin for Output Drive Strength Calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

NOTE :

1) Data includes DQ and DM.

# 5.0 FUNCTIONAL DESCRIPTION

LPDDR3-SDRAM is a high-speed synchronous DRAM device internally configured as an 8-Bank memory. This device contains the following number of bits:

8Gb has 8,589,934,592 bits

LPDDR3 devices use a double data rate architecture on the Command/Address (CA) bus to reduce the number of input pins in the system. The 10-bit CA bus contains command, address, and bank information. Each command uses one clock cycle, during which command information is transferred on both the positive and negative edge of the clock.

These devices also use a double data rate architecture on the DQ pins to achieve high speed operation. The double data rate architecture is essentially an 8n prefetch architecture with an interface designed to transfer two data bits per DQ every clock cycle at the I/O pins. A single read or write access for the LPDDR3 SDRAM effectively consists of a single 8n-bit wide, one clock cycle data transfer at the internal DRAM core and eight corresponding n-bit wide, one-half-clock-cycle data transfers at the I/O pins.

Read and write accesses to the LPDDR3 SDRAMs are burst oriented; accesses start at a selected location and continue for a programmed number of locations in a programmed sequence. Accesses begin with the registration of an Activate command, which is then followed by a Read or Write command. The address and BA bits registered coincident with the Activate command are used to select the row and the Bank to be accessed. The address bits registered coincident with the Read or Write command are used to select the Bank and the starting column location for the burst access.

Prior to normal operation, the LPDDR3 SDRAM must be initialized. The following section provides detailed information covering device initialization, register definition, command description and device operation.

# 6.0 LPDDR3 SDRAM ADDRESSING

### [Table 2] LPDDR3 SDRAM Addressing

|     | Items                                | 8Gb     |

|-----|--------------------------------------|---------|

|     | Number of Banks                      | 8       |

|     | Bank Addresses                       | BA0-BA2 |

|     | t <sub>REFI</sub> (us) <sup>2)</sup> | 3.9     |

| ×16 | Row Addresses 3)                     | R0-R14  |

| .0  | Column Addresses 1), 3)              | C0-C10  |

| ×32 | Row Addresses 3)                     | R0-R14  |

|     | Column Addresses 1), 3)              | C0-C9   |

- 1) The least-significant column address C0 is not transmitted on the CA bus, and is implied to be zero.

- 2)  $t_{REFI}$  values for all bank refresh is Tc = -25~85°C, Tc means Operating Case Temperature

- 3) Row and Column Address values on the CA bus that are not used are "don't care."

# LPDDR3 SDRAM

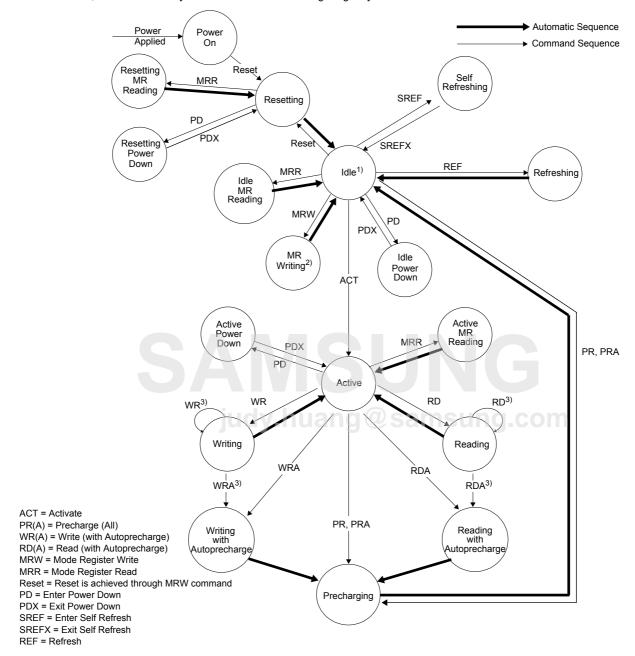

# 6.1 Simplified LPDDR3 State Diagram

LPDDR3-SDRAM state diagram provides a simplified illustration of allowed state transitions and the related commands to control them. For a complete definition of the device behavior, the information provided by the state diagram should be integrated with the truth tables and timing specification.

The truth tables provide complementary information to the state diagram, they clarify the device behavior and the applied restrictions when considering the actual state of all the banks.

For the command definition, see datasheet of [Command Definition & Timing Diagram].

Figure 1. LPDDR3: Simplified Bus Interface State Diagram

# NOTE

1)In the Idle state, all banks are precharged.

2) In the case of MRW to enter CA Training mode or Write Leveling Mode, the state machine will not automatically return to the Idle state. In these cases an additional MRW command is required to exit either operating mode and return to the Idle state. See sections "CA Training" or "Write Leveling".

3) Terminated bursts are not allowed. For these state transitions, the burst operation must be completed before the transition can occur.

4) Use caution with this diagram. It is intended to provide a floorplan of the possible state transitions and commands to control them, not all details. In particular, situations involving more than one bank are not captured in full detail.

# 6.2 Mode Register Definition

# 6.2.1 Mode Register Assignment and Definition in LPDDR3 SDRAM

Table 3 shows the mode registers for LPDDR3 SDRAM. Each register is denoted as "R" if it can be read but not written, "W" if it can be written but not read, and "R/W" if it can be read and written. A Mode Register Read command is used to read a mode register. A Mode Register Write command is used to write a mode register.

Table 31 Mode Register Assignment in LPDDR3 SDRAM

| MR#    | MA<br><7:0>                      | Function                    | Access | OP7                                                  | OP6           | OP5        | OP4         | OP3          | OP2           | OP1        | OP0 |

|--------|----------------------------------|-----------------------------|--------|------------------------------------------------------|---------------|------------|-------------|--------------|---------------|------------|-----|

| 0      | 00 <sub>H</sub>                  | Device Info.                | R      | (RFU)                                                | WL<br>(Set B) | (RFU)      | 1           | 'QI<br>onal) | (RFI          | ٦)         | DAI |

| 1      | 01 <sub>H</sub>                  | Device Feature 1            | W      | n'                                                   | WR (for Al    | P)         | (RI         | =U)          |               | BL         |     |

| 2      | 02 <sub>H</sub>                  | Device Feature 2            | W      | WR Lev                                               | WL<br>Select  | (RFU)      | nWRE        |              | RL &          | WL         |     |

| 3      | 03 <sub>H</sub>                  | I/O Config-1                | W      |                                                      | (RF           | =U)        |             |              | DS            | ;          |     |

| 4      | 04 <sub>H</sub>                  | Refresh Rate                | R      | TUF                                                  |               | (RI        | FU)         |              | Re            | fresh Rate | !   |

| 5      | 05 <sub>H</sub>                  | Basic Config-1              | R      |                                                      |               | L          | .PDDR3 M    | lanufactur   | er ID         |            |     |

| 6      | 06 <sub>H</sub>                  | Basic Config-2              | R      |                                                      |               |            | Revi        | sion ID1     |               |            |     |

| 7      | 07 <sub>H</sub>                  | Basic Config-3              | R      |                                                      |               |            | Revi        | sion ID2     |               |            |     |

| 8      | 08 <sub>H</sub>                  | Basic Config-4              | R      | I/O v                                                | width         |            | D           | ensity       |               | Ту         | ре  |

| 9      | 09 <sub>H</sub>                  | Test Mode                   | W      | Vendor-Specific Test Mode                            |               |            |             |              |               |            |     |

| 10     | 0A <sub>H</sub>                  | IO Calibration              | W      | Calibration Code                                     |               |            |             |              |               |            |     |

| 11     | 0B <sub>H</sub>                  | ODT Feature                 |        |                                                      |               | (RFU)      |             |              | PD CTL        | DQ         | ODT |

| 12:15  | 0C <sub>H</sub> ~0F <sub>H</sub> | (reserved)                  |        |                                                      |               |            | (1          | RFU)         |               |            |     |

| 16     | 10 <sub>H</sub>                  | PASR_Bank                   | W      |                                                      |               |            | PASR        | Bank Mas     | k             |            |     |

| 17     | 11 <sub>H</sub>                  | PASR_Seg                    | W      |                                                      |               |            | PASR Se     | egment Ma    | ask           |            |     |

| 18-31  | 12 <sub>H</sub> -1F <sub>H</sub> | (Reserved)                  |        |                                                      |               |            | (1          | RFU)         |               |            |     |

| 32     | 20 <sub>H</sub>                  | DQ Calibration<br>Pattern A | R      | oll 31                                               | See "I        | DQ Calibra | ation" on ( | Operations   | & Timing Dia  | agram.     |     |

| 33:39  | 21 <sub>H</sub> ~27 <sub>H</sub> | (Do Not Use)                | uuy.i  | Iuai                                                 |               | , Sai      |             |              |               |            |     |

| 40     | 28 <sub>H</sub>                  | DQ Calibration<br>Pattern B | R      | See "DQ Calibration" on Operations & Timing Diagram. |               |            |             |              |               |            |     |

| 41     | 29 <sub>H</sub>                  | CA Training 1               | W      | See "Mode Register Write-CA Training Mode".          |               |            |             |              |               |            |     |

| 42     | 2A <sub>H</sub>                  | CA Training 2               | W      |                                                      | S             | ee "Mode   | Register \  | Vrite-CA ٦   | Fraining Mode | e".        |     |

| 43:47  | 2B <sub>H</sub> ~2F <sub>H</sub> | (Do Not Use)                |        |                                                      |               |            |             |              |               |            |     |

| 48     | 30 <sub>H</sub>                  | CA Training 3               | W      |                                                      | S             | ee "Mode   | Register \  | Write-CA 7   | Fraining Mode | e".        |     |

| 49:62  | 31 <sub>H</sub> ~3E <sub>H</sub> | (Reserved)                  |        |                                                      |               |            | (1          | RFU)         |               |            |     |

| 63     | 3F <sub>H</sub>                  | Reset                       | W      |                                                      |               |            |             | Х            |               |            |     |

| 64:255 | 40 <sub>H</sub> ∼FF <sub>H</sub> | (Reserved)                  |        |                                                      |               |            | (1          | RFU)         |               |            |     |

- 1) RFU bits shall be set to '0' during Mode Register writes.

- 2) RFU bits shall be read as '0' during Mode Register reads.

- 3) All Mode Registers that are specified as RFU or write-only shall return undefined data when read and DQS\_t, DQS\_c shall be toggled.

- 4) All Mode Registers that are specified as RFU shall not be written.

- 5) See vendor device datasheets for details on vendor-specific mode registers.6) Writes to read-only registers shall have no impact on the functionality of the device.

# MR0\_Device Information (MA<7:0> = $00_H$ ):

| OP7   | OP6                | OP5   | OP4 | OP3          | OP2 | OP1 | OP0 |

|-------|--------------------|-------|-----|--------------|-----|-----|-----|

| (RFU) | WL (Set B) Support | (RFU) |     | 'QI<br>onal) | (RF | =U) | DAI |

| DAI (Device Auto-Initialization Status)       | Read-only | OP<0>   | 0 <sub>B</sub> : DAI complete<br>1 <sub>B</sub> : DAI still in progress                                                                                                                                                                                                              |                                    |

|-----------------------------------------------|-----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| RZQI (Built in Self Test for RZQ Information) | Read-only | OP<4:3> | 00 <sub>B</sub> : RZQ self test not supported 01 <sub>B</sub> : ZQ-pin may connect to VDDCA or float 10 <sub>B</sub> : ZQ-pin may short to GND 11 <sub>B</sub> : ZQ-pin self test completed, no error condition detected (ZQ-pin may not connect to VDDCA or float nor short to GND) | 1-4                                |

| WL (Set B) Support                            | Read-only | OP<6>   | <b>0</b> <sub>B</sub> : DRAM does not support WL (Set B) <b>1</b> <sub>B</sub> : DRAM supports WL (SetB)                                                                                                                                                                             | WL<br>(Set B)<br>Option<br>Support |

## NOTE :

- 1) RZQI, if supported, will be set upon completion of the MRW ZQ Initialization Calibration command.

2) If ZQ is connected to VDDCA to set default calibration, OP[4:3] shall be set to 01. If ZQ is not connected to VDDCA, either OP[4:3] = 01 or OP[4:3] = 10 might indicate a ZQ-pin assembly error. It is recommended that the assembly error is corrected.

3) In the case of possible assembly error (either OP[4:3]=01 or OP[4:3]=10 per Note 4), the LPDDR3 device will default to factory trim settings for RON, and will ignore ZQ cal-

- ibration commands. In either case, the system may not function as intended.

- 4) In the case of the ZQ self-test returning a value of 11b, this result indicates that the device has detected a resistor connection to the ZQ pin. However, this result cannot be used to validate the ZQ resistor value or that the ZQ resistor tolerance meets the specified limits (i.e 240-Ω +/- 1%).

# MR1\_Device Feature 1 (MA $<7:0> = 01_H$ ):

|    | OP7        | OP6        | OP5    | OP4 | OP3                        | OP2 | OP1 | OPU |  |

|----|------------|------------|--------|-----|----------------------------|-----|-----|-----|--|

|    | n          | WR (for AF | P)     | (RF | =U)                        |     | BL  |     |  |

| BL | Write-only | OI         | P<2:0> |     | .8 (default)<br>s: Reserve | ed  |     |     |  |

| BL                | Write-only | OP<2:0>         | 011 <sub>B</sub> : BL8 (default) All others: Reserved                                                                                                                                                                                                                                                   |

|-------------------|------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nWR <sup>1)</sup> | Write-only | judy<br>OP<7:5> | If nWRE (MR2 OP<4>) = 0:  100 <sub>B</sub> : nWR=6  110 <sub>B</sub> : nWR=8  111 <sub>B</sub> : nWR=9  If nWRE (MR2 OP<4>) = 1:  000 <sub>B</sub> : nWR=10 (default)  001 <sub>B</sub> : nWR=11  010 <sub>B</sub> : nWR=12  100 <sub>B</sub> : nWR=14  110 <sub>B</sub> : nWR=16  All others: Reserved |

# NOTE :

### [Table 4] Burst Sequence

|                |                | -              |    |                                               |   |   |   |   |   |   |   |

|----------------|----------------|----------------|----|-----------------------------------------------|---|---|---|---|---|---|---|

| C2             | C1             | CO             | DI | Burst Cycle Number and Burst Address Sequence |   |   |   |   |   |   |   |

| 62             | C1             |                | BL | 1                                             | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| 0 <sub>B</sub> | 0 <b>B</b>     | 0 <sub>B</sub> |    | 0                                             | 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 0 <sub>B</sub> | 1 <sub>B</sub> | 0 <sub>B</sub> |    | 2                                             | 3 | 4 | 5 | 6 | 7 | 0 | 1 |

| 1 <sub>B</sub> | 0 <sub>B</sub> | 0 <sub>B</sub> | 0  | 4                                             | 5 | 6 | 7 | 0 | 1 | 2 | 3 |

| 1 <sub>B</sub> | 1 <sub>B</sub> | 0 <sub>B</sub> |    | 6                                             | 7 | 0 | 1 | 2 | 3 | 4 | 5 |

- 1) C0 input is not present on CA bus. It is implied zero.

- 2) The burst address represents C2 C0.

<sup>1)</sup> Programmed value in nWR register is the number of clock cycles which determines when to start internal precharge operation for a write burst with AP enabled. It is determined by RU(tWR/tCK).

# MR2\_Device Feature 2 (MA<7:0> = $02_H$ ):

| Ī | OP7    | OP6          | OP5   | OP4  | OP3 | OP2  | OP1  | OP0 |

|---|--------|--------------|-------|------|-----|------|------|-----|

|   | WR Lev | WL<br>Select | (RFU) | nWRE |     | RL 8 | k WL |     |

| RL & WL     | Write-only | OP<3:0> | If $OP<6>=0$ (WL Set A, default) $0100_B$ : RL = 6 / WL = 3 ( $\leq 400 \text{ MHz}$ ) $0110_B$ : RL = 8 / WL = 4 ( $\leq 533 \text{ MHz}$ ) $0111_B$ : RL = 9 / WL = 5 ( $\leq 600 \text{ MHz}$ ) $1000_B$ : RL = 10 / WL = 6 ( $\leq 667 \text{ MHz}$ , default) $1001_B$ : RL = 11 / WL = 6 ( $\leq 667 \text{ MHz}$ ) $1010_B$ : RL = 12 / WL = 6 ( $\leq 800 \text{ MHz}$ ) $1100_B$ : RL = 12 / WL = 8 ( $\leq 933 \text{ MHz}$ ) $1110_B$ : RL = 16 / WL = 8 ( $\leq 1066 \text{ MHz}$ ) $1110_B$ : RL = 16 / WL = 8 ( $\leq 1066 \text{ MHz}$ ) $1110_B$ : RL = 6 / WL = 3 ( $\leq 400 \text{ MHz}$ ) $1110_B$ : RL = 8 / WL = 4 ( $\leq 533 \text{ MHz}$ ) $1110_B$ : RL = 8 / WL = 4 ( $\leq 533 \text{ MHz}$ ) $1110_B$ : RL = 10 / WL = 8 ( $\leq 667 \text{ MHz}$ , default) $1000_B$ : RL = 10 / WL = 8 ( $\leq 667 \text{ MHz}$ , default) $1010_B$ : RL = 11 / WL = 9 ( $\leq 733 \text{ MHz}$ ) $1110_B$ : RL = 12 / WL = 9 ( $\leq 800 \text{ MHz}$ ) $1110_B$ : RL = 14 / WL = 11 ( $\leq 933 \text{ MHz}$ ) $1110_B$ : RL = 16 / WL = 13 ( $\leq 1066 \text{ MHz}$ ) All others: reserved |

|-------------|------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nWRE        | Write-only | OP<4>   | <ul><li>0<sub>B</sub>: Enable nWR programming ≤ 9</li><li>1<sub>B</sub>: Enable nWR programming &gt; 9 (default)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| WL Select   | Write-only | OP<6>   | 0 <sub>B</sub> : Select WL Set A (default) 1 <sub>B</sub> : Select WL Set B (optional <sup>2)</sup> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| WR Leveling | Write-only | OP<7>   | 0 <sub>B</sub> : Disable (default) 1 <sub>B</sub> : Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

# MR3\_I/O Configuration 1 (MA<7:0> = $03_H$ ):

| OP7 | OP6 | OP5 | OP4 | OP3 | OP2 | OP1 | OP0 |

|-----|-----|-----|-----|-----|-----|-----|-----|

|     | (RF | -U) |     |     | D   | S   |     |

| DS | Write-only | OP<3:0> | $ \begin{array}{c} \textbf{0001}_{\mathbf{B}} : 34.3-\Omega \ \text{typical pull-down/pull-up} \\ \textbf{0010}_{\mathbf{B}} : 40-\Omega \ \text{typical pull-down/pull-up} \ \ \textbf{(default)} \\ \textbf{0011}_{\mathbf{B}} : 48-\Omega \ \text{typical pull-down/pull-up} \\ \textbf{0100}_{\mathbf{B}} : \text{Reserved for } 60\Omega \ \text{typical pull-down/pull-up} \\ \textbf{0110}_{\mathbf{B}} : \text{Reserved for } 80\Omega \ \text{typical pull-down/pull-up} \\ \textbf{1001}_{\mathbf{B}} : 34.3\Omega \ \text{typical pull-down, } 40\Omega \ \text{typical pull-up} \\ \textbf{1010}_{\mathbf{B}} : 40\Omega \ \text{typical pull-down, } 48\Omega \ \text{typical pull-up} \\ \textbf{1011}_{\mathbf{B}} : 34.3\Omega \ \text{typical pull-down, } 48\Omega \ \text{typical pull-up} \\ \textbf{All others} : \text{Reserved} \\ \end{array} $ |

|----|------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|----|------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

NOTE:

1) See MR0, OP<7>

2) See MR0, OP<6>

# $MR4_Device Temperature (MA<7:0> = 04_H)$

| OP7 | OP6 | OP5 | OP4 | OP3 | OP2  | OP1        | OP0  |

|-----|-----|-----|-----|-----|------|------------|------|

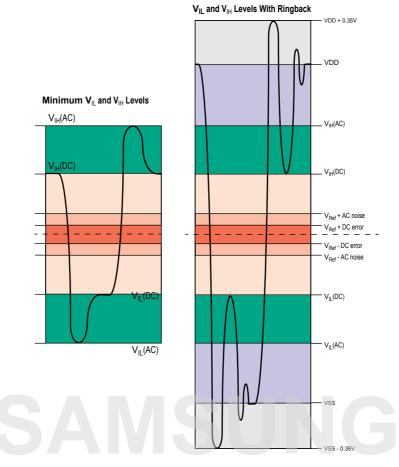

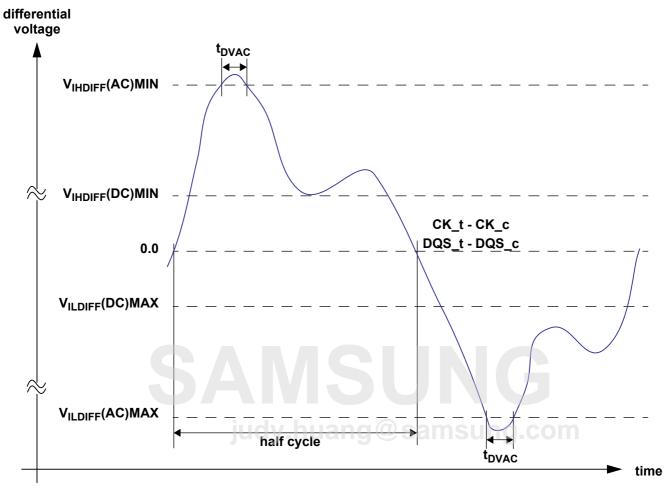

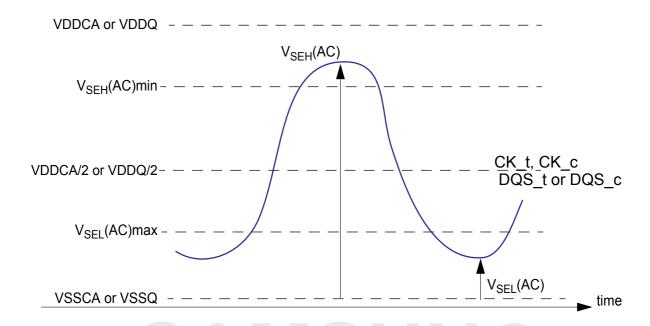

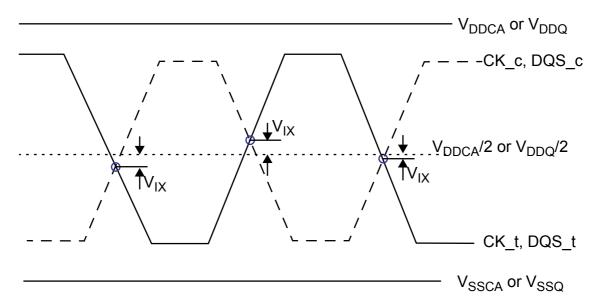

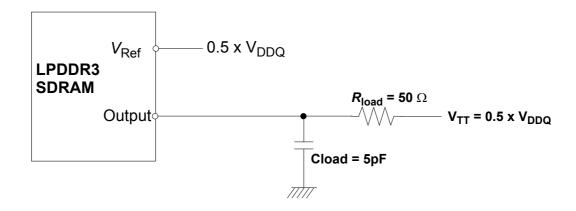

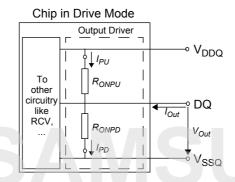

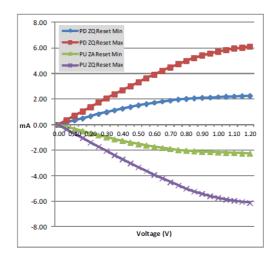

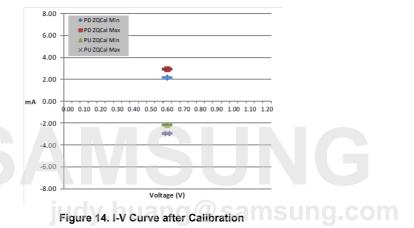

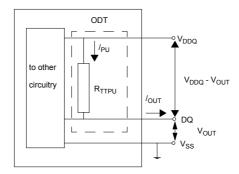

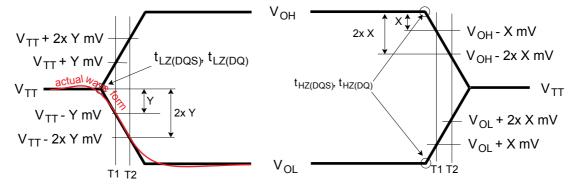

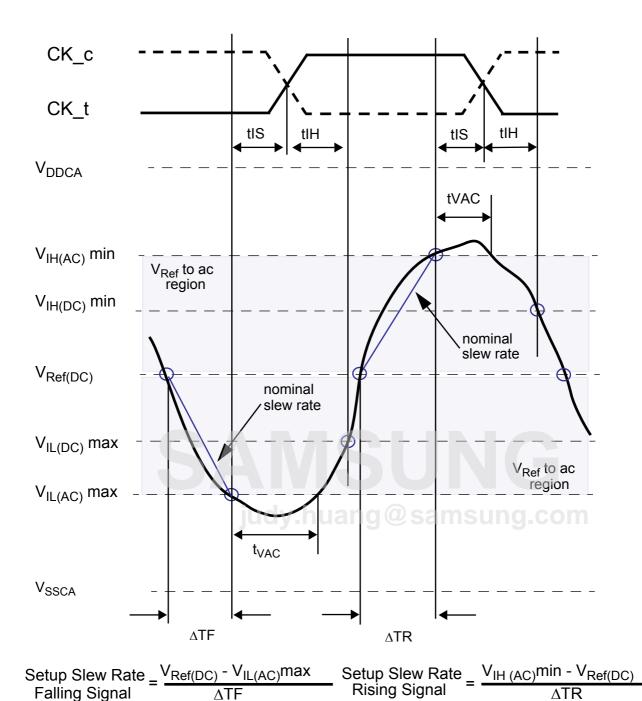

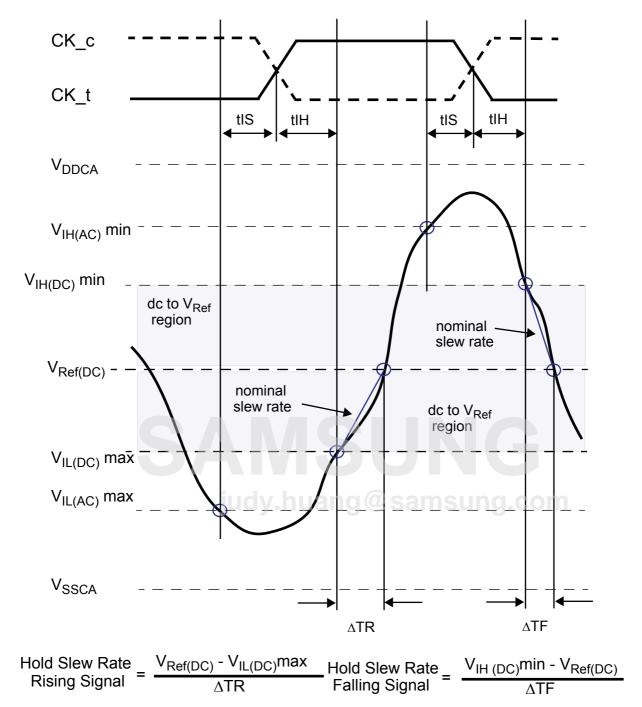

| TUF |     | (RF | =U) |     | SDRA | AM Refresh | Rate |