# 2.5GBPS Post Amplifier and 1.25GBPS LD Driver with MCU

## **GENERAL DESCRIPTION**

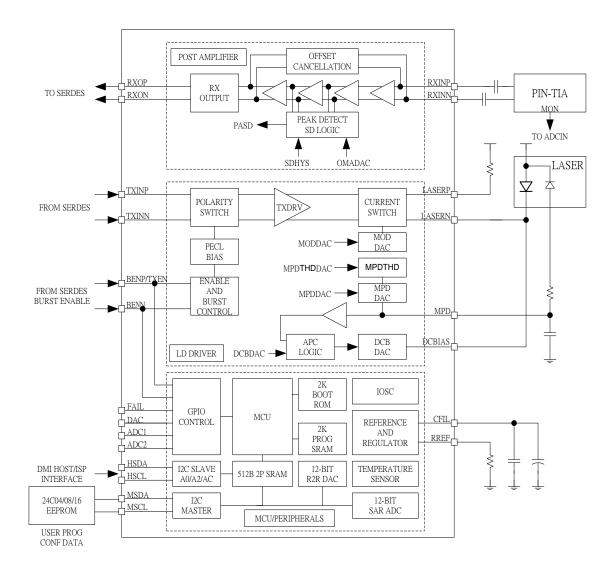

CS6721 integrates three main functions in a single chip providing optimal solutions for various fiber module applications. The functional blocks include a 2.5G postamplifier, a 1.25G burst or continuous mode LD driver, and an 8-bit MCU for configuring and controlling the module functions.

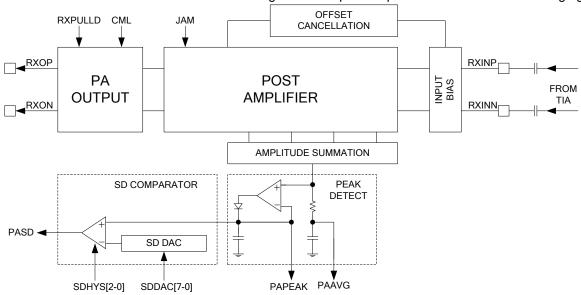

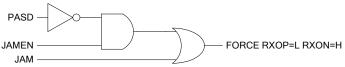

The post-amplifier receives AC coupled differential signal from pre-amplifier and performs the quantization amplifications. There are total four amplification stages excluding the output stage. The offset cancellation is built-in on chip. The LOS status is also configurable as a set peak level detection by the post-amplifier or combined with ADC detection on peak level.

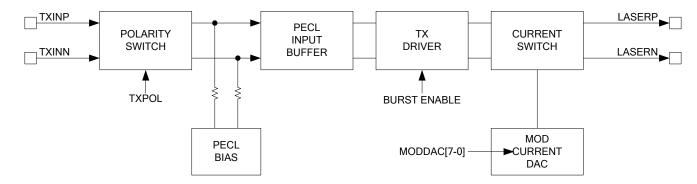

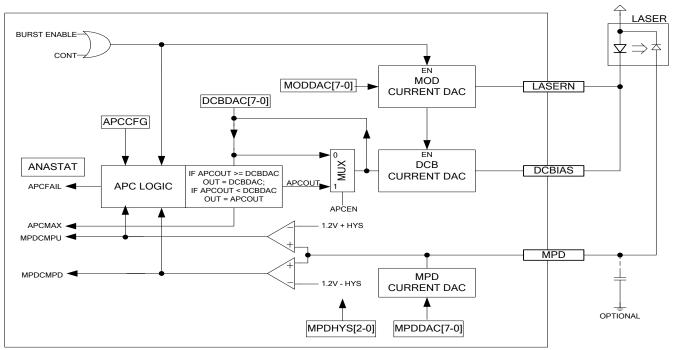

The LD driver performs the transmit function that receives the PECL differential signal TXINP/TXINN and convert to drive LD output driver. The LD driver is also controlled by burst-enable signal BENN/BENP. The polarity of control can be configured. The laser driver includes differential modulation outputs and DC bias control output. The setting of output power level is controlled through automatic power control loop and is configurable by MCU. The output can be connected to Laser diode either by AC or DC coupled. The transmit path can be enabled or disabled by TXEN signal.

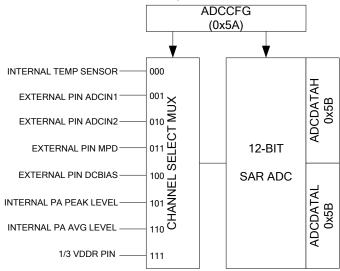

The on-chip MCU is the flexibility and versatility of controlling and configurations of fiber module design. Almost all configurations and parameters of the PA and LD driver parameters and can be controlled by MCU through software. The 12-bit ADC associated with MCU can be used to acquire various internal and external analog signals such on-chip temperature sensor and reference voltages. The MCU has 2K boot ROM and 2K SRAM for program storage which can meet the need of application of SFP/PON, Also the boot ROM is responsible for uploads the user program from external serial EEPROM(with capacity of 2k 4k 8k), The I<sup>2</sup>C slave interface also serves as ISP/IAP interface as well as SFP/SFF DMI function.

CS6721 integrates essential building blocks for Fiber module design. The integration of MCU allows precision control to tailor various module applications and facilitates configuration and automatic calibration in the manufacturing process. Using CS6721, the module can achieve low cost and high performance and can be applied in FTTH, BPON, GEPON, and GPON.

#### **APPLICATIONS**

♦ SONET/SDH, FTTH, GEPON, GPON

## **FEATURES**

#### Post Amplifier

- ◆ 1.25GBPS 2.5GBPS

- → -3dB bandwidth 50KHz 2GHz

- 2mV sensitivity

- ♦ On-chip offset cancellation

- Programmable signal detect level and hysteresis

- Programmable LOS function and Power detection

- SD control

- Peak/ADC control

- External Monitor/ADC control

- ♦ Programmable power down

- ◆ CML output

#### LD Driver

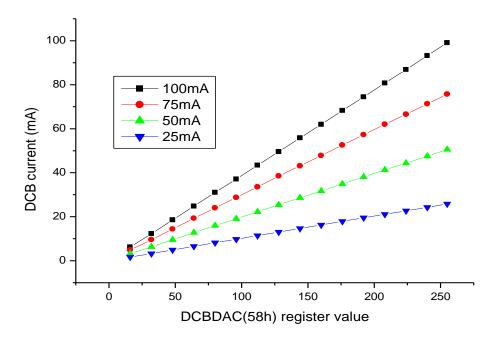

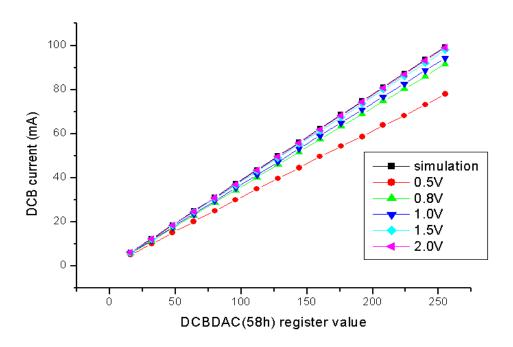

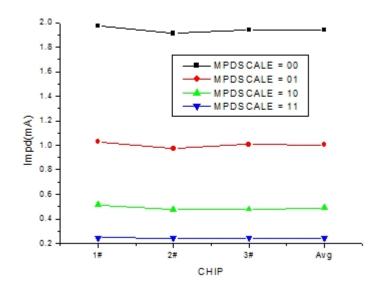

- Programmable bias current (up to 100mA)

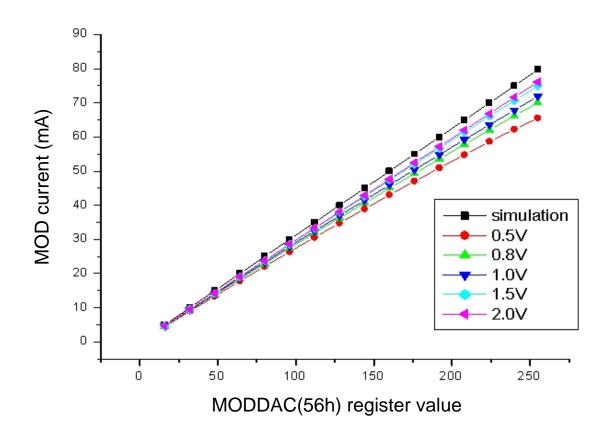

- Programmable modulation current (up to 80mA)

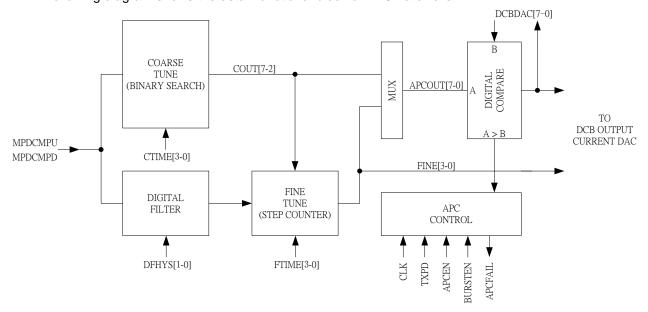

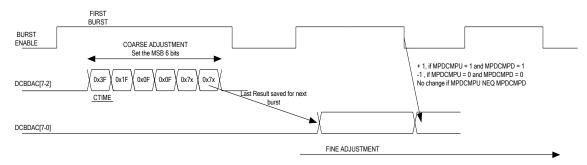

- Digital automatic power control loop

- Fast acquisition of laser power < 3 bursts</li>

- Programmable loop time constant

- Update only at burst-off state

- Loop monitoring by MCU

- ♦ Rise/Fall time < 200psec</li>

- ♦ Burst or continuous mode compatible

- ◆ Programmable polarity and FAIL status

- DCBIAS fail

- MPD fail

- APC fail

- Programmable power down and TX enable/disable function

- Laser power monitor and burst-on monitor

## Micro Controller (MCU)

- ♦ RISC CPU 12.5MHz

- 2K Program ROM for Boot

- 2K Program SRAM for user program

- Watchdog timer

- Low voltage reset

- I<sup>2</sup>C master for EEPROM program upload and data storage

- ♦ I<sup>2</sup>C slave for host ISP/IAP and DMI

- Two level password protection for A0/A2 access

- Support software TX\_DISABLE

- Burst Counter

- A0/A2 or B0/B2 configurable

- ♦ 8-Channel 12-bit ADC

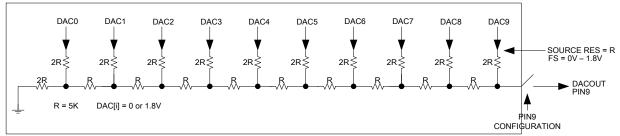

- ♦ 10-bit R2R DAC

- ♦ On-chip temperature sensor

#### General

- Low power consumption (300mW)

- ♦ Single 3.3V supply with on-chip regulator

- ◆ Extended temperature range -40°C ~ +85°C

- RoHS compliance package

## **BLOCK DIAGRAM**

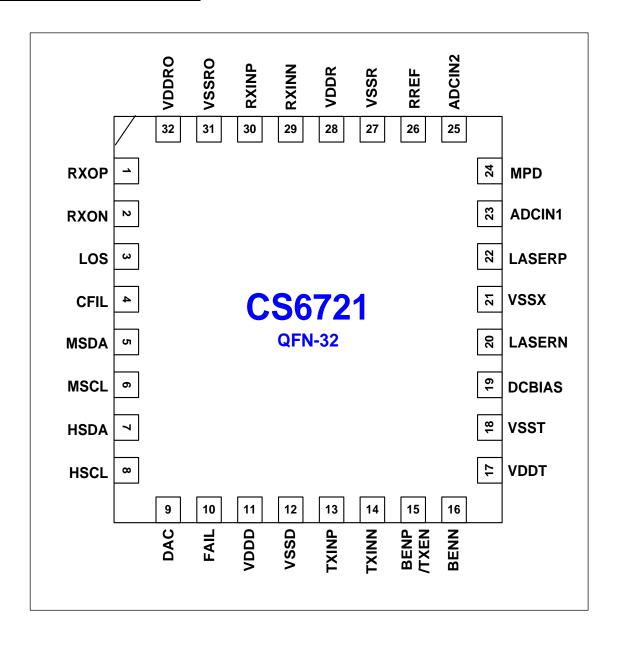

## **PIN CONNECTION DIAGRAM**

## **PIN DESCRIPTION**

| NAME  | PIN# | TYPE      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RXOP  | 1    | A, OUT    | Post Amplifier Positive Data Output. This is a CML output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RXON  | 2    | A, OUT    | Post Amplifier Negative Data Output. This is a CML output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

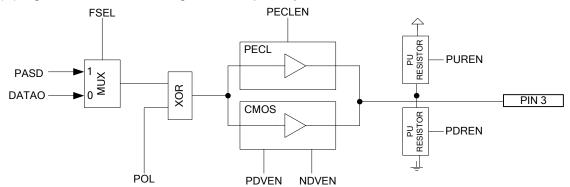

| LOS   | 3    | AD, IO    | Loss of Signal. This pin can be configured in CMOS, OD, or PECL output. It can also can be configured as an GPIO pin to the MCU.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

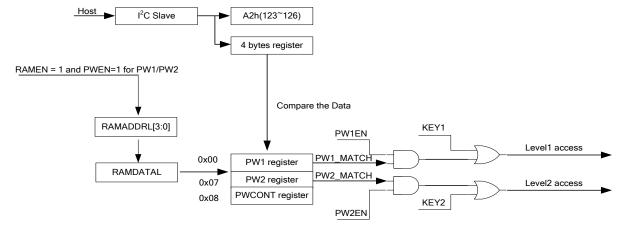

| CFIL  | 4    | Р         | Internal 1.8V regulator output. The regulator supplies internal analog circuits and digital core logic. A good decoupling should be connected from this pin to VSS, typically 0.1uF in parallel with 10uF.                                                                                                                                                                                                                                                                                                                                                        |

| MSDA  | 5    | D, OD, IO | Master Serial Interface Data. This pin is connected to the data signal of external 24C32 EEPROM for application program and calibration data. It is an open-drain I/O and an external pull-up resistor is required.                                                                                                                                                                                                                                                                                                                                               |

| MSCL  | 6    | D, O, IO  | Master Serial Interface Clock. This pin is connected to the clock signal of external 24C32 EEPROM for application program and calibration data. This is output only. This pin is also used to configure whether Slave I <sup>2</sup> C address as A0/A2/AC or B0/B2/BC. If an external pull-up resistor is present, the Slave I <sup>2</sup> C is configured as A0/A2/AC. If an external pull-down resistor is present, the slave I <sup>2</sup> C slave is configured as B0/B2/BC. The evaluation of A0/A2/AC and B0/B2/BC is done at the end of power-on reset. |

| HSDA  | 7    | D, OD, IO | Host Serial Interface Data. This pin is connected to host data line for performing DMI as well calibration and in system programming. It is an open-drain I/O and an external pull-up resistor is required.                                                                                                                                                                                                                                                                                                                                                       |

| HSCL  | 8    | D, OD, IO | Host Serial Interface Clock. This pin is connected to host data line for performing DMI as well calibration and in system programming. It is an open-drain I/O and an external pull-up resistor is required.                                                                                                                                                                                                                                                                                                                                                      |

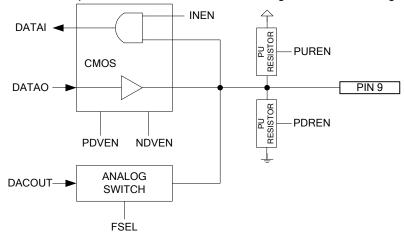

| DAC   | 9    | AD, IO    | DAC Output. This pin is connected to the on-chip R2R DAC output. The DAC has high source impedance. This pin can also be configured as a GPIO pin to the MCU and used for enable/disable control.                                                                                                                                                                                                                                                                                                                                                                 |

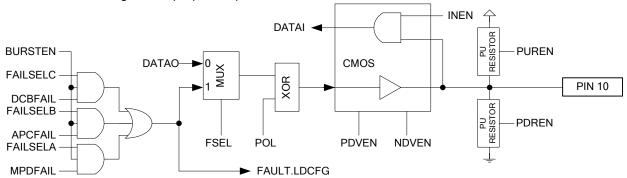

| FAIL  | 10   | D, IO     | FAIL Status Output. This pin is connected to the hardware fail status. This pin can also be configured as a GPIO pin to the MCU.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VDDD  | 11   | Р         | Digital Circuit Supply 3.3V. This pin should be connected to external 3.3V supply with good decoupling to VSSD.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VSSD  | 12   | G         | Digital Circuit Ground 0V. This pin connects to internal digital circuit ground and should have good decoupling to VDDD.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| TXINP | 13   | A, I      | Transmit Data Positive. This is positive of differential transmit data signals. This pin is internally biased to PECL level through 10K resistor.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TXINN | 14   | A, I      | Transmit Data Negative. This is negative of differential transmit data signals. This pin is internally biased to PECL level through 10K resistor.                                                                                                                                                                                                                                                                                                                                                                                                                 |

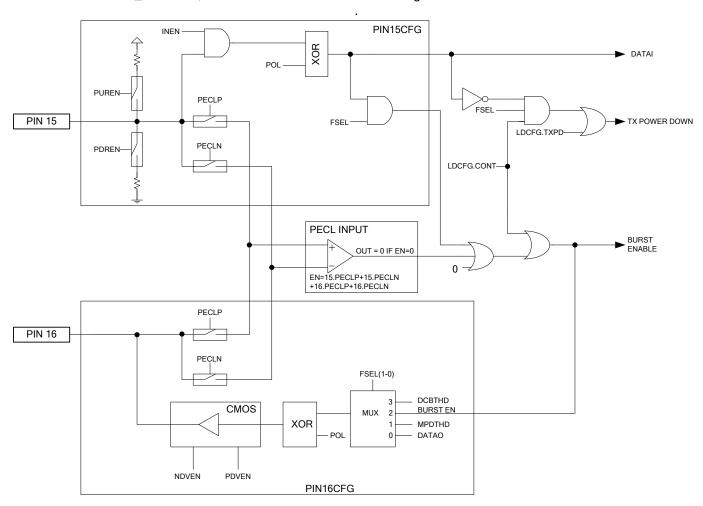

| BENP  | 15   | AD, I     | Burst Enable Positive. This pin is burst-enable control and can be in single-ended PECL or CMOS level, or as differential PECL mode with BENN pin. In PECL mode, the pin is internally biased to PECL level through a 10K resistor. This pin can also be configured as a GPI pin to the MCU and used for transmit enable/disable control or other digital input.                                                                                                                                                                                                  |

| BENN  | 16   | AD, I     | Burst Enable Negative. This pin is burst-enable control and can be in single-ended PECL or CMOS level, or as differential PECL mode with BENP pin. In PECL mode, the pin is internally biased to PECL level through a 10K resistor. This pin can also be configured as a GPO pin to the MCU and can be used for Laser Warning status.                                                                                                                                                                                                                             |

| VDDT  | 17   | Р         | 3.3V supply for transmit output driver. Should have good decoupling to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| NAME   | PIN# | TYPE  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                       |

|--------|------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |      |       | VSST. VDDT is an independent power supply that only supplies to DCB and MOD driver. When VDDT drops below VDDR-1V, the transmit path is automatically disabled.                                                                                                                                                                                                   |

| VSST   | 18   | G     | LD DC Bias Driver Circuit Ground 0V. This pin connects to the ground of the Bias current source and should have good decoupling to VDDT.                                                                                                                                                                                                                          |

| DCBIAS | 19   | A, O  | LD DC Bias Current Output. This pin sinks a DC bias current for the laser diode. The current sink is controlled by APC loop or can be set by MCU directly. In burst-mode, the current sink is turned-off during burst disable state.                                                                                                                              |

| LASERN | 20   | A, O  | LD AC Modulation Current Negative Output. This pin switches modulation current depending on the TXINP and TXINN and the polarity can be controlled. The current is programmable by MCU.                                                                                                                                                                           |

| VSSX   | 21   | G     | LD AC Modulation Driver Circuit Ground 0V. This pin connects to the ground of the modulation current source and should have good decoupling to VDDT as well supply connecting to laser.                                                                                                                                                                           |

| LASERP | 22   | A, O  | LD AC Modulation Current Positive Output. This pin switches modulation current depending on the TXINP and TXINN and the polarity can be controlled. The current is programmable by MCU.                                                                                                                                                                           |

| ADCIN1 | 23   | A, IO | ADC Input Channel 1. This pin is connected to internal ADC channel 1. Typically, this pin can be used to connect to an external temperature sensor to determine the module temperature. Under this mode, a programmable sensor DC bias current can be turned-on and connected.                                                                                    |

| MPD    | 24   | A, I  | Power Monitor Diode Input. This pin should connect to the power monitor diode of the laser. An internal programmable current source is connected to this pin for setting the laser power under APC mode.                                                                                                                                                          |

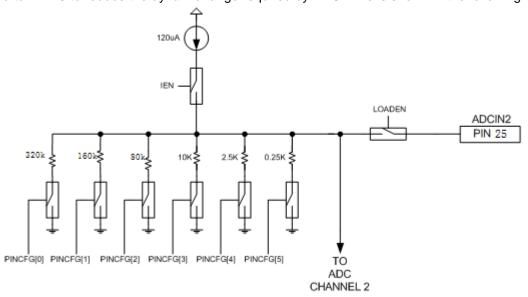

| ADCIN2 | 25   | A, I  | ADC Input Channel 2. This pin is connected to internal ADC channel 2.                                                                                                                                                                                                                                                                                             |

| RREF   | 26   | A, I  | Current Reference Setting Resistor. An external precision 10K Ohm resistor should be connected between this pin and VSSR. The resistor should be placed as close as possible to the device.                                                                                                                                                                       |

| VSSR   | 27   | G     | Analog and Receive Path Circuits Ground 0V. This pin connects to circuit grounds of the reference and receive path. This pin should have good decoupling to VDDR. These are very sensitive circuit and thus should be isolated from transmit supply to avoid board-level crosstalk.                                                                               |

| VDDR   | 28   | Р     | Analog and Receive Path Circuits Supply 3.3V. An external very clean and noise free 3.3V should be connected to this pin. This pin connects to circuit grounds of the reference and receive path. This pin should have good decoupling to VDDR. These are very sensitive circuit and thus should be isolated from transmit supply to avoid board-level crosstalk. |

| RXINN  | 29   | A, I  | Post Amplifier Negative Input. This pin is typically connected to PIN-TIA through AC coupling. This pin is internally biased. The AC coupling capacitor and internally bias resistor (10K) set the 3dB low frequency.                                                                                                                                             |

| RXINP  | 30   | A, I  | Post Amplifier Positive Input. This pin is typically connected to PIN-TIA through AC coupling. This pin is internally biased. The AC coupling capacitor and internally bias resistor (10K) set the 3dB low frequency.                                                                                                                                             |

| VSSRO  | 31   | G     | Receive Output Buffer Ground 0V. This pin connects to circuit grounds of the receive output buffer. This pin should have good decoupling to VDDRO.                                                                                                                                                                                                                |

| VDDRO  | 32   | Р     | 3.3V supply for the receive output buffers. Should have good decoupling to VSSRO                                                                                                                                                                                                                                                                                  |

## **FUNCTIONAL DESCRIPTION**

CS6721 combined three main functional blocks: Post Amplifier, Laser Driver, and Micro Controller. This combination allows significant enhancement over conventional design that offers flexibility and cost-saving through application software programming. Using external EEPROM as storage for program and data storage, the application software can designed to precision control of the parameters of the PA and LD driver and compensate for temperature variation and device fluctuations. The following section describes the functions of each block. Extensive descriptions on MCU programming and its SFR (Special Function Register) controlling on-chip peripherals are described in details.

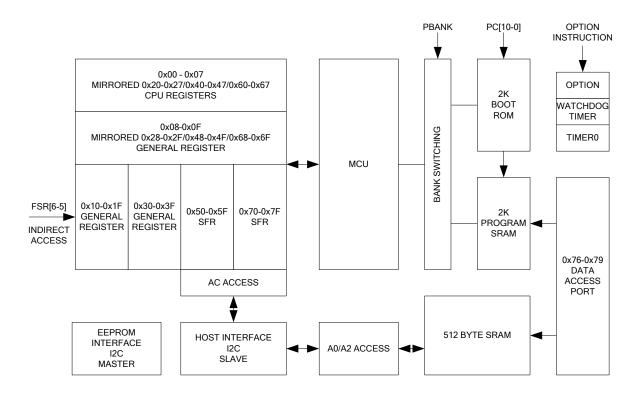

## 1. MCU and Digital Peripherals

The MCU is an 8-bit CPU with 12-bit wide instructions. The instruction of the CPU is listed in the appendix, and the block diagram is shown below.

#### 1.1 Program Memory and Space

The native addressing space of the MCU is 2K and can be bank-switched between two 2K spaces, one for on-chip ROM, and one for on-chip program SRAM. The MCU will execute the boot ROM after reset as PBANK is cleared to 0 at reset. The on-chip program SRAM is actually a two-port structure, and the content of the program SRAM can be written by CPU through special function registers using data/address port manipulations. The boot-ROM uses this feature to upload application program from the external EEPROM into the program SRAM, and then switches PBANK to 1 turning over the CPU control to application program.

Also, after reset and boot loaded procedure, the program counter is loaded with 0x000. For writing program in assembly language, the program needs to start at 0x000. In C programming, the main program also needs to be located at 0x000.

## 1.2 Register Map and Definitions

0x00 - 0x07 are CPU registers and are mirrored to 0x20-0x27, 0x40-0x47, and 0x60-0x6F. This space can be accessed using direct or indirect addressing mode.

0x08 - 0x0F are general-purpose data registers and are mirrored to 0x28-0x2F, 0x48-0x4F, and 0x60-0x6F. This space can be accessed using direct or indirect addressing mode.

0x10-0x1F and 0x30-0x3F are also general-purpose data register, and 0x50-0x5F, 0x70-0x7F are special function registers. These spaces are bank-switched by FSR[6-5]. 0x50 to 0x5F are special function registers that control the analog peripherals. 0x70 to 0x7F are special function registers that control on-chip digital peripherals. Both of these two ranges can also be accessed by the Host I<sup>2</sup>C slave interface. This allows host to directly control the analog peripherals in the calibration phase and perform in-system-programming of the external EEPROM.

## 1.3 CPU Registers

## INDF (0x00) Index Data Port R/W (0x00000000)

|       | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| READ  | INDF7 | INDF6 | INDF5 | INDF4 | INDF3 | INDF2 | INDF1 | INDF0 |

| WRITE | INDF7 | INDF6 | INDF5 | INDF4 | INDF3 | INDF2 | INDF1 | INDF0 |

INDF is not a physical register. It functions as a data port to read and write data in indirect address mode. The indirect address mode uses FSR[6-0] for register address where FSR[6-5] are used to do bank select.

#### TMR (0x01) Timer Register R/W (0x00000000)

|       | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| READ  | TMR7  | TMR6  | TMR5  | TMR4  | TMR3  | TMR2  | TMR1  | TMR0  |

| WRITE | TMR7  | TMR6  | TMR5  | TMR4  | TMR3  | TMR2  | TMR1  | TMR0  |

TMR is an 8-bit up and wrap-over counter. CPU can read and write this location to set or clear the counter. The configurations of the timer, such as pre-scaler, and count/stop are through OPTION register using OPTION instruction. The overflow status of the timer can be obtained from the STATUS register.

#### PCL (0x02) Program Counter Low Byte R/W (0x00000000)

|       | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| READ  | PCL7  | PCL6  | PCL5  | PCL4  | PCL3  | PCL2  | PCL1  | PCL0  |

| WRITE | PCL7  | PCL6  | PCL5  | PCL4  | PCL3  | PCL2  | PCL1  | PCL0  |

PCL register is the low byte of the program counter. Writing to this register will cause the CPU to branch into new location. Also instruction that modifies PCL will cause PC[8] to be cleared to 0. This also includes CALL instruction.

## STATUS (0x03)CPU Status Register R/W (0x00000000)

|       | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| READ  | PBANK | PA1   | PA0   | WON   | TON   | Z     | DC    | С     |

| WRITE | PBANK | PA1   | PA0   | WON   | TON   | Z     | DC    | С     |

PBANK

This bit controls the program memory bank select. This bit is cleared to 0 after reset and selecting the on-chip Boot ROM. This bit is set to 1 to select the on-chip program SRAM.

PA1

This bit reflect the program counter's 11<sup>th</sup> bit, PC[10]. Writing to this bit will cause the CPU to branch to a new location.

PA0

This bit reflect the program counter's 10<sup>th</sup> bit, PC[9]. Writing to this bit will cause the CPU to branch to a new location. PA1 and PA2 are used together with GOTO (Unconditional Branch) instruction to perform long jump.

WON

This bit is set and latched by the watchdog timer when WDT time out (overflow) occurred.

This bit must be cleared by software.

TON This bit is set and latched by the 8-bit timer when timer time out (overflow) occurred. This

bit must be cleared by software.

Z This bit reflects the zero status of previous logic or arithmetic operations of CPU.

DC This bit reflects the digit carry (4th bit carry) status of previous ADDWF, SUBWF arithmetic

operations of CPU.

C This bit reflects the carry status of previous ADDWF, SUBWF, RRF, RLF arithmetic

operations of CPU.

## FSR (0x04) Indirect Register Access Address Register R/W (0x00000000)

|       | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| READ  | -     | FSR6  | FSR5  | FSR4  | FSR3  | FSR2  | FSR1  | FSR0  |

| WRITE | -     | FSR6  | FSR5  | FSR4  | FSR3  | FSR2  | FSR1  | FSR0  |

FSR[6-5] These two bits are bank select bits for register bank.

FSR[4-0] These bits are used for indirect address pointer for register operation. The data port of the

indirect access is INDF.

#### PORTA, PORTB, PORTC (0x05, 0x06, 0x07) Port A, B, C Register R/W (0x00000000)

|       |       |       |       |       |       | •     |       |       |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|       | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

| READ  | -     | -     | -     | -     | -     | -     | -     | -     |

| WRITE | -     | -     | -     | -     | -     | -     | -     | -     |

In CS6721, PORT A, B, and C are not used. Therefore, these registers can be used as general-purpose data registers. There are also several implicit registers associated with the MCU, W, TRIS, OPTION, and WDT. W is the working register where ALU operand and result are stored. TRIS is the PORT A, PORT B, and PORT C IO configuration control. Since PORT A, B, and C are not used, so TRIS register and TRIS instruction will have no effect.

OPTION register is write-only and only accessible through "OPTION" instruction which transfer W into OPTION register. The OPTION register is defined as following.

#### OPTION (NA) Option Register W (0x00000000)

|       | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| READ  | -     | -     | -     | -     | -     | -     | -     | -     |

| WRITE | TEN   | TPS2  | TPS1  | TPS0  | WEN   | WPS2  | WPS1  | WPS0  |

TEN Set this bit to 1 to allow Timer to count. Set this bit to 0 will stop the counting of the Timer.

The Timer will remain the current counting value when stopped.

TPS[2-0] These bits determine the pre-scaling factor of the Timer clock.

000 = SYSCLK

001 = SYSCLK/2

010 = SYSCLK/4

011 = SYSCLK/8

100 = SYSCLK/16

101 = SYSCLK/32

110 = SYSCLK/64

111 = SYSCLK/128

WEN Set this bit to 1 to allow Watchdog Timer to count. Set this bit to 0 will stop the counting of

the Watchdog Timer. WDT is always cleared at the transition from disable to enable state.

WPS[2-0] These bits determine the pre-scaling factor of the Watchdog Timer clock.

000 = SYSCLK/2

001 = SYSCLK/4

010 = SYSCLK8

011 = SYSCLK/16

100 = SYSCLK/32

101 = SYSCLK/64

110 = SYSCLK/128

111 = SYSCLK/256

WDT is the Watchdog Timer that can only be cleared using "CLRWDT" instruction. WDT is a 16-bit counter with pre-scaling defined in the OPTION register.

## 2. System Digital Peripherals and Its Registers

This section describes the system digital peripherals such as I<sup>2</sup>C slave for host communication and it's associated SFP 2-port RAM, and I<sup>2</sup>C master for EEPROM interface, and the access to on-chip 2K program SRAM.

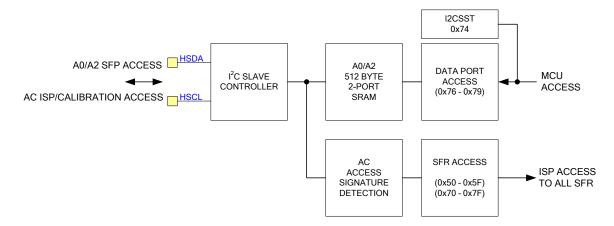

## 2.1 <u>I<sup>2</sup>C Slave Controller</u>

The purpose of on-chip I²C Slave has several usages. Its main purpose from fiber equipment view is SFP access to allow DMI information to be passed to host. However, it is also important purpose that I²C slave is used for parameter calibration and in-system-programming during module manufacturing. The I²C slave is implemented in hardware and the following block diagram shows the implementations. The hardware is implemented using synchronous logic thus require system clock to be running. The system clock needs to be higher than 8X higher than the I²C speed. For example, if I²C has maximum of 100K bit/second, then SYSCLK needs to be set higher than 800KHz.

For normal condition after system reset, the I<sup>2</sup>C slave will respond to only A0 and A2 access requests. These requests will be passed to the on-chip 512-byte 2-port SRAM partitioned into two pages. The contents of the 2-port SRAM is uploaded and updated by the MCU through application software to meet SFP DMI requirements. The write-protection of A0/A2 access is default on which only allow modification by the host in the range of 128 to 147 of A2 page. This write-protection can be turned-off by application program.

MCU access the 2-port SRAM through a data port using RAMADDRH (0x76) and RAMADDRL(0x77) to specify the 2-port SRAM address, and then perform read/write operation through RAMDATAL(0x79) SFR locations.

There is arbitration logic to resolve contention between Host A0/A2 access and MCU access. In the contention, the access from Host has higher priority and MCU is stalled. That means Host will always get the access at higher priority. To ease the programming, I²C slave provide status to indicate host access, and also status to indicate A0/A2 modification. It is upon application program to determine if the modification should be permanent and update the data into the EEPORM.

The I<sup>2</sup>C Slave also provides a backdoor that Host can perform calibration and in-system-programming for installing application program on a blank external EEPROM. The backdoor is open upon receiving a sequence of

BIT 0

BIT 7

byte write commands to address A0:80. The write data sequence is 0x00 - 0xAA - 0x55 - 0xAC - "A" - "C" - "E" - "S" - "S". After the slave completes detection of this exact sequence, the slave will start to respond to address AC. The sequence must be exact and any violation will cause the detection to be restarted. After AC access is turned on, any additional or further I²C host access to address A0:80 will cause the backdoor to be closed again. During the AC access, the host has full control (read and write) of all the Special Function Register while the CPU is put into idle. As the result, in this backdoor access, the host can manipulate ADC and measure the VDD18 or the present temperature sensor reading to establish parameter calibrations. The host can also manipulate the I²C master command and data registers, thus transfer application program and look-up tables to the connected external EEPROM. After these, host can also issue reset command to allow CS6721 to resume normal operations. For rare design requirement, AC access mode can also be used so that an external MCU can control CS6721's on-chip analog functional blocks, for example, an extremely large application program space is required.

BIT 4

BIT 2

BIT 1

BIT 3

### I2CSCS (0x74) I2C Slave Configuration and Status Register RW (0x00000000)

BIT 5

BIT 6

| READ  | I2CSRST                                                                                                                                                                     | A0HMST                       | INFILEN                                                                                                                 | A0LMST                             | A2HMST         | A2LMST         | ACST            | BUSY                             |        |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------------|----------------|-----------------|----------------------------------|--------|--|--|--|

| WRITE | I2CSRST                                                                                                                                                                     | A0HMST                       | MST   INFILEN   A0LMST   A2HMST   A2LMST                                                                                |                                    |                |                |                 |                                  |        |  |  |  |

| 120   | SRST                                                                                                                                                                        | Set this bit                 | to 1 will cau                                                                                                           | se the I2C sla                     | ave controlle  | r to reset. Se | t this bit to 0 | for normal                       | •      |  |  |  |

|       |                                                                                                                                                                             | operations                   |                                                                                                                         |                                    |                |                |                 |                                  |        |  |  |  |

| A0    | HMST                                                                                                                                                                        |                              |                                                                                                                         |                                    |                |                |                 | was modified                     |        |  |  |  |

|       |                                                                                                                                                                             |                              |                                                                                                                         | •                                  | alid if the co | rresponding    | password is     | valid. This b                    | It     |  |  |  |

| INIT  | -II                                                                                                                                                                         | must be cleared by software. |                                                                                                                         |                                    |                |                |                 |                                  |        |  |  |  |

| IINI  | FILEN                                                                                                                                                                       |                              | Set this bit to 1 will enable a pulse filter on the SDA input. The filter filters out any pulse less than 50nsec width. |                                    |                |                |                 |                                  |        |  |  |  |

| ΔΩ    | LMST                                                                                                                                                                        |                              | This bit is set by the I <sup>2</sup> C slave hardware after any of A0 location 128 to 255 was modified                 |                                    |                |                |                 |                                  |        |  |  |  |

| 710   | LIVIOT                                                                                                                                                                      |                              |                                                                                                                         |                                    |                |                |                 | l is valid. Thi                  |        |  |  |  |

|       |                                                                                                                                                                             |                              | must be cleared by software.                                                                                            |                                    |                |                |                 |                                  |        |  |  |  |

| A2    | HMST                                                                                                                                                                        | This bit is                  | set by the I <sup>2</sup> 0                                                                                             | Slave hardv                        | vare after an  | y of A2 locat  | tion 128 to 2   | 55 was modi                      | fied   |  |  |  |

|       |                                                                                                                                                                             | •                            |                                                                                                                         | •                                  | valid if the o | corresponding  | g password i    | s valid. This                    | bit    |  |  |  |

|       |                                                                                                                                                                             |                              | eared by sof                                                                                                            |                                    |                |                |                 |                                  |        |  |  |  |

| A2    | LMST                                                                                                                                                                        |                              |                                                                                                                         |                                    |                |                |                 | was modified                     |        |  |  |  |

|       |                                                                                                                                                                             |                              |                                                                                                                         | •                                  |                |                |                 | alid. This bi                    |        |  |  |  |

|       |                                                                                                                                                                             |                              |                                                                                                                         |                                    |                |                | t if the host a | altered A2(11                    | U) bit |  |  |  |

| 4.0   | 6 for controlling TX_DISABLE software control function.                                                                                                                     |                              |                                                                                                                         |                                    |                |                |                 |                                  |        |  |  |  |

| AC    | ACST This bit is read-only and reflects the backdoor status. It is set to 1 by the hardware if AC access mode is on. It is automatically cleared if the backdoor is closed. |                              |                                                                                                                         |                                    |                |                |                 |                                  |        |  |  |  |

| DU    | 10)/                                                                                                                                                                        |                              |                                                                                                                         |                                    | •              |                |                 | :-                               |        |  |  |  |

| BU    | ISY                                                                                                                                                                         |                              | •                                                                                                                       | d set to 1 by<br>I wait after it i |                |                |                 | access is on-<br>plication first |        |  |  |  |

The I<sup>2</sup>C slave module supports the following transaction modes: single-write, page-write, single-read, and page-read. The formats of these four modes are shown below and the host must follow these formats for access. The byte address in the page mode is automatically incremented for each byte access.

check this bit status before access the A0/A2 2-port SRAM through the data port.

Please note the I2C slave can be configured to respond to A0/A2/AC or B0/B2/BC access. This is useful if two CS6721 are connected in parallel on the slave I<sup>2</sup>C bus and can be separately accessed by the host. The configuration is determined at the exit of power-on reset and if MSCL pin has external pull-up resistor for A0/A2/AC, and external pull-down resistor for B0/B2/BC.

## 2.2 DATA Port Access to A0/A2 SRAM and Program SRAM

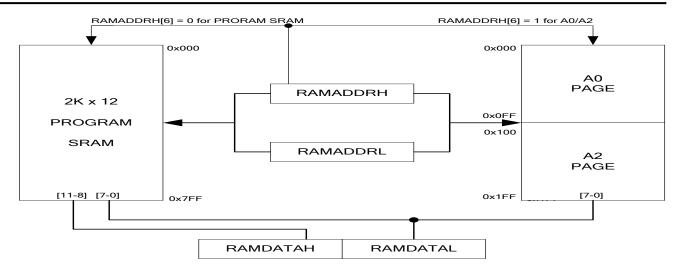

This section describes the read/write accesses from MCU to the A0/A2 2-port SRAM and to the 2Kx12 Program SRAM. Both accesses share the same address point SFR and data buffer SFR. The block diagram is shown in the following figure.

#### RAMADDRH (0x76) RAM Address Pointer High Byte RW (0x00000000)

|       | , ,   |       |       | <u>, , , , , , , , , , , , , , , , , , , </u> |       |        |       |       |

|-------|-------|-------|-------|-----------------------------------------------|-------|--------|-------|-------|

|       | BIT 7 | BIT 6 | BIT 5 | BIT 4                                         | BIT 3 | BIT 2  | BIT 1 | BIT 0 |

| READ  | RAMEN | A0A2  | -     | -                                             | PWEN  | ADDR10 | ADDR9 | ADDR8 |

| WRITE | RAMEN | A0A2  | -     | -                                             | PWEN  | ADDR10 | ADDR9 | ADDR8 |

RAMEN A0A2 Set this bit to 1 to allow data port to operations. Set this bit to 0 to disable the access. Set this bit to 1 to direct the operation to the A0/A2 512-byte SRAM. Set this bit to 0 to direct the operation to the 2K x 12 program SRAM.

PWEN Set this bit to 1 to direct the operation to the PW1(4 bytes), PW2(4 bytes) and PWCONT

register address. The address is the RAMADDRL[3:0].

Setting the PW2 password to FFFFh will disable the password protection function. Set this

bit to 0 to disable the access.

ADDR[10-8] Address bit 10, 9, 8 of the pointer. For A0/A2 access, A10 and A9 are ignored.

## RAMADDRL (0x77) RAM Address Pointer Low Byte RW (0x00000000)

|       | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| READ  | ADDR7 | ADDR6 | ADDR5 | ADDR4 | ADDR3 | ADDR2 | ADDR1 | ADDR0 |

| WRITE | ADDR7 | ADDR6 | ADDR5 | ADDR4 | ADDR3 | ADDR2 | ADDR1 | ADDR0 |

This register contains the low byte of the address pointer for the data port operations.

## RAMDATAH (0x78) RAM Data Port High Byte RW (0x00000000)

|       | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3  | BIT 2  | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|--------|--------|-------|-------|

| READ  | -     | -     | -     | -     | DATA11 | DATA10 | DATA9 | DATA8 |

| WRITE | -     | -     | -     | -     | DATA11 | DATA10 | DATA9 | DATA8 |

This is a pseudo register. Operation on this register yields the execution to the SRAM location pointed by the RAM address register. For program SRAM access, only the lower four bits are used. For A0/A2 access, this register is not used and ignored.

## RAMDATAL (0x79) RAM Data Port Low Byte RW (0x00000000)

|       | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| READ  | DATA7 | DATA6 | DATA5 | DATA4 | DATA3 | DATA2 | DATA1 | DATA0 |

| WRITE | DATA7 | DATA6 | DATA5 | DATA4 | DATA3 | DATA2 | DATA1 | DATA0 |

This is a pseudo register. Operation on this register yields the execution to the SRAM location pointed by the RAM address register.

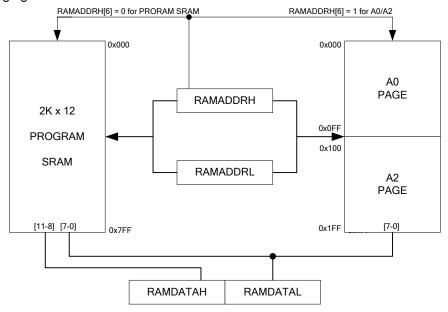

## PWDATA (0x00~0x07) PW1 and PW2 Data Register W (0x00000000)

|       | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| READ  | -     | -     | -     | -     | -     | -     | -     | -     |

| WRITE | DATA7 | DATA6 | DATA5 | DATA4 | DATA3 | DATA2 | DATA1 | DATA0 |

## PWCONT (0x08) Password Control Register W (0x00000000)

|       | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| READ  | -     | -     | -     | -     | -     | -     | -     | -     |

| WRITE | PW1EN | PW2EN | KEY1  | KEY2  | -     | -     | -     | -     |

PW1EN Set this bit to 1 to allow PW1 to operations. Set this bit to 0 to disable the hardware PW

function.

PW2EN Set this bit to 1 to allow PW2 to operations. Set this bit to 0 to disable the hardware PW

function.

KEY1 Set this bit to 1 to open Level 1 access by software. Set this bit to 0 to disable the access. KEY2 Set this bit to 1 to open Level 2 access by software. Set this bit to 0 to disable the access.

|    | ADDRESS RANGE                                          | READ | WRITE   | Note   |

|----|--------------------------------------------------------|------|---------|--------|

| A2 | 0~95 (Warning/Alarm Thresholds, Calibration Constants) | all  | PW2     |        |

|    | 96~110 (Diagnostic Monitor Data)                       | all  | PW2     |        |

|    | 110 (bit[6] Soft TX_Disable)                           | all  | PW1/PW2 | Note 1 |

|    | 111~119(Alarm flags, Warning flags)                    | all  | PW2     |        |

|    | 120~126(123~126:PW1 PW2 Access) (Note 1)               | NA   | all     | Note 2 |

|    | 127                                                    | all  | PW2     |        |

|    | 128~255                                                | all  | PW1     |        |

| A0 | 0~127; 128~255                                         | all  | PW2     |        |

Note 1: If PW1 is opened then only bit[6] soft TX\_DISABLE can be written. If PW2 is opened then whole byte can be written. Also note altering bit-6 does not set A2LMST status bit.

Note 2: A2 [120-126] are write-only. The write is into password register not into the I<sup>2</sup>C SRAM.

## 2.3 <u>I<sup>2</sup>C Master Controller</u>

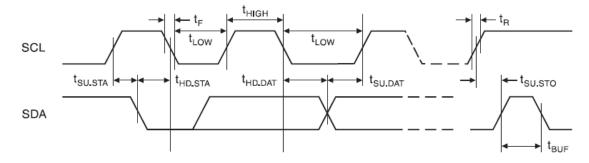

The I2C master controller provides the interface to I<sup>2</sup>C slave devices. The main purpose of I<sup>2</sup>C master in CS6721 is to control the external I<sup>2</sup>C EEPROM that is used to store the application program as well as configuration data and temperature look up tables. It can be programmed to operate with arbitration and clock synchronization to allow it to operate in multi-master configurations. The master uses MSCL and MSDA pins. The controller contains a built-in 8-bit timer to allow various I<sup>2</sup>C bus speed. Please note MSCL is an output only pin. MSCL is also used to configure the slave I<sup>2</sup>C address depending on the external pull-up or pull-down resistor configuration during the exit of power-on reset.

## I2CMTPRD (0x71) I<sup>2</sup>C Master SCL Clock Configuration RW (0x00000000)

|       | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| READ  | TP7   | TP6   | TP5   | TP4   | TP3   | TP2   | TP1   | TP0   |

| WRITE | TP7   | TP6   | TP5   | TP4   | TP3   | TP2   | TP1   | TP0   |

This register set the period time of I2C bus clock – SCL. The SCL period time is set according to SCLPERIOD = 8 \* (1 + I2CMTPRD)/SYSCLK

#### I2CMSA (0x72) I2C Master Slave Address Register RW (0x00000000)

|       | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| READ  | SA6   | SA5   | SA4   | SA3   | SA2   | SA1   | SA0   | RS    |

| WRITE | SA6   | SA5   | SA4   | SA3   | SA2   | SA1   | SA0   | RS    |

SA6 - SA0 defines the slave address the I<sup>2</sup>C master uses to communicate. RS bit determines if the next operation will be a RECEIVE (1) or SEND (0).

## I2CMBUF (0x73) I<sup>2</sup>C Master Data Buffer(0x00 RW (0x00000000)

|       | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| READ  | RD7   | RD6   | RD5   | RD4   | RD3   | RD2   | RD1   | RD0   |

| WRITE | TD7   | TD6   | TD5   | TD4   | TD3   | TD2   | TD1   | TD0   |

I2CMBUF functions as a transmit data register when written and as a receive data register when read. When written, TD will be sent on the bus by the next SEND or BURST SEND operations. TD7 is sent first. When read, RD contains the 8-bit data that has been received the bus due to the last RECEIVE or BURST RECEIVE operations.

## I2CMCR (0x70) I<sup>2</sup>C Master Status and Configuration RW (0x00000000)

| <br>  |       |       |       |       |       |       |       |

|-------|-------|-------|-------|-------|-------|-------|-------|

| BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

| READ  | -       | BUSBUSY | IDLE | ARBLOST | DATAACK | ADDRACK | ERROR | BUSY |

|-------|---------|---------|------|---------|---------|---------|-------|------|

| WRITE | INFILEN | I2CMRST | -    | HS      | ACK     | STOP    | START | RUN  |

INFILEN Set this bit to 1 will enable a analog filter that filters out pulse width less than 50nsec on

SDA and SCL lines.

I2CMRST Set this bit to 1 will reset the I2C Master Controller. All state machine and signal returns to

their idle mode. Set this bit to 0 for normal operations.

The I<sup>2</sup>C MCR register is used for setting control when it is written, and serve as the status when read. INFILEN is input pulse filtering control. When IFILEN is set, pulses shorter than 50 nsec on inputs of SDA and SCL are filtered out.

The START bit is used to generate START, or REPEAT START protocol. The STOP bit determines if the cycle will stop at the end of the data cycle or continue on to a burst. To generate a single read cycle, SA is written with the desired address, RS is set to 1, and I<sup>2</sup>C MCR is written with ACK=0, STOP=1, START=1, RUN=1 to perform the operation and then STOP. When the operation is completed (or aborted due to errors), I<sup>2</sup>C master generates an interrupt. The ACK bit must be set normally 1. This causes the controller to send an ACK automatically after each byte transaction. The ACK bit must be reset when set to 0 when the master is operated in receive mode and intend not to receive further data from the slave device.

The following table lists the permitted control bits combinations in master idle mode.

| HS | RS | ACK | STOP | START | RUN | OPERATIONS                                                                                       |

|----|----|-----|------|-------|-----|--------------------------------------------------------------------------------------------------|

| 0  | 0  | ı   | 0    | 1     | 1   | START condition followed by SEND. Master remains in TRANSMITTER mode                             |

| 0  | 0  | 1   | 1    | 1     | 1   | START condition followed by SEND and STOP                                                        |

| 0  | 1  | 0   | 0    | 1     | 1   | START condition followed by RECEICE operation with negative ACK. Master remains in RECEICER mode |

| 0  | 1  | 0   | 1    | 1     | 1   | START condition followed by RECEIVE and STOP                                                     |

| 0  | 1  | 1   | 0    | 1     | 1   | START condition followed by RECEIVE. Master remains in RECEIVER mode                             |

| 0  | 1  | 1   | 1    | 1     | 1   | Illegal command                                                                                  |

| 1  | 0  | 0   | 0    | 0     | 1   | Master Code sending and switching to HS mode                                                     |

The following table lists the permitted control bits combinations in master TRANSMITTER mode.

| HS | RS | ACK | STOP | START | RUN | OPERATIONS                                                                                                   |

|----|----|-----|------|-------|-----|--------------------------------------------------------------------------------------------------------------|

| 0  | -  | -   | 0    | 0     | 1   | SEND operation. Mater remains in TRANSMITTER mode                                                            |

| 0  | -  | -   | 1    | 0     | 0   | STOP condition                                                                                               |

| 0  | -  | -   | 1    | 0     | 1   | SEND followed by STOP condition                                                                              |

| 0  | 0  | -   | 0    | 1     | 1   | Repeated START condition followed by SEND.  Master remains in TRANSMITTER mode                               |

| 0  | 1  | -   | 1    | 1     | 1   | Repeated START condition followed by SEND and STOP condition                                                 |

| 0  | 1  | 0   | 0    | 1     | 1   | Repeated START condition followed by RECEIVE operation with negative ACK. Master remains in TRANSMITTER mode |

| 0  | 1  | 0   | 1    | 1     | 1   | Repeated START condition followed by SEND and STOP condition.                                                |

| 0 | 1 | 1 | 0 | 1 | 1 | Repeated START condition followed by RECEIVE. Master remains in RECEIVER mode. |

|---|---|---|---|---|---|--------------------------------------------------------------------------------|

| 0 | 1 | 1 | 1 | 1 | 1 | Illegal command                                                                |

The following table lists the permitted control bits combinations in master RECEIVER mode.

| HS | RS | ACK | STOP | START | RUN | OPERATIONS                                                                                                |  |  |

|----|----|-----|------|-------|-----|-----------------------------------------------------------------------------------------------------------|--|--|

| 0  | -  | 0   | 0    | 0     | 1   | RECEIVE operation with negative ACK. Mater remains in RECEIVE mode                                        |  |  |

| 0  | -  | -   | 1    | 0     | 0   | STOP condition                                                                                            |  |  |

| 0  | -  | 0   | 1    | 0     | 1   | RECEIVE followed by STOP condition                                                                        |  |  |

| 0  | -  | 1   | 0    | 0     | 1   | RECEIVE operation. Mater remains in RECEIVER mode                                                         |  |  |

| 0  | -  | 1   | 1    | 0     | 1   | Illegal command                                                                                           |  |  |

| 0  | 1  | 0   | 0    | 1     | 1   | Repeated START condition followed by RECEIVE operation with negative ACK. Master remains in RECEIVER mode |  |  |

| 0  | 1  | 0   | 1    | 1     | 1   | Repeated START condition followed by RECEIVE and STOP conditions                                          |  |  |

| 0  | 1  | 0   | 1    | 1     | 1   | Repeated START condition followed by RECEIVE. Master remains in RECEIVER mode                             |  |  |

| 0  | 0  | -   | 0    | 1     | 1   | Repeated START condition followed by SEND. Master remains in TRANSMITTER mode.                            |  |  |

| 0  | 0  | -   | 1    | 1     | 1   | Repeated START condition followed by SEND and STOP conditions.                                            |  |  |

All other control bits combinations not mentioned in the above three tables are NOP. In Master RECEIVER mode, STOP conditions should be generated only when after data negative ACK executed by Master, or address negative ACK executed by slave. Negative ACK here means SDA is pulled low during the acknowledge clock pulse.

I2CMCR when read reflect the status of the I<sup>2</sup>C master controller.

IDLE this bit indicates that I<sup>2</sup>C master is in the IDLE mode.

BUSY this bit indicates that I<sup>2</sup>C master is receiving or transmitting data, and other status bits are

not valid.

BUSBUSY this bit indicates that the external I<sup>2</sup>C bus is busy and access to the bus is not possible.

This bit is set/reset by START and STOP conditions.

ERROR this bit indicates that error occurred in the last operations. The errors include slave address

was not acknowledged, or transmitted data was not acknowledged, or the master controller

lost arbitration.

ADDRERR this bit indicates that the last operation slave address transmitted was not acknowledged.

DATAERR this bit indicates that the last operation data transmitted was not acknowledged.

ARBLOST this bit indicates that the last operation I<sup>2</sup>C master controller lost the bus arbitration.

## 2.4 System Reset Register

This register is used for either MCU or host to issue a system-wide reset to CS6721. Writing to SYSRESET (0x75) location with data content of "55" will cause the system reset after 1024 clock cycles.

## SYSRESET (0x75) System Reset Register WO (0x00000000)

|       | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| READ  | -     | -     | -     | -     | -     | -     | -     | -     |

| WRITE | -     | -     | -     | -     | -     | -     | -     | -     |

The effects of reset register and WDT reset is the same. Both resets will load all register with default value, then execute boot ROM procedure that loads the application program into SRAM and pass the control to the application program.

## 2.5 **Boot ROM Code and EEPROM Contents**

The on-chip ROM integrated three application: 1. Special application program by the user defined; 2. general purpose SFP/PON application program with DDM function. Romcode gets all data from the external EEPROM in this application; 3. general purpose SFP/EPON application program without the external EEPROM.

CS6721 has a 2K ROM for Boot and before code is executed, the ROMSEL (0x51) bit is tested first...

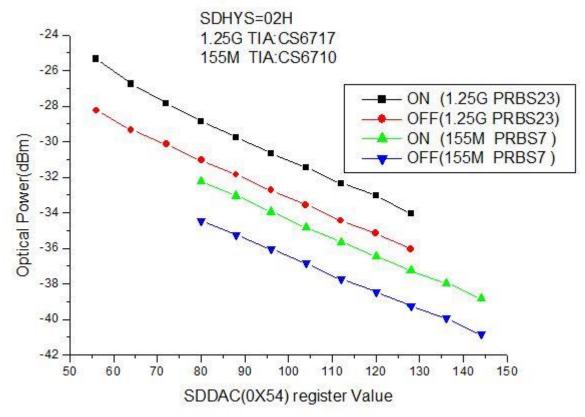

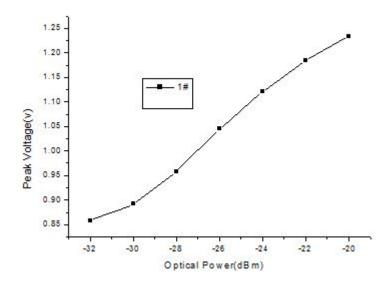

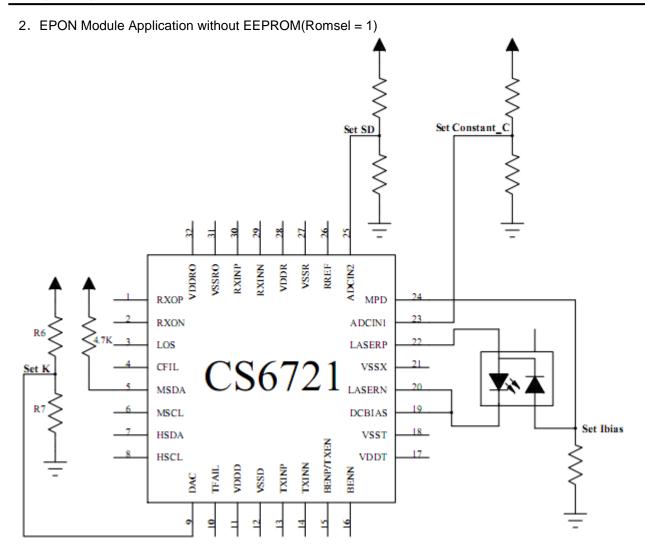

When ROMSEL=1, it means the commonly application of SFP/EPON without the external EEPROM, which includes: the setting of SDDAC through ADCIN2, adjustment of DCBBIAS by adjusting the resistance of MPD pin, temperature compensation of MODDAC through ADCIN1 and pin9, during this mode, DDM and open loop is invalid.

Unlike the situation above, when ROMSEL=0, the romcode will load Romheader from EEPROM first, and therefore determine which application be supported.

Romheader (stored in EEPROM) a 48 bytes table which ranges from 0x0000-0x002F is described as below:

|              | Ow.                       |                                                  | CS6721     | RomHeader (0x0000)                                                                                                                                                                                                       |

|--------------|---------------------------|--------------------------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADRE<br>EERF | ESS in                    | CONTENT                                          | SIZE       | DESCRPTION                                                                                                                                                                                                               |

|              | bit7 Application Solution |                                                  |            | bit7 = 0: uploads and execute the program of external EEPROM, bit0~bit6 was not concerned at this situation. bit7 = 1: executing the romcode, the last 16bytes of romheade (0020H ~ 002FH)can be used with other purpose |

|              | bit6                      | Temperature Compensation of APD  Open/Close loop |            | bit7 = 1&& bit6 = 1: adjust the APD voltage through PIN9 DACOUT 0~1.8V<br>bit7 = 1&& bit6 = 0: the voltage of APD is not adjustable                                                                                      |

|              | bit5                      |                                                  |            | bit7 = 1&& bit5 = 1: open loop of TX<br>bit7 = 1&& bit5 = 0: close loop of TX                                                                                                                                            |

| 0X0<br>(con  | bit4                      | Temperature Sensor<br>Selection                  |            | bit7 = 1&& bit4 = 1: internal temperature sensor<br>bit7 = 1&& bit4 = 0: external temperature sensor                                                                                                                     |

| trol<br>byte | bit3                      | Host write to A0/A2                              | 1<br>bytes | bit7 = 1&& bit3 = 1: allow host write the A0 A2,when the data updating of A0 A2 had been tested by romcode ,it will be stored in the EEPROM; bit7 = 1&& bit3 = 0: host is not allowed to write the A0 A2.                |

|              | bit2                      | DDM                                              |            | bit7 = 1&& bit2 = 1: DDM available<br>bit7 = 1&& bit3 = 0: DDM not available                                                                                                                                             |

|              | bit1                      | Voltage Protection                               |            | bit7 = 1&& bit2 = 1: shut off TX RX when voltage of VDDR is higher than 3.6;and TX RX are working properly when the voltage of VDDR is beyond 2.8 ~ 3.6V bit7 = 1&& bit3 = 0: TX RX are not shut off                     |

|              | bit0                      | Rise/Fall of APD<br>Compensation LUT             |            | bit7 = 1&& bit0 = 1: rise of APD temperature compensation LUT bit7 = 1&& bit0 = 0: fall of APD temperature compensation LUT                                                                                              |

|             |                 | CS6721 RomHeader                          | (48Bytes | s)                                                                                                                                                |  |  |

|-------------|-----------------|-------------------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|             |                 |                                           | SIZE     |                                                                                                                                                   |  |  |

| ADDRESS     | CONTENT         |                                           | (bytes)  | DESCRPTION                                                                                                                                        |  |  |

| 0X0001      | HIGH            | The starting address of                   | 2        |                                                                                                                                                   |  |  |

| 0X0002      | LOW             | application program                       | 2        |                                                                                                                                                   |  |  |

| 0X0003      | HIGHT           | Size of application                       | 2        | Maximum: 2KPutaa                                                                                                                                  |  |  |

| 0X0004      | LOW             | program                                   |          | Maximum:3KBytes                                                                                                                                   |  |  |

| 0X0005      | The CDC of one  | lication program                          | 2        |                                                                                                                                                   |  |  |

| 0X0006      | The CRC of app  | lication program                          |          |                                                                                                                                                   |  |  |

| 0X0007      | HIGH            | Starting address of DMI                   | 2        |                                                                                                                                                   |  |  |

| 0X0008 LOW  |                 | Starting address of DMI                   |          |                                                                                                                                                   |  |  |

| 0X0009      | HIGH            |                                           |          |                                                                                                                                                   |  |  |

| 0X000A      | LOW             | Size of DMI                               | 2        |                                                                                                                                                   |  |  |

| 0X000B HIGH |                 | Starting address of<br>SFP data           | 2        |                                                                                                                                                   |  |  |

| 0X000C LOW  |                 | SFF data                                  |          |                                                                                                                                                   |  |  |

| 0X000D HIGH |                 |                                           |          | 1≤ SFP size ≤512,The data size                                                                                                                    |  |  |

| 0X000E      | LOW             | SFP size                                  | 2        | stored in SFP from A0 to A2                                                                                                                       |  |  |

| 0X000F bit7 | Set MOD         |                                           | 1        | bit7=0: configuration the MOD by<br>ATC(see RomHeader 0x16 0x17)<br>bit7=1: MOD compensation by LUT                                               |  |  |

| 0X0010      | HIGH            |                                           |          | ·                                                                                                                                                 |  |  |

| 0X0011      | LOW             | Starting address of ADC temperature table | 2        | The data in temperature sensor table is the ADC of +85°C and ADC D-value of each gap compared with the former                                     |  |  |

| 0X0012      | Size of ADC tem | perature table                            | 1        | It represent the addressing space of temperature sensor, and the size can't be more than 127 with the situation of small EEPROM with DDM function |  |  |

| 0X0013      | Undefined       |                                           | 1        |                                                                                                                                                   |  |  |

| 0X0014      | HIGH            | Starting address of SD                    | 2        |                                                                                                                                                   |  |  |

| 0X0015      | LOW             | compensation table                        | 2        |                                                                                                                                                   |  |  |

| 0X0016      | Kratio          | Calculation of MOD                        | 2        | When 0x000F:BIT7=0 , MODDAC =                                                                                                                     |  |  |

| 0X0017      | CONSTANT_C      | Calculation of MOD                        |          | Kratio X DCBDAC/256 +CONSTANT_C                                                                                                                   |  |  |

| 0X0016      | HIGH            | Starting address of MOD compensation      | 2        | When 0x000F:BIT7=1 , 0X16&0X17 are used individually to Store the high                                                                            |  |  |

| 0X0017      |                 |                                           |          | and low byte of MOD compensation table                                                                                                            |  |  |

| 0X0018      | HIGH            | Starting address of                       |          | The starting address of MPD                                                                                                                       |  |  |

| 0X0019      | LOW             | DCB compensation table                    | 2        | compensation table in the close loop                                                                                                              |  |  |

| 0X001A      | HIGH            | Starting address of                       | _        |                                                                                                                                                   |  |  |

| 0X001B      | LOW             | APD compensation table                    | 2        |                                                                                                                                                   |  |  |

| 0X001C | HIGH              | Starting address of          | _  |                                              |  |  |

|--------|-------------------|------------------------------|----|----------------------------------------------|--|--|

| 0X001D | LOW               | register configuration table | 2  |                                              |  |  |

| 0X001E | Size of register  | configuration table          | 1  |                                              |  |  |

| 0X001F | CHECKSUM          |                              | 1  | Data CHECKSUM of EEPROM from 0X0000 ~ 0X001E |  |  |

| 0X0020 | HIGH              | Title of application         | 12 | ASCII characters                             |  |  |

| 0X002B | LOW               | program                      | 12 | ASON Characters                              |  |  |

| 0X002C | Varaian of applic | ection program               | 1  | ASCII characters                             |  |  |

| 0X002F | Version of applic | alion program                | 4  | ASCII CIIdidCleis                            |  |  |

|                                      |                                     |                   | - 44    | On-chip progran | n SRAM (12BIT)    |                   |

|--------------------------------------|-------------------------------------|-------------------|---------|-----------------|-------------------|-------------------|

| EEPROM address                       | EEPRO                               |                   | address | HIGH (4bit)     | LOW (8bit)        |                   |

| The last address of user program ——• | :                                   |                   | :       | :               | :                 |                   |

| :                                    | :                                   |                   | :       | :               | :                 |                   |

| :                                    | :                                   |                   | :       | :               | :                 |                   |