#### FEATURES

- Low Cost Solution Built-in 800V power BJT

- Quasi-Resonant Primary Side Regulation (QR-PSR) Control with High Efficiency

- Multi-Mode PSR Control

- Fast Dynamic Response

- Built-in Dynamic Base Drive

- Audio Noise Free Operation

- $\pm$  4% CC and CV Regulation

- Low Standby Power <70mW

- Programmable Cable Drop Compensation (CDC) in CV Mode

- Built-in AC Line & Load CC Compensation

- Build in Protections:

- Short Load Protection (SLP)

- Cycle-by-Cycle Current Limiting

- Leading Edge Blanking (LEB)

- Pin Floating Protection

- VDD OVP & UVP & Clamp

- Over temperature protection(OTP)

- Available with DP1801KB Versions in SOP-7 Package

#### **APPLICATIONS**

- Battery Chargers for Cellular Phones

- AC/DC Power Adapter and LED Lightings

#### **GENERAL DESCRIPTION**

DP1801KB is a high performance Quasi Resonant (QR) Primary Side Regulation (PSR) PWM power switch with high precision CV/CC control ideal for charger applications.

In CV mode, DP1801KB adopts Multi Mode QR Control which uses the hybrid of AM (Amplitude Modulation) mode and (Frequency Modulation) FM mode to improve system efficiency and reliability. In CC mode, the IC uses PFM control with line and load CC compensation. The IC can achieve fast dynamic response. The built-in Cable Drop Compensation (CDC) function can provide excellent CV performance.

DP1801KB integrates functions and protections of Under Voltage Lockout (UVLO), VDD over Voltage Protection (VDD OVP), Cycle-by-cycle Current Limiting (OCP), Short Load Protection (SLP), On-Chip Thermal Shutdown, VDD Clamping, etc.

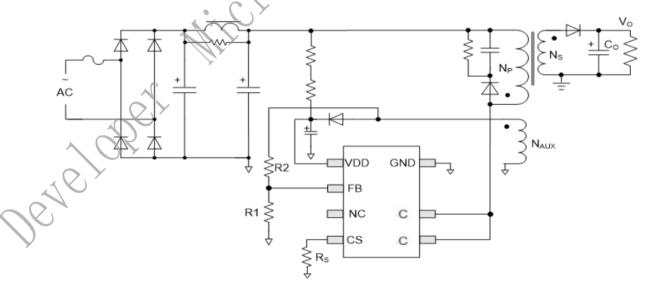

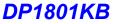

# TYPICAL APPLICATION CIRCUIT

Rev.1.1

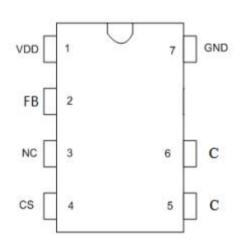

### **Pin Configuration**

#### **Marking Information**

DP1801KB for product name;

KBXXXXXX The KB represents the version; The first X reresents the last year, 2020 is 0; The second X represents the month, in A-L 12 letters; The third and fourth X on behalf of the date, 01-31 said; The last two X represents the wafer batch code. (

| Pin<br>Number | Pin<br>Name | I/O | Description                                                                                                                                                 |

|---------------|-------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | VDD         |     | Power Supply Pin of the Chip.                                                                                                                               |

| 2             | FB          |     | System feedback pin which regulates both the output voltage in CV mode and output current in CC mode based on the flyback voltage of the auxiliary winding. |

| 3             | NC          | NC  |                                                                                                                                                             |

| 4             | CS          | I   | Current Sense Input Pin.                                                                                                                                    |

| 5,6           | C           | 0   | The Power BJT Collector                                                                                                                                     |

| 7             | GND         | Р   | The Ground of the IC                                                                                                                                        |

| ever          |             |     |                                                                                                                                                             |

#### Pin Description (DP1801KB)

Rev.1.1 The content of the document is a trade secret, without permission, any organization or individual shall not be

copied and disseminated in any form!

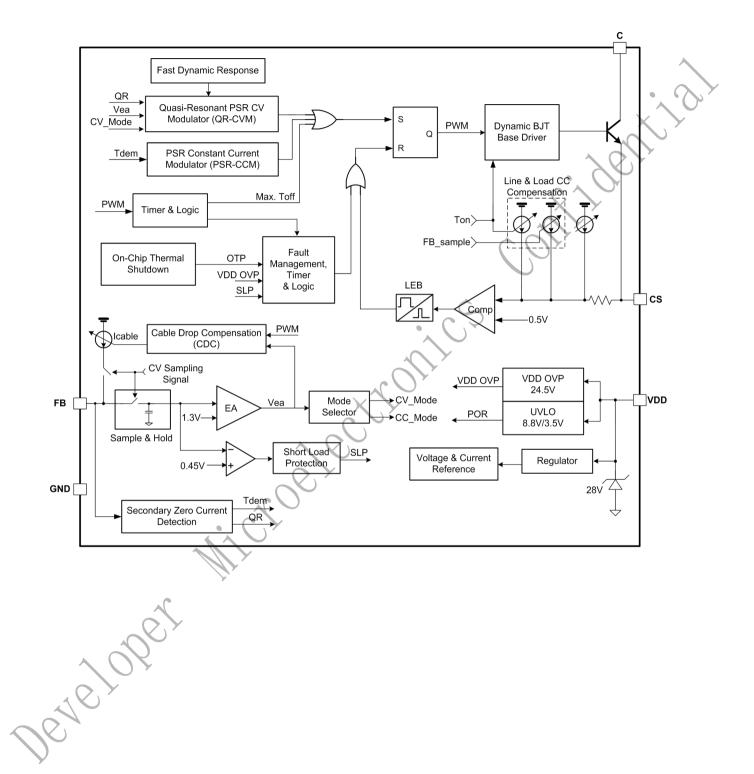

# **Block Diagram**

Rev.1.1 The content of the document is a trade secret, without permission, any organization or individual shall not be

copied and disseminated in any form!

#### Absolute Maximum Ratings (Note 1)

| Parameter                              | Value      | Unit |

|----------------------------------------|------------|------|

| C PIN Maximum Voltage                  | 800        | V    |

| C PIN DC Current @DP1801KB             | 800        | mA   |

| VDD DC Supply Voltage                  | 30         | V    |

| VDD DC Clamp Current                   | 10         | mA   |

| CS, BASE voltage range                 | -0.3 to 7  | V 🔨  |

| FB voltage range                       | -0.7 to 7  | V    |

| RθJC (℃/W) (SOP7)                      | 45         | °C/W |

| RθJA (℃/W) (SOP7)                      | 90         | °C/W |

| Maximum Junction Temperature           | 165        | °C   |

| Operating Temperature Range            | -20 to 85  | Da ( |

| Storage Temperature Range              | -65 to 150 | 0° C |

| Lead Temperature (Soldering, 10sec.)   | 260        | °C   |

| ESD Capability, HBM (Human Body Model) | 3          | kV   |

| ESD Capability, MM (Machine Model)     | 250        | V    |

#### Recommended Operation Conditions (Note 2)

| Parameter                                  | Ġ | Value     | Unit |

|--------------------------------------------|---|-----------|------|

| Supply Voltage, VDD                        |   | 5 to 19   | V    |

| Operating Ambient Temperature              |   | -40 to 85 | °C   |

| Maximum Switching Frequency @ Full Loading |   | 70        | kHz  |

| Minimum Switching Frequency @ Full Loading |   | 35        | kHz  |

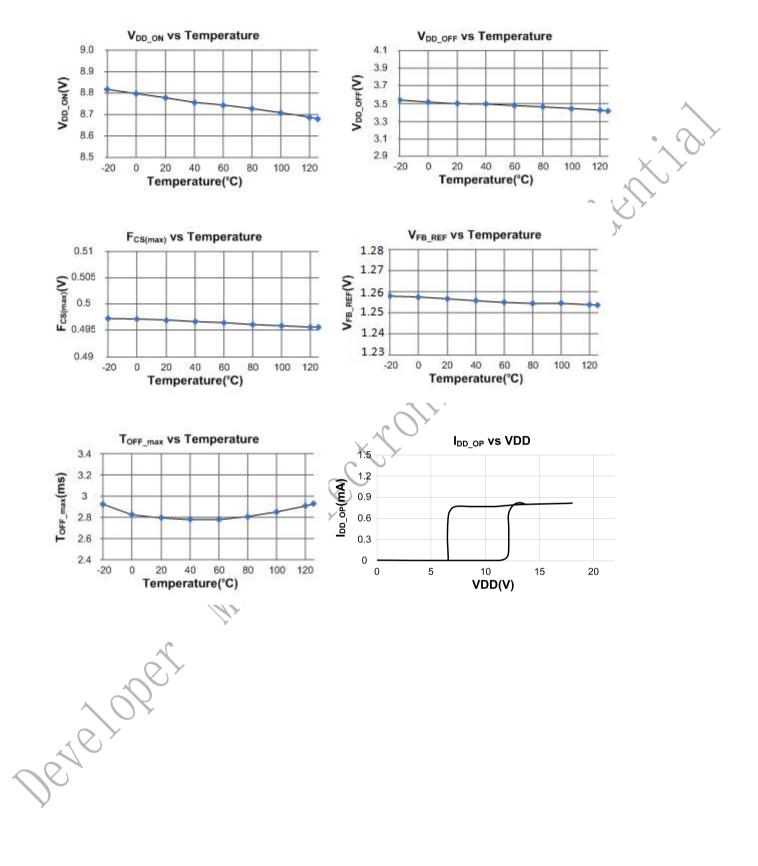

# ELECTRICAL CHARACTERISTICS (T<sub>A</sub> = 25°C, VDD=20V, if not otherwise noted)

| Symbol                   | Parameter                                        | Test Conditions            | Min  | Тур. | Max  | Unit |

|--------------------------|--------------------------------------------------|----------------------------|------|------|------|------|

| Supply Vol               | tage Section(VDD Pin)                            | )                          |      |      |      |      |

| I <sub>VDD_st</sub>      | Start-up current into VDD pin                    |                            |      | 3    | 20   | uA   |

| I <sub>VDD_Op</sub>      | Operation Current                                |                            |      | 0.8  | 1.5  | mA   |

| I <sub>VDD_standby</sub> | Standby Current                                  |                            |      | 0.5  | 1    | mA   |

| V <sub>DD_ON</sub>       | VDD Under Voltage Lockout<br>Exit                |                            | 9    | 10.2 | 11.5 | V    |

|                          | VDD Under Voltage Lockout<br>Enter               |                            | 3    | 3.6  | 4.5  | V    |

| VDD_OVP                  | VDD OVP Threshold                                |                            | 20   | 22   | 24   | V    |

| VDD_Clamp                | VDD Zener Clamp Voltage                          | I(V <sub>DD</sub> ) = 7 mA |      | 28   |      | V    |

| Control Fu               | nction Section (FB Pin)                          |                            |      | ·    | •    |      |

| V <sub>FBREF</sub>       | Internal Error Amplifier (EA)<br>Reference Input |                            | 1.23 | 1.25 | 1.27 | V    |

Rev.1.1

# P1801KB

Quasi-Resonant PSR CC/CV PWM Power Switch

| $V_{FB\_SLP}$               | Short Load Protection (SLP)<br>Threshold                                 |                                           |      | 0.35 |                  | V  |

|-----------------------------|--------------------------------------------------------------------------|-------------------------------------------|------|------|------------------|----|

| $T_{FB\_Short}$             | Short Load Protection (SLP)<br>Debounce Time                             | (Note 3)                                  |      | 36   |                  | ms |

| $V_{FB\_DEM}$               | Demagnetization Comparator<br>Threshold                                  |                                           |      | 25   |                  | mV |

| $T_{off}$ min               | Minimum OFF time                                                         | (Note 3)                                  |      | 2    |                  | us |

| T <sub>on_max</sub>         | Maximum ON time                                                          | (Note 3)                                  |      | 20   |                  | us |

| T <sub>off_max</sub>        | Maximum OFF time                                                         |                                           |      | 2.8  | $\sum_{i=1}^{n}$ | ms |

| Cable_max                   | Maximum Cable Drop<br>Compensation(CDC) Current                          |                                           | 76.5 | 85   | 93.5             | uA |

| Tsw /Tdem                   | Ratio between Switching<br>Period and Demagnetization<br>Time in CC Mode |                                           |      | 7/4  |                  |    |

| Current Se                  | ense Input Section (CS Pin)                                              |                                           | (    | 212  |                  |    |

| T <sub>LEB</sub>            | CS Input Leading Edge<br>Blanking Time                                   |                                           |      | 500  |                  | ns |

| $V_{\text{cs}(\text{max})}$ | Current limiting threshold                                               |                                           | 490  | 500  | 510              | mV |

| T <sub>D_OC</sub>           | Over Current Detection and Control Delay                                 |                                           |      | 100  |                  | ns |

| On-Chip T                   | hermal Shutdown                                                          | · 0 ·                                     |      |      |                  |    |

| $T_{SD}$                    | Thermal Shutdown                                                         | (Note 3)                                  |      | 155  |                  | °C |

| T <sub>RC</sub>             | Thermal Recovery                                                         | (Note 3)                                  |      | 140  |                  | °C |

| BJT Sectio                  | on (HV Pin)                                                              | )                                         |      |      |                  |    |

| lc                          | Maximum DC Collector<br>Current                                          |                                           |      | 0.8  |                  | А  |

|                             | Collector-Emitter Saturation Voltage                                     | I <sub>C</sub> =0.2A,I <sub>B=</sub> 40mA |      | 0.3  | 0.6              | V  |

| V <sub>CE(sat)</sub>        | Voltage                                                                  |                                           |      |      |                  |    |

| V <sub>CE(sat)</sub>        | Collector-Emitter voltage                                                |                                           | 480  |      |                  | V  |

Note1. Stresses listed as the above "Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to maximum rating conditions for extended periods may remain possibility to affect device reliability.

Note2. The device is not guaranteed to function outside its operating conditions.

Note3. Guaranteed by the Design.

#### **CHARACTERIZATION PLOTS**

Rev.1.1

#### PERATION DESCRIPTION

DP1801KB is a high performance, multi mode, highly integrated Quasi Resonant Primary Side Regulation (QR-PSR) power switch. The built-in high precision CV/CC control with high level protection features makes it suitable for offline small power converter applications.

#### System Start-Up Operation

Before the IC starts to work, it consumes only startup current (typically 3uA) which allows a large value startup resistor to be used to minimize the power loss and the current flowing through the startup resistor charges the VDD hold-up capacitor from the high voltage DC bus. When VDD reaches UVLO turn-on voltage of 8.8V (typical), DP1801KB begins switching and the IC operation current is increased to be 0.8mA (typical). The hold-up capacitor continues to supply VDD before the auxiliary winding of the transformer takes the control of VDD voltage.

Once DP1801KB enters very low frequency FM (Frequency Modulation) mode, the operating current is reduced to be 500uA typically, which helps to reduce the standby power loss.

#### Quasi Resonant PSR CV Modulation

#### (QR-CVM)

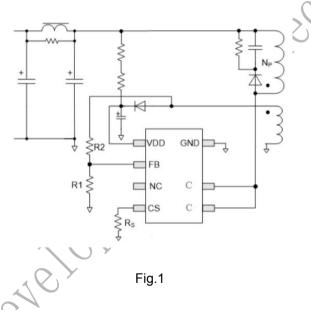

In Primary Side Regulation (PSR) control, the output voltage is sensed on the auxiliary winding during the transfer of transformer energy to the secondary. Fig.2 illustrates the timing waveform of CV sampling signal, demagnetization signal (DEM) quasi-resonant (QR) trigger signal in and DP1801KB. When the CV sampling process is over, the internal sample/hold (S&H) circuit captures the error signal and amplifies it through the internal Error Amplifier (EA). The output of EA is sent to the Quasi Resonant PSR CV Modulator (QR-CVM) for CV regulation. A valley is selected to trigger new PWM cycle by the output of the QR-CVM bock, which is determined by the load. The internal reference voltage for EA is trimmed to 1.3V with high accuracy.

During the CV sampling process, an internal variable current source is flowing to FB pin for Cable Drop Compensation (CDC). Thus, there is step at FB pin in the transformer а demagnetization process, as shown in Fig.2. Fig.2 also illustrates the equation for "demagnetization plateau", where Vo and VF is the output voltage and diode forward voltage; R1 and R2 is the resistor divider connected from the

-7-/11

Rev.1.1 The content of the document is a trade secret, without permission, any organization or individual shall not be copied and disseminated in any form!

auxiliary winding to FB Pin, Ns and Na are secondary winding and auxiliary winding respectively.

When heavy load condition, the Mode Selector (as shown in "**Block Diagram**") based on EA output will switch to CC Mode automatically.

#### PSR Constant Current Modulation (PSR-CCM)

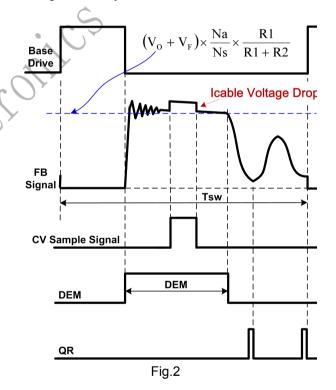

Timing information at the FB pin and current information at the CS pin allow accurate regulation of the secondary average current. The control law dictates that as power is increased in CV regulation and approaching CC regulation the primary peak current is at Ipp(max), as shown in Fig.3.

Referring to Fig.3 above, the primary peak current, transformer turns ratio, secondary demagnetization time (Tdem), and switching period (Tsw) determines the secondary average output current lout. Ignoring leakage inductance effects, the equation for average output current is shown in Fig.3. When the average output current lout reaches the regulation reference in the Primary Side Constant Current Modulator (PSR-CCM) block, the IC operates in pulse frequency modulation

(PFM) mode to control the output current at any output voltage at or below the voltage regulation target as long as the auxiliary winding can keep VDD above the UVLO turn-off threshold.

In DP1801KB, the ratio between Tdem and Tsw in CC mode is **4/7**. Therefore, the average output current can be expressed as:

$$I_{CC_{OUT}}(mA) \cong \frac{2}{7} \times N \times \frac{500mV}{Rcs(\Omega)}$$

In the equation above,

N----The turn ratio of primary side winding to secondary side winding.

Rcs--- the sensing resistor connected between the power BJT emitter to GND.

#### Multi Mode Control in CV Mode

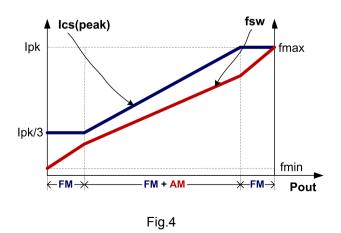

To meet the tight requirement of averaged system efficiency and no load power consumption, a hybrid of frequency modulation (FM) and amplitude modulation (AM) is adopted in DP1801KB which is shown in the Fig 4.

Around the full load, the system operates in FM mode. When normal to light load conditions, the IC operates in FM+AM mode to achieve excellent regulation and high efficiency. When the system is near zero loading, the IC operates in FM again for standby power reduction. In this way, the no-load consumption can be less than 70mW.

-8-/11

Rev.1.1

**DP1801KB**

Quasi-Resonant PSR CC/CV PWM Power Switch

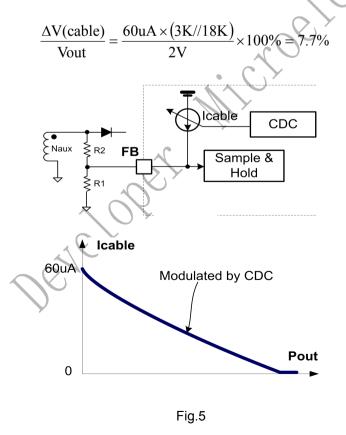

#### • Programmable Cable Drop Compensation (CDC) in CV Mode

In smart phone charger application, the battery is always connected to the adapter with a cable wire which can cause several percentages of voltage drop on the actual battery voltage. In DP1801KB. an offset voltage is generated at FB pin by an internal current source (modulated by CDC block, as shown in Fig.5) flowing into the resistor divider. The current is proportional to the switching period, thus, it is inversely proportional to the output power Pout. Therefore, the drop due the cable loss can be compensated. As the load decreases from full loading to zero loading, the offset voltage at FB pin will increase. By adjusting the resistance of R1 and R2 (as shown in Fig.), the cable loss compensation can be programmed. The percentage of maximum compensation is given by

$\frac{\Delta V(\text{cable})}{\text{Vout}} \approx \frac{\text{Icable}_{\text{max}} \times (\text{R1}/\text{R2})}{V_{\text{FB}_{\text{REF}}}} \times 100\%$

For example, R1=3K  $\Omega$  , R2=18K  $\Omega$  , The percentage of maximum compensation is given by:

#### Optimized Dynamic Response

In DP1801KB, the dynamic response performance is optimized to meet USB charge requirements.

#### • On Chip Thermal Shutdown (OTP)

When the IC temperature is over 155 °C, the IC shuts down. Only when the IC temperature drops to 140 °C, IC will restart.

#### Audio Noise Free Operation

As mentioned above, the multi-mode CV control with a hybrid of FM and AM provides frequency modulation. An internal current source flowing to CS pin realizes CS peak voltage modulation. In DP1801KB, the optimized combination of frequency modulation and CS peak voltage modulation algorithm can provide audio noise free operation from full loading to zero loading.

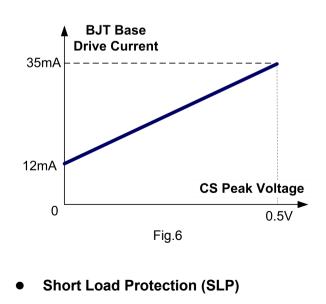

#### Dynamic BJT Base Drive

DP1801KB drives a power BJT with dynamic base drive control to optimize efficiency. The BJT base drive current ranges from 12mA to 35mA (typical), and is dynamically controlled according to the power supply load change. The higher the output power, the higher the based current. Specifically, the base current is related to CS peak voltage, as shown in Fig.6

-9-/11

In DP1801KB, the output is sampled on FB pin and then compared with a threshold of UVP (0.45V typically) after an internal blanking time (36ms typical).

In DP1801KB, when sensed FB voltage is below 0.45V, the IC will enter into Short Load Protection (SLP) mode, in which the IC will enter into auto recovery protection mode.

#### • VDD Over Voltage Protection (OVP) and **Zener Clamp**

When VDD voltage is higher than 24.5V (typical), the IC will stop switching. This will cause VDD fall down to be lower than VDD OFF (typical 3.5V) and then the system will restart up again. An internal 30V (typical) zener clamp is integrated to prevent contidenti the IC from damage.

Deretoper

copied and disseminated in any form!

Hiccoelectronics

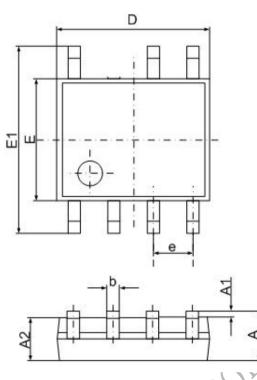

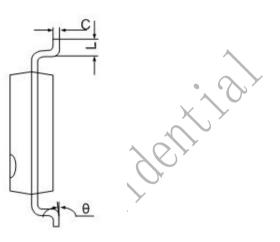

# Package Dimension

SOP7

| Symbol     | Dimensions i | in Millimeters | Dimensions in Inches |       |  |

|------------|--------------|----------------|----------------------|-------|--|

| Symbol     | Min          | Мах            | Min                  | Мах   |  |

| А          | 1.350        | 1.750          | 0.053                | 0.069 |  |

| A1         | 0.100        | 0.250          | 0.004                | 0.010 |  |

| A2         | 1.350        | 1.550          | 0.053                | 0.061 |  |

| b          | 0.330        | 0.510          | 0.013                | 0.020 |  |

| С          | 0.170        | 0.250          | 0.006                | 0.010 |  |

| D          | 4.700        | 5.100          | 0.185                | 0.200 |  |

| E          | 3.800        | 4.000          | 0.150                | 0.157 |  |

| E1 🔿       | 5.800        | 6.200          | 0.228                | 0.244 |  |

| e          | 1.270        | (BSC)          | 0.050 (              | BSC)  |  |

| $\sqrt{0}$ | 0.400        | 1.270          | 0.016                | 0.050 |  |

| θ          | 0°           | 8°             | 0°                   | 8°    |  |

www.depuw.com -11-/11 Rev.1.0 The content of the document is a trade secret, without permission, any organization or individual shall not be copied and disseminated in any form! Rev.1.0