# 支持USB-PD3.0的升降压控制器

# 1 特性

## ● 4管桥式升降压控制器

- ☆ 输入范围3.6V-32V

- ☆ 支持CC/CV模式

- ☆ 支持动态调压/限流

- ☆ 内置2A驱动电路

- ☆ 效率高达98%

- ☆ 可编程软启动,有效限制启动时浪涌

- ☆ 内置抖频技术,有效降低EMI干扰

## • 快充协议

- ☆ 支持PD2.0/PD3.0

- ☆ 支持QC2.0/3.0/3+

- ☆ 支持华为FCP/SCP

- ☆ 支持AFC

- ☆ 支持苹果协议

- ☆ 支持BC1.2

- ☆ 可编程PDO功能

- ☆ 支持多口控制

- ☆ 支持VBUS泄放功能

## ● 支持DFP/Source角色

● QFN5x5-40封装

### ● 多重保护功能

- ☆ 输入欠压保护

- ☆ 输出过压保护

- ☆ 逐周期限流保护

- ☆ 输出过流/短路保护

- ☆ 过温保护

# 2 典型应用

- ☆ 储能电源

- ☆ 车充

- ☆ 适配器

# 3 概述

LYF63303是一款集成PD/QC等全部协议的4管桥式升降 压控制器。自主专利的升降压控制模式,从而实现在升压、 降压、升降压平滑切换;采用COT架构和内置2A的驱动电路, 从而实现高效率的、大功率负载输出;开关频率可编程设置 150kHZ、300kHz、600kHz和1200kHz; VADJ,IADJ引脚用于 动态输出调压和输出恒流控制。

LYF63303内置PD3. 0等全协议,专为Type-C电源侧充电应用;系统通过监控CC引脚,以检测Type-C插入和拔出,同时可提供5V至20V的输出电压;通过监控D+/D-引脚,检测不同的设备需求自动调整输出电压,可提供3. 6V至20V的输出电压;内部集成两个放大器和参考电压,用于电压和电流环路调节。

LFY63303宽范围的输入输出电压和自带协议等特点,有效的降低了系统的复杂性和减少了方案的成本,因此非常适用于移动储能电源、车充、适配器等需要支持Type-C端口输出的应用场景。

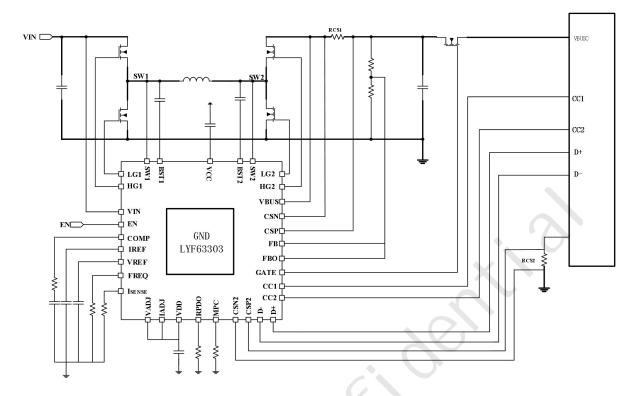

# 4 应用框架图

図 ·

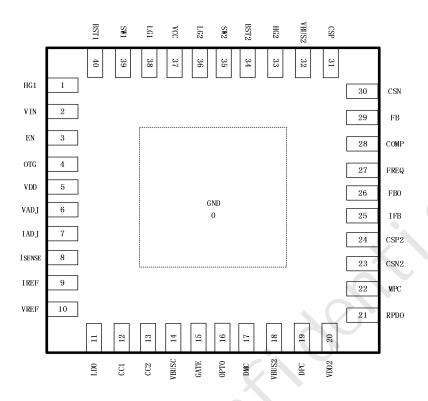

# 5 引脚定义及功能

图. 2 引脚图 (QFN5x5-40)

| 5  | 川脚     | алты                                       |

|----|--------|--------------------------------------------|

| 序号 | 名称     | 描述                                         |

| 1  | HG1    | 高端驱动1                                      |

| 2  | VIN    | 输入端,接电池电压或输入电压                             |

| 3  | EN     | 使能脚,设置1:使能 0:关闭,悬空时芯片默认处于使能状态              |

| 4  | OTG    | 接IC的LDO引脚                                  |

| 5  | VDD    | 5.4V电源为IC内部系统供电                            |

| 6  | VADJ   | 接PWM信号或0-2V模拟电压,可动态调接输出电压,不用该功能时接IC的VDD引脚  |

| 7  | IADJ   | 接PWM信号或0-2V模拟电压,可动态控制输出恒流点,不用该功能时接IC的VDD引脚 |

| 8  | ISENSE | 放电电流监控脚,可给供外部MCU读取电流信息                     |

| 9  | IREF   | 电流环路的参考电压                                  |

| 10 | VREF   | 电压环路的参考电压                                  |

| 11 | LDO    | 5V LDO 给外部供电                               |

| 12 | CC1    | Type-C 配置通道信号1                             |

| 13 | CC2    | Type-C 配置通道信号2                             |

| 14 | VBUSC  | Type-C 端口的电压检测                             |

| 15 | GATE   | 输出控制引脚,可驱动N-MOS                            |

| 16 | ОРТО   | 输出电压控制脚,用于驱动光耦                             |

| 17 | DMC    | Type-C 口DM信号                               |

| 18 | VBUS2  | VBUS电压检测脚                                  |

| 19 | DPC    | Type-C 口DM信号                               |

| 5  | 川脚   | 描述                                                        |  |  |  |

|----|------|-----------------------------------------------------------|--|--|--|

| 序号 | 名称   | <b>加</b>                                                  |  |  |  |

| 20 | VDD2 | 内部系统供电                                                    |  |  |  |

| 21 | RPDO | 输出功率选择脚,连接100k电阻到地                                        |  |  |  |

| 22 | MPC  | 多端口功率分配控制脚,连接100k电阻到地                                     |  |  |  |

| 23 | CSN2 | 电流检测电路,负极输入端                                              |  |  |  |

| 24 | CSP2 | 电流检测电路,正极输入端                                              |  |  |  |

| 25 | IFB  | 电流环反馈控制脚                                                  |  |  |  |

| 26 | FBO  | 电压环反馈控制脚                                                  |  |  |  |

| 27 | FREQ | 频率设置脚 ,直接接地设置150kHz ,接VDD设置300kHz ,从VDD分压可设置600kHz或1.2MHz |  |  |  |

| 28 | COMP | 误差放大器输出端                                                  |  |  |  |

| 29 | FB   | VBUS电压反馈脚,通过VBUS分压电阻设置输出电压                                |  |  |  |

| 30 | CSN  | 输出电流检测电路,负极输入端                                            |  |  |  |

| 31 | CSP  | 输出电流检测电路,正极输入端                                            |  |  |  |

| 32 | VBUS | VBUS电压                                                    |  |  |  |

| 33 | HG2  | 高端MOS驱动2                                                  |  |  |  |

| 34 | BST2 | 高端MOS驱动2的Boost引脚                                          |  |  |  |

| 35 | SW2  | 开关节点2                                                     |  |  |  |

| 36 | LG2  | 低端MOS驱动2                                                  |  |  |  |

| 37 | VCC  | 驱动电源                                                      |  |  |  |

| 38 | LG1  | 低端MOS驱动1                                                  |  |  |  |

| 39 | SW1  | 开关节点1                                                     |  |  |  |

| 40 | BST1 | 高端MOS驱动1的Boost引脚                                          |  |  |  |

| 0  | GND  | 模拟地                                                       |  |  |  |

# 6 订购信息

| 器件名称     | 订购信息           | 封装          | 包装   | 丝印              |

|----------|----------------|-------------|------|-----------------|

| LYF63303 | LYF63303IQN40A | QFN5x5 - 40 | 5000 | 63303<br>RAAYMD |

LYF63303: Part Number

RAAYMD: RAA: LOT NO.; YMD: Package Date

# 7 规格参数

# 7.1 极限参数<sup>(备注 1)</sup>

| 参数                            | 最小   | 最大  | 单位 |

|-------------------------------|------|-----|----|

| VIN, VBUS, CSN, CSP, SW1, SW2 | -0.3 | 40  |    |

| HG1, BST1 to SW1              | -0.3 | 7   |    |

| HG2, BST2 to SW2              | -0.3 | 7   |    |

| LG1, LG2, VCC, VDD2 to GND    | -0.3 | 7   |    |

| CSP to CSN                    | -0.3 | 0.6 | V  |

| VBUS to CSP, CSN              | -0.3 | 0.6 |    |

| CC1,CC2,D-,D+,OPTO            | -0.3 | 24  |    |

| GATE,VBUS2,VBUSC              | -0.3 | 35  |    |

| Other Pins to GND             | -0.3 | 6   |    |

## 7.2 操作范围

| 符号               | 参数       | 最小  | 最大   | 单位 |

|------------------|----------|-----|------|----|

| T <sub>ST</sub>  | 存储温度范围   | -65 | 150  | °C |

| TJ               | 结温       |     | +150 | °C |

| T∟               | 引脚温度     |     | +260 | °C |

| V <sub>ESD</sub> | HBM 人体模型 |     | 2    | kV |

# 7.3 推荐工作条件 (<sup>备注2)</sup>

|      | 参数      | 最小  | 最大   | 单位 |

|------|---------|-----|------|----|

| 输入电压 | VIN     | 3.6 | 30   | V  |

| 温度   | 结温范围,T」 | -40 | +125 | °C |

# 7.4 热阻参数<sup>(备注 3)</sup>

| 符号  | 描述        | QFN5x5-40 | 单位   |

|-----|-----------|-----------|------|

| θја | 芯片到环境间的热阻 | 44        | °C/W |

| θυς | 芯片到外壳间的热阻 | 9         | C/VV |

### 备注:

- 1) 超过正常范围可能会损坏IC。

- 2) 超出推荐范围外应用可能会损坏IC。

- 3) 在1盎司铜箔上测试。

# **7.5 电气特性** (VIN = 12V, T<sub>J</sub> =25°C, 除特别说明.)

| 符号                                    | 参数                                                                | 条件                                       | 最小       | 典型   | 最大    | 单位  |

|---------------------------------------|-------------------------------------------------------------------|------------------------------------------|----------|------|-------|-----|

| VIN                                   | Input voltage                                                     |                                          | 3.6      |      | 30    | V   |

| 1 1/11/1                              | VIN Shutdown Current                                              | EN=0V, VIN=7.2V                          |          | 15   |       | uA  |

| $I_{Q_{-}}VIN$                        | VIN Supply Current                                                | No Switching, FB=2.1V                    |          | 1000 |       | uA  |

| VBUS                                  | Bus line voltage                                                  | İ                                        | 3.6      |      | 22    | V   |

| $V_{VCC}$                             | Driver power supply voltage                                       | VIN =15V                                 |          | 6.6  |       | V   |

| $V_{VDD}$                             | Control core power supply voltage                                 | VIN =15V                                 |          | 5.4  |       | V   |

| $V_{\text{LDO}}$                      | LDO output voltage                                                | VIN =15V                                 |          | 5    |       | V   |

| I <sub>LDO</sub>                      | LDO output current                                                | V <sub>LDO</sub> =5V                     |          |      | 55    | mA  |

| VDD2                                  | Input voltage                                                     |                                          | 3.2      |      | 6.8   | V   |

| VDD2_SUP                              | VDD2 Supply Current                                               | VDD2=5V,Nothing Attach                   | 66       | 100  | 136   | uA  |

| VDD2 <sub>UV</sub>                    | VDD2 UVLO Rising                                                  |                                          |          | 3.5  |       | V   |

|                                       | Hysteresis                                                        |                                          |          | 300  |       | mV  |

| UVLO/EN                               |                                                                   |                                          |          |      |       |     |

| VIN_uv                                | VIN UVLO Rising                                                   |                                          |          | 3.5  |       | V   |

| • • • • • • • • • • • • • • • • • • • | Hysteresis                                                        |                                          |          | 300  |       | mV  |

| $V_{EN\_UV}$                          | Operation Threshold                                               |                                          | 1.1      | 1.2  | 1.3   | V   |

|                                       | Hysteresis                                                        |                                          |          | 200  |       | mV  |

| Control loop                          |                                                                   |                                          |          |      |       |     |

| V <sub>FB</sub>                       | VFB regulation voltage                                            | FB voltage                               | 1.96     | 2    | 2.04  | V   |

| G <sub>mEA</sub>                      | Error amplifier gm                                                |                                          |          | 450  |       | uS  |

| Isink                                 | COMP sink/source current                                          | VFB=VREF+100mV                           |          | 15   |       | uA  |

| ISOURCE                               | COMP source current                                               | VFB=VREF-100mV                           |          | 20   |       | uA  |

| I <sub>FB</sub>                       | FB bias current                                                   | FB in regulation                         |          |      | 100   | nA  |

| Frequency                             |                                                                   |                                          |          |      |       |     |

|                                       |                                                                   | FREQ 0-0.4V, short FREQ pin to GND.      |          | 150  |       | kHz |

| F <sub>sw</sub>                       | Switching Frequency                                               | FREQ 1.8-5.4V, short                     |          | 300  |       | kHz |

| 1 300                                 | Switching Frequency                                               | FREQ pin to VDD.                         |          |      |       |     |

|                                       |                                                                   | FREQ 0.4-0.85V                           | 600      |      |       | kHz |

| 0                                     |                                                                   | FREQ 0.85-1.8V                           | <u> </u> | 1200 |       | kHz |

| Current Limit                         | I Dura anno anno anti timit                                       | 1                                        |          |      |       |     |

| Icclim_bus                            | Bus average current Limit,<br>V <sub>CSP</sub> - V <sub>CSN</sub> |                                          |          | 40   |       | mV  |

| NMOS Driver                           |                                                                   |                                          |          |      |       |     |

| I <sub>HDRV1,2</sub> (Note 4)         | Driver peak source current                                        | V <sub>BST</sub> - V <sub>SW</sub> =6.6V |          | 2    |       | Α   |

| IHDRV1,2`                             | Driver peak sink current                                          | V <sub>BST</sub> - V <sub>SW</sub> =6.6V |          | 2    |       | Α   |

| . (Note 4)                            | Driver peak source current                                        | VCC=6.6V                                 |          | 2    |       | Α   |

| I <sub>LDRV1,2</sub> (Note 4)         | Driver peak sink current                                          | VCC=6.6V                                 |          | 2    |       | Α   |

|                                       | UVLO                                                              |                                          |          | 2    |       | V   |

| V <sub>BSTUV</sub>                    | Hysteresis                                                        |                                          |          | 300  |       | mV  |

| Output Protectio                      |                                                                   |                                          |          |      |       |     |

| V <sub>OVP</sub>                      | Output over voltage threshold                                     |                                          |          | 110  |       | %   |

| V <sub>UVP</sub>                      | Output under voltage threshold                                    | 1                                        |          | 50   |       | %   |

| VADJ, IADJ                            | Takpar ander remage ameened                                       | I                                        | <u> </u> |      |       | ,,, |

| -                                     | VPWM low voltage                                                  |                                          | Ι        |      | 0.4   | V   |

| V <sub>TH_VADJ</sub> (Note 4)         | VPWM high voltage                                                 |                                          | 2.5      |      | - 0.4 | V   |

|                                       | IPWM low voltage                                                  |                                          | 2.5      |      | 0.4   | V   |

| V <sub>TH_IADJ</sub> (Note 4)         | IPWM high voltage                                                 | 1                                        | 2.5      |      | 0.4   | V   |

| T <sub>SD</sub> <sup>(Note 4)</sup>   | Thermal Shutdown Threshold                                        |                                          | 2.5      | 150  |       | °C  |

|                                       |                                                                   |                                          | -        | 150  |       | °C  |

| T <sub>HYS</sub> (Note 4)             | Thermal Shutdown Hysteresis                                       | <u> </u>                                 | <u> </u> | 20   |       | - U |

| N-MOSFET Gate                         |                                                                   | 1                                        | 1        |      |       |     |

| Vgate                                 | Sourcing Voltage between gate and VBUS                            | VIN=3.2V to 6.8V                         | 5        |      | 15    | V   |

# 电气特性(续)

| 符号                              | 参数                                      | 条件                             | 最小   | 典型              | 最大   | 单位      |

|---------------------------------|-----------------------------------------|--------------------------------|------|-----------------|------|---------|

| USB Type-C                      |                                         |                                |      |                 |      |         |

| Icc_3A                          | SRC CC Current                          |                                | 304  | 330             | 356  | uA      |

| $V_{DPDNOV}$                    | D+/D- OV Threshold                      | In DCP mode                    |      | 7               |      | V       |

| V_DPDNOV                        | D+/D- OV Threshold                      | In HVDCP mode                  |      | 4               |      | V       |

| $V_{\text{CCOV-rising}}$        | CC OV Rising Hysteresis                 |                                |      | 1.04*VII<br>300 | N .  | V<br>mV |

| High Voltage Ded                | icated Charging Port (HVDCP)            |                                |      |                 |      |         |

| VDAT(REF)                       | Data Detect Voltage                     |                                | 0.25 | 0.325           | 0.4  | V       |

| Vsel_ref                        | Output Voltage Selection Reference      |                                | 1.8  | 2.0             | 2.2  | V       |

| TGLITCH(BC)-DPA-H               | D+ High Glitch Filter Time              |                                | 1000 | 1250            | 1500 | ms      |

| TGLITCH(BC)-DNA-L               | D- Low Glitch Filter Time               |                                |      | 1               |      | ms      |

| TGLITCH(V) CHANGE               | Output Voltage Glitch Filter Time       |                                | 20   | 40              | 60   | ms      |

| RDNA(DWN)                       | D- Pull-Down Resistance                 | 7()                            |      | 20              |      | kΩ      |

| TGLITCH-CONTCHANGE              | Continuous Mode Glitch Filter Time      |                                | 100  |                 | 200  | ms      |

|                                 |                                         | V <sub>DD2</sub> =3.2 to 6.4V  |      |                 |      |         |

| RDAT-LKG                        | D+ Leakage Resistance                   | VDPA=0.6-3.6V Switch           | 300  | 500             | 800  | kΩ      |

|                                 |                                         | SW1=off                        |      |                 |      |         |

| Rds_on_n1                       | Switch SW1 On-Resistance                | V <sub>DD2</sub> =5V,SW1=200μA |      |                 | 40   | Ω       |

|                                 |                                         | Iυρ =0μA (5V),40μA (9V),       |      |                 |      |         |

|                                 |                                         | 70μA (12V),100μA (15V),        |      |                 |      |         |

| IUP, IDOWN                      | UP/Down Current Step                    | 150μA (20V)                    |      | 2               |      | uA      |

|                                 |                                         | IDOWN=14μA (3.6V)              |      |                 |      |         |

| DCP Charging Mo                 | ode                                     |                                |      |                 | •    |         |

| V <sub>D+</sub> V <sub>D-</sub> | D+_0.48v / D0.48v Line Output Voltage   |                                | 0.44 | 0.48            | 0.52 | V       |

| RD+-D-                          | D+_0.48v / D0.48v Line Output Impedance |                                |      | 900             |      | kΩ      |

| Apple Mode                      |                                         |                                |      |                 | •    |         |

| V <sub>D+</sub> V <sub>D-</sub> | D+_2.7v / D2.7v Line Output Voltage     |                                | 2.57 | 2.7             | 2.84 | V       |

| RD+-D-                          | D+_2.7v / D2.7v Line Output Impedance   |                                |      | 33.6            |      | kΩ      |

| D- Section (FCP o               | r SCP)                                  |                                |      |                 |      |         |

| VTX-VOH                         | D- Tx Valid Output High                 |                                | 2.55 |                 | 3.6  | V       |

| VTX-VOL                         | D- Tx Valid Output Low                  |                                |      |                 | 0.3  | V       |

| V <sub>RX-VIH</sub>             | D- Rx Valid Output High                 |                                | 1.4  |                 | 3.6  | V       |

| Vrx-vil                         | D- Rx Valid Output Low                  |                                |      |                 | 1.0  | V       |

| RPD                             | D- Output Pull-Low Resistance           |                                | 400  | 500             | 600  | Ω       |

| UI                              | Unit Interval for PHY Communication     | Fclk=125kHz                    | 144  | 160             | 180  | us      |

### 电气特性(续)

| 符号                | 参数                             | 条        | 件      | 最小 典型 | 最大   | 单位 |

|-------------------|--------------------------------|----------|--------|-------|------|----|

| Regulator Section |                                |          |        |       |      |    |

| VREF              | Voltage Control Loop Reference |          |        | 1.2   | 1    | V  |

|                   |                                |          | In SCP | 60    |      |    |

| VCS+              | Current control Loop Reference | RCS=10mR | In QC  | 36    |      | mV |

|                   |                                |          | In PD  | 120%* | lout |    |

| Іорто             | OPTO Sinking Current           |          |        | 27    | 80   | mA |

Note:

4) 设计中保证,生产时不测试。

# 8 功能描述

#### 8.1 升降压控制器

LYF63303 是集成了协议的升降压控制器。升降压采用同步4管桥式架构,自主专利的控制方式,根据输入、输出电压自动地在升压、降压及升降压模式间平滑切换。LYF63303采用了 COT 控制模式,工作频率可通过外部设置,内置 CC/CV 环简化了外围器件,有效降低设计难度和设计周期。

#### 8.1.1 使能开关

当 EN 引脚电压大于1.2V 时,LYF63303开始工作;当 EN 引脚电压低于待机阈值(典型值1.1V)LYF63303停止工作,此时只有 LDO 有输出电压。EN 内部已拉高,悬空时,IC 处于工作状态。

#### 8.1.2 频率设置

LYF63303 工作频率可通过 FREQ 引脚来设置。当 FREQ 接 GND 时设置为150kHz;当 FREQ 接 VDD 时设置为300kHz;当 FREQ 通过 VDD 与 GND 分压在0.4V 至0.85V 时设置为600kHz;当 FREQ 通过 VDD 与 GND 分压在0.85V 至1.5V 时设置为1200kHz。

#### 8.1.3 输出限流设置

LYF63303采用CC/CV控制模式,对输出平均电流进行检测,当负载电流小于设定值时,IC工作于恒压模式,输出电压为设定电压要求,当负载电流高于设定值时,IC工作于恒流模式,输出电压由外部负载阻抗决定。LYF63303通过检测CSP和CSN引脚间的电压与内部40mV基准进行比较,当大于40mV时系统调节COMP电压以降低输出电流。恒流电流计算公式由式1:

$$I_{CL(AVG)} = \frac{40 \, mV}{R_{cs}} \tag{1}$$

#### 8.1.4 过流保护和短路保护

LYF63303内置逐周期电流限制,以防止过流和短路的发生。当输出电流到达恒流点的1.2倍时,系统进入过流保护;当 VBUS 电压降低到 UV 阈值时,系统进入短路保护;过流和短路保护是以打嗝模式进行。

#### 8.1.5 过温保护

LYF63303内置热保护电路,当内部结温度到达150°时,热保护电路触发关闭驱动电路,同时软启动电容放电。当温度 降低到关闭阈值15°C 以下时,IC 自动重新启动。

#### 8.1.6 VREF 和 IREF

VREF 引脚是电压环路的参考电压,当 VADJ 连接 VDD 时 VREF 上电压是2V,当 VADJ 连接的是 PWM 信号时,内部斩波电路、电阻与外部电容构成的滤波电路最终得到参考电压,同时 VREF 上电容也作为软启动电容,建议使用100nF或以上电容;IREF 与 VREF 机制相同。

### 8.2 协议

LYF63303集成的 PD3.0和 USB 高压专用充电协议(HVDCP)协议,可用于高通的 QC2.0/3.0/3+、AFC、FCP 和 SCP、Apple 等协议规范。

#### 8.2.1 PD 协议

LYF63303支持 PD3.0协议同时兼容 PD2.0协议,可输出5V/9V/12V/15V/20V 电压。通过设置 RPDO 电阻可选择输出不同功率档。同时,它还支持苹果20W(9V/2.22A)充电。

#### 8.2.1 QC 协议

LYF63303支持 QC2.0/3.0/3+协议。通过设置 RPDO 电阻可选择设置为 A 类或 B 类。QC2.0 A 类(5V/9V/12V)和 B 类(5V/9V/12V/20V)输出电压范围;QC3.0 A 类(3.6V 至12V,200mV)和 B 类(3.6V 至20V,200mV)输出电压范围;QC3+的步进电压为20mV。

| Rpdo | QC<br>mode | Rated<br>Power | 5V | 9V     | 12V   | 15V | 20V    | Power<br>Reduction | QC<br>mode | 5V | 9V     | 12V   | 15V   | 20V   |

|------|------------|----------------|----|--------|-------|-----|--------|--------------------|------------|----|--------|-------|-------|-------|

| open | Class A    | 25W            | 3A | 2. 77A |       |     |        | 15W                | 5V         | 3A |        |       |       |       |

| 680k | Class A    | 20W            | 3A | 2. 22A |       |     |        | 15W                | 5V         | 3A |        |       |       |       |

| 470k | Class B    | 30W            | 3A | 3A     | 2. 5A | 2A  | 1.5A   | 20W                | Class A    | 3A | 3A     | 2.22A | 1.67A |       |

| 220k | Class A    | 18W            | 3A | 3A     | 1.5A  |     |        | 15W                | 5V         | 3A |        |       |       |       |

| 100k | Class B    | 30W            | 3A | 3A     | 2. 5A | 2A  | 1.5A   | 15W                | 5V         | 3A |        |       |       |       |

| 68k  | Class B    | 45W            | 3A | 3A     | 3A    | 3A  | 2.25A  | 20W                | Class A    | 3A | 2. 22A | 1.67A |       |       |

| 47k  | Class B    | 45W            | 3A | 3A     | 3A    | 3A  | 2. 25A | 30W                | Class B    | 3A | 3A     | 2. 5A | 2A    | 1.5A  |

| 22k  | Class B    | 60W            | 3A | 3A     | 3A    | 3A  | 3A     | 45W                | Class B    | 3A | 3A     | 3A    | 3A    | 2.25A |

| 10k  | Class B    | 60W            | 3A | 3A     | 3A    | 3A  | 3A     | 30W                | Class B    | 3A | 3A     | 2. 5A | 2A    | 1.5A  |

| 0    | Class A    | 20W            | 3A | 2. 22A | 1.67A |     |        | 15W                | 5V         | 3A |        |       |       |       |

### 8.2.1 AFC/FCP/SCP 协议

YF63303支持 AFC 协议,输出电压范围为5V/9V;支持 FCP 协议,输出电压范围为5V/9V/12V;还支持 SCP 协议,充电能力为4.5V/5A。

### 8.3 多端口控制

LYF63303支持多端口输出实现功率分配。两个或多个 MPC 连接起来,通过100k 电阻到地即可。

#### 8.4 VDD2供电

VDD2引脚内置6.4V 稳压二极管 ,同时 ,通过外接限流电阻 ,以支持更宽范围的输出电压。推荐电阻及电容为1.2k 和470nF。

#### 8.5 CC1/CC2引脚过压保护

LYF63303支持 CC1/CC2引脚的过压保护。异常情况下,当外部电压接触到 CC 引脚时,为了保护设备不受损坏,芯片会控制输出电压返回到默认输出电压5V。

#### 8.6 D+/D-引脚过压保护

LYF63303支持 D+/D-引脚的过压保护。异常情况下,当外部电压接触到 D+/D-引脚且大于7.5V 时,为了保护设备不受损坏,芯片会控制输出电压返回到默认输出电压5V,如果是在 HVDCP 模式下,D+/D-引脚过压保护为4V。

## 9 应用设计

#### 9.1 输出电压设置

LYF63303输出电压由外部反馈分压电阻设置,电阻精度推荐1%。反馈信号与内部误差放大器2V基准比较。输出电压公式如下式:

$$V_{OUT} = 2V * \left(1 + \frac{R_{up}}{R_{down}}\right) \tag{2}$$

实际应用中,由于需要协议调压,Vout 应设置5V 且 Rup 必须选择100k。

#### 9.2 电感的选择

在电感设计的时候,需要先确定频率,通过外围电阻选所需频率后,再选定电感纹波率一般选择0.3-0.5,最后确定在最恶劣的工况下计算所需电感量。在 CCM 模式下计算公式如下:

$$L_{BOOST} > \frac{V_{IN(MIN)}^{2*}(V_{OUT} - V_{IN(MIN)})^* 1000}{f^* \Delta l_1^* V_{OUT}^2} uH$$

(3)

$$L_{\text{BUCK}} > \frac{V_{\text{OUT}}^*(V_{\text{IN}(\text{MAX})} \cdot V_{\text{OUT}})^*1000}{f^*\Delta I_L^*V_{\text{IN}(\text{MAX})}} \text{ uH}$$

(4)

这里: f 是选择的工作频率, kHz

VIN<sub>(MIN)</sub> 是最小输入电压, V

VIN<sub>(MAX)</sub> 是最大输入电压, V

Vout 是设置输出电压, V

ΔIL 是电感纹波电流, A, 通常选择20~40%的最大输出电流

为了提高效率,通常还需要考虑电感材质,体积等因素。

### 9.3 功率 MOS 管的选择

LYF63303应用中有5个 NMOS。MOS 管选择需要关注 VBR、VDS、开通阈值 Vth、导通电阻 RDS、输入电容 Ciss 等参数。驱动电压由 IC 的 VCC 提供6.6V,最大驱动电流2A,使得 MOS 选择更加灵活。

#### 9.4 输入/输出电容的选择

IC 工作升压模式时,输入电流是连续的。工作在降压模式时输入电流不是连续的,所以以降压模式来计算输入电容能处理的最大纹波电流有效值,其公式如下:

$$I_{CIN} = I_{OUT(MAX)} \times \sqrt{\frac{V_{OUT}}{V_{IN}}} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

(5)

从上式子可知,当V<sub>IN</sub> = 2V<sub>OUT</sub> 时,出现最大值,此时,I<sub>CIN(MAX)</sub> = I<sub>OUT(MAX)</sub>/2.

当在升压模式时,输出电流不是连续的,需要输出电容为负载提供能量。所以以升压最恶劣的工况来计算输出电容的容值。 输出电压的纹波可以由以下公式来计算:

$$\Delta V_{\text{(BOOST,Cap)}} = \frac{I_{\text{OUT}(\text{MAX})}^*(V_{\text{OUT}} - V_{\text{IN(MIN)}})}{C_{\text{OUT}}^*V_{\text{OUT}}^*f} V$$

(6)

这里的 Cour 是输出电容的容值。

另外由于电容的ESR 引起的电压纹波也必须考虑进来,其计算公式如下:

$$\Delta V_{(BOOST,ESR)} = I_{OUT(MAX,BOOST)} *ESR$$

(7)

在降压模式下,输出电压纹波计算公式如下:

$$\Delta V_{OUT} \leq \Delta I_{L}^{*} \left( ESR + \frac{1}{8^{*}f^{*}C_{OUT}} \right)$$

(8)

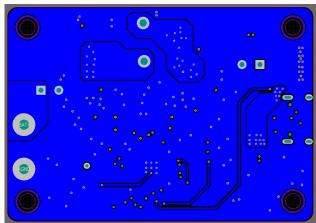

# 10 PCB LAYOUT

### 10.1 LAYOUT 原则

布局是良好电源设计的关键部分。以下的指导方针将帮助用户设计出具有最佳的功率转换性能、热性能和最小化产生不需要的 EMI 的 PCB。

- 1. 反馈网络,电阻 Rup 和 Rdown,应保持靠近 FB 引脚。保持 VBUS 反馈网络远离噪声节点,最好通过屏蔽层另一侧的一层。

- 2. 输入/输出旁路电容器必须放置在尽可能靠近 VIN/VBUS 引脚和接地的位置。有必要在 VIN 和 VBUS 附近放置陶瓷电容,以降低高频干扰的注入。

- 3. 对于电流采样信号脚(CSP、CSN)、(CSP2、CSN2)需要直接连接到检测电阻的两个端子上,尽可能走差分线,并且远离 BST1、BST2、SW1、SW2、HG1、HG2、LG1、LG2 等噪声节点。

- 4. 功率环路、驱动环路最小化

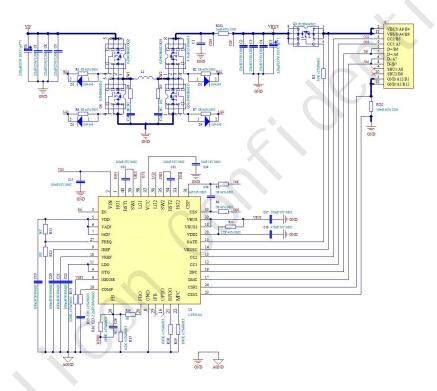

### 10.2 应用案例

图. 3 原理图

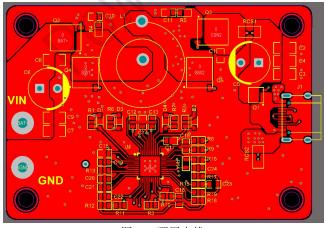

图. 5 底层走线

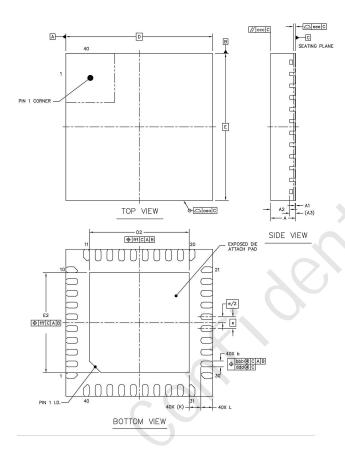

# 11 封装信息

## 11.1 封装图

### 11.2 封装尺寸

| 2 El AZ/CI | Dimension in Millimeters |         |      |  |  |  |  |  |  |

|------------|--------------------------|---------|------|--|--|--|--|--|--|

| Symbol     | MIN                      | NOM     | MAX  |  |  |  |  |  |  |

| A          | 0.8                      | 0.85    | 0. 9 |  |  |  |  |  |  |

| A1         | 0                        | 0.02    | 0.05 |  |  |  |  |  |  |

| A2         |                          | 0.65    |      |  |  |  |  |  |  |

| A3         | 0. 203 REF               |         |      |  |  |  |  |  |  |

| b          | 0. 15                    | 0. 2    | 0.25 |  |  |  |  |  |  |

| D          |                          | 5 BSC   |      |  |  |  |  |  |  |

| Е          |                          | 5 BSC   |      |  |  |  |  |  |  |

| е          |                          | 0.4 BSC |      |  |  |  |  |  |  |

| D2         | 3. 3                     | 3. 4    | 3. 5 |  |  |  |  |  |  |

| E2         | 3. 3                     | 3. 4    | 3. 5 |  |  |  |  |  |  |

| L          | 0.3 0.4 0.5              |         |      |  |  |  |  |  |  |

| K          |                          | 0.4 REF |      |  |  |  |  |  |  |

# 12 版本信息

| 版本      | 日期         | 撰写     | 页数 | 更新说明 |

|---------|------------|--------|----|------|

| Rev.1.0 | 2019-02-18 | Victor | 14 | 首次发布 |

|         |            |        |    |      |

|         |            |        |    |      |

|         |            |        |    |      |

|         |            |        |    |      |

|         |            |        |    |      |

|         |            |        |    |      |