# **Hardware Design Checklist**

#### 1.0 INTRODUCTION

This document provides a hardware design checklist for the Microchip KSZ8863MLL. These checklist items should be followed when utilizing the KSZ8863MLL in a new design. A summary of these items is provided in Section 9.0, "Hardware Checklist Summary," on page 10. Detailed information on these subjects can be found in the corresponding sections:

- · General Considerations on page 1

- · Power on page 1

- · Ethernet Signals on page 3

- · Clock Circuit on page 5

- · Digital Interfaces on page 6

- · Startup on page 7

- · Miscellaneous on page 9

#### 2.0 GENERAL CONSIDERATIONS

#### 2.1 Pin Check

Check the pinout of the part against the data sheet. Ensure all pins match the data sheet and are configured as inputs, outputs, or bidirectional for error checking.

#### 2.2 Ground

- The ground pin, GND and AGND, should be connected to the solid ground plane on the board.

- It is recommended that all ground connections be tied together to the same ground plane. Separate ground planes are not recommended.

#### 3.0 POWER

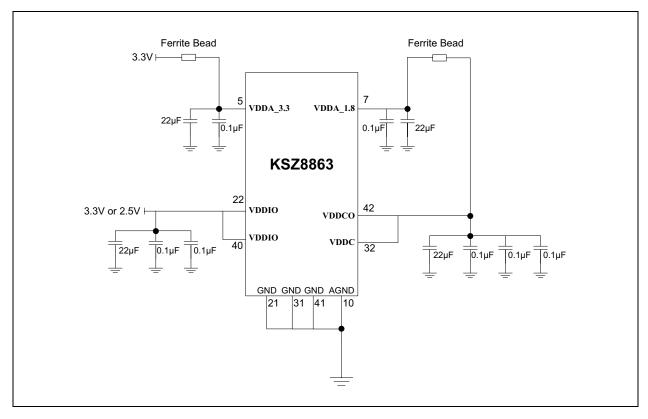

- KSZ8863MLL 3.3V analog supply (VDDA\_3.3) is on pin 5. A ferrite bead should be placed in series between the 3.3V supply and this pin. Be sure to place bulk capacitance on each side of the ferrite bead.

- The VDDA\_3.3 pin should have a 0.1 uF capacitor to decouple the device. The capacitor size should be SMD 0603 or smaller.

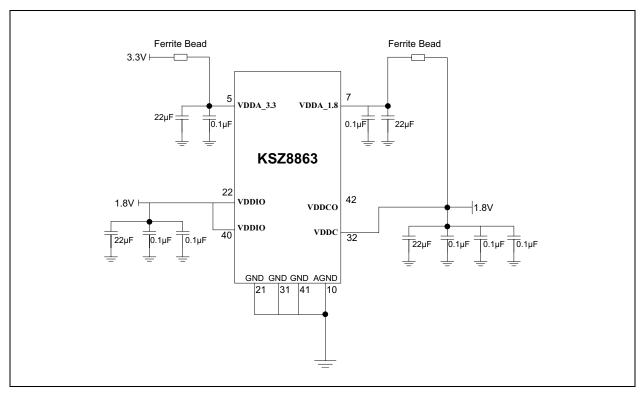

- Pins 22 and 40 (VDDIO) should be connected to the +1.8V, +2.5V, or +3.3V supply of the board.

- The 1.8V digital core supply (VDDC) is on pin 32. When VDDIO is 3.3V or 2.5V, connect this pin directly to the

1.8V regulator output (VDDCO) on pin 42. When VDDIO is 1.8V, an external 1.8V supply is required for this pin,

and this pin should not be connected to VDDCO.

- KSZ8863MLL 1.8V analog supply (VDDA\_1.8) is on pin 7. A ferrite bead should be placed in series between the 1.8V supply at pin 32 (VDDC) and this pin. Be sure to place bulk capacitance on each side of the ferrite bead.

The power and ground connections are shown in Figure 3-1 and Figure 3-2.

FIGURE 3-1: POWER AND GROUND CONNECTIONS FOR VDDIO = 3.3V OR 2.5V

FIGURE 3-2: POWER AND GROUND CONNECTIONS FOR VDDIO = 1.8V

#### 4.0 ETHERNET SIGNALS

#### 4.1 PHY No. 1 Interface

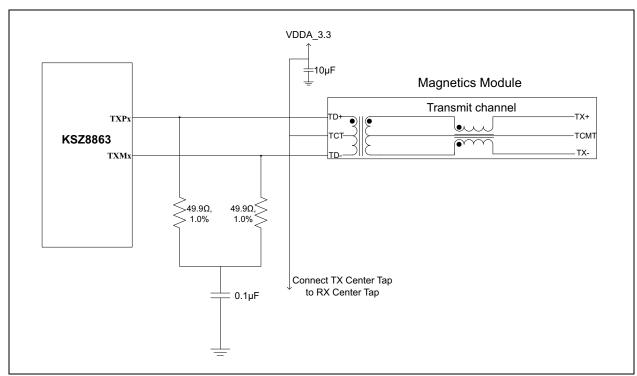

- TXP1 (pin 4): This pin is the transmit twisted pair output positive connection from the internal PHY. A 49.9Ω (1.0%) termination resistor with AC coupled to the digital ground through a 0.1 uF capacitor is required on this pin.

- TXM1 (pin 3): This pin is the transmit twisted pair output negative connection from the internal PHY. A 49.9Ω (1.0%) termination resistor with AC coupled to the digital ground through a 0.1 uF capacitor is required on this pin.

- For transmit channel connection and termination details, refer to Figure 4-1.

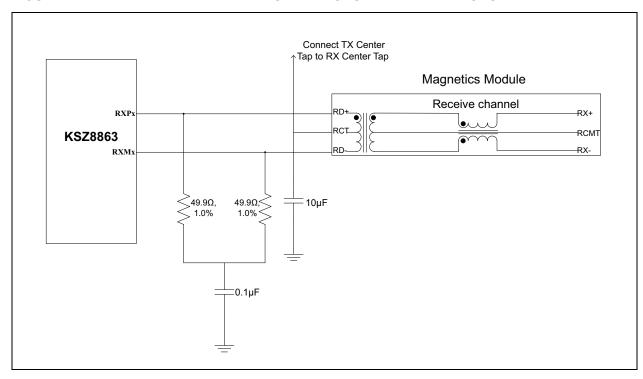

- RXP1 (pin 2): This pin is the receive twisted pair input positive connection to the internal PHY. A 49.9Ω (1.0%) termination resistor with AC coupled to the digital ground through a 0.1 uF capacitor is required on this pin.

- RXM1 (pin 1): This pin is the receive twisted pair input negative connection to the internal PHY. A 49.9Ω (1.0%) termination resistor with AC coupled to the digital ground through a 0.1 uF capacitor is required on this pin.

- For receive channel connection and termination details, refer to Figure 4-2.

#### 4.2 PHY No. 2 Interface

- TXP2 (pin 12): This pin is the transmit twisted pair output positive connection from the internal PHY. A 49.9Ω (1.0%) termination resistor with AC coupled to the digital ground through a 0.1 uF capacitor is required on this pin.

- TXM2 (pin 11): This pin is the transmit twisted pair output negative connection from the internal PHY. A 49.9Ω (1.0%) termination resistor with AC coupled to the digital ground through a 0.1 uF capacitor is required on this pin.

- For transmit channel connection and termination details, refer to Figure 4-1.

- RXP2 (pin 9): This pin is the receive twisted pair input positive connection to the internal PHY. A 49.9Ω (1.0%) termination resistor with AC coupled to the digital ground through a 0.1 uF capacitor is required on this pin.

- RXM2 (pin 8): This pin is the receive twisted pair input negative connection to the internal PHY. A 49.9Ω (1.0%) termination resistor with AC coupled to the digital ground through a 0.1 uF capacitor is required on this pin.

- For receive channel connection and termination details, refer to Figure 4-2.

#### FIGURE 4-1: TRANSMIT CHANNEL CONNECTIONS AND TERMINATIONS

#### FIGURE 4-2: RECEIVE CHANNEL CONNECTIONS AND TERMINATIONS

#### 4.3 Magnetics Connection

- The center tap connection on the KSZ8863MLL side for the transmit channel must be directly connected to VDDA (created from +3.3V). The transmit channel center tap of the magnetics also connects to the receive channel center tap of the magnetics. In addition, a 10 uF capacitor is required from the receive channel center tap of the magnetics to digital ground.

- The center tap connection on the KSZ8863MLL side for the receive channel is connected to the transmit channel center tap on the magnetics.

- The center tap connection on the cable side (RJ45 side) for the transmit channel should be terminated with a 75Ω resistor through a 1000 pF, 2 KV capacitor to chassis ground.

- The center tap connection on the cable side (RJ45 side) for the receive channel should be terminated with a 75Ω resistor through a 1000 pF, 2 KV capacitor to chassis ground.

- Only one 1000 pF, 2 KV capacitor to chassis ground is required. It is shared by both TX and RX center taps.

- · Assuming the design of an end-point device (NIC):

- Pin 1 of the RJ45 is TX+ and should trace through the magnetics to TXPx of the KSZ8863MLL.

- Pin 2 of the RJ45 is TX- and should trace through the magnetics to TXMx of the KSZ8863MLL.

- Pin 3 of the RJ45 is RX+ and should trace through the magnetics to RXPx of the KSZ8863MLL.

- Pin 6 of the RJ45 is RX- and should trace through the magnetics to RXMx of the KSZ8863MLL.

- When using the KSZ8863MLL device in the HP Auto MDIX mode of operation, the use of an Auto MDIX style

magnetics module is required.

#### 4.4 RJ45 Connector

- Pins 4 and 5 of the RJ45 connector interface to one pair of unused wires in CAT 5-type cables. These should be terminated to chassis ground through a 1000 pF, 2 KV capacitor. There are two methods of accomplishing this:

- Pins 4 and 5 can be connected together with two  $49.9\Omega$  resistors. The common connection of these resistors should be connected through a third  $49.9\Omega$  resistor to the 1000 pF, 2 KV capacitor.

- For a lower component count, the resistors can be combined. The two 49.9Ω resistors in parallel perform like

a  $25\Omega$  resistor. The  $25\Omega$  resistor in series with the  $49.9\Omega$  resistor causes the entire circuit to function as a  $75\Omega$  resistor. So, by shorting pins 4 and 5 together on the RJ45 and terminating them with a  $75\Omega$  resistor in series with the 1000 pF, 2 KV capacitor to chassis ground, an equivalent circuit is created.

- Pins 7 and 8 of the RJ45 connector interface to one pair of unused wires in CAT 5-type cables. These should be terminated to chassis ground through a 1000 pF, 2 KV capacitor. There are two methods of accomplishing this:

- Pins 7 and 8 can be connected together with two  $49.9\Omega$  resistors. The common connection of these resistors should be connected through a third  $49.9\Omega$  resistor to the 1000 pF, 2 KV capacitor.

- For a lower component count, the resistors can be combined. The two  $49.9\Omega$  resistors in parallel perform like a  $25\Omega$  resistor. The  $25\Omega$  resistor in series with the  $49.9\Omega$  resistor causes the entire circuit to function as a  $75\Omega$  resistor. Therefore, by shorting pins 7 and 8 together on the RJ45 and terminating them with a  $75\Omega$  resistor in series with the 1000 pF, 2 KV capacitor to chassis ground, an equivalent circuit is created.

- The RJ45 shield should be attached directly to chassis ground.

#### 5.0 CLOCK CIRCUIT

#### 5.1 Crystal and External Oscillator/Clock Connections

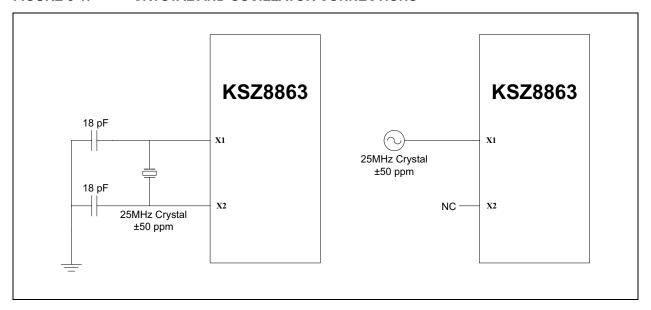

When using the KSZ8863MLL, a 25.000-MHz (±50ppm) crystal should be used to provide the clock source. For exact specifications and tolerances, refer to the latest revision of the *KSZ8863MLL Data Sheet*.

- X1 (pin 14) is the clock circuit input for the KSZ8863MLL device. This pin requires a capacitor to ground. One side

of the crystal connects to this pin.

- X2 (pin 15) is the clock circuit output for the KSZ8863MLL device. This pin requires a capacitor to ground. One side of the crystal connects to this pin.

- Since every system design is unique, the capacitor values are system dependent based on the CL specifications

of the crystal and the stray capacitance value. The PCB design, crystal, and layout all contribute to the characteristics of this circuit.

Alternately, a 25.000 MHz clock oscillator may be used to provide the clock source for the KSZ8863MLL. When using a single-ended clock source, X1 (pin 14) connects to a 3.3V-tolerant oscillator and X2 (pin 15) should be left floating as No Connect (NC).

FIGURE 5-1: CRYSTAL AND OSCILLATOR CONNECTIONS

#### 6.0 DIGITAL INTERFACES

#### 6.1 MII Interface

• The MII that the KSZ8863MLL provides is connected to the device's third MAC port. The MII default is PHY mode and can be set to MAC mode with the register 53 bit 7. Table 6-1 describes the signals used by the MII bus.

**Note:** The external MAC signals should also be checked to ensure the pin types are consistent and match correspondingly with the KSZ8863MLL pin types (that is, MII outputs are connected to the corresponding MII inputs). Do not depend only on the pin names to match the MII pin connections between two devices.

TABLE 6-1: MII CONNECTIONS

| PHY Mode (                        | Connections              |                     | MAC Mode Connections |                          |

|-----------------------------------|--------------------------|---------------------|----------------------|--------------------------|

| External MAC<br>Controller Signal | KSZ8863MLL PHY<br>Signal | Pin Description     | External PHY Signal  | KSZ8863MLL MAC<br>Signal |

| MTXEN                             | SMTXEN3                  | Transmit Enable     | MTXEN SMRXDV3        |                          |

| MTXER                             | SMTXER3                  | Transmit Error      | MTXER                | (NOT USED)               |

| MTXD3                             | SMTXD33                  | Transmit Data Bit 3 | MTXD3                | SMRXD33                  |

| MTXD2                             | SMTXD32                  | Transmit Data Bit 2 | MTXD2                | SMRXD32                  |

| MTXD1                             | SMTXD31                  | Transmit Data Bit 1 | MTXD1 SMRXD31        |                          |

| MTXD0                             | SMTXD30                  | Transmit Data Bit 0 | MTXD0 SMRXD30        |                          |

| MTXC                              | SMTXC3                   | Transmit Clock      | MTXC SMRXC3          |                          |

| MCOL                              | SCOL3                    | Collision Detection | MCOL SCOL3           |                          |

| MCRS                              | SCRS3                    | Carrier Sense       | MCRS SCRS3           |                          |

| MRXDV                             | SMRXDV3                  | Receive Data Valid  | MRXDV                | SMTXEN3                  |

| MRXER                             | (NOT USED)               | Receive Error       | MRXER                | SMTXER3                  |

| MRXD3                             | SMRXD33                  | Receive Data Bit 3  | MRXD3 SMTXD33        |                          |

| MRXD2                             | SMRXD32                  | Receive Data Bit 2  | MRXD2 SMTXD32        |                          |

| MRXD1                             | SMRXD31                  | Receive Data Bit 1  | MRXD1                | SMTXD31                  |

| MRXD0                             | SMRXD30                  | Receive Data Bit 0  | MRXD0                | SMTXD30                  |

| MRXC                              | SMRXC3                   | Receive Clock       | MRXC SMTXC3          |                          |

- The KSZ8863MLL does not provide the MRXER signal for the PHY mode operation and the MTXER signal for the MAC mode operation. Normally, MRXER indicates a receive error coming from the physical layer device and MTXER indicates a transmit error from the MAC device. Because the switch filters error frames, these MII error signals are not used by KSZ8863MLL. Therefore, for PHY mode operation, if the device interfacing with KSZ8863MLL has an MRXER input pin, it needs to be tied low. For MAC mode operation, if the device interfacing with KSZ8863MLL has an MTXER input pin, it also needs to be tied low.

- Provisions should be made for series terminations for all outputs on the MII interface. Series resistors enable the

designer to closely match the output driver impedance of the KSZ8863MLL and the PCB trace impedance to minimize ringing on these signals. Exact resistor values are application-dependent and must be analyzed in-system.

A suggested starting point for the value of these series resistors would be 22Ω.

#### 6.2 Series Termination Resistor Values

TABLE 6-2: SERIES TERMINATION RESISTOR VALUES

| Signal  | Series Resistor Value |

|---------|-----------------------|

| SMRXD33 | 22Ω                   |

| SMRXD32 | 22Ω                   |

| SMRXD31 | 22Ω                   |

| SMRXD30 | 22Ω                   |

| SMRXDV3 | 22Ω                   |

| SMRXC3  | 22Ω                   |

| SMTXC3  | 22Ω                   |

| SCOL3   | 22Ω                   |

| SCRS3   | 22Ω                   |

### 6.3 Required External Pull-ups

- When using the MII interface of the KSZ8863MLL with a MAC device on board, a pull-up resistor of 4.7 k $\Omega$  on the SDA\_MDIO signal (pin 37) is required.

- INTRN (pin 35) requires a 4.7 kΩ external pull-up resistor since this output is an open drain type. If INTRN is not used, the pull-up resistor is not required.

#### 7.0 STARTUP

#### 7.1 Reset Circuit

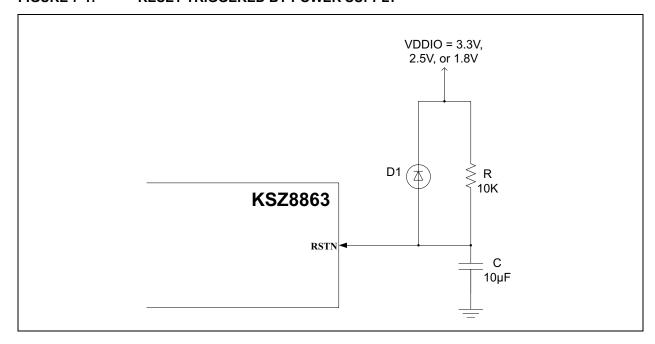

RSTN (pin 47) is an active-low reset input. This signal resets all logic and registers within the KSZ8863MLL. A hardware reset (RSTN assertion) is required following power-up. Please refer to the latest copy of the KSZ8863MLL Data Sheet for reset timing requirements. Figure 7-1 shows a recommended reset circuit for powering up the KSZ8863MLL device when reset is triggered by the power supply.

FIGURE 7-1: RESET TRIGGERED BY POWER SUPPLY

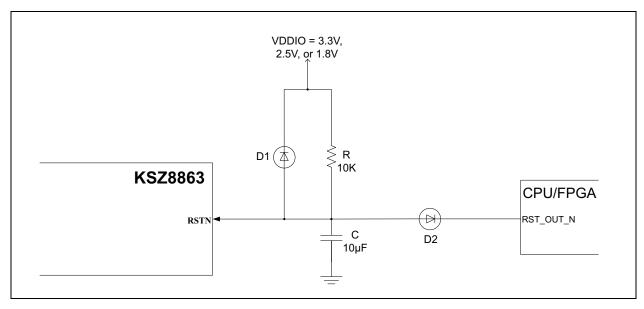

Figure 7-2 shows the recommended reset circuit for applications where reset is driven by an external CPU or FPGA. The reset out pin, RST\_OUT\_N, from CPU/FPGA provides the warm reset after power-up. If the Ethernet device and CPU/FPGA use the same VDDIO voltage, D2 can be removed and both reset pins can be connected directly.

FIGURE 7-2: RESET CIRCUIT INTERFACE WITH CPU/FPGA RESET OUTPUT

#### 7.2 Configuration Mode Pins (Strapping Options)

The default configuration of the 10/100 PHY for Speed, Duplex, Autonegotiation, flow control and Serial Bus mode functionality can be configured through strip option pins. The value of these ten pins are latched in upon power-up and reset. As indicated in the data sheet, each of these pins has either an internal pull-up or pull-down resistor to set the default strapping level. To choose the non-default option for a strapping pin, an external pull-up or pull-down resistor is needed. Resistor values can be 1 k $\Omega$  to 10 k $\Omega$ , except for pull-down resistors on LED pins that should be 1 k $\Omega$  or less to ensure they are pulled adequately low during reset. In some systems, the MAC receive input pins may drive high during power-up or reset, and consequently cause the PHY strap-in pins on the MII/RMII signals to be latched high. Refer to the KSZ8863MLL Data Sheet for the complete details on the operation of strapping pins.

The strapping option for pin 44 (P1LED0) determines whether port 1 autonegotiation is enabled or disabled. This pin has an internal pull-down, causing port 1 autonegotiation to be disabled by default. To enable port 1 autonegotiation, this pin needs an external 10  $k\Omega$  resistor to VDDIO.

It is also important to ensure that pins 45 and 46 (P2LED1 and P2LED0) strapping settings are correct for selecting the Serial Bus mode: either I<sup>2</sup>C master (EEPROM), I<sup>2</sup>C slave, SPI, or SMI/MIIM.

#### 7.3 LED Pins

The KSZ8863MLL provides two LED signals per port. These indicators display speed, link, and activity information about the current state of the PHY ports. The LED pins are active low and require a 220Ω series resistor. See KSZ8863MLL Data Sheet for further details on how to strap each pin for correct operation.

#### 8.0 MISCELLANEOUS

#### 8.1 ISET Resistor

**ISET** (pin 6) on the KSZ8863MLL should connect to digital ground through a 11.8 k $\Omega$  resistor with a tolerance of 1.0%. This pin is used to set up critical bias currents for the embedded 10/100 Ethernet physical device.

#### 8.2 Other Considerations

- Incorporate a large SMD footprint (SMD\_1210) to connect the chassis ground to the digital ground. This allows some flexibility at EMI testing for different grounding options. Leaving the footprint open allows the two grounds to remain separate. Shorting them together with a  $0\Omega$  resistor will connect them. For best performance, short them together with a cap or a ferrite bead.

- Be sure to incorporate enough bulk capacitors (4.7  $\mu F$  to 22  $\mu F$ ) for each power plane.

## 9.0 HARDWARE CHECKLIST SUMMARY

## TABLE 9-1: HARDWARE DESIGN CHECKLIST

| Section                               | Check                               | Explanation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ٧ | Notes |

|---------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------|

| Section 2.0, "General Considerations" | Section 2.1, "Pin Check"            | Verify if the pins match the data sheet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |       |

|                                       | Section 2.2, "Ground"               | Verify if grounds are tied together.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |       |

| Section 3.0, "Power"                  | Section 3.0, "Power"                | Ensure that VDDA_3.3 is in the range 3.135V to 3.465V, and a 22 µF capacitor is on each pin.  Ensure that VDDIO is connected to 3.3V, 2.5V, or 1.8V, with a ±5% tolerance each. Operating ranges are as follows:  - 3.135V to 3.465V for 3.3V  - 2.375V to 2.625V for 2.5V  - 1.710V to 1.890V for 1.8V  If VDDIO is 3.3V or 2.5V, use pin 42 as the 1.8V power source, and do not use an external 1.8V source.  If VDDIO is 1.8V, leave pin 42 open, and use an external 1.8V source for pins 32 and 7.  Ferrite beads are recommended for VDDA_3.3 and VDDA_1.8. |   |       |

| Section 4.0, "Ethernet Signals"       | Section 4.1, "PHY No. 1 Interface"  | Verify the termination resistors (49.9 $\Omega$ , 1.0%) and capacitors (0.1 uF) on the TX and RX pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |       |

|                                       | Section 4.2 "PHY No. 2 Interface"   | Verify the termination resistors (49.9 $\Omega$ , 1.0%) and capacitors (0.1 uF) on the TX and RX pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |       |

|                                       | Section 4.3, "Magnetics Connection" | Verify if the center taps are connected to the VDDA_3.3 (pin 3) supply on the KSZ8863MLL device side and are terminated with $75\Omega$ resistors through a 1000 pF, 2 kV capacitor to chassis ground on the RJ45 line side.                                                                                                                                                                                                                                                                                                                                       |   |       |

|                                       | Section 4.4, "RJ45 Connector"       | Verify if pins 4/5 and 7/8 of the RJ45 connect to CAT 5 cable and are terminated to chassis ground through a 1000 pF, 2 kV capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                              |   |       |

| TABLE 9-1: | HAF | RDWARE DESIGN CHECKLIST | (CONTINUED) |

|------------|-----|-------------------------|-------------|

| Section    |     | Check                   |             |

| Section                              | Section Check Explanation v                                      |                                                                                                                                                                                                                                 | ٧ | Notes |

|--------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------|

| Section 5.0, "Clock Circuit"         | Section 5.1, "Crystal and External Oscillator/Clock Connections" | Verify usage of 25 MHz (±50 ppm) crystal or external oscillator/clock.                                                                                                                                                          |   |       |

| Section 6.0, "Digital<br>Interfaces" | Section 6.1, "MII Interface"                                     | Confirm proper MII signals between MAC and PHY interface with correct series termination resistors. (22 $\Omega$ ).                                                                                                             |   |       |

|                                      | Section 6.2 "Series Termination Resistor Values"                 | Confirm proper MII signals between MAC and PHY interface with correct series termination resistors. (22 $\Omega$ ).                                                                                                             |   |       |

|                                      | Section 6.3 "Required External Pull-<br>ups"                     | <ul> <li>A 4.7 kΩ pull-up on SDA_MDIO signal is required when using MII interface with a MAC device.</li> <li>A 4.7 kΩ pull-up is required if INTRN signal is used.</li> </ul>                                                  |   |       |

| Section 7.0, "Startup"               | Section 7.1, "Reset Circuit"                                     | Confirm proper reset circuit design: standalone reset or external CPU/FPGA reset.                                                                                                                                               |   |       |

|                                      | Section 7.2 "Configuration Mode Pins (Strapping Options)"        | <ul> <li>Confirm if the strapping options are correctly configured as per the application requirements.</li> <li>To choose the non-default option, an external pull-up or pull-down of 1 kΩ to 10 kΩ should be used.</li> </ul> |   |       |

|                                      | Section 7.3, "LED Pins"                                          | If used, confirm proper connections, taking into consideration shared functionality on select LED pins.                                                                                                                         |   |       |

| Section 8.0, "Miscella-<br>neous"    | Section 8.1, "ISET Resistor"                                     | Confirm proper ISET resistor (11.8 k $\Omega$ , 1.0%) with a 100 uF capacitor in parallel.                                                                                                                                      |   |       |

|                                      | Section 8.2, "Other Considerations"                              | <ul> <li>Incorporate a large SMD footprint (SMD_1210) to connect the chassis ground to the digital ground.</li> <li>Incorporate sufficient power plane bulk capacitors (4.7 μF to 22 μF).</li> </ul>                            |   |       |

#### **APPENDIX A: REVISION HISTORY**

#### **TABLE A-1: REVISION HISTORY**

| Revision Level & Date     | Section/Figure/Entry | Correction |

|---------------------------|----------------------|------------|

| DS00002713A<br>(06-14-18) | Initial release.     |            |

| KS           | 78           | 2 | 63 | M   | H |  |

|--------------|--------------|---|----|-----|---|--|

| $\mathbf{I}$ | $\mathbf{z}$ |   | uJ | IVI |   |  |

| NOTES: |

|--------|

|--------|

#### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at <a href="www.microchip.com">www.microchip.com</a>. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's

guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

#### CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

#### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- · Field Application Engineer (FAE)

- · Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, AnyRate, AVR, AVR logo, AVR Freaks, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KeeLoq, Kleer, LANCheck, LINK MD, maXStylus, maXTouch, MediaLB, megaAVR, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, Prochip Designer, QTouch, SAM-BA, SpyNIC, SST, SST Logo, SuperFlash, tinyAVR, UNI/O, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, EtherSynch, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and Quiet-Wire are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, Anyln, AnyOut, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, INICnet, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, memBrain, Mindi, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries

All other trademarks mentioned herein are property of their respective companies.

© 2018, Microchip Technology Incorporated, All Rights Reserved.

ISBN: 978-1-5224-3215-9

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# Worldwide Sales and Service

#### **AMERICAS**

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200

Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/ support

Web Address:

www.microchip.com

Atlanta Duluth, GA

Tel: 678-957-9614 Fax: 678-957-1455

**Austin, TX** Tel: 512-257-3370

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Dallas

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI

Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis

Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC Tel: 919-844-7510

New York, NY Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110 Tel: 408-436-4270

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

**China - Beijing** Tel: 86-10-8569-7000

China - Chengdu Tel: 86-28-8665-5511

**China - Chongqing** Tel: 86-23-8980-9588

**China - Dongguan** Tel: 86-769-8702-9880

**China - Guangzhou** Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

China - Nanjing Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

**China - Shanghai** Tel: 86-21-3326-8000

China - Shenyang Tel: 86-24-2334-2829

**China - Shenzhen** Tel: 86-755-8864-2200

China - Suzhou Tel: 86-186-6233-1526

**China - Wuhan** Tel: 86-27-5980-5300

**China - Xian** Tel: 86-29-8833-7252

China - Xiamen

Tel: 86-592-2388138

China - Zhuhai Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631

India - Pune Tel: 91-20-4121-0141

Japan - Osaka

Tel: 81-6-6152-7160 Japan - Tokyo

Tel: 81-3-6880- 3770

**Korea - Daegu** Tel: 82-53-744-4301

Korea - Seoul Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

**Singapore** Tel: 65-6334-8870

**Taiwan - Hsin Chu** Tel: 886-3-577-8366

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600

Thailand - Bangkok Tel: 66-2-694-1351

Vietnam - Ho Chi Minh Tel: 84-28-5448-2100

#### **EUROPE**

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen Tel: 45-4450-2828

Fax: 45-4485-2829 Finland - Espoo Tel: 358-9-4520-820

France - Paris

Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79

**Germany - Garching** Tel: 49-8931-9700

**Germany - Haan** Tel: 49-2129-3766400

Germany - Heilbronn Tel: 49-7131-67-3636

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Rosenheim Tel: 49-8031-354-560

Israel - Ra'anana Tel: 972-9-744-7705

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Padova Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7289-7561

**Poland - Warsaw** Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**Sweden - Gothenberg** Tel: 46-31-704-60-40

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820