#### 3.3-V RS-485 TRANSCEIVERS

#### **FEATURES**

- Operates With a 3.3-V Supply

- Bus-Pin ESD Protection Exceeds 16 kV HBM

- 1/8 Unit-Load Option Available (Up to 256 Nodes on the Bus)

- Optional Driver Output Transition Times for Signaling Rates (1) of 1

Mbps, 10 Mbps, and 32 Mbps

- Meets or Exceeds the Requirements of ANSI TIA/EIA-485-A

- Bus-Pin Short Circuit Protection From -7 V to 12 V

- Low-Current Standby Mode . . . 1 μA Typical

- Open-Circuit, Idle-Bus, and Shorted-Bus Failsafe Receiver

- Thermal Shutdown Protection

- Glitch-Free Power-Up and Power-Down Protection for Hot-Plugging Applications

#### ORDERING INFORMATION

| DEVICE          | Package Type | MARKING | Packing | Packing Qty  |

|-----------------|--------------|---------|---------|--------------|

| SN65HVD10EIN    | DIP8L        | 65HVD10 | TUBE    | 2000pcs/box  |

| SN65HVD11EIN    | DIP8L        | 65HVD11 | TUBE    | 2000pcs/box  |

| SN65HVD12EIN    | DIP8L        | 65HVD12 | TUBE    | 2000pcs/box  |

| SN65HVD10EIM/TR | SOP8L        | 65HVD10 | REEL    | 2500pcs/reel |

| SN65HVD11EIM/TR | SOP8L        | 65HVD11 | REEL    | 2500pcs/reel |

| SN65HVD12EIM/TR | SOP8L        | 65HVD12 | REEL    | 2500pcs/reel |

#### DESCRIPTION

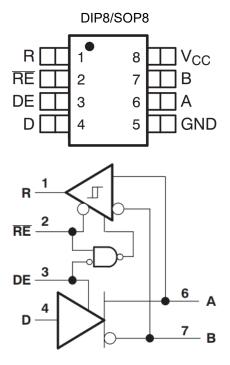

The SN65HVD10, SN65HVD11, and SN65HVD12, combine a 3-state differential line driver and differential input line receiver that operate with a single 3.3-V power supply. They are designed for balanced transmission lines and meet or exceed ANSI standard TIA/EIA-485-A and ISO 8482:1993.

These differential bus transceivers are monolithic integrated circuits designed for bidirectional data communication on multipoint bus-transmission lines.

The drivers and receivers have active-high and active-low enables respectively, that can be externally connected together to function as direction control.

Very low device standby supply current can be achieved by disabling the driver and the receiver.

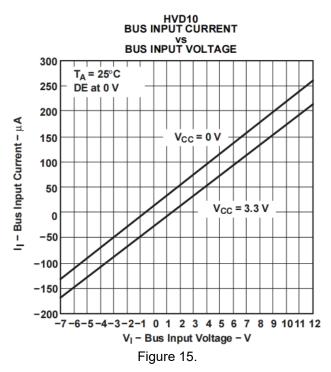

The driver differential outputs and receiver differential inputs connect internally to form a differential input/output (I/O) bus port that is designed to offer minimum loading to the bus whenever the driver is disabled or VCC = 0. These parts feature wide positive and negative common-mode voltage ranges, making them suitable for party-line applications.

1 / 17

#### **APPLICATIONS**

- Digital Motor Control

- Utility Meters

- Chassis-to-Chassis Interconnects

- Electronic Security Stations

- Industrial Process Control

- Building Automation

- Point-of-Sale (POS) Terminals and Networks

#### **Pin Connection**

(1) The signaling rate of a line is the number of voltage transitions that are made per second expressed in the units bps (bits per second).

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range unless otherwise noted (1) (2)

|                                      |                                     |                                   | UNIT                         |  |  |  |

|--------------------------------------|-------------------------------------|-----------------------------------|------------------------------|--|--|--|

| V <sub>CC</sub> Supply voltage range | је                                  |                                   | –0.3 V to 6 V                |  |  |  |

| Voltage range at A or B              |                                     |                                   | –9 V to 14 V                 |  |  |  |

| Input voltage range at D,            | DE, R or RE                         | -0.5 V to V <sub>CC</sub> + 0.5 V |                              |  |  |  |

| Voltage input range, trans           | –50 V to 50 V                       |                                   |                              |  |  |  |

| Io Receiver output cur               | Io Receiver output current          |                                   |                              |  |  |  |

|                                      | Livers are less divines adai(3)     | A, B, and GND                     | ±16 kV                       |  |  |  |

| Electrostaticdischarge               | Human body model <sup>(3)</sup>     | All pins                          | ±4 kV                        |  |  |  |

|                                      | Charged-device model <sup>(4)</sup> | All pins charge                   | ±1 kV                        |  |  |  |

| Continuous total power d             | issipation                          |                                   | See Dissipation Rating Table |  |  |  |

| Electrical Fast Transient/           | Burst <sup>(5)</sup>                | A, B, and GND                     | ±4 kV                        |  |  |  |

| T <sub>J</sub> Junction temperatu    | re                                  |                                   | 170°C                        |  |  |  |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) All voltage values, except differential I/O bus voltages, are with respect to network ground terminal.

- (3) Tested in accordance with JEDEC Standard 22, Test Method A114-A and IEC 60749-26.

- (4) Tested in accordance with JEDEC Standard 22, Test Method C101.

- (5) Tested in accordance with IEC 61000-4-4.

#### RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range unless otherwise noted

|                                   |                               |                            | MIN   | NOM | MAX | UNIT |  |

|-----------------------------------|-------------------------------|----------------------------|-------|-----|-----|------|--|

| VCC                               | Supply voltage                |                            | 3     |     | 3.6 |      |  |

| V <sub>I</sub> or V <sub>IC</sub> | Voltage at any bus terminal ( | separately or common mode) | _7(1) |     | 12  |      |  |

| VIH                               | High-level input voltage      | D, DE, RE                  | 2     |     | VCC | V    |  |

| VIL                               | Low-level input voltage       | D, DE, RE                  | 0     |     | 8.0 |      |  |

| VID                               | Differential input voltage    | Figure 7                   | -12   |     | 12  |      |  |

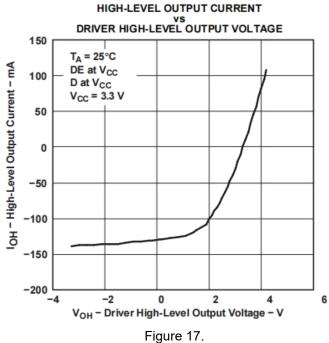

| ЮН                                | High level output ourrent     | Driver                     |       |     | -60 | A    |  |

| 100                               | High-level output current     | Receiver                   |       |     | -8  | mA   |  |

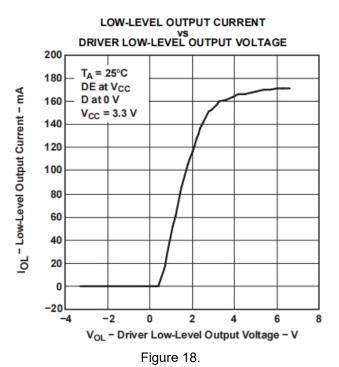

| loi                               | Lave lavel autout accoment    | Driver                     |       |     | 60  | mA   |  |

| lOL                               | Low-level output current      | Receiver                   |       |     | 8   |      |  |

| RL                                | Differential load resistance  |                            | 54    | 60  |     | Ω    |  |

| CL                                | Differential load capacitance |                            | 50    |     |     | pF   |  |

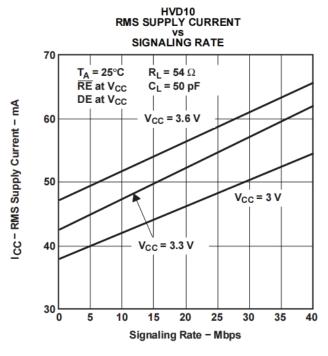

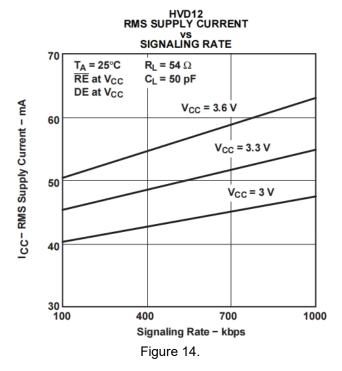

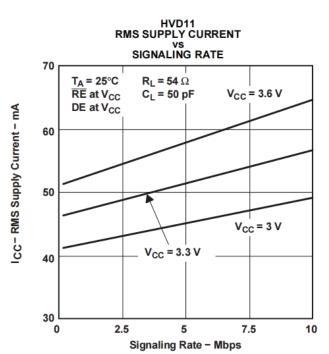

|                                   |                               | HVD10                      |       |     | 32  |      |  |

| Signaling r                       | ate                           | HVD11                      |       |     | 10  | Mbps |  |

|                                   |                               | HVD12                      |       |     | 1   |      |  |

| T.I. (2)                          | Junction temperature          |                            |       |     | 145 | °C   |  |

<sup>(1)</sup> The algebraic convention, in which the least positive (most negative) limit is designated as minimum is used in this data sheet.

#### DRIVER ELECTRICAL CHARACTERISTICS

over recommended operating conditions unless otherwise noted

|                          | PARAMETER                                       |                                                                       | TEST                                                              | MIN                                             | TYP <sup>(1)</sup> | MAX  | UNIT |    |

|--------------------------|-------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------|--------------------|------|------|----|

| VIK                      | Input clamp voltage                             |                                                                       | I <sub>I</sub> = -18 mA                                           |                                                 | -1.5               |      |      | ٧  |

|                          |                                                 |                                                                       | I <sub>O</sub> = 0                                                | 2                                               |                    | VCC  |      |    |

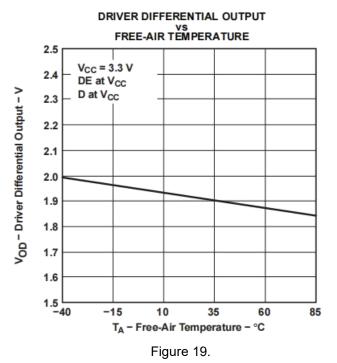

| V <sub>OD</sub>          | Differential output voltage <sup>(2)</sup>      |                                                                       | $R_L = 54 \Omega$ , Se                                            | e Figure 1                                      | 1.5                |      |      | V  |

|                          |                                                 |                                                                       | $V_{\text{test}} = -7 \text{ V to}$                               | 12 V, See Figure 2                              | 1.5                |      |      |    |

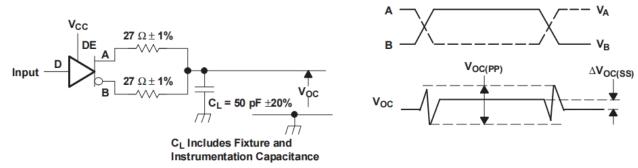

| $\Delta  V_{\text{OD}} $ | Change in magnitude of differentia              | l outputvoltage                                                       | See Figure 1                                                      | and Figure 2                                    | -0.2               |      | 0.2  | V  |

| VOC(PP)                  | Peak-to-peak common-mode outpu                  | ut voltage                                                            |                                                                   |                                                 |                    | 400  |      | mV |

| Voc(ss)                  | Steady-state common-mode outpu                  | t voltage                                                             | See Figure 3                                                      |                                                 | 1.4                |      | 2.5  | V  |

| ΔV <sub>OC</sub> (SS)    | Change in steady-state common-molecular voltage | See Figure 3                                                          |                                                                   | -0.05                                           |                    | 0.05 | ٧    |    |

| loz                      | High-impedance output current                   |                                                                       | See receiver i                                                    |                                                 |                    |      |      |    |

| li                       | I lament accomment                              |                                                                       |                                                                   |                                                 | -100               | 0    |      | μA |

| II .                     | Input current                                   | DE                                                                    |                                                                   |                                                 | 0                  |      | 100  | μΛ |

| los                      | Short-circuit output current                    |                                                                       | –7 V ≤ V <sub>0</sub> ≤ 1                                         | -250                                            |                    | 250  | mA   |    |

| C <sub>(OD)</sub>        | Differential output capacitance                 |                                                                       | V <sub>OD</sub> = 0.4 sin (4E6πt) + 0.5 V,                        |                                                 |                    | 16   |      | pF |

| -(00)                    | Differential output capacitance                 | DE at 0 V                                                             | 10                                                                |                                                 |                    | Pi   |      |    |

|                          |                                                 |                                                                       | RE at V <sub>CC</sub> ,<br>D & DE at<br>V <sub>CC</sub> ,No load  | Receiver disabled and driver enabled            |                    | 9    | 15.5 | mA |

| ICC                      | Supply current                                  |                                                                       | RE at V <sub>CC</sub> , D at V <sub>CC</sub> , DE at 0 V, No load | Receiver disabled and driver disabled (standby) |                    | 1    | 5    | μА |

|                          |                                                 | RE at 0 V, D & DE at Vcc,No load  Receiver enabled and driver enabled |                                                                   |                                                 | 9                  | 15.5 | mA   |    |

<sup>(1)</sup> All typical values are at 25°C and with a 3.3-V supply.

<sup>(2)</sup> See thermal characteristics table for information regarding this specification.

<sup>(2)</sup> For TA > 85°C, VCC is ±5%.

#### **DRIVER SWITCHING CHARACTERISTICS**

over recommended operating conditions unless otherwise noted

|                         | PARAMETER                                           |                | TEST CONDITIONS                           | MIN | TYP <sup>(1)</sup> | MAX | UNIT |  |

|-------------------------|-----------------------------------------------------|----------------|-------------------------------------------|-----|--------------------|-----|------|--|

|                         | Dronagation delay time                              | HVD10          |                                           | 5   | 8.5                | 16  |      |  |

| tPLH                    | Propagation delay time, low-to-high-level output    | HVD11          |                                           | 18  | 25                 | 40  | ns   |  |

|                         | low-to-nigh-level output                            | HVD12          |                                           | 135 | 200                | 300 |      |  |

|                         | Dropogation delay time                              | HVD10          |                                           | 5   | 8.5                | 16  |      |  |

| tPHL                    | Propagation delay time,<br>high-to-low-level output | HVD11          |                                           | 18  | 25                 | 40  | ns   |  |

|                         | riigii-to-low-level output                          | HVD12          | -                                         | 135 | 200                | 300 |      |  |

|                         |                                                     | HVD10          | $R_L = 54 \Omega$ , $C_L = 50 pF$ ,       | 3   | 4.5                | 10  |      |  |

| t <sub>r</sub>          | Differential output signal rise time                | HVD11          | See Figure 4                              | 10  | 20                 | 30  | ns   |  |

|                         |                                                     | HVD12          | Occ riguic 4                              | 100 | 170                | 300 |      |  |

|                         |                                                     | HVD10          |                                           | 3   | 4.5                | 10  |      |  |

| t <sub>f</sub>          | Differential output signal fall time                | HVD11          |                                           | 10  | 20                 | 30  | ns   |  |

|                         |                                                     | HVD12          |                                           | 100 | 170                | 300 |      |  |

|                         |                                                     | HVD10          |                                           |     |                    | 1.5 | ns   |  |

| <sup>t</sup> sk(p)      | Pulse skew $( t_{PHL} - t_{PLH} )$                  | HVD11          |                                           |     |                    | 2.5 |      |  |

|                         |                                                     | HVD12          |                                           |     |                    | 7   |      |  |

|                         |                                                     | HVD10          |                                           |     |                    | 6   |      |  |

| <sup>t</sup> sk(pp) (2) | Part-to-part skew                                   | HVD11          |                                           |     |                    | 11  | ns   |  |

|                         |                                                     | HVD12          |                                           |     |                    | 100 |      |  |

|                         | Propagation delay time,                             | HVD10          | 4                                         |     | 31                 |     |      |  |

| tPZH                    | high-impedance-to-high-level output                 | HVD11          |                                           |     | 55<br>300          |     |      |  |

|                         | mgn-impedance to-nigh-level output                  |                | $R_L$ = 110 Ω, RE at 0 V,                 |     |                    |     |      |  |

|                         | Propagation delay time,                             | HVD10          | See Figure 5                              | 25  |                    |     |      |  |

| tPHZ                    | high-level-to-high-impedance output                 | HVD11          | 4                                         | 55  |                    |     | ns   |  |

|                         | mg// lover to mg// impodance output                 | HVD12          |                                           |     |                    | 300 |      |  |

|                         | Propagation delay time,                             | HVD10          |                                           |     |                    | 26  |      |  |

| tPZL                    | high-impedance-to-low-level output                  | HVD11          |                                           |     |                    | 55  | ns   |  |

|                         | - Ing. Impode to to low lover edipat                |                | $R_L$ = 110 Ω, RE at 0 V,                 |     |                    | 300 |      |  |

|                         | Propagation delay time,                             | HVD10          | See Figure 6                              |     |                    | 26  |      |  |

| t <sub>PLZ</sub>        | low-level-to-high-impedance output                  | HVD11<br>HVD12 | -                                         | 75  |                    |     | ns   |  |

|                         | 10W-10VOF to High Impedance output                  |                |                                           |     |                    | 400 |      |  |

| tPZH                    | Propagation delay time, standby-to-high-leve        | el output      | $R_L$ = 110 Ω, RE at 3 V,<br>See Figure 5 |     |                    | 6   | μs   |  |

| tPZL                    | Propagation delay time, standby-to-low-leve         | l output       | $R_L$ = 110 Ω, RE at 3 V,<br>See Figure 6 |     |                    | 6   | μs   |  |

<sup>(1)</sup> All typical values are at 25°C and with a 3.3-V supply.

<sup>(2)</sup> tsk(pp) is the magnitude of the difference in propagation delay times between any specified terminals of two devices when both devices operate with the same supply voltages, at the same temperature, and have identical packages and test circuits.

### RECEIVER ELECTRICAL CHARACTERISTICS

over recommended operating conditions unless otherwise noted

|                  | PARAMETER                                                 |                                                                                                                                                      | TEST CONDITI              | ONS                    | MIN   | TYP    | MAX   | UNIT |

|------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------------|-------|--------|-------|------|

| V <sub>IT+</sub> | Positive-going input threshold voltage                    | I <sub>O</sub> = -8 mA                                                                                                                               |                           |                        |       | -0.065 | -0.01 |      |

| VIT-             | Negative-going input thresholdvoltage                     | I <sub>O</sub> = 8 mA                                                                                                                                |                           |                        | -0.2  | -0.1   |       | V    |

| V <sub>hys</sub> | Hysteresis voltage (V <sub>IT+</sub> - V <sub>IT-</sub> ) |                                                                                                                                                      |                           |                        |       | 35     |       | mV   |

| VIK              | Enable-input clamp voltage                                | I <sub>I</sub> = -18 mA                                                                                                                              |                           |                        | -1.5  |        |       | V    |

| Vон              | High-level output voltage                                 | V <sub>ID</sub> = 200 mV,                                                                                                                            | $I_{OH} = -8 \text{ mA},$ | See Figure 7           | 2.4   |        |       | V    |

| VOL              | Low-level output voltage                                  | V <sub>ID</sub> = -200<br>mV,                                                                                                                        | I <sub>OL</sub> = 8 mA,   | See Figure 7           |       |        | 0.4   | V    |

| loz              | High-impedance-state output current                       | $V_0 = 0$ or $V_{CC}$                                                                                                                                | RE at V <sub>CC</sub>     |                        | -1    |        | 1     | μA   |

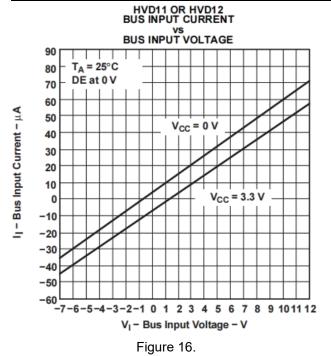

|                  |                                                           | V <sub>A</sub> or V <sub>B</sub> = 12 \                                                                                                              | <b>/</b>                  |                        |       | 0.05   | 0.11  |      |

|                  |                                                           | $V_A 	ext{ or } V_B = 12 	ext{ V},  V_{CC} = 0 	ext{ V}$ $V_A 	ext{ or } V_B = -7 	ext{ V}$ $V_A 	ext{ or } V_B = -7 	ext{ V},  V_{CC} = 0 	ext{ V}$ |                           | HVD11, HVD12,          |       | 0.06   | 0.13  |      |

|                  |                                                           |                                                                                                                                                      |                           | Other input at 0 V     | -0.1  | -0.05  |       | mA   |

| ١.               | Due invest comment                                        |                                                                                                                                                      |                           |                        | -0.05 | -0.04  |       |      |

| l lı             | I <sub>I</sub> Bus input current                          | V <sub>A</sub> or V <sub>B</sub> = 12 \                                                                                                              | <b>/</b>                  |                        |       | 0.2    | 0.5   |      |

|                  |                                                           | $V_A$ or $V_B = 12 V$ , $V_{CC} = 0 V$                                                                                                               |                           | HVD10,                 |       | 0.25   | 0.5   | ^    |

|                  |                                                           | $V_A$ or $V_B = -7$                                                                                                                                  | <b>/</b>                  | Other input at 0 V     | -0.4  | -0.2   |       | mA   |

|                  |                                                           | $V_A$ or $V_B = -7$                                                                                                                                  | V, V <sub>CC</sub> = 0 V  |                        | -0.4  | -0.15  |       |      |

| lіН              | High-level input current, RE                              | V <sub>IH</sub> = 2 V                                                                                                                                |                           |                        | -30   |        | 0     | μA   |

| ΙΙL              | Low-level input current, RE                               | V <sub>IL</sub> = 0.8 V                                                                                                                              |                           |                        | -30   |        | 0     | μA   |

| CID              | Differential input capacitance                            | V <sub>ID</sub> = 0.4 sin (4                                                                                                                         | E6πt) + 0.5 V, D          | E at 0 V               |       | 15     |       | pF   |

|                  |                                                           | RE at 0 V,<br>D & DE at 0 V,<br>No load                                                                                                              | Receiver enab             | led and driverdisabled |       | 4      | 8     | mA   |

| ICC              | Supply current                                            | RE at V <sub>CC</sub> , D at V <sub>CC</sub> , DE at 0 V, No load                                                                                    | Receiver disab            |                        |       | 1      | 5     | μА   |

|                  |                                                           | RE at 0 V,<br>D & DE at V <sub>cc</sub> ,<br>No load                                                                                                 | Receiver enab             |                        | 9     | 15.5   | mA    |      |

<sup>(1)</sup> All typical values are at 25°C and with a 3.3-V supply.

#### RECEIVER SWITCHING CHARACTERISTICS

over recommended operating conditions unless otherwise noted

|                         | PARAMETER                                         |                | TEST CONDITIONS                         | MIN  | TYP(1) | MAX | UNIT |  |

|-------------------------|---------------------------------------------------|----------------|-----------------------------------------|------|--------|-----|------|--|

| t <sub>PLH</sub> Propa  | agation delay time, low-to-high-level output      | HVD10          |                                         | 12.5 | 20     | 25  | ns   |  |

| t <sub>PHL</sub> Propa  | agation delay time, high-to-low-level output      | HVD10          |                                         | 12.5 | 20     | 25  | IIS  |  |

| t <sub>PLH</sub> Propa  | agation delay time, low-to-high-level output      | HVD11<br>HVD12 | V <sub>ID</sub> = -1.5 V to 1.5 V,      | 30   | 55     | 70  | ns   |  |

| t <sub>PHL</sub> Propa  | agation delay time, high-to-low-level output      | HVD11<br>HVD12 | C <sub>L</sub> = 15 pF,<br>See Figure 8 | 30   | 55     | 70  | ns   |  |

|                         |                                                   | HVD10          |                                         |      |        | 1.5 |      |  |

| t <sub>sk(p)</sub> Puls | e skew ( t <sub>PHL</sub> - t <sub>PLH</sub>  )   | HVD11          |                                         |      |        | 4   | ns   |  |

|                         |                                                   | HVD12          |                                         |      |        | 4   |      |  |

|                         |                                                   | HVD10          |                                         |      |        | 8   |      |  |

| t <sub>sk(pp)</sub> (2) | Part-to-part skew                                 | HVD11          |                                         |      |        | 15  | ns   |  |

|                         |                                                   | HVD12          |                                         |      |        | 15  |      |  |

| t <sub>r</sub>          | Output signal rise time                           |                | C <sub>L</sub> = 15 pF,                 | 1    | 2      | 5   |      |  |

| <b>t</b> f              | Output signal fall time                           |                | See Figure 8                            | 1    | 2      | 5   | ns   |  |

| t <sub>PZH</sub> (1)    | Output enable time to high level                  |                |                                         |      |        | 15  |      |  |

| t <sub>PZL</sub> (1)    | Output enable time to low level                   |                | C <sub>L</sub> = 15 pF, DE at 3 V,      |      |        | 15  |      |  |

| t <sub>PHZ</sub>        | Output disable time from high level               |                | See Figure 9                            |      |        | 20  | ns   |  |

| t <sub>PLZ</sub>        | Output disable time from low level                |                |                                         |      | 15     |     |      |  |

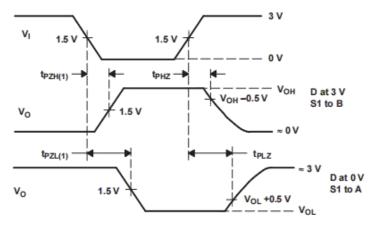

| t <sub>PZH</sub> (2)    | Propagation delay time, standby-to-high-level out | tput           | C <sub>L</sub> = 15 pF, DE at 0,        |      |        | 6   |      |  |

| t <sub>PZL</sub> (2)    | Propagation delay time, standby-to-low-level outp | out            | See Figure 10                           |      |        | 6   | μs   |  |

<sup>(1)</sup> All typical values are at 25°C and with a 3.3-V supply

#### PARAMETER MEASUREMENT INFORMATION

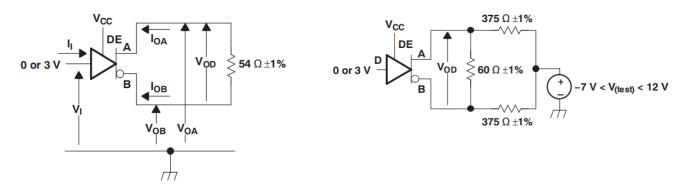

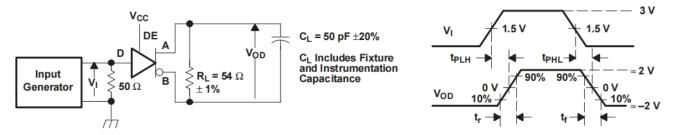

Figure 1. Driver VOD Test Circuit and Voltage and Current Definitions

Figure 2. Driver VOD With Common-Mode Loading

Test Circuit

<sup>(2)</sup> tsk(pp) is the magnitude of the difference in propagation delay times between any specified terminals of two devices when both devices operate with the same supply voltages, at the same temperature, and have identical packages and test circuits.

Input: PRR = 500 kHz, 50% Duty Cycle, $t_r$ <6ns,  $t_f$ <6ns,  $Z_O$  = 50  $\Omega$

Figure 3. Test Circuit and Definitions for the Driver Common-Mode Output Voltage

Generator: PRR = 500 kHz, 50% Duty Cycle,  $t_r$  <6 ns,  $t_f$  <6 ns,  $Z_o$  = 50  $\Omega$

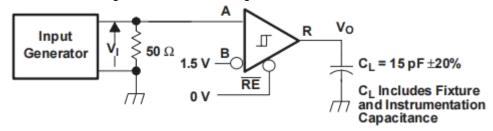

Figure 4. Driver Switching Test Circuit and Voltage Waveforms

Generator: PRR = 500 kHz, 50% Duty Cycle,  $t_r$  <6 ns,  $t_f$  <6 ns,  $Z_o$  = 50  $\Omega$

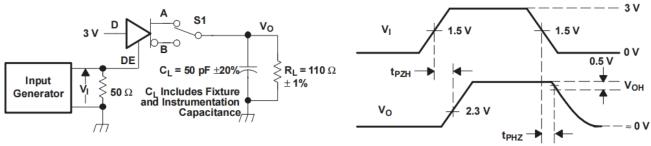

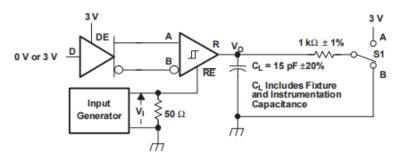

Figure 5. Driver High-Level Enable and Disable Time Test Circuit and Voltage Waveforms

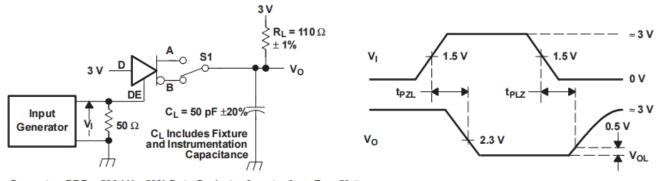

Generator: PRR = 500 kHz, 50% Duty Cycle,  $t_{\rm r}$  <6 ns,  $t_{\rm f}$  <6 ns,  $Z_{\rm o}$  = 50  $\Omega$

Figure 6. Driver Low-Level Output Enable and Disable Time Test Circuit and Voltage Waveforms

2016 JAN

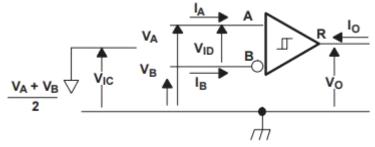

Figure 7. Receiver Voltage and Current Definitions

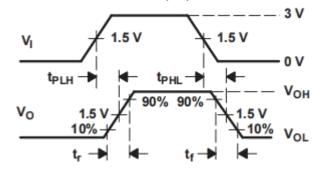

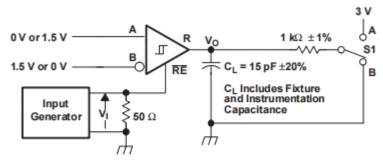

Generator: PRR = 500 kHz, 50% Duty Cycle, tr <6 ns, tf <6 ns, Zo = 50  $\Omega$

Figure 8. Receiver Switching Test Circuit and Voltage Waveforms

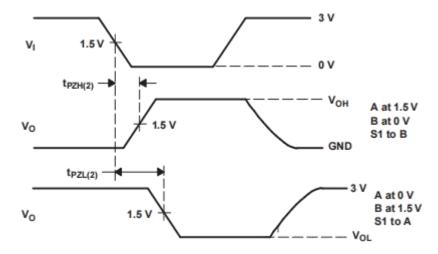

Generator: PRR = 500 kHz, 50% Duty Cycle,  $t_{\rm f}$  <6 ns,  $t_{\rm f}$  <6 ns,  $Z_{\rm o}$  = 50  $\Omega$

Figure 9. Receiver Enable and Disable Time Test Circuit and Voltage Waveforms With Drivers Enabled

8 / 17

Generator: PRR = 100 kHz, 50% Duty Cycle,  $t_r$ <6 ns,  $t_f$ <6 ns,  $Z_0$  = 50  $\Omega$

Figure 10. Receiver Enable Time From Standby (Driver Disabled)

NOTE: This test is conducted to test survivability only. Data stability at the R output is not specified.

Figure 11. Test Circuit, Transient Over Voltage Test

## PARAMETER MEASUREMENT INFORMATION (continued)

#### **FUNCTION TABLES**

Table 1. DRIVER(1)

|            |              | OUTPUTS |   |  |  |  |  |

|------------|--------------|---------|---|--|--|--|--|

| INPU<br>TD | ENABLE<br>DE | A       | В |  |  |  |  |

| Н          | Н            | Н       | L |  |  |  |  |

| L          | Н            | L       | Н |  |  |  |  |

| X          | L            | Z       | Z |  |  |  |  |

| Open       | Н            | Н       | L |  |  |  |  |

<sup>(1)</sup> H = high level; L = low level; Z = high impedance; X = irrelevant; ? = indeterminate

Table 2. RECEIVER(1)

| DIFFERENTIAL INPUTSV <sub>ID</sub> = V <sub>A</sub> - V <sub>B</sub> | EN <u>AB</u> LERE | OUTPUTR |

|----------------------------------------------------------------------|-------------------|---------|

| V <sub>ID</sub> ≤ -0.2 V                                             | L                 | L       |

| -0.2 V < V <sub>ID</sub> < -0.01 V                                   | L                 | ?       |

| -0.01 V ≤ V <sub>ID</sub>                                            | L                 | Н       |

| X                                                                    | Н                 | Z       |

| Open Circuit                                                         | L                 | Н       |

| Short circuit                                                        | L                 | Н       |

<sup>(1)</sup> H = high level; L = low level; Z = high impedance; X = irrelevant; ? = indeterminate

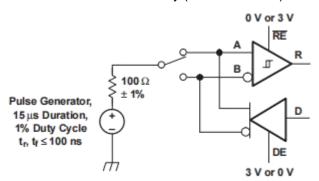

## **EQUIVALENT INPUT AND OUTPUT SCHEMATIC DIAGRAMS**

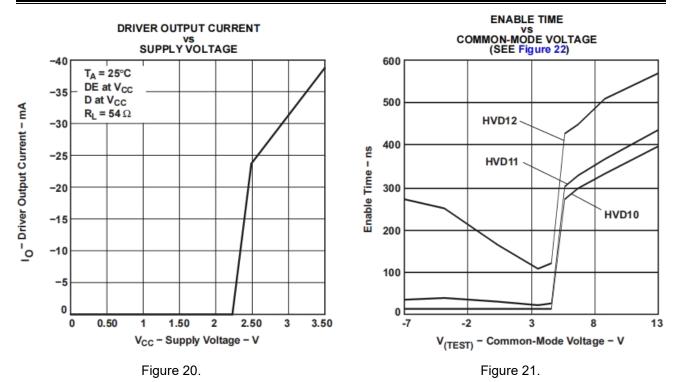

#### TYPICAL CHARACTERISTICS

Figure 12.

Figure 13.

375  $\Omega \pm 1\%$ -7 V < V<sub>(TEST)</sub> < 12 V D **60** Ω  $V_{OD}$ 0 or 3 V ±1% z  $\textbf{375}~\Omega \pm \textbf{1\%}$ Input 50  $\Omega$ Generator 50% t<sub>pZH</sub>(diff) V<sub>OD</sub> (high) 1.5 V

Figure 22. Driver Enable Time From DE to VOD

-1.5 V

V<sub>OD</sub> (low)

The time tPZL(x) is the measure from DE to VOD(x). VOD is valid when it is greater than 1.5 V.

$t_{pZL}(diff)$

0 V

#### APPLICATION INFORMATION

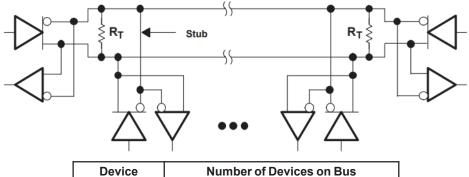

| Device | Number of Devices on Bus |

|--------|--------------------------|

| HVD10  | 64                       |

| HVD11  | 256                      |

| HVD12  | 256                      |

NOTE: The line should be terminated at both ends with its characteristic impedance (RT = ZO). Stub lengths off the main line should be kept as short as possible.

Figure 23. Typical Application Circuit

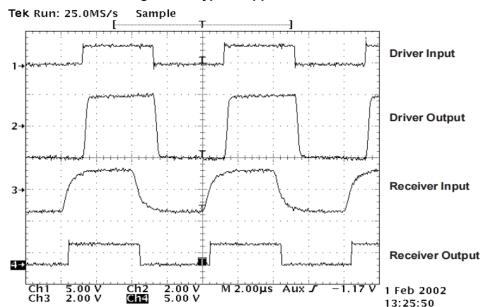

Figure 24. HVD12 Input and Output Through 2000 Feet of Cable

An example application for the HVD12 is illustrated in Figure 23. Two HVD12 transceivers are used to communicate data through a 2000 foot (600 m) length of Commscope 5524 category 5e+ twisted pair cable. The bus is terminated at each end by a  $100-\Omega$  resistor, matching the cable characteristic impedance. Figure 24 illustrates operation at a signaling rate of 250 kbps.

#### LOW-POWER STANDBY MODE

When both the driver and receiver are disabled (DE low and RE high) the device is in standby mode. If the enable inputs are in this state for less than 60 ns, the device does not enter standby mode. This guards against inadvertently entering standby mode during driver/receiver enabling. Only when the enable inputs are held in this state for 300 ns or more, the device is assured to be in standby mode. In this low-power standby mode, most internal circuitry is powered down, and the supply current is typically less than 1 nA. When either the driver or the receiver is re-enabled, the internal circuitry becomes active.

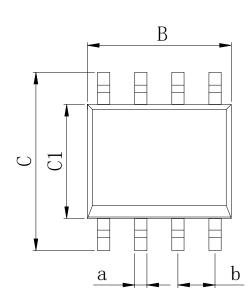

# **Physical Dimensions**

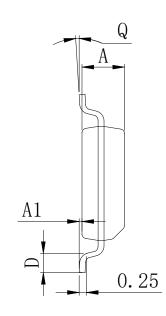

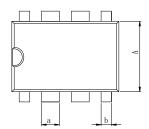

SOP8

| Dimensions In Millimeters(SOP8) |      |      |      |      |      |      |    |      |          |  |

|---------------------------------|------|------|------|------|------|------|----|------|----------|--|

| Symbol:                         | Α    | A1   | В    | С    | C1   | D    | Q  | а    | b        |  |

| Min:                            | 1.35 | 0.05 | 4.90 | 5.80 | 3.80 | 0.40 | 0° | 0.35 | 1.27 BSC |  |

| Max:                            | 1.55 | 0.20 | 5.10 | 6.20 | 4.00 | 0.80 | 8° | 0.45 | 1.27 650 |  |

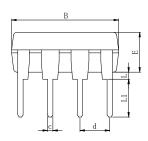

DIP8

| Dimensions In Millimeters(DIP8) |      |      |      |      |      |      |      |      |      |      |          |  |

|---------------------------------|------|------|------|------|------|------|------|------|------|------|----------|--|

| Symbol:                         | Α    | В    | D    | D1   | Е    | L    | L1   | а    | b    | С    | d        |  |

| Min:                            | 6.10 | 9.00 | 8.40 | 7.42 | 3.10 | 0.50 | 3.00 | 1.50 | 0.85 | 0.40 | 2.54 BSC |  |

| Max:                            | 6.68 | 9.50 | 9.00 | 7.82 | 3.55 | 0.70 | 3.60 | 1.55 | 0.90 | 0.50 |          |  |

#### **IMPORTANT STATEMENT:**

Huaguan Semiconductor reserves the right to change its products and services without notice. Before ordering, the customer shall obtain the latest relevant information and verify whether the information is up to date and complete. Huaguan Semiconductor does not assume any responsibility or obligation for the altered documents.

Customers are responsible for complying with safety standards and taking safety measures when using Huaguan Semiconductor products for system design and machine manufacturing. You will bear all the following responsibilities: select the appropriate Huaguan Semiconductor products for your application; Design, validate and test your application; Ensure that your application meets the appropriate standards and any other safety, security or other requirements. To avoid the occurrence of potential risks that may lead to personal injury or property loss.

Huaguan Semiconductor products have not been approved for applications in life support, military, aerospace and other fields, and Huaguan Semiconductor will not bear the consequences caused by the application of products in these fields.

The technical and reliability data (including data sheets), design resources (including reference designs), application or other design suggestions, network tools, safety information and other resources provided for the performance of semiconductor products produced by Huaguan Semiconductor are not guaranteed to be free from defects and no warranty, express or implied, is made. The use of testing and other quality control technologies is limited to the quality assurance scope of Huaguan Semiconductor. Not all parameters of each device need to be tested.

The documentation of Huaguan Semiconductor authorizes you to use these resources only for developing the application of the product described in this document. You have no right to use any other Huaguan Semiconductor intellectual property rights or any third party intellectual property rights. It is strictly forbidden to make other copies or displays of these resources. You should fully compensate Huaguan Semiconductor and its agents for any claims, damages, costs, losses and debts caused by the use of these resources. Huaguan Semiconductor accepts no liability for any loss or damage caused by infringement.