# 器件参数表 DataSheet

文档编号: SPEC51761001 版本:A

# ICW5176 【 同步降压升压控制器 】

合肥艾创微电子科技有限公司

# ICW5176 High Efficiency, Synchronous Buck-Boost Controller

## 1 Description

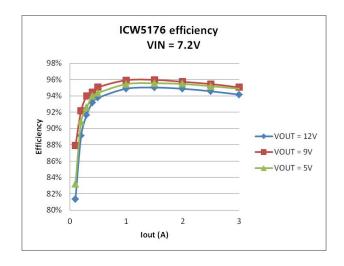

The ICW5176 is a synchronous 4-switch buck-boost controller. It is able to effectively output voltage no matter it is higher, lower or equal to the input voltage. The ICW5176 supports very wide input and output voltage range. It can support applications from 2.7V to 36V input range and 2V to 36V output range. The driver voltage is set to 10V to fully utilize external MOSFETs for highest efficiency.

The ICW5176 supports input current limit, output current limit and over temperature protections to ensure safety under different abnormal conditions. The ICW5176 adopts 32 pin QFN 4x4 package.

#### 2 Features

- High efficient buck-boost operation

- Dynamic adjustable output voltage

- Dynamic adjustable Input and Output current limit

- Wide input voltage range: 2.7 V to 36 V

- Wide output range: 2V to 36V

- Integrated 10V, 2A gate driver

- Adjustable frequency 200kHz to 600kHz

- Under voltage protection

- QFN-32 Package

## 3 Applications

- Power Bank

- USB PD

- Car Charger

- Industrial applications

#### 4 Device Information

| ORDER NUMBER | PACKAGE    | BODY SIZE          |

|--------------|------------|--------------------|

| ICW5176QDER  | 32 pin QFN | 4mm x 4mm x 0.75mm |

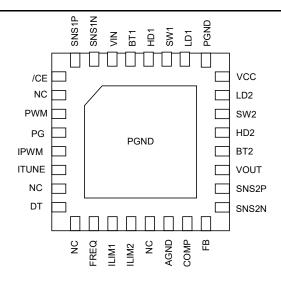

# 5 Terminal Configuration and Functions

| TERM   | TERMINAL I/O |     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|--------|--------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NUMBER | NAME         | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 1      | /CE          | I   | Chip Logic Enable, CE=Low, chip enable. Internal pull low                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 2      | NC           | I   | Floating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

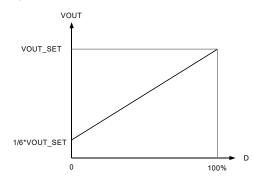

| 3      | PWM          | I   | PWM pin accepts square waveform from 20K to 100K. By adjusting duty cycle, output voltage can be adjusted according to needs. When duty=0, output voltage = 1/6 of the preset value by the feedback resistor divider at FB pin. When duty = 100%, output voltage = preset value.  VOUT = $V_{OUT\_SET} \times (\frac{1}{6} + \frac{5}{6} \times D)$                                                                                                                                                                                                                                                                                                                      |  |

| 4      | PG           | 0   | Open drain, active high when VOUT is within 90% to 110% * VOUT target.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| 5      | IPWM         | I   | IPWM pin is used together with ITUNE pin to adjust the current limit value of either ILIM1 or ILIM2. The ITUNE pin is used to select the control object between ILIM1 and ILIM2, and IPWM signal is to adjust the limit value.  IPWM pin accepts PWM waveform from 20kHz to 100kHz, and the current limit value is proportional to its duty cycle.  For example, if ITUNE pin selects ILIM1, then the input current limit is set by:  In the equation above, I <sub>LIM1_SET</sub> is the current limit value set by the resistor at ILIM1 pin, D is the duty cycle of the IPWM signal.  Similarly, if ITUNE pin selects ILIM2, then the output current limit is set by: |  |

| 6      | ITUNE        | Ю   | ITUNE pin selects the IPWM control object between ILIM1 and ILIM2  If ILIM1 current limit needs to be controlled, connect the ILIM1 resistor between ILIM1 ITUNE pin. If ILIM2 current limit is to be controlled, connect the ILIM2 resistor between IL and ITUNE pin.  Only one current limit can be selected by ITUNE pin.  If IPWM function is not needed, leave ITUNE pin and IPWM pin floating, and connect the resistor from the ILIMx pin to AGND accordingly.                                                                                                                                                                                                    |  |

| 7  | NC    | ı | Floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----|-------|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8  | DT    | I | Dead Time selection. Short to ground: 20ns; $8k\Omega$ : 40ns; $70k\Omega$ : 0ns; Open: 80ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 9  | NC    | I | Floating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10 | FREQ  | I | Frequency selection Short to ground: 200kHz; 8kΩ: 400kHz; Open: 600kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 11 | ILIM1 | I | Connect a resistor to set the current limit value of input current. $I_{LIM1\_SET} = \frac{V_{REF} \times R_{SS1}}{R_{ILIM1}}$ Vref is the internal reference voltage 1.21V; $R_{LIM1} \text{ is the resistor from ILIMT1 to ground or to ITUNE;}$ $R_{SNS1} \text{ is the current sense resistor. Recommended } 5m\Omega  0m\Omega \text{ , typical } 0m\Omega;$ $R_{SS1} \text{ are the resistors connected to SNS1P , SNS1N. The two resistors must be equal and the recommended value is 1k\Omega.} A 2.2nF capacitor to ground is needed to bypass noise. If IPWM function is applied to ILIM1, increase the capacitor value to 10nF. If current limiting function is not needed, please short ILIM1 to ground.}$                                              |

| 12 | ILIM2 | I | Connect a resistor to set the current limit value of output current. $I_{LIM2\_SET} = \frac{V_{REF}}{R_{ILIM2}} \times \frac{R_{SS2}}{R_{SNS2}}$ $V_{REF} \text{ is the internal reference voltage 1.21V};$ $R_{LIM2} \text{ is the resistor from ILIM2 to ground or to ITUNE};$ $R_{SNS2} \text{ is current sensing resistor. Recommended } 5m\Omega - 0m\Omega \text{ , typical } 0m\Omega \text{ ;}$ $R_{SS2} \text{ are the resistors connected to SNS2P , SNS2N. The two resistors must be equal and the recommended value is 1k\Omega.} A \text{ 2.2nF capacitor to ground is needed to bypass noise. If IPWM function is applied to ILIM2, increase the capacitor value to 10nF. If current limiting function is not needed, please short ILIM2 to ground.}$ |

| 13 | NC    | I | Floating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 14 | AGND  | Ю | Analog Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 15 | COMP  | 0 | Compensation for the control loop.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 16 | FB    | I | Feedback for output voltage. $VOUT = V_{REF} \times \left(1 + \frac{R_{UP}}{R_{DOWN}}\right)$ $V_{REF} \text{ equals to 1.22V. } R_{UP} \text{ and } R_{DOWN} \text{ are the value of voltage divider.}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 17 | SNS2N | I | Negative input of current sense amplifier. Connect an external current sense resistor between SNS2P and SNS2N. Current flows from SNS2P to SNS2N.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 18 | SNS2P          | I   | Positive input of current sense amplifier. Connect an external current sense resistor between SNS2P and SNS2N. Current flows from SNS2P to SNS2N.            |

|----|----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19 | VOUT           | I   | Output node of the converter.                                                                                                                                |

| 20 | BT2            | PWR | Connect a capacitor between BT2 pin and SW2 pin to bootstrap a voltage to provide the bias voltage for high side MOSFET gate driver2.                        |

| 21 | HD2            | PWR | High side MOSFET gate driver2 output                                                                                                                         |

| 22 | SW2            | PWR | Switching Node 2                                                                                                                                             |

| 23 | LD2            | PWR | Low side MOSFET gate driver2 output                                                                                                                          |

| 24 | VCC            | PWR | Output of internal regulator to provide 10V voltage for the bias voltage of internal gate drivers.<br>Connect a 1 µF ceramic capacitor from VCC to PGND pin. |

| 25 | PGND           | PWR | Power Ground                                                                                                                                                 |

| 26 | LD1            | PWR | Low side MOSFET gate driver1 output                                                                                                                          |

| 27 | SW1            | PWR | Switching Node 1                                                                                                                                             |

| 28 | HD1            | PWR | High side MOSFET gate driver1 output                                                                                                                         |

| 29 | BT1            | PWR | Connect a capacitor between BT1 pin and SW1 pin to bootstrap a voltage to provide the bias voltage for high side MOSFET gate driver1.                        |

| 30 | VIN            | I   | Input node of the converter                                                                                                                                  |

| 31 | SNS1N          | I   | Negative input of current sense amplifier. Connect an external current sense resistor between SNS1P and SNS1N. Current flows from SNS1P to SNS1N.            |

| 32 | SNS1P          | I   | Positive input of current sense amplifier. Connect an external current sense resistor between SNS1P and SNS1N. Current flows from SNS1P to SNS1N.            |

|    | Thermal<br>Pad |     | For thermal dissipation. Connect to AGND or PGND.                                                                                                            |

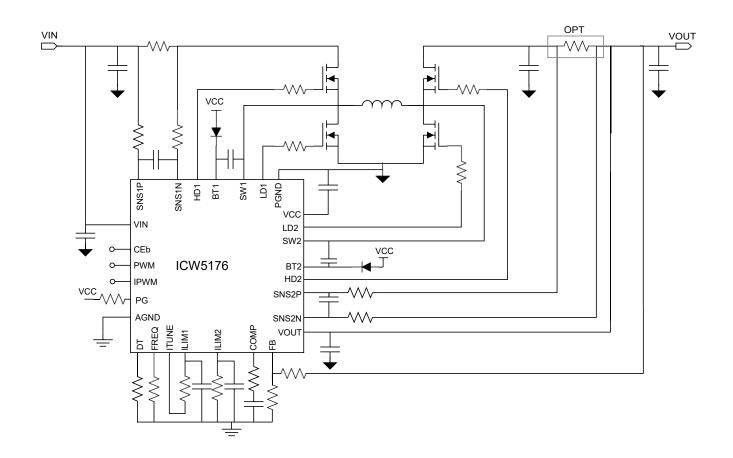

# 6 Typical Application Circuit

# 7 Specifications

## 7.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted) (1)

|                                           |                                             | MIN  | MAX | UNIT |

|-------------------------------------------|---------------------------------------------|------|-----|------|

|                                           | VIN, VOUT, SNS1P, SNS1N, SNS2P, SNS2N, /CE  | -0.3 | 42  | V    |

|                                           | SW1, SW2                                    | -1   | 42  | V    |

|                                           | VCC, PG, PWM, IPWM                          | -0.3 | 20  | V    |

| Voltage range at terminals <sup>(2)</sup> | FREQ, ILIM1, ILIM2, COMP, DT, FB, ITUNE     | -0.3 | 5.5 | V    |

|                                           | LD1, LD2                                    | -0.3 | 12  | V    |

|                                           | BT1, HD1 to SW1                             | -0.3 | 12  | V    |

|                                           | BT2, HD2 to SW2                             | -0.3 | 12  | V    |

|                                           | BT1, BT2                                    | -0.3 | 50  | V    |

| Tomporatura Banga                         | Operating Junction, T <sub>J</sub>          | -40  | 150 | °C   |

| Temperature Range                         | Storage temperature range, T <sub>stg</sub> | -65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *recommended operating conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 7.2 Thermal Information

| THERMAL RESISTANCE | THERMAL RESISTANCE(1)                  |    |      |

|--------------------|----------------------------------------|----|------|

| $\Theta_{JA}$      | Junction to ambient thermal resistance | 35 | °C/W |

| Θ <sub>JC</sub>    | Junction to case resistance            | 7  | °C/W |

<sup>(1)</sup> Measured on JESD51-7, 4-layer PCB.

#### 7.3 Handling Ratings

| PARAMETER | DEFINITION                                        |      | MAX | UNIT |

|-----------|---------------------------------------------------|------|-----|------|

| ESD (1)   | Human body model (HBM) ESD stress voltage (2)     | -2   | 2   | kV   |

| 200       | Charged device model (CDM) ESD stress voltage (3) | -750 | 750 | V    |

<sup>(1)</sup> Electrostatic discharge (ESD) to measure device sensitivity and immunity to damage caused by assembly line electrostatic discharges into the device.

# 7.4 Recommended Operating Conditions

|                  |                      | MIN | TYP | MAX | UNIT |

|------------------|----------------------|-----|-----|-----|------|

| V <sub>IN</sub>  | Input voltage range  | 2.7 |     | 36  | V    |

| V <sub>OUT</sub> | Output voltage range | 2   |     | 36  | V    |

| C <sub>IN</sub>  | Input Capacitance    | 30  |     |     | μF   |

| Соит             | Output capacitance   | 30  |     |     | μF   |

<sup>(2)</sup> All voltage values are with respect to network ground terminal.

<sup>(2)</sup> Level listed above is the passing level per ANSI, ESDA, and JEDEC JS-001. JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(3)</sup> Level listed above is the passing level per EIA-JEDEC JESD22-C101. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

| L                                    | Inductance                     |     | 10  | μН  |

|--------------------------------------|--------------------------------|-----|-----|-----|

| R <sub>SNS1/2</sub>                  | Current Sensing Resistor       |     | 20  | mΩ  |

| f <sub>SW</sub>                      | Operating frequency range      | 200 | 600 | kHz |

| f <sub>PWM</sub> , f <sub>IPWM</sub> | PWM signal frequency range     |     | 100 | kHz |

| D <sub>PWM</sub> , D <sub>IPWM</sub> | PWM signal duty cycle range    |     | 100 | %   |

| TJ                                   | Operating junction temperature | -40 | 125 | °C  |

# 7.5 Electrical Characteristic

$T_J$ = 25°C and  $V_{IN}$  = 12V,  $V_{OUT}$  = 5V,  $R_{SS1}$  =  $R_{SS2}$  = 1k $\Omega$  unless otherwise noted.

| PARAMETI                | ER                                                            | TEST CONDITIONS                                                                                 | MIN   | TYP   | MAX   | UNIT       |

|-------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------|-------|-------|------------|

| SUPPLY V                | OLTAGE (VIN, VOUT)                                            | W with                                                                                          | iii   |       |       | 753<br>557 |

| V <sub>IN</sub>         | Operating voltage                                             |                                                                                                 | 2.7   |       | 36    | V          |

| Vour                    | Operating voltage                                             |                                                                                                 | 2     |       | 36    | V          |

|                         | Input under-voltage lockout                                   | Rising edge                                                                                     |       | 2.6   | 2.7   | V          |

| V <sub>UVLO</sub>       | threshold                                                     | Hysteresis                                                                                      |       | 160   |       | mV         |

| la                      | Standby current into VIN or VOUT<br>pin (whichever is higher) | /CE = low, controller non-switching                                                             |       | 0.7   | 2     | mA         |

| Local Control           | Shutdown current into VIN or VOUT pin (which is higher)       | /CE = high                                                                                      |       | 6     | 10    | μА         |

| Iso                     | Shutdown current into VIN or VOUT pin (which is lower)        | /CE = high                                                                                      |       |       | 2     | μА         |

| VCC AND                 | DIRVER                                                        | ~                                                                                               |       |       |       |            |

| V <sub>cc</sub>         | VCC clamp voltage                                             |                                                                                                 | 9.4   | 10    | 10.6  | ٧          |

| Ivoc_LM                 | VCC current limit                                             | V <sub>cc</sub> = 2V ~10V                                                                       | 50    | 75    | 100   | mA         |

| R <sub>HVx_pu</sub>     | High side driver pull up resistor                             |                                                                                                 |       | 1.5   |       | Ω          |

| R <sub>HVx_pd</sub>     | High side driver pull down resistor                           |                                                                                                 |       | 1     |       | Ω          |

| R <sub>LVx_pu</sub>     | Low side driver pull up resistor                              |                                                                                                 |       | 1.5   |       | Ω          |

| R <sub>LVx_pd</sub>     | Low side driver pull down resistor                            |                                                                                                 |       | ্ৰ    |       | Ω          |

| ERROR AN                | PLIFIER                                                       |                                                                                                 |       |       |       |            |

| V <sub>FB_REF</sub>     | FB reference voltage                                          |                                                                                                 | 1.214 | 1.22  | 1.226 | V          |

| VILIMIX_REF             | ILIMx reference voltage                                       |                                                                                                 | 1.196 | 1.212 | 1.228 | ٧          |

| Gm <sub>EA</sub>        | Error amplifier gm                                            |                                                                                                 |       | 0.16  |       | mS         |

| Rout                    | Error amplifier output resistance (1)                         |                                                                                                 |       | 20    |       | ΜΩ         |

| IBIAS(FBx)              | FBx pin input bias current                                    | FBx in regulation                                                                               |       |       | 100   | nA         |

| CURRENT                 | LIMIT                                                         |                                                                                                 | ~     |       |       |            |

| I <sub>LIMb</sub>       | ILIMx current limit accuracy                                  | I <sub>IN_LIM</sub> R <sub>SNS1</sub> ≥ 30 mV<br>I <sub>OUT_LIM</sub> R <sub>SNS2</sub> ≥ 30 mV | -10%  |       | 10%   |            |

| SWITCHIN                | G FREQUENCY                                                   | \$0.                                                                                            | ¢1    |       |       | (#)<br>(#) |

|                         |                                                               | $R_{FREQ} = 0\Omega$                                                                            | 180   | 210   | 240   | kHz        |

| f <sub>sw</sub>         | Switching frequency                                           | R <sub>FREQ</sub> = 68kΩ (±10%)                                                                 | 360   | 410   | 460   | kHz        |

|                         |                                                               | $R_{FREQ} = 270k\Omega (\pm 10\%)$                                                              | 540   | 600   | 660   | kHz        |

| INDICATIO               | N                                                             |                                                                                                 |       |       |       |            |

| t <sub>PG_deglich</sub> | PG signal deglitch time                                       | f <sub>sw</sub> = 200kHz                                                                        | 27    | 38.5  | 50    | ms         |

| Isink_PG                | PG sink current                                               | V <sub>PG</sub> = 0.4 V                                                                         | 3.6   | 4.1   | 4.6   | mA         |

|                         |                                                               | High limit falling edge (PG from low to high)                                                   |       | 110%  |       |            |

| Va.a.s-                 | VOUT power good threshold                                     | High limit hysteresis (PG from high to low)                                                     |       | 5%    |       | 32         |

| Vout_PG                 | 7001 power good trieshold                                     | Low limit rising edge (PG from low to high)                                                     |       | 90%   |       | 837        |

|                         |                                                               | Low limit hysteresis (PG from high to low)                                                      | 8     | 5%    |       | 3          |

|                         |                                                               |                                                                                                 |       |       |       |            |

| LOGIC C          | ONTROL                               | W.                       | 80  |     | XX |  |

|------------------|--------------------------------------|--------------------------|-----|-----|----|--|

|                  | /CE internal pull down resistor      |                          | 1   |     | MΩ |  |

| R <sub>PD</sub>  | PWM pin internal pull down resistor  |                          | 0.5 |     |    |  |

|                  | IPWM pin internal pull down resistor |                          | 1   |     | МΩ |  |

| V <sub>R</sub> L | /CE, PWM, IPWM input low voltage     |                          |     | 0.4 | ٧  |  |

| V <sub>BH</sub>  | /CE, PWM, IPWM input high voltage    |                          | 1.2 |     | ٧  |  |

| Soft Star        | rt                                   |                          |     |     |    |  |

| tss              | Internal soft-start time             | From /CE low to 90% VOUT | 8   | 15  | ms |  |

| THERMA           | AL SHUTDOWN                          |                          | •   |     | _  |  |

|                  | Thermal shutdown temperature (1)     |                          | 165 |     | °C |  |

| T <sub>SD</sub>  | Thermal shutdown hysteresis (1)      |                          | 15  |     | °C |  |

<sup>(1)</sup> Guarantee by design

# 8 Detailed Description

The ICW5176 is a synchronous four-switch buck-boost controller with a wide input/output voltage range. The ICW5176 regulates the output at, above, below the input voltage.

The ICW5176 features automatic buck, boost mode smooth transition and maximum input and output current limit capability using additional resistors. In addition, the ICW5176 features output voltage dynamic change, input/output current limit dynamic change, and power MOSFETs dead time control.

#### 8.1 Feature Description

#### 8.1.1 Chip Enable (/CE)

The ICW5176 turns on/off by /CE signal. When /CE input is " ", the C870 is turned on; when /C input is "H", the ICW5176 is turned off.

#### 8.1.2 VOUT voltage setting (FB)

The VOUT voltage is set by external resistor divider at FB pin and is calculated as:

$$VOUT = V_{FB\_REF} \times \left(1 + \frac{R_{UP}}{R_{DOWN}}\right)$$

Where:

V<sub>FB REF</sub> = Internal reference voltage 1.22V

$R_{UP}$  and  $R_{DWON}$  = Resistor divider at FB connected to VOUT and AGND.

#### 8.1.3 Output voltage POWER GOOD indicator (PG)

The PG signal indicates VOUT voltage status.

If VOUT voltage remains in between  $90\% \sim 110\%$  of programmed voltage, PG pin becomes high impedance and due to the output pull-up resistor, PG out becomes "H" to indicate the output voltage is good.

If VOUT is out of normal voltage range, PG out becomes "". If power good indication is not required, leave PG pin floating.

#### 8.1.4 Real-time output voltage control (PWM)

The ICW5176 supports VOUT voltage change by PWM signal at PWM pin.

The PWM pin accepts a PWM signal in the range of 20kHz to 100kHz, and its duty cycle can adjust the VOUT voltage. VOUT output voltage is calculated as:

$$VOUT = V_{OUT\_SET} \times (\frac{1}{6} + \frac{5}{6} \times D)$$

Where;

$V_{\text{OUT\_SET}}$  = VOUT voltage which is set by FB resistor divider;

D = Duty cycle of PWM signal.

The relationship between VOUT voltage and D is showed in Figure 1

Figure 1 VOUT voltage vs PWM duty cycle.

If PWM input signal is logic high, it means 100% of duty cycle, then the output voltage become the set value by FB1 resistor divider.

If PWM input signal is logic low, it means 0% of duty cycle, then the output voltage become the 1/6 of the set value.

If PWM pin is left floating, due to the IC internal pull down circuit at PWM pin, VOUT voltage becomes the 1/6 of programmed voltage.

If real-time output voltage control is not required, connect PWM pin to VCC pin.

#### 8.1.5 Input/output current setting (ILIMx)

The ICW5176 can adjust the current limit of both input side and output side by resistors at ILIM1 and ILIM2 pins.

| Control Pins | Description                                         |

|--------------|-----------------------------------------------------|

| ILM1         | Set the input current limit (I <sub>IN_LIM</sub> )  |

| ILM2         | Set the output current limit(I <sub>OUT_LIM</sub> ) |

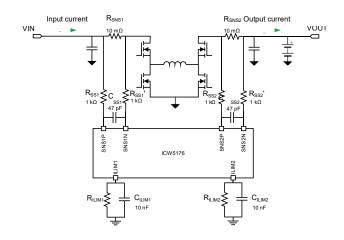

The ICW5176 senses the input and output current by monitoring  $R_{\text{SNS1}}$  and  $R_{\text{SNS2}}$  respectively as below figure shows.

Figure 3 Input/output current monitoring circuit

$R_{\text{SNSX}}$  is the current sense resistor (x means 1 or 2) at input /output. The ICW5176 monitors the voltage across the sense resistors  $R_{\text{SNSX}}$  through  $R_{\text{SSX}}$  and  $R_{\text{X'}}$  and calculates the input and output current.  $C_{\text{SSX}}$  is the filter capacitor and typically 47pF is sufficient.

The ILIMx pin is used to set the current limit. Connect the  $R_{\text{ILIMX}}$  resistor between  $\text{ILIM}_X$  pin and GND (or ITUNE pin if IPWM function is used).

The current limit is calculated as:

$$I_{IN\_LIM} = \frac{V_{LIM\_REF}}{R_{ILIM1}} \times \frac{R_{SS1}}{R_{SNS1}}$$

$$I_{OUT\_LIM} = \frac{V_{LIM\_REF}}{R_{ILIM2}} \times \frac{R_{SS2}}{R_{SNS2}}$$

Where:

V<sub>LIM REF</sub> = Internal reference voltage 1.21V;

R<sub>ILIMx</sub> = Resistors at ILIMx pin;

R<sub>SNSx</sub> = Current sense resistors;

R<sub>SSx</sub> = Resistors between current sense resistor and the ICW5176 pins (SNSxP, SNSxN).

$R_{\text{SNS1}}$  should be placed between MOSFET and input capacitor.  $R_{\text{SNS2}}$  can be placed either between the MOSFET and output capacitor or behind the output capacitor.

$R_{SS1}$  and R , should have the same value;  $R_{SS2}$  and R , also the same. Typically  $1k\Omega$  resistor is used.

If  $R_{SNSX}$  is changed,  $R_{SSX}/R_{SSX}$  values need to be adjusted accordingly with below calculation:

$$\frac{R_{SNSx}}{R_{SSx}} = \frac{10 \text{ m}\Omega}{1 \text{ k}\Omega}$$

For example, If  $R_{SNSX}$  is  $20m\Omega$ , then  $R_{SSX}/R_{SSX'}$  should be  $2k\Omega$ ; if  $R_{SNSX}$  is  $5m\Omega$ , then  $R_{SSX}/R_{SSX'}$  should be  $500\Omega$ .

If both VIN and VOUT current limits are programmed, the ICW5176 controls the current which reaches its current limit first.

If the input/output current limit is not required, connect ILIM1/ILIM2 pin to GND.

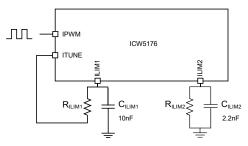

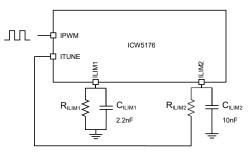

#### 8.1.6 Real-Time current control (IPWM)

The ICW5176 is able to control the input/output current dynamically by applying a PWM signal to IPWM pin.

The IPWM signal should be in the range of 20kHz ~ 100kHz, and the input/output current is proportional to its duty cycle as:

Where:

$I_{LIMX\_SET} = I_{LIMX}$  Input or output current limit value (x=1: input, x=2: output);

D = IPWM duty cycle;

I<sub>LIMx</sub> = Target current limit of input/output current.

ITUNE pin selects the target which is controlled by IPWM. If input current should be controlled, the resistor at ILIM1 should be connected between ILIM1 and ITUNE pins; If output current should be controlled, the resistor at ILIM2 should be connected between ILIM2 and ITUNE pins.

Only one target can be selected by ITUNE pin.

Refer to Figure 2. IPWM real-time input/output current control.

a. IPWM controls input current, ILIM1 = ILIM1\_set x D, as above

b. IPWM controls output current, ILIM2 = ILIM2\_set x D, as above

Figure 2. IPWM real-time input/output current control.

When the IPWM signal is logic high, which means the duty cycle is 100%, the current limit is then the ILIMx set value.

For the ILIMx pin which is controlled by IPWM signal, its filter capacitor should still be connected to ground. If the IPWM frequency is low, higher capacitance should be applied. For example, 22nF capacitor is suggested for 20kHz frequency.

If real-time current control is not required, connect ILIMx resistor to GND and float IPWM and ITUNE pins.

Do not leave IPWM pin float if the ITUNE pin is connected to one ILIMx resistor; otherwise, the ICW5176 cannot operate normally.

It is not allowed to set any of the current limits to 0A. Keep the minimum current limit above 0.3A.

#### 8.1.7 Dead time setting (DT)

The one of four dead times is selectable by resistor value at DT pin:

| DT resistor  | Dead time |

|--------------|-----------|

| 0Ω           | 20ns      |

| 68kΩ (±10%)  | 40ns      |

| 270kΩ (±10%) | 60ns      |

| Open         | 80ns      |

The accuracy of the resistor at DT is allowed ±10%. DT does not support the real-time change and new resistor value change will be applied in next turn on.

When driving large power MOSFET with high C<sub>ISS</sub> value, or adding driver resistors at LDx or HDx to adjust the MOSFET turning on/off time, it is suggested to check and change the dead time to prevent MOSFET shoot-through.

#### 8.1.8 Switching frequency setting (FREQ)

The one of three switching frequency is selectable by resistor value at FREQ pin:

| FREQ resistor | Switching frequency f <sub>sw</sub> |

|---------------|-------------------------------------|

| 0Ω            | 200kHz                              |

| 68kΩ (±10%)   | 400kHz                              |

| Open          | 600kHz                              |

The accuracy of the resistor at FREQ is allowed  $\pm 10\%$ . The real-time switching frequency change is not valid and new resistor value change will be applied in next turn on.

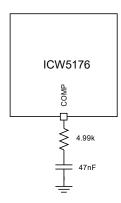

#### 8.1.9 Feedback compensation (COMP)

The feedback loop can be compensated by adjusting the external components to the COMP pin. Typically, the values in Figure 4 are used. If faster loop response is required, user can increase the resistor to like 10kOhm or 20kOhm. After changing the compensation, check and make sure the loop is stable under the application operation conditions.

Figure 4 Feedback loop compensation setting

#### 8.1.10 VCC driver voltage

The ICW5176 generates driver voltage VCC internally. The VCC is selected higher voltage between VIN and VOUT, and clamped to 10V if it is higher than 10V.

The driving signal LDx to drive low side MOSFET (Q2 and Q3) is directly supplied from VCC; the driving signal HDx to drive high side MOSFET (Q1 and Q4) is supplied from the diode in between VCC to BTx pin, which is generated by bootstrap circuit with bootstrap capacitor between BTx and SWx.

## 9 Application Information

## 9.1 Input and output capacitor selection

The switching frequency of the ICW5176 is in the range of 200kHz  $\sim 600 kHz$ . Since MLCC ceramic capacitor has good high frequency filtering with low ESR, above  $60 \mu F$  X5R or X7R capacitors with higher voltage rating then operating voltage with margin is recommended. For example, if the highest operating Vin or Vout voltage is 12V, select at least 16V capacitor and to secure enough margin, 25V voltage rating capacitor is recommended.

The high capacitance electrolytic capacitor and tantalum capacitor can be used for stable input and output but capacitor voltage rating should be higher than the highest operating voltage. When the tantalum capacitor is used, at least  $1\mu F$  ceramic capacitor is placed in parallel. If the electrolytic capacitor is used, much more ceramic capacitors are required. For example, if a  $47\mu F$  electrolytic capacitor is used, the ceramic capacitors' capacitance is allowed to reduce to  $30\mu F \sim 40\mu F$ . Even higher capacitance electrolytic capacitor is used, at least  $20\mu F$  ceramic capacitor is required.

#### 9.2 Inductor selection

For the ICW5176 system stability, the inductance of  $2.2\mu H \sim 10~\mu H$  inductor is required. High inductance ( $4.7\mu H \sim 10\mu H$ ) is used in the system where the input voltage and output voltage difference is big, such as 5V Vin and 20V Vout or the switching frequency is low; Low inductance ( $2.2\mu H$ ) is used in the system which the input voltage and output voltage difference is small but high current is required. Typically,  $3.3\mu H$  inductor is recommended. The inductance can be adjusted for high efficiency and optimization in application.

The inductor DC resistance value (DCR) affects the conduction loss of switching regulator, so around  $10m\Omega$  DCR is recommended for the first selection. If the power is relatively small, high DCR inductor can be selected. But if switch current is high, just like around 10A, then select the lowest DCR inductor as much as possible because  $10m\Omega$  DCR also causes 1W power loss.

The inductor saturation current  $I_{SAT}$  should be higher than input / output current with sufficient margin.

#### 9.3 Current sense resistor

The RSNS1 and RSNS2 are current sense resistors and  $5m\Omega \sim 20m\Omega$  resistor value is recommended.

Higher resistor value leads to higher current limit accuracy but using higher resistor value in high current application causes higher conduction loss. Typically,  $10m\Omega$  is recommended. Resistor value can be adjusted depending on current limit and target power efficiency. If  $R_{\text{SNSx}}$  valued is adjusted, related  $R_{\text{SSx}}$  value should be adjusted simultaneously.

Please refer to 8.1.5 Input/output current setting (ILIMx) for proper  $R_{\text{SNSx}}$  and  $R_{\text{SSx}}$  values. The resistor power rating and temperature coefficient should also be considered. The power dissipation is roughly calculated as  $P\!=\!1^2R$ , and I is the highest current flowing through the resistor. The resistor power rating should be higher than roughly calculated power dissipation. The resistor value can be varied if the temperature increased and the variation is decided by temperature coefficient along with temperature change. If high accuracy of current limit is required, select lower temperature coefficient resistor as much as possible.

#### 9.4 MOSFET selection

The ICW5176 is a synchronous 4-switch buck-boost controller and it requires 4 NMOS for power switching circuit.

The  $V_{DS}$  of MOSFET should be higher than the highest operating voltage with enough margin (recommend more than 10V higher). For example, if the highest operating voltage is 20V, at least 30V rated  $V_{DS}$  MOSFET should be selected; If the highest operating voltage is 24V, 40V  $V_{DS}$  voltage rating should be selected.

In the application, if the input and output voltage are higher than 10V, driver circuit voltage can reach 10V, and  $V_{\rm GS}$  voltage rating of MOSFET should be selected higher than

Considering PCB parasitic parameters during operation, driver voltage can be higher than VCC due to transient overshoot, and  $\pm 20 \text{V}$   $\text{V}_{\text{GS}}$  is recommended to secure sufficient margin.

The MOSFET current  $I_{\text{D}}$  should be higher than the highest input and output current with enough margin.

To ensure the sufficient current capability in relatively high temperature circumstance, the current rate at  $T_A=70^{\circ}\text{C}$  or  $T_C$

=  $100^{\circ}$ C should be considered. In addition, the power dissipation value  $P_D$  should also be considered and higher  $P_D$  is better in applications. Make sure that MOSFET power consumption must not exceed  $P_D$  value.

The MOSFET  $R_{DS(ON)}$  and input capacitor  $C_{ISS}$  impact power efficiency directly. Typically, lower  $R_{DS(ON)}$  MOSFET has higher  $C_{ISS}$ . The  $R_{DS(ON)}$  is related to conduction loss. Higher  $R_{DS(ON)}$  results in higher conduction loss, thus lower efficiency and higher thermal dissipation; the  $C_{ISS}$  is related to MOSFET switch on/off time, and longer on/off time results in higher switching loss and lower efficiency. The proper MOSEFT should be selected based on tradeoff between the  $R_{DS(ON)}$  and  $C_{ISS}$ .

Normally, if the output power is around 20W ~ 30W, the MOSFET with around  $10m\Omega$  of  $R_{DS/ON)}$  and lower than

1000pF of  $C_{\rm ISS}$  is recommended. If the output power is increased, the MOSFET with lower  $R_{\rm DS(ON)}$  and under 2000pF  $C_{\rm ISS}$  is recommended. The highest  $C_{\rm ISS}$  is suggested not to exceed 3000pF.

If high  $C_{\rm ISS}$  MOSFET is selected, the switching on and off time become longer, then the dead time should be adjusted with DT pin to avoid simultaneous turn on for both high side and low side MOSFETs.

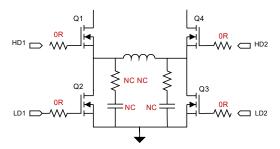

#### 9.5 Driver resistor and SWx snubber circuit

For a convenient adjustment of MOSFET switching time and transient overshoot at EMI debugging, recommend to add 0603 series resistor between driver pins (LD1, LD2, HD1, HD2) and MOSFET Gate pins, and add RC snubber (0603) circuit at SW1 and SW2 (refer to Figure 5 Driver resistor and SWx snubber circuit)

The driver resistor should be placed near to MOSFET Gate pin. At first, add  $0\Omega$  and adjust the resistor value appropriately within  $10\Omega$ . After increasing the driver resistor value, the on time of high side and low side MOSFET should

be monitored. If the dead time is insufficient, adjust dead time accordingly.

Figure 5 Driver resistor and SWx snubber circuit

The RC snubber circuit is required when the overshoot at SWx needs to suppressed. Leave RC snubber circuit as NC at the first time

# **Packaging Information**

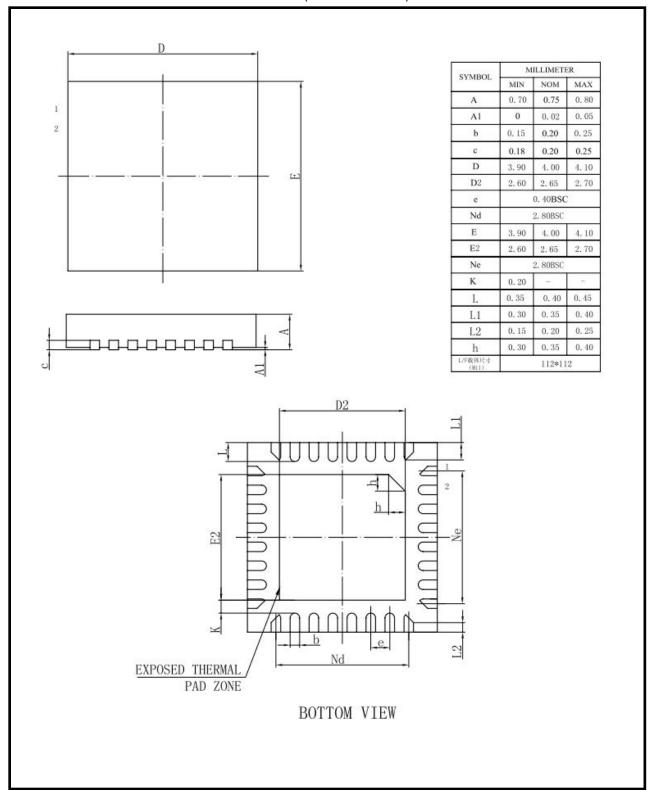

QFN32L(0404x0.75-0.40)