# 3-to-8 line decoder/demultiplexer

## **FEATURES**

- Demultiplexing capability

- Multiple input enable for easy expansion

- Ideal for memory chip select decoding

- Active HIGH mutually exclusive outputs

- Output capability: standard

- ICC category: MSI

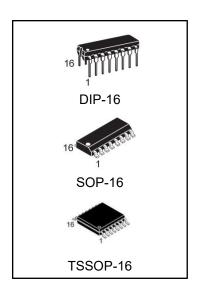

## **ORDERING INFORMATION**

| DEVICE       | Package Type | MARKING | Packing | Packing Qty  |

|--------------|--------------|---------|---------|--------------|

| 74HC238N     | DIP-16       | 74HC238 | TUBE    | 1000pcs/box  |

| 74HC238M/TR  | SOP-16       | 74HC238 | REEL    | 2500pcs/reel |

| 74HC238MT/TR | TSSOP-16     | HC238   | REEL    | 2500pcs/reel |

### **GENERAL DESCRIPTION**

The 74HC238 are high-speed Si-gate CMOS devices and are pin compatible with low power Schottky TTL (LSTTL). They are specified in compliance with JEDEC standard no. 7A.

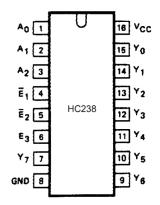

The 74HC238 decoders accept three binary weighted address inputs (A0, A1, A2) and when enabled, provide 8 mutually exclusive active HIGH outputs (Y0 to Y7).

The 74HC238 features three enable inputs: two active LOW ( $\bar{\mathbb{E}}1$  and  $\bar{\mathbb{E}}2$ ) and one active HIGH ( $\bar{\mathbb{E}}3$ ). Every output will be LOW unless  $\bar{\mathbb{E}}1$  and  $\bar{\mathbb{E}}2$  are LOW and  $\bar{\mathbb{E}}3$  is HIGH.

This multiple enable function allows easy parallel expansion of the HC238 to a 1-of-32 (5 lines to 32 lines) decoder with just four HC238 ICs and one inverter.

The 74HC238 can be used as an eight output demultiplexer by using one of the active LOW enable inputs as the data input and the remaining enable inputs as strobes. Unused enable inputs must be permanently tied to their appropriate active HIGH or LOW state.

The 74HC238 is identical to the 74HC138 but has non-inverting outputs.

## PIN DESCRIPTION

| PIN NO.                      | SYMBOL                           | NAME AND FUNCTION          |  |  |  |

|------------------------------|----------------------------------|----------------------------|--|--|--|

| 1, 2, 3                      | A <sub>0</sub> to A <sub>2</sub> | address inputs             |  |  |  |

| 4, 5                         | Ē₁, Ē₂                           | enable inputs (active LOW) |  |  |  |

| 6                            | E <sub>3</sub>                   | enable input (active HIGH) |  |  |  |

| 8                            | GND                              | ground (0 V)               |  |  |  |

| 15, 14, 13, 12, 11, 10, 9, 7 | Y <sub>0</sub> to Y <sub>7</sub> | outputs (active HIGH)      |  |  |  |

| 16                           | VCC                              | positive supply voltage    |  |  |  |

Fig.1 Pin configuration.

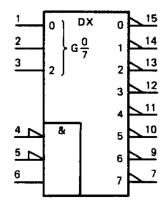

Fig.2 Logic symbol.

Fig.3 IEC logic symbol.

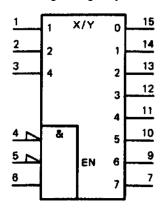

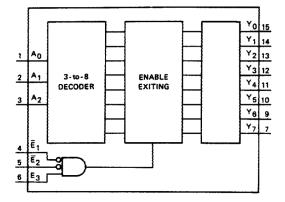

Fig.4 Functional diagram.

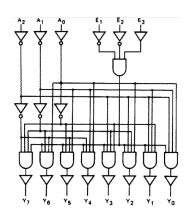

Fig.5 Logic diagram.

## **FUNCTION TABLE**

| INPUTS      |             |                |                  |                       |                       |                |                       | OUTF             | PUTS                  |                |                       |                       |                       |

|-------------|-------------|----------------|------------------|-----------------------|-----------------------|----------------|-----------------------|------------------|-----------------------|----------------|-----------------------|-----------------------|-----------------------|

| Ē₁          | Ē₂          | E <sub>3</sub> | A <sub>0</sub>   | <b>A</b> <sub>1</sub> | <b>A</b> <sub>2</sub> | Y <sub>0</sub> | <b>Y</b> <sub>1</sub> | Y <sub>2</sub>   | <b>Y</b> <sub>3</sub> | Y <sub>4</sub> | <b>Y</b> <sub>5</sub> | <b>Y</b> <sub>6</sub> | <b>Y</b> <sub>7</sub> |

| H<br>X<br>X | X<br>H<br>X | X<br>X<br>L    | X<br>X<br>X      | X<br>X<br>X           | X<br>X<br>X           | L<br>L<br>L    | L<br>L<br>L           | L<br>L<br>L      | L<br>L<br>L           | L<br>L<br>L    | L<br>L<br>L           | L<br>L<br>L           | L<br>L<br>L           |

| L<br>L<br>L | L<br>L<br>L | H<br>H<br>H    | L<br>H<br>L<br>H | L<br>L<br>H           | L<br>L<br>L           | H<br>L<br>L    | L<br>H<br>L           | L<br>L<br>H<br>L | L<br>L<br>H           | L<br>L<br>L    | L<br>L<br>L           | L<br>L<br>L           | L<br>L<br>L           |

| L<br>L<br>L | L<br>L<br>L | H<br>H<br>H    | L<br>H<br>L      | L<br>L<br>H           | H<br>H<br>H           | L<br>L<br>L    | L<br>L<br>L           | L<br>L<br>L      | L<br>L<br>L           | H<br>L<br>L    | L<br>H<br>L           | L<br>L<br>H<br>L      | L<br>L<br>L           |

#### Note

- H = HIGH voltage level

- L = LOWvoltage level

- X = don't care

### **QUICK REFERENCE DATA**

GND = 0 V;  $T_{amb} = 25$ °C;  $t_r = t_f = 6$  ns

| SYMBOL                              | PARAMETER                                 | CONDITIONS                                  | TYPICAL | UNIT |

|-------------------------------------|-------------------------------------------|---------------------------------------------|---------|------|

|                                     | propagation delay                         |                                             |         |      |

| t <sub>PHL</sub> / t <sub>PLH</sub> | A <sub>n</sub> to Y <sub>n</sub>          | C = 15 pF: \/ = 5 \/                        | 14      | ns   |

| PHL/ PLH                            | E <sub>3</sub> to Y <sub>n</sub>          | $C_L = 15 \text{ pF}; V_{CC} = 5 \text{ V}$ | 16      | ns   |

|                                     | $\overline{E}_n$ to $Y_n$                 |                                             | 17      | ns   |

| Сі                                  | input capacitance                         |                                             | 3.5     | рF   |

| CPD                                 | power dissipation capacitance per package | notes 1and 2                                | 72      | pF   |

#### **Notes**

CPD is used to determine the dynamic power dissipation (PD in  $\mu W$ ):

PD = CPD $\times$ VCC<sup>2</sup> $\times$  fi +  $\sum$ (CL $\times$  VCC<sup>2</sup> $\times$  fo) where:

fi = input frequency in MHz

fo = output frequency in MHz

$\Sigma$ (CL  $\times$  VCC  $\times$  fo) = sum of outputs CL = output load capacitance in pF

Vcc = supply voltage in V

For HC238 the condition is V I = GND to VCC

## **AC CHARACTERISTICS FOR**

GND = 0 V; tr = tf = 6 ns; CL = 50 pF

|            |                                                  | $T_{amb}({}^{\circ}\!\!C)$ |      |            |       |             |      |      |        | TEST CONDITIONS |              |

|------------|--------------------------------------------------|----------------------------|------|------------|-------|-------------|------|------|--------|-----------------|--------------|

| 0)/11001   |                                                  |                            |      | 7          | 74HC2 | 38          |      |      |        |                 |              |

| SYMBOL     | PARAMETER                                        | +25                        |      | -40 to +85 |       | -40 to +125 |      | UNIT | VCC(V) | WAVEFORMS       |              |

|            |                                                  | min.                       | typ. | max.       | min.  | max.        | min. | max. |        |                 |              |

|            |                                                  |                            | 47   | 150        |       | 190         |      | 225  |        | 2.0             |              |

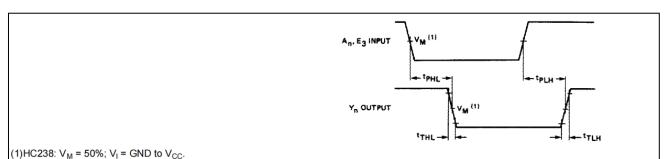

| tPHL/ tPLH | propagation delayA <sub>n</sub> toY <sub>n</sub> |                            | 17   | 30         |       | 38          |      | 45   | ns     | 4.5             | Fig.6        |

|            |                                                  |                            | 14   | 26         |       | 33          |      | 38   |        | 6.0             |              |

|            |                                                  |                            | 52   | 160        |       | 200         |      | 240  |        | 2.0             |              |

| tPHL/ tPLH | propagation delayE <sub>3</sub> toY <sub>n</sub> |                            | 19   | 32         |       | 40          |      | 48   | ns     | 4.5             | Fig.6        |

|            |                                                  |                            | 15   | 27         |       | 34          |      | 41   |        | 6.0             |              |

|            |                                                  |                            | 50   | 155        |       | 195         |      | 235  |        | 2.0             |              |

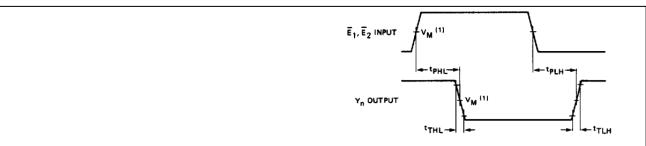

| tPHL/ tPLH | propagation delayEn toYn                         |                            | 18   | 31         |       | 39          |      | 47   | ns     | 4.5             | Fig.7        |

|            |                                                  |                            | 14   | 26         |       | 33          |      | 40   |        | 6.0             |              |

|            |                                                  |                            | 19   | 75         |       | 95          |      | 110  |        | 2.0             |              |

| tTHL/ tTLH | output transition time                           |                            | 7    | 15         |       | 19          |      | 22   | ns     | 4.5             | Figs 6 and 7 |

|            |                                                  |                            | 6    | 13         |       | 16          |      | 19   |        | 6.0             |              |

## **AC WAVEFORMS**

Fig.6 Waveforms showing the address input (A<sub>n</sub>) and enable input (E<sub>3</sub>) to output (Y<sub>n</sub>) propagation delays and the output transition times.

(1)HC238:  $V_M$  = 50%;  $V_I$  = GND to  $V_{CC}$ .

Fig.7 Waveforms showing the enable input  $(\overline{E}_n)$  to output  $(Y_n)$  propagation delays and the output transition times.

# **Physical Dimensions**

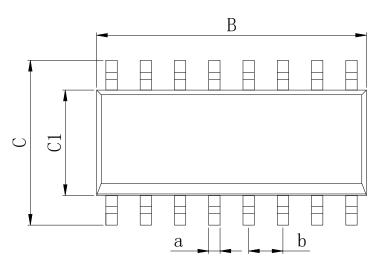

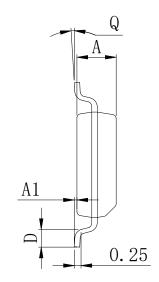

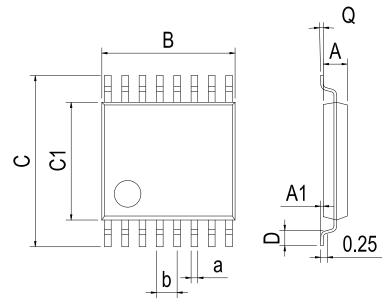

## SOP16

| Dimensions In Millimeters(SOP16) |      |      |      |      |      |      |    |      |          |  |  |  |

|----------------------------------|------|------|------|------|------|------|----|------|----------|--|--|--|

| Symbol:                          | Α    | A1   | В    | С    | C1   | D    | Q  | а    | b        |  |  |  |

| Min:                             | 1.35 | 0.05 | 9.80 | 5.80 | 3.80 | 0.40 | 0° | 0.35 | 1.27 BSC |  |  |  |

| Max:                             | 1.55 | 0.20 | 10.0 | 6.20 | 4.00 | 0.80 | 8° | 0.45 | 1.27 630 |  |  |  |

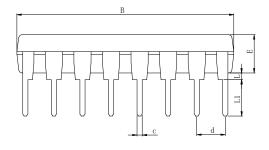

## DIP16

| Dimensions In Millimeters(DIP16) |      |       |      |      |      |      |      |      |      |      |          |

|----------------------------------|------|-------|------|------|------|------|------|------|------|------|----------|

| Symbol:                          | Α    | В     | D    | D1   | E    | L    | L1   | а    | b    | С    | d        |

| Min:                             | 6.10 | 18.94 | 8.40 | 7.42 | 3.10 | 0.50 | 3.00 | 1.50 | 0.85 | 0.40 | 2 F4 BCC |

| Max:                             | 6.68 | 19.56 | 9.00 | 7.82 | 3.55 | 0.70 | 3.60 | 1.55 | 0.90 | 0.50 | 2.54 BSC |

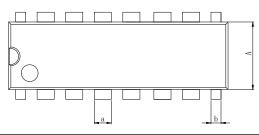

# **Physical Dimensions**

TSSOP16

| Dimensions In Millimeters(TSSOP16) |      |      |      |      |      |      |    |      |          |  |  |

|------------------------------------|------|------|------|------|------|------|----|------|----------|--|--|

| Symbol:                            | Α    | A1   | В    | С    | C1   | D    | Q  | а    | b        |  |  |

| Min:                               | 0.85 | 0.05 | 4.90 | 6.20 | 4.30 | 0.40 | 0° | 0.20 | 0.65 BSC |  |  |

| Max:                               | 0.95 | 0.20 | 5.10 | 6.60 | 4.50 | 0.80 | 8° | 0.25 | 0.00 BSC |  |  |

#### **IMPORTANT STATEMENT:**

Huaguan Semiconductor reserves the right to change its products and services without notice. Before ordering, the customer shall obtain the latest relevant information and verify whether the information is up to date and complete. Huaguan Semiconductor does not assume any responsibility or obligation for the altered documents.

Customers are responsible for complying with safety standards and taking safety measures when using Huaguan Semiconductor products for system design and machine manufacturing. You will bear all the following responsibilities: Select the appropriate Huaguan Semiconductor products for your application; Design, validate and test your application; Ensure that your application meets the appropriate standards and any other safety, security or other requirements. To avoid the occurrence of potential risks that may lead to personal injury or property loss.

Huaguan Semiconductor products have not been approved for applications in life support, military, aerospace and other fields, and Huaguan Semiconductor will not bear the consequences caused by the application of products in these fields. All problems, responsibilities and losses arising from the user's use beyond the applicable area of the product shall be borne by the user and have nothing to do with Huaguan Semiconductor, and the user shall not claim any compensation liability against Huaguan Semiconductor by the terms of this Agreement.

The technical and reliability data (including data sheets), design resources (including reference designs), application or other design suggestions, network tools, safety information and other resources provided for the performance of semiconductor products produced by Huaguan Semiconductor are not guaranteed to be free from defects and no warranty, express or implied, is made. The use of testing and other quality control technologies is limited to the quality assurance scope of Huaguan Semiconductor. Not all parameters of each device need to be tested.

The documentation of Huaguan Semiconductor authorizes you to use these resources only for developing the application of the product described in this document. You have no right to use any other Huaguan Semiconductor intellectual property rights or any third party intellectual property rights. It is strictly forbidden to make other copies or displays of these resources. You should fully compensate Huaguan Semiconductor and its agents for any claims, damages, costs, losses and debts caused by the use of these resources. Huaguan Semiconductor accepts no liability for any loss or damage caused by infringement.