# **Datasheet**

APM32F103xB

Arm® Cortex®-M3 based 32-bit MCU

**Chip version: Version D**

Manual version: V1.7

#### 1. Features

- System Architecture

- 32-bit Arm® Cortex®-M3 core

- Up to 96MHz working frequency

- Clock and Memories

- HSECLK: 4MHz~16MHz external crystal oscillator supported

- LSECLK: 32.768KHz RTC oscillator supported

- HSICLK: 8 MHz RC oscillator with calibration

- LSICLK: 40 KHz RC oscillator

- Flash: maximum 128 Kbytes

- SRAM: maximum 20 Kbytes

- Power supply and low-power mode

- 2.0 ~ 3.6 V reset supply voltage

- Support programmable voltage

Detector(PVD)

- Sleep, Stop and Standby modes

- V<sub>Bat</sub> power supply can support RTC and backup registers

- FPU

- Independent FPU module supports floating point operations

- ADCs and Temperature Sensor

- 2 12-bit ADCs, 16 input channels are supported

- ADC voltage conversion range:0~V<sub>DDA</sub>

- Double-sample and hold capability supported

- 1 on-chip temperature sensor

- I/O

- 80/51/37/26 I/Os selectable,

depending on models and packages

- All I/O pins are mappable to 16 external interrupt

- DMA

1 DMA, 7 separate configurable channels are supported

#### Timers

- 1 16-bit advanced control timer TMR1, support dead zone control and emergency braking functions

- 3 16-bit general-purpose timers

TMR2/3/4, each with up to 4 independent channels to support input capture, output comparison, PWM, pulse count and other functions

- 2 watchdog timers(Independent IWDT and Window WWDT)

- 1 24-bit autodecrement SysTick Timer

- Communication Interfaces

- 3 USART, support ISO7816, LIN and IrDA

- 2 I2C, support SMBus/PMBus

- 2 SPI with a maximum transfer speed of 18Mbps

- 1 QSPI, support single and four-wire access to Flash

- 1 USB 2.0 FS Device

- 1 CAN 2.0B, USBD and CAN can work independently at the same time)

- 1 CRC Unit

- 96-bit UID

- Serial wire debug SWD and JTAG interfaces

- Chip Packaging

- LQFP100/LQFP64/LQFP48/QFN36

- Applications

- Medical devices, PC peripherals,

industrial control, smart meters, household

appliances

## **CONTENTS**

| 1.     | Features                                                         | . 2 |

|--------|------------------------------------------------------------------|-----|

| 2.     | Overview                                                         | 10  |

| 3.     | Features Description                                             | 11  |

| 3.1.   | Arm® Cortex®-M3 Core                                             | 11  |

| 3.2.   | Memory                                                           | 12  |

| 3.3.   | Power Management                                                 | 12  |

| 3.3.1. | Power Supply Schemes                                             | 12  |

| 3.3.2. | Voltage Regulator                                                | 12  |

| 3.3.3. | Power Supply Monitor                                             | 13  |

| 3.3.4. | Low Power Mode                                                   | 13  |

| 3.4.   | Clocks and Startup                                               | 14  |

| 3.5.   | RTC and Backup Registers                                         | 14  |

| 3.6.   | Boot Modes                                                       | 14  |

| 3.7.   | CRC (Cyclic Redundancy Check) Calculation Unit                   | 14  |

| 3.8.   | General Purpose IO Port                                          | 15  |

| 3.8.1. | General-purpose urpose Input\Output Interface                    | 15  |

| 3.9.   | Interrupt Controller                                             | 15  |

| 3.9.1. | Nested Vectored Interrupt Controller (NVIC)                      | 15  |

| 3.9.2. | External Interrupt/Event Controller (EINT)                       | 15  |

| 3.10.  | Floating Point Unit (FPU)                                        | 15  |

| 3.11.  | DMA                                                              | 15  |

| 3.12.  | Timer                                                            | 16  |

| 3.13.  | Watchdog (WDT)                                                   | 17  |

| 3.14.  | Peripheral Interface                                             | 17  |

| 3.14.1 | .l <sup>2</sup> C Bus                                            | 17  |

| 3.14.2 | .Universal Synchronous/Asynchronous Receiver Transmitter (USART) | 18  |

| 3.14.3 | .Serial Peripheral Interface (SPI)                               | 18  |

| 3.14.4 | .Quad SPI Controller (QSPI)                                      | 18  |

| 3.14.5 | .Controller Area Network (CAN)                                   | 18  |

| 3.14.6 | .Universe Serial Bus (USBD)                                      | 18  |

| 3.14.7 | .Simultaneous Use of USBD Interface and CAN Interface:           | 19  |

| 3.14.8 | .ADC (Analog/Digital Converter)                                  | 19  |

| 3.14.9 | .Temperature Sensor                                              | 19  |

| 3.14.1 | 0. Debug Interface (SWJ-DP)                     | 19 |

|--------|-------------------------------------------------|----|

| 4.     | Pin Features                                    | 20 |

| 4.1.   | Pinouts and Pin Description                     | 20 |

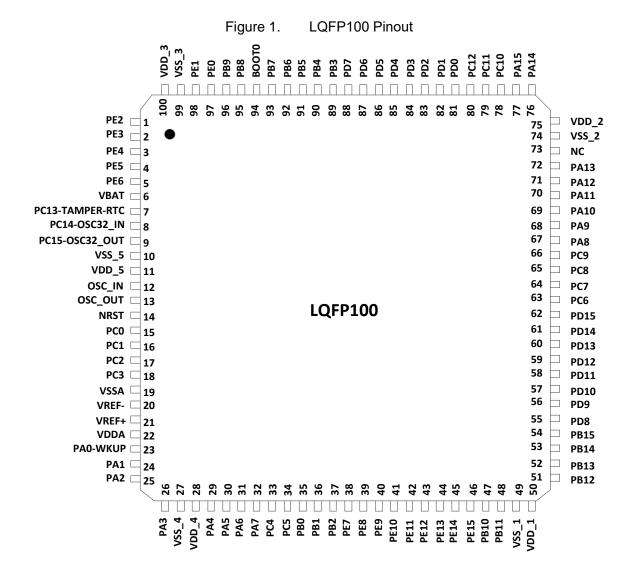

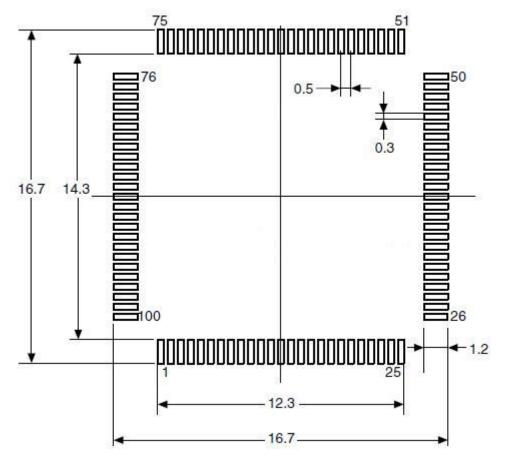

| 4.1.1. | APM32F103xB Series LQFP100                      | 20 |

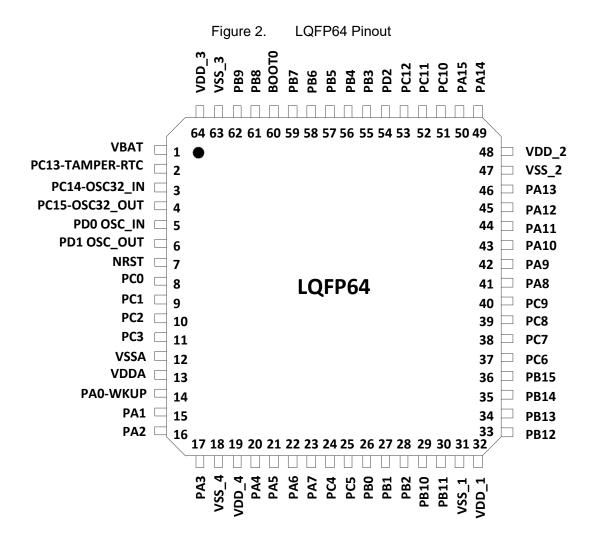

| 4.1.2. | APM32F103xB Series LQFP64                       | 21 |

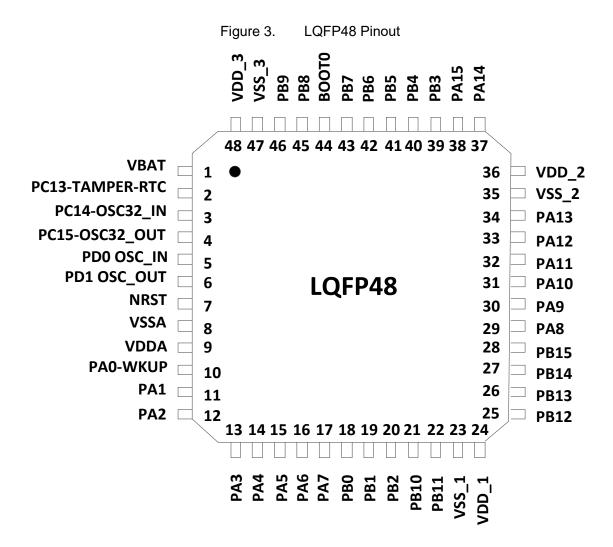

| 4.1.3. | APM32F103xB Series LQFP48                       | 22 |

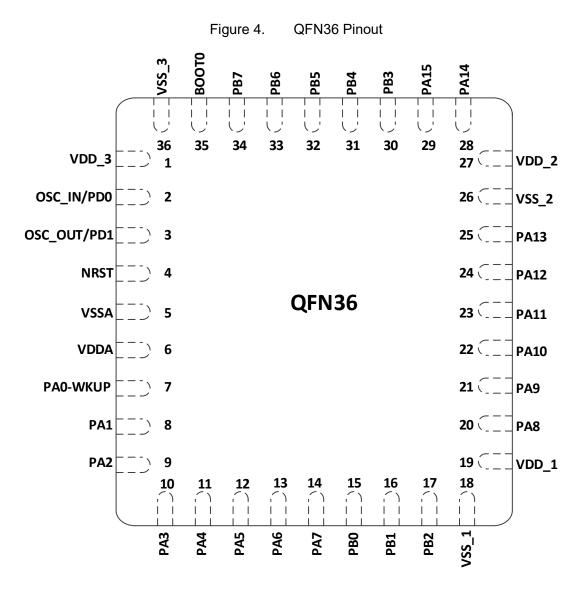

| 4.1.4. | APM32F103xB Series QFN36                        | 23 |

| 4.2.   | Pin Description                                 | 24 |

| 4.3.   | System Diagram                                  | 31 |

| 4.4.   | Clock Tree                                      | 32 |

| 4.5.   | Address Mapping                                 | 32 |

| 4.6.   | Power Supply Scheme                             | 35 |

| 5.     | Electrical Features                             | 36 |

| 5.1.   | Parameter Conditions                            | 36 |

| 5.1.1. | Maximum and Minimum Values                      | 36 |

| 5.1.2. | Typical Value                                   | 36 |

| 5.1.3. | Typical Curve                                   | 36 |

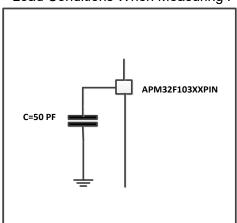

| 5.1.4. | Load Capacitance                                | 36 |

| 5.2.   | Absolute Maximum Ratings                        | 37 |

| 5.2.1. | Maximum Rated Voltage Features                  | 37 |

| 5.2.2. | Maximum Rated Current Features                  | 38 |

| 5.2.3. | Maximum Temperature Features                    | 39 |

| 5.2.4. | Maximum Ratings Electrical Sensitivity          | 39 |

| 5.3.   | Test Under the General Working Conditions       | 40 |

| 5.3.1. | Embedded Reset and Power Control Block Features | 41 |

| 5.3.2. | Built-in Reference Voltage Features Test        | 41 |

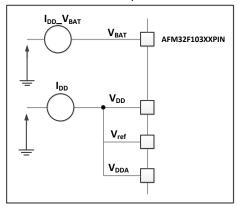

| 5.3.3. | Supply Current Features                         | 42 |

| 5.3.4. | External Clock Source Features                  | 50 |

| 5.3.5. | Internal Clock Source Features                  | 53 |

| 5.3.6. | PLL Features                                    | 55 |

| 5.3.7. | Memory Features                                 | 55 |

| 5.3.8. | I/O Ports Features                              | 56 |

| 5.3.9. | NRST Pins Features                              | 59 |

| E 2 10 | Communication Interface                         | 50 |

| 5.3.11 | .12-bit ADC Features                       | 64 |

|--------|--------------------------------------------|----|

| 5.3.12 | Temperature Sensor Features                | 67 |

| 5.3.13 | EMC Features                               | 67 |

| 6.     | Package Information                        | 69 |

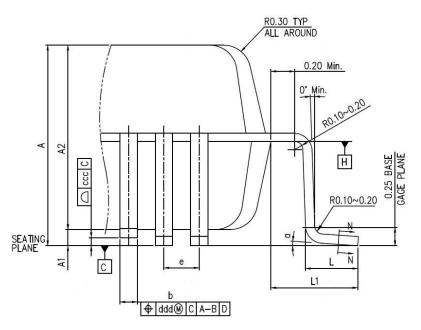

| 6.1.   | LQFP100 Package Diagram                    | 69 |

| 6.2.   | LQFP64 Package Diagram                     | 72 |

| 6.3.   | LQFP48 Package Diagram                     | 75 |

| 6.4.   | QFN36 Package Diagram                      | 78 |

| 7.     | Ordering Information                       | 81 |

| 8.     | Packaging Information                      | 83 |

| 9.     | Commonly Used Function Module Denomination | 87 |

| 10.    | Version History                            | 88 |

## **TABLE CONTENTS**

| Table 1.  | Functions and peripherals of APM32F103xB                                                                                 | 11 |

|-----------|--------------------------------------------------------------------------------------------------------------------------|----|

| Table 2.  | Memory Description                                                                                                       | 12 |

| Table 3.  | Power Supply Schemes                                                                                                     | 12 |

| Table 4.  | Operation Modes of Voltage Regulator                                                                                     | 12 |

| Table 5.  | Low Power Consumption Mode                                                                                               | 13 |

| Table 6.  | Timer Feature Comparison                                                                                                 | 16 |

| Table 7.  | Watchdog                                                                                                                 | 17 |

| Table 8.  | APM32F103xB Pin Definitions                                                                                              | 24 |

| Table 9.  | APM32F103xB Storage Mapping Table                                                                                        | 32 |

| Table 10. | Maximum Rated Voltage Features                                                                                           | 37 |

| Table 11. | Maximum Rated Current Features                                                                                           | 38 |

| Table 12. | Temperature Features                                                                                                     | 39 |

| Table 13. | ESD Absolute Maximum Ratings (1)                                                                                         | 39 |

| Table 14. | Static Latch (1)                                                                                                         | 39 |

| Table 15. | General Working Conditions                                                                                               | 40 |

| Table 16. | Embedded Reset and Power Control Block Features (T <sub>A</sub> =25°C) $(-40^{\circ}\text{C} \sim +105^{\circ}\text{C})$ | 41 |

| Table 17. | Built-in Reference Voltage                                                                                               | 41 |

| Table 18. | Run-mode Current Consumption, Code with Data Processing Running From Internal Flash                                      | 43 |

| Table 19. | Run-mode Current Consumption, Code with Data processing Running From Internal RAM                                        | 44 |

| Table 20. | Maximum Current Consumption in Sleep Mode, Code Runs from Flash or RAM                                                   | 45 |

| Table 21. | Maximum Current Consumption in Stop Mode and Standby Mode                                                                | 46 |

| Table 22. | Run-mode current consumption, code with data processing running from internal Flash                                      | 47 |

| Table 23. | Run-mode current consumption, code with data processing running from internal RAM                                        | 48 |

| Table 24. | Typical current consumption in sleep mode, code running from Flash or RAM                                                | 49 |

| Table 25. | Typical current Consumption in Stop Mode and Standby Mode                                                                | 50 |

| Table 26. | HSECLK 4~16MHz Oscillator Features <sup>(1)(2)</sup>                                                                     | 50 |

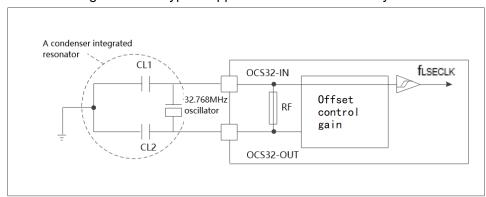

| Table 27. | LSECLK Oscillator Features (flseclk =32.768KHz) (1)                                                                      | 52 |

| Table 28. | HSICLK Oscillator Features <sup>(1)</sup>                                                                                | 53 |

| Table 29. | LSICLK Oscillator Features (1)                                                                                           | 54 |

| Table 30. | Wake Up Time in Low Power Mode                                                                                           | 54 |

| Table 31. | PLL Features                                                                                                             | 55 |

| Table 32. | FLASH Memory Features (1)                                                                                                | 55 |

| Table 33. | FLASH Memory Life and Data Retention Period                                                                              | 55 |

| Table 34.I/O Static Features (Test conditions Vcc=2.7-3.6V, T <sub>A</sub> = -40~105°C)                      | . 56 |

|--------------------------------------------------------------------------------------------------------------|------|

| Table 35.Output Voltage Features (test conditions V <sub>CC</sub> =2.7-3.6V,T <sub>A</sub> = -40~105°C)      | . 57 |

| Table 36.Input and Output AC Features                                                                        | . 57 |

| Table 37.NRST NRST Pin Features (Test condition V <sub>CC</sub> =3.3V,T <sub>A</sub> = -40~105°C)            | . 59 |

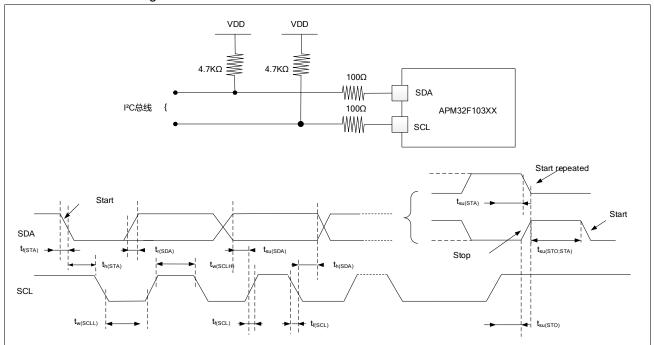

| Table 38.I <sup>2</sup> C Interface Features (Test conditions V <sub>DD</sub> = 3.3V, T <sub>A</sub> = 25°C) | . 59 |

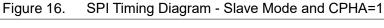

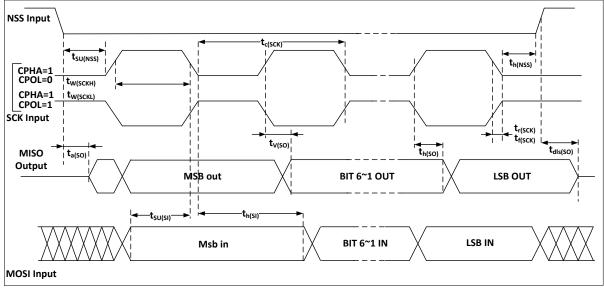

| Table 39.SPI Features (V <sub>DD</sub> = 3.3V,T <sub>A</sub> =25°C)                                          | . 61 |

| Table 40.USBD DC Characteristics                                                                             | . 63 |

| Table 41.USBD Full-speed Electrical Characteristics                                                          | . 64 |

| Table 42.ADC Features (V <sub>DD</sub> = 2.4-3.6V,T <sub>A</sub> =-40~105°C)                                 | . 64 |

| Table 43.Maximum R <sub>AIN</sub> at f <sub>ADC</sub> =14MHz <sup>(</sup> )                                  | . 66 |

| Table 44.ADC Accuracy                                                                                        | . 66 |

| Table 45.Temperature Sensor Features                                                                         | . 67 |

| Table 46.EMS Features                                                                                        | . 68 |

| Table 47.EMI Features                                                                                        | . 68 |

| Table 48.LQFP100 Package Data                                                                                | . 70 |

| Table 49.LQFP64 Package Data                                                                                 | . 73 |

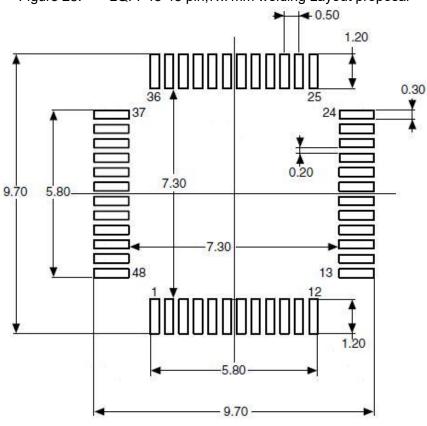

| Table 50.LQFP Package Data                                                                                   | . 76 |

| Table 51.QFN36 Package Data                                                                                  | . 79 |

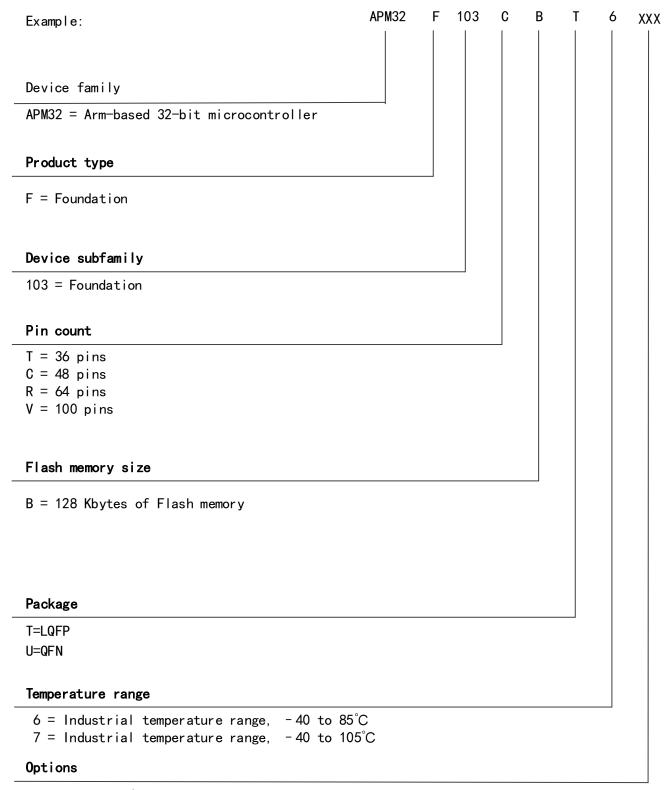

| Table 52.Ordering Information Table                                                                          | . 82 |

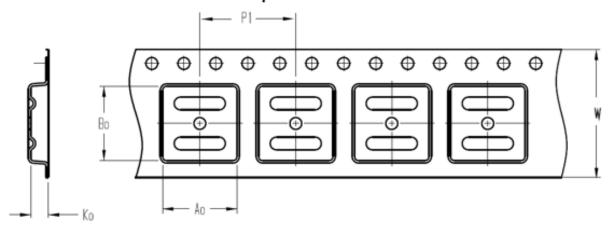

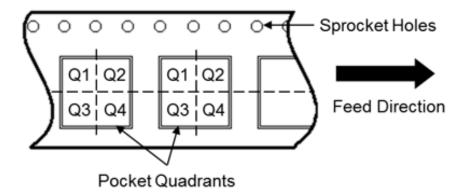

| Table 53.Reel Packaging Parameters Specification                                                             | . 84 |

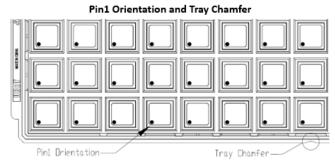

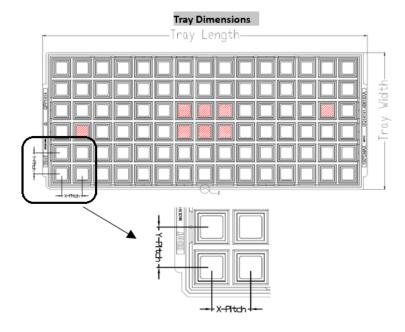

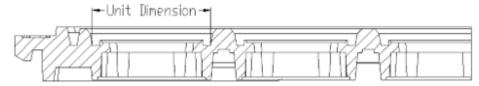

| Table 54.Tray Packaging Parameters Specification                                                             | . 85 |

| Table 55.Commonly Used Function Module Denomination                                                          | . 87 |

| Table 56.Document Version History                                                                            | . 88 |

## **FIGURE CONTENTS**

| Figure 1. LQF | FP100 Pinout                                               | 20 |

|---------------|------------------------------------------------------------|----|

| Figure 2. LQI | FP64 Pinout                                                | 21 |

| Figure 3. LQI | FP48 Pinout                                                | 22 |

| Figure 4. QFI | N36 Pinout                                                 | 23 |

| Figure 5. API | M32F103xB Series System Diagram                            | 31 |

| Figure 6. API | M32F103xB Series Clock Tree                                | 32 |

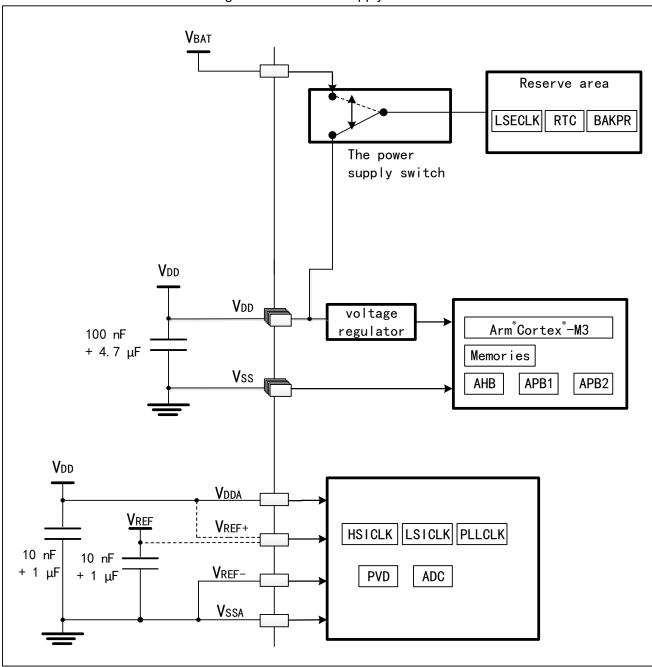

| Figure 7. Pov | ver Supply Scheme                                          | 35 |

| Figure 8. Loa | d Conditions When Measuring Pin Parameters                 | 36 |

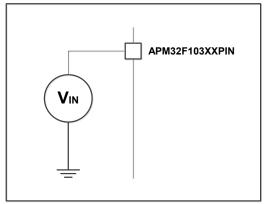

| Figure 9. Pin | Input Voltage Measurement Scheme                           | 37 |

| Figure 10.    | Current Consumption Measurement Scheme                     | 37 |

| Figure 11.    | Typical application of 8MHz crystal oscillator             | 52 |

| Figure 12.    | Typical application of 32.768MHz crystal oscillator.       | 53 |

| Figure 13.    | Input and Output AC Features Definition                    | 58 |

| Figure 14.    | Bus AC Waveform and Measurement Circuit (1)                | 60 |

| Figure 15.    | SPI Timing Diagram - Slave Mode and CPHA=0                 | 62 |

| Figure 16.    | SPI Timing Diagram - Slave Mode and CPHA=1                 | 62 |

| Figure 17.    | SPI Timing Diagram - Master Mode <sup>(3)</sup>            | 63 |

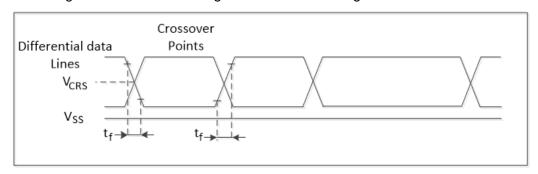

| Figure 18.    | USBD Timing: Definition of Data Signal Rise and Fall Times | 64 |

| Figure 19.    | Typical application of ADC                                 | 65 |

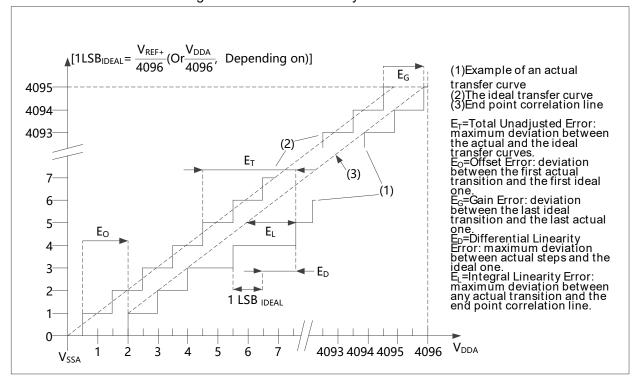

| Figure 20.    | ADC Accuracy Characteristics                               | 67 |

| Figure 21.    | LQFP100 Package Diagram.                                   | 69 |

| Figure 22.    | LQFP100-100 pins,14x14mm welding Layout proposal           | 71 |

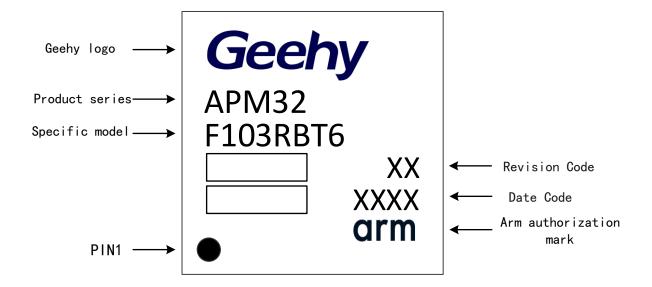

| Figure 23.    | LQFP100-100 pin,14x14mm package identification diagram     | 71 |

| Figure 24.    | LQFP64 Package Diagram                                     | 72 |

| Figure 25.    | LQFP64-64 pin,10x10mm welding Layout proposal              | 74 |

| Figure 26.    | LQFP64-64 pin,10x10mm package identification diagram       | 74 |

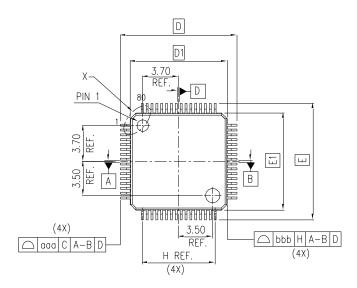

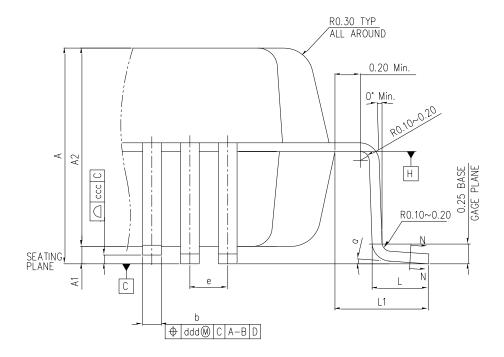

| Figure 27.    | LQFP48 Package Diagram                                     | 75 |

| Figure 28.    | LQFP48-48 pin,7x7mm welding Layout proposal                | 77 |

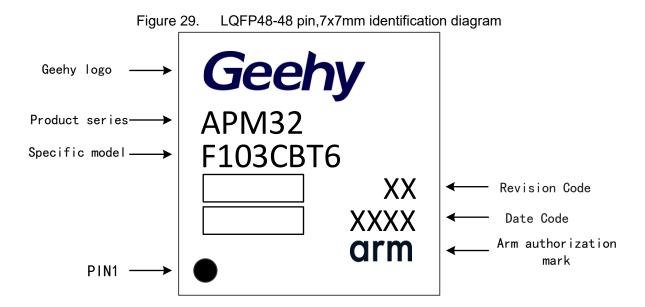

| Figure 29.    | LQFP48-48 pin,7x7mm identification diagram                 | 77 |

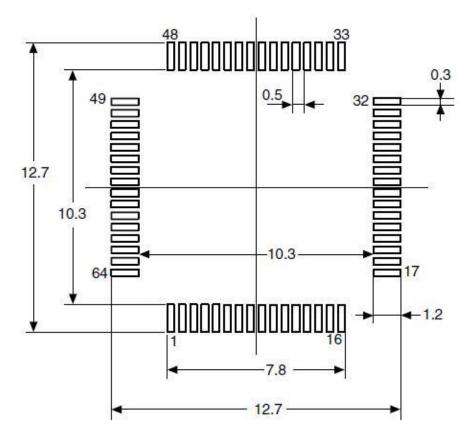

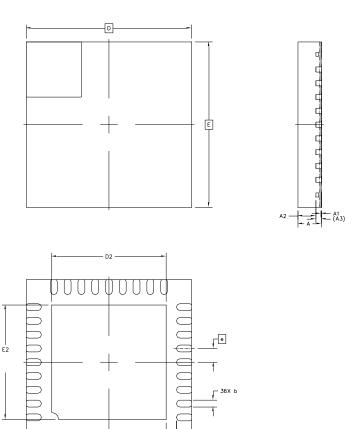

| Figure 30.    | QFN36 Package Diagram                                      | 78 |

| Figure 31.    | QFN36 pin, 6 x 6mm Welding Layout Proposal                 | 80 |

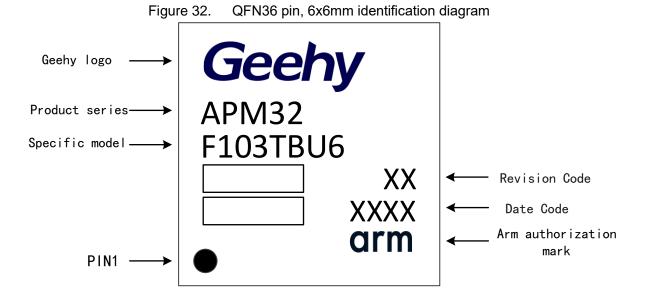

| Figure 32.    | QFN36 pin, 6x6mm identification diagram                    | 80 |

| Figure 33.    | Reel Packaging Specification Diagram                       | 83 |

| Figure 34. | Tray Packaging Diagram | <br>8 |

|------------|------------------------|-------|

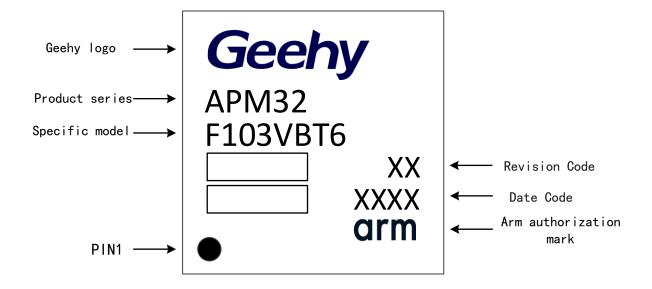

#### 2. Overview

The APM32F103xB series chips are Arm<sup>®</sup> Cortex<sup>®</sup>-M3 core based 32-bit microcontrollers with a maximum operating frequency of 96MHz. Built-in AHB high-performance bus, combined with high-speed memory and DMA for fast data processing and storage. The built-in APB advanced peripheral bus expands the rich peripherals and enhanced I/O, ensuring fast connection and control flexibility. The chips are equipped with a powerful FPU floating-point arithmetic processing unit that supports single-precision data processing instructions and data types.

Built-in up to 128K bytes of flash memory and 20K bytes of SRAM memory, and all models include 2 12-bit ADCs, 3 general-purpose 16-bit timers, 1 advanced control timer and 1 temperature sensor, as well as standard communication interfaces: 2 I2C interfaces, 2 SPI interfaces, 1 QSPI interface, 3 USART interfaces, 1 USB 2.0 FS interface and 1 CAN 2.0B interface(USBD and CAN can work independently at the same time).

Operating voltage is  $2.0V \sim 3.6V$ , there are two types of operating temperature range selectable:  $-40^{\circ}C \sim +85^{\circ}C$  and  $-40^{\circ}C \sim +105^{\circ}C$ . Available for four different package forms of LQFP100/LQFP64/LQFP48/QFN36, with different peripherals and I/O configurations.

For information about the Arm® Cortex®-M3 core, please refer to the Arm® Cortex®-M3 technical reference manual, which can be downloaded from Arm's website.

This datasheet is applicable to APM32F103xB series D version products.

## 3. Features Description

See the following table for specific APM32F103xB product functions and peripheral configuration.

Table 1. Functions and peripherals of APM32F103xB

| Product                 |                         | APM32F103xB |        |         |          |

|-------------------------|-------------------------|-------------|--------|---------|----------|

|                         |                         | ТВ          | СВ     | RB      | VB       |

|                         | Packaging               | QFN36       | LQFP48 | LQFP 64 | LQFP 100 |

|                         | Flash(Kbytes)           |             | 12     | 28      |          |

|                         | SRAM(Kbytes)            |             | 2      | 0       |          |

|                         | General-purpose(16-bit) |             | 3      |         |          |

| ပ                       | Advanced(16-bit)        |             | 1      |         |          |

| Timers                  | SysTick                 |             | 1      |         |          |

| _                       | Watchdog                |             | 2      | 2       |          |

|                         | RTC                     |             | 1      |         |          |

|                         | SPI                     | 1           |        | 2       |          |

| Communication           | QSPI                    |             | 0      |         | 1        |

| mmunicati<br>Interfaces | I2C                     | 1           |        | 2       |          |

| nmu<br>nter             | USART                   | 2           |        | 3       |          |

| Cor                     | CAN2.0B                 |             | 1      |         |          |

|                         | USB2.0 FS               | 1           |        |         |          |

| 12 bit<br>ADC           | Unit                    | 2           |        |         |          |

| 12<br>A                 | Channel                 | 10 16       |        | 3       |          |

| GPIOs                   |                         | 26          | 37     | 51      | 80       |

| CPU@Max. frequency      |                         |             | M3@9   | 6MHz    |          |

| FPU                     |                         | 1           |        |         |          |

| Operating voltage       |                         |             | 2.0 V~ | 3.6 V   |          |

## 3.1. Arm<sup>®</sup> Cortex<sup>®</sup>-M3 Core

APM32F103xB series with built-in Arm® Cortex®-M3 core, 96MHz working frequency, and are compatible with Arm's tools and softwares.

System diagram of APM32F103xB series products is shown in Figure 5.

## 3.2. Memory

Table 2. Memory Description

| Memory                       | The biggest byte | Function                                                            |

|------------------------------|------------------|---------------------------------------------------------------------|

| Embedded High-speed<br>Flash | 128 Kbytes       | For storing programs and data                                       |

| Embedded Static Memory       | 20 Kbytes        | Can be accessed in bytes, halfwords(16 bits) or full words(32 bits) |

## 3.3. Power Management

### 3.3.1. Power Supply Schemes

Table 3. Power Supply Schemes

| Name Voltage Range |           | Description                                                               |

|--------------------|-----------|---------------------------------------------------------------------------|

|                    |           | $V_{\text{DD}}$ directly supplies power to IO port, and $V_{\text{DD}}$   |

| $V_{DD}$           | 2.0∼3.6V  | supplies power to core circuit through voltage                            |

|                    |           | regulator.                                                                |

|                    |           | Connected to V <sub>DD</sub> , it supplies power to the analog            |

|                    |           | parts of ADC, reset module, RC oscillator and PLL.                        |

| $V_{DDA}$          | 2.4~3.6V  | When ADC is being used, $V_{\text{DDA}}$ is greater than or               |

|                    |           | equal to 2.4V. $V_{\text{DDA}}$ and $V_{\text{SSA}}$ must be connected to |

|                    |           | V <sub>DD</sub> and V <sub>SS</sub> respectively.                         |

|                    |           | Automatically supply power to RTC, external                               |

| $V_{BAT}$          | 1.8V∼3.6V | 32KHz oscillator and backup registers when $V_{\text{DD}}$ is             |

|                    |           | off.                                                                      |

Note: See Figure 8 for more details on how to connect power supply pins.

### 3.3.2. Voltage Regulator

There are three main modes of voltage regulator. The working mode of MCU can be adjusted by voltage regulator to reduce power consumption.

Table 4. Operation Modes of Voltage Regulator

| Name                 | Description                                            |

|----------------------|--------------------------------------------------------|

| Main Mode(MR)        | 1.6V power supply(core, memory, peripherals) in normal |

|                      | regulation mode                                        |

| Low Power Mode(LPR)  | 1.6V power supply in low power mode to preserve the    |

| Low Fower Mode(EFTY) | contents of register and SRAM                          |

| Power Down Mode      | Used in Standby mode: the regulator output is in high  |

| Name | Description                                               |

|------|-----------------------------------------------------------|

|      | impedance: the kernel circuitry is powered down, inducing |

|      | zero consumption (but the contents of the registers and   |

|      | SRAM are lost)                                            |

This regulator is always enabled after reset, and outputs with high impedance in power-down mode.

#### 3.3.3. Power Supply Monitor

Two circuits of power-on reset (POR) and power-down reset (PDR), are integrated inside the product. When  $V_{DD}$  reaches the set threshold  $V_{POR/PDR}$ , the system works normally. When  $V_{DD}$  is below the specified threshold  $V_{POR/PDR}$ , the system remains in a reset state without the need for an external reset circuit.

For details of V<sub>POR/PDR</sub>, please refer to the electrical feature in chapter 5.

#### 3.3.4. Low Power Mode

The product supports the following three low power consumption modes, which can be configured by users to meet the best application requirements.

Table 5. Low Power Consumption Mode

| Mode Types   | Description                                                                   |

|--------------|-------------------------------------------------------------------------------|

| Sloop Mada   | In Sleep mode, only the CPU is stopped. All peripherals continue to           |

| Sleep Mode   | operate and can wake up the CPU when an interrupt/event occurs.               |

|              | The Stop mode achieves the lowest power consumption while retaining           |

|              | the content of SRAM and registers. At this point, part of the 1.6V power      |

| Stan Mada    | supply are stopped, resulting in the HSECLK, HSICLK, and PLL clocks           |

| Stop Mode    | are disabled. The voltage regulator is either in normal or in low-power       |

|              | mode. Interrupt, event wakeup configured as EINT can wake up the              |

|              | CPU from stop mode.                                                           |

|              | The Standby mode is used to achieve the lowest power consumption.             |

|              | The internal voltage regulator is switched off so that part of 1.6 V          |

|              | domain is powered off. The HSECLK, HSICLK, and PLL clocks are also            |

| Standby Mada | switched off. The contents of SRAM and registers are lost, but contents       |

| Standby Mode | of the backup registers will still remain, and the standby circuit will still |

|              | work. The external reset signal on NRST, IWDT, will reset an ascending        |

|              | edge on the WKUP pin or the RTC clock will then terminate the chip            |

|              | standby mode.                                                                 |

Note: The RTC, the IWDT, and the corresponding clock sources are not stopped by entering

stop or standby mode. QSPI interrupts cannot wake up low power mode.

### 3.4. Clocks and Startup

The internal 8MHz RC oscillator serves as the default clock for system startup, and can be switched to the external 4-16mhz clock with failure monitoring through configuration.

When an external clock failure is detected, the system will automatically switch to an internal RC oscillator, and if an interrupt is set, the software can receive the related interrupt.

The frequencies of AHB high-speed APB(APB2) and low-speed APB(APB1) can be configured through the predivider. The maximum frequency of AHB and high-speed APB is 96MHz and that of low speed APB is 48MHz.

See Figure 6 for details on the clock tree.

### 3.5. RTC and Backup Registers

The RTC has a set of continuously running counters, which can provide calendar alarm interruption and stage interruption functions with softwares. Its clock source can choose external 32.768khz crystal oscillator, internal 40KHz low-speed RC oscillator or external high-speed clock with 128 frequency division. Moreover, the RTC clock can be calibrated for errors through a 512Hz signal.

A backup register for 10 16-bit registers to hold 20 bytes of user data when VDD is off. RTC and backup registers are powered by  $V_{DD}$  when  $V_{DD}$  is in effect; otherwise, it will be powered by  $V_{BAT}$  pins. System or power reset source reset, waking up from standby mode, does not cause the reset of RTC and backup register.

#### 3.6. Boot Modes

At startup, you can choose one of three bootstrap modes through the bootstrap pin:

- Boot from User Flash

- Boot from System Memory

- Boot from embedded SRAM

The boot loader is located in System Memory. It is used to reprogram the Flash memory by using USART1.

## 3.7. CRC (Cyclic Redundancy Check) Calculation Unit

The CRC (Cyclic Redundancy Check) calculation unit is used to get a CRC code from a 32-bit data word and a fixed generator polynomial.

The CRC calculation unit helps compute a signature of the software during runTime, to be compared with a reference signature generated at link-Time and stored at a given memory location.

### 3.8. General Purpose IO Port

80/51/37/26 I/O is available for the product, and the specific selection can refer to the model and package. All I/O can be mapped to 16 external interrupt controllers, and most of I/O support 5V logic level input.

#### 3.8.1. General-purpose urpose Input\Output Interface

The product can be up to 80 GPIO pins, each of the GPIOs can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions. The I/Os alternate function configuration can be locked if needed following a specific sequence in order to avoid spurious writing to the I/Os registers.

I/Os on APB2 with up to 18 MHz toggling speed.

### 3.9. Interrupt Controller

#### 3.9.1. Nested Vectored Interrupt Controller (NVIC)

It embeds a nested vectored interrupt controller (NVIC) that can handle up to 47 maskable interrupt channels (not including 16 interrupt lines of Cortex®-M3) and 16 priority levels. The interrupt vector entry address can be directly transmitted to the core, so that the interrupt response processing with low delay can give priority to the late higher priority interrupt.

#### 3.9.2. External Interrupt/Event Controller (EINT)

The external interrupt/event controller consists of 19 edge detector lines used to generate interrupt/event requests. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. Up to 80 GPIOs can be connected to the 16 external interrupt lines. The EINT can detect an external line with a pulse width shorter than the Internal APB2 clock period.

## 3.10. Floating Point Unit (FPU)

The product has a embedded independent FPU floating-point arithmetic processing unit that supports the IEEE754 standard and supports single-precision floating-point operations.

#### 3.11. DMA

The flexible 7-channel general-purpose DMA is able to manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers.

Each channel is connected to dedicated hardware DMA requests, with support for software trigger on each channel. Configuration is made by software and transfer sizes between source

and destination are independent.

The DMA can be used with the main peripherals: SPI, I2C, USART, general-purpose and advanced-control Timers TMRx and ADC.

#### 3.12. Timer

The product includes an advanced-control Timer (TMR1), three general-purpose Timers (TMR2/3/4), an independent watchdog Timer, a window watchdog Timer, and a SysTickTimer. The following table compares the features of the advanced-control and general-purpose Timers:

Table 6. Timer Feature Comparison

| Table 6. Timer realure Companson |                                                                                                                                    |                                                                                                                                                                 |             |                                                                                               |                                                                                                                                                                                             |                    |                                                                                                                                                               |  |  |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Type of Timer                    | SysTick Timer                                                                                                                      | Gen                                                                                                                                                             | eral-purpos | e Timer                                                                                       | Advanced -control Timer                                                                                                                                                                     |                    |                                                                                                                                                               |  |  |

| Timer                            | Sys Tick Timer                                                                                                                     | TMR2                                                                                                                                                            | TMR3        | TRM4                                                                                          | TMR1                                                                                                                                                                                        |                    |                                                                                                                                                               |  |  |

| Counter<br>Resolution            | 24-bit                                                                                                                             |                                                                                                                                                                 | 16-bit      |                                                                                               | 16-bit                                                                                                                                                                                      |                    |                                                                                                                                                               |  |  |

| Counter Type                     | Down                                                                                                                               | Uį                                                                                                                                                              | p, down, up | /down                                                                                         | Up, down, up/down                                                                                                                                                                           |                    |                                                                                                                                                               |  |  |

| Prescaler<br>Factor              | -                                                                                                                                  | Any integ                                                                                                                                                       | jer between | 1 and 65536                                                                                   | Any integer between 1 and 65536                                                                                                                                                             |                    |                                                                                                                                                               |  |  |

| DMA Request generation           | -                                                                                                                                  |                                                                                                                                                                 | Yes         |                                                                                               | Yes                                                                                                                                                                                         |                    |                                                                                                                                                               |  |  |

| Capture/Compa<br>re Channels     | -                                                                                                                                  |                                                                                                                                                                 | 4           |                                                                                               | 4                                                                                                                                                                                           |                    |                                                                                                                                                               |  |  |

| Complementary Outputs            | -                                                                                                                                  |                                                                                                                                                                 | No          |                                                                                               | Yes                                                                                                                                                                                         |                    |                                                                                                                                                               |  |  |

| Pin<br>characteristics           | -                                                                                                                                  | There are 5 pins in total:  1-way external trigger signal input pins,  4-way channel (non-complementary channel) pins                                           |             | r signal input                                                                                | There are 9 pins in total:  1-way external trigger signal input pins,  1-way braking input signal pins,  3-pair complementary channel pins,  1-way channel (non-complementary channel) pins |                    |                                                                                                                                                               |  |  |

| Function<br>Specification        | Dedicated for OS  Automatic reload function  Maskable system interrupt  generation when the  counter reaches 0  Programmable clock | Synchronization or event chaining function provided.  Counters can be frozen in debug mode  Can be used to generate PWM outputs  Each Timer has independent DMA |             | function provided.  Counters can be frozen in debug mode  Can be used to generate PWM outputs |                                                                                                                                                                                             | in debug<br>te PWM | Complementary PWM outputs with programmable inserted dead-Times  If configured as a general-purpose 16-bit Timer, it has the same features as the TMRx Timer. |  |  |

|                                  | source                                                                                                                             | Each Timer                                                                                                                                                      | has indepe  | ndent DMA                                                                                     | If configured as the 16-bit PWM                                                                                                                                                             |                    |                                                                                                                                                               |  |  |

|  | request generation.                    | generator, it has full modulation   |

|--|----------------------------------------|-------------------------------------|

|  | It can handle quadrature (incremental) | capability (0-100%).                |

|  | encoder signals and the digital        | In debug mode, the advanced-control |

|  | outputs from 1 to 3 hall-effect        | Timer counter can be frozen and     |

|  | sensors                                | the PWM outputs disabled.           |

|  |                                        | Synchronization or event chaining   |

|  |                                        | provided                            |

## 3.13. Watchdog (WDT)

The product includes two watchdogs, providing greater security, Time accuracy and flexibility. The two watchdogs(independent and window watchdog)can be used for detecting and resolving failures caused by software errors. When the counter reaches a given Timeout value, an interrupt is triggered (for window watchdogs only) or a system reset is generated.

Table 7. Watchdog

| Watahdaa                    | Counter    | Counter | Prescale                               | functional                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|-----------------------------|------------|---------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Watchdog                    | Resolution | Type    | Factor                                 | Tunctional                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| Independe<br>nt<br>Watchdog | 12-bit     | down    | Any<br>integer<br>between 1<br>and 256 | It is clocked from an independent 40 kHz internal RC oscillator and as it operates independently from the main clock, it can operate in stop and standby modes.  Reset the device when a problem occurs.  As a free-running Timer for application Timeout management.  It is hardware- or software-configurable through the option bytes.  The counter can be frozen in debug mode. |  |  |

| Window<br>Watchdog          | 7-bit      | down    | -                                      | It can be set as free-running.  Reset the device when a problem occurs.  It is clocked from the main clock. It has an early warning interrupt capability.  The counter can be frozen in debug mode.                                                                                                                                                                                 |  |  |

## 3.14. Peripheral Interface

#### 3.14.1. I2C Bus

Two embedded I<sup>2</sup>C (I<sup>2</sup>C1, I<sup>2</sup>C2) bus interfaces can operate in multimaster or slave mode. They can support standard and fast modes. They support dual slave addressing (7-bit only) and both

7/10-bit addressing in master mode. A hardware CRC generation/verification is embedded. They can be served by DMA and they support SM Bus 2.0/PM Bus.

I<sup>2</sup>C3/4 bus extended the function of I<sup>2</sup>C 1/2. They can operate in standard, fast and high speed mode. The fast mode and high speed mode devices are backwards compatible.

#### 3.14.2. Universal Synchronous/Asynchronous Receiver Transmitter (USART)

Three USART communication interfaces are embedded, providing hardware management of the CTS and RTS signals, and IrDA SIR ENDEC supported. They are ISO 7816 compliant and have LIN Master/Slave capability. One of the USART interfaces is able to communicate at speeds of up to 4.5 Mbit/s. The other available interfaces communicate at up to 2.25 Mbit/s. All USART interfaces can be served by the DMA controller.

#### 3.14.3. Serial Peripheral Interface (SPI)

Two SPIs are able to communicate up to 18 Mbits/s in slave and master modes in full-duplex and simplex communication modes while the frame is configurable to 8 bits or 16 bits. Both SPIs can be served by the DMA controller.

#### 3.14.4. Quad SPI Controller (QSPI)

The product has an embedded QSPI dedicated communication interface that can be connected to external flash via single, dual or quad SPI mode, supporting 8-bit, 16-bit and 32-bit access. There are 8 bytes of transmit FIFO and 8 bytes of receive FIFO.

#### 3.14.5. Controller Area Network (CAN)

The CAN is compliant with specifications 2.0A and B (active) with a bit rate up to 1 Mbit/s. It can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers. It has three transmit mailboxes, two receive FIFOs with 3 stages and 14 scalable filter banks.

#### 3.14.6. Universe Serial Bus (USBD)

The product embeds USBD modules (USBD1 and USBD2) compatible with full-speed USBD devices, which comply with the standard of full-speed USBD devices (12Mb/s), and the endpoints can be configured by software, and have standby/wake-up functions. The dedicated 48MHz clock for USBD is directly generated by internal PLL. When using the USBD function, the system clock can only be one of 48MHz, 72MHz and 96MHz, which can obtain 48MHz required for USBD through 1 fractional frequency, 1.5 fractional frequency and 2 fractional frequency respectively.

USBD1 and USBD2 share register address and pin interface, so only one of them can be used at the same time.

#### 3.14.7. Simultaneous Use of USBD Interface and CAN Interface:

When USBD and CAN are used together, you need to:

- Write 0x00000001 at the base address offset 0x100 of the USBD.

- The PA11 and PA12 pins are for USBD and CAN is used to multiplex other pins.

#### 3.14.8. ADC (Analog/Digital Converter)

Two 12-bit analog-to-digital converters are embedded into APM32F103x8xb performance line devices and each ADC shares up to 16 external channels, performing conversions in single-shot or scan modes. In scan mode, automatic conversion is performed on a selected group of analog inputs.

Additional logic functions embedded in the ADC interface allow:

- Simultaneous sample and hold

- Interleaved sample and hold

- Single shunt

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

The events generated by the general-purpose Timers (TMRx) and the advanced-control Timer (TMR1) can be internally connected to the ADC start trigger, injection trigger, and DMA trigger respectively, to allow the application to synchronize A/D conversion and Timers.

#### 3.14.9. Temperature Sensor

The temperature sensor has to generate a voltage that varies linearly with temperature. The conversion range is between 2 V < VDDA < 3.6 V. The temperature sensor is internally connected to the ADC12\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

#### 3.14.10. Debug Interface (SWJ-DP)

The product supports serial debug interface (SW-DP) and JTAG (JTAG-DP) debug interface. The JTAG interface provides a 5-pin standard JTAG interface for the AHB access port. The SW-DP interface provides a 2-pin (data + clock) interface to the AHB module.

The two pins of the SW-DP interface and the five pins of the JTAG interface are multiplexed.

#### 4. Pin Features

## 4.1. Pinouts and Pin Description

#### 4.1.1. APM32F103xB Series LQFP100

#### 4.1.2. APM32F103xB Series LQFP64

#### 4.1.3. APM32F103xB Series LQFP48

#### 4.1.4. APM32F103xB Series QFN36

## 4.2. Pin Description

Table 8. APM32F103xB Pin Definitions

|                                    |        | Pi     | ns      |       |          |               | Main Function (3)   | Alternate func | tions              |

|------------------------------------|--------|--------|---------|-------|----------|---------------|---------------------|----------------|--------------------|

| Pin Name                           | LQFP48 | LQFP64 | LQFP100 | QFN36 | Type (1) | I/O level (2) | (after reset)       | Default        | Remap              |

| PE2                                | -      | -      | 1       | -     | I/O      | FT            | PE2                 | TRACECK        | -                  |

| PE3                                | -      | -      | 2       | -     | I/O      | FT            | PE3                 | TRACED0        | -                  |

| PE4                                | -      | -      | 3       | -     | I/O      | FT            | PE4                 | TRACED1        | -                  |

| PE5                                | -      | 1      | 4       | -     | I/O      | FT            | PE5                 | TRACED2        | -                  |

| PE6                                | -      | -      | 5       | -     | I/O      | FT            | PE6                 | TRACED3        | -                  |

| $V_{BAT}$                          | 1      | 1      | 6       | -     | S        | -             | $V_{BAT}$           | -              | -                  |

| PC13-<br>TAMPER-RTC <sup>(4)</sup> | 2      | 2      | 7       | -     | I/O      | 1             | PC13 <sup>(3)</sup> | TAMPER-RTC     | -                  |

| PC14-<br>OSC32_IN <sup>(4)</sup>   | 3      | 3      | 8       | -     | I/O      | 1             | PC14 <sup>(3)</sup> | OSC32_IN       | -                  |

| PC15-<br>OSC32_OUT <sup>(4)</sup>  | 4      | 4      | 9       | -     | I/O      | 1             | PC15 <sup>(3)</sup> | OSC32_OUT      | -                  |

| V <sub>SS</sub> _5                 | -      | 1      | 10      | -     | S        | -             | V <sub>SS</sub> _5  | -              | -                  |

| V <sub>DD</sub> _5                 | -      | -      | 11      | -     | S        | -             | V <sub>DD</sub> _5  | -              | -                  |

| OSC_IN                             | 5      | 5      | 12      | 2     | I        | -             | OSC_IN              | -              | PD0 <sup>(5)</sup> |

| OSC_OUT                            | 6      | 6      | 13      | 3     | 0        | -             | OSC_OUT             | -              | PD1 <sup>(5)</sup> |

| NRST                               | 7      | 7      | 14      | 4     | I/O      | -             | NRST                | -              | -                  |

| PC0                                | -      | 8      | 15      | -     | I/O      | -             | PC0                 | ADC12_IN10     | -                  |

| PC1                                | -      | 9      | 16      | -     | I/O      | -             | PC1                 | ADC12_IN11     | -                  |

| PC2                                | -      | 10     | 17      | -     | I/O      | -             | PC2                 | ADC12_IN12     | -                  |

| PC3                                | -      | 11     | 18      | -     | I/O      | -             | PC3                 | ADC12_IN13     | -                  |

| V <sub>SSA</sub>                   | 8      | 12     | 19      | 5     | S        | -             | V <sub>SSA</sub>    | -              | -                  |

| V <sub>REF</sub> -                 | -      | -      | 20      | -     | S        | -             | V <sub>REF</sub> -  | -              | -                  |

| V <sub>REF+</sub>                  | -      | -      | 21      | -     | S        | -             | V <sub>REF</sub> +  | -              | -                  |

| V <sub>DDA</sub>                   | 9      | 13     | 22      | 6     | S        | -             | $V_{DDA}$           | -              | -                  |

|                    |        |        |         |       |          |               |                      | SEMICONDUCTOR                                                            |           |

|--------------------|--------|--------|---------|-------|----------|---------------|----------------------|--------------------------------------------------------------------------|-----------|

|                    |        | Pi     | ns      |       |          | (2)           | Main<br>Function (3) | Alternate fund                                                           | tions     |

| Pin Name           | LQFP48 | LQFP64 | LQFP100 | QFN36 | Type (1) | I/O level (2) | (after<br>reset)     | Default                                                                  | Remap     |

| PA0-WKUP           | 10     | 14     | 23      | 7     | I/O      | -             | PA0                  | WKUP/ USART2_CTS <sup>(6)</sup> / ADC12_IN0/ TMR2_CH1_ETR <sup>(6)</sup> | -         |

| PA1                | 11     | 15     | 24      | 8     | I/O      | -             | PA1                  | USART2_RTS <sup>(6)</sup> / ADC12_IN1/ TMR2_CH2 <sup>(6)</sup>           | -         |

| PA2                | 12     | 16     | 25      | 9     | I/O      | -             | PA2                  | USART2_TX <sup>(6)</sup> / ADC12_IN2/ TMR2_CH3 <sup>(6)</sup>            | -         |

| PA3                | 13     | 17     | 26      | 10    | I/O      | 1             | PA3                  | USART2_RX <sup>(6)</sup> /<br>ADC12_IN3/<br>TMR2_CH4 <sup>(6)</sup>      | -         |

| Vss_4              | -      | 18     | 27      | 1     | S        | -             | V <sub>SS</sub> _4   | -                                                                        | -         |

| V <sub>DD</sub> _4 | -      | 19     | 28      | -     | S        | -             | V <sub>DD</sub> _4   | -                                                                        | -         |

| PA4                | 14     | 20     | 29      | 11    | I/O      | -             | PA4                  | SPI1_NSS <sup>(6)</sup> /<br>USART2_CK <sup>(6)</sup> /<br>ADC12_IN4     | -         |

| PA5                | 15     | 21     | 30      | 12    | I/O      | -             | PA5                  | SPI1_SCK <sup>(6)</sup> /<br>ADC12_IN5                                   | -         |

| PA6                | 16     | 22     | 31      | 13    | I/O      |               | PA6                  | SPI1_MISO <sup>(6)</sup> / ADC12_IN6/ TMR3_CH1 <sup>(6)</sup>            | TMR1_BKIN |

| PA7                | 17     | 23     | 32      | 14    | I/O      |               | PA7                  | SPI1_MOSI <sup>(6)</sup> /<br>ADC12_IN7/<br>TMR3_CH2 <sup>(6)</sup>      | TMR1_CH1N |

| PC4                | -      | 24     | 33      | -     | I/O      | -             | PC4                  | ADC12_IN14                                                               | -         |

| PC5                | -      | 25     | 34      | -     | I/O      | -             | PC5                  | ADC12_IN15                                                               | -         |

| PB0                | 18     | 26     | 35      | 15    | I/O      | -             | PB0                  | ADC12_IN8/<br>TMR3_CH3 <sup>(6)</sup>                                    | TMR1_CH2N |

| PB1                | 19     | 27     | 36      | 16    | I/O      | -             | PB1                  | ADC12_IN9/<br>TMR3_CH4 <sup>(6)</sup>                                    | TMR1_CH3N |

|                    | ı      |        |         |       | ,        |               |                                 |                                                                                                 | SEMICONDUCTOR |

|--------------------|--------|--------|---------|-------|----------|---------------|---------------------------------|-------------------------------------------------------------------------------------------------|---------------|

|                    |        | Pi     | ns      |       |          | (2)           | Main<br>Function <sup>(3)</sup> | Alternate fund                                                                                  | tions         |

| Pin Name           | LQFP48 | LQFP64 | LQFP100 | QFN36 | Type (1) | I/O level (2) | (after<br>reset)                | Default                                                                                         | Remap         |

| PB2                | 20     | 28     | 37      | 17    | I/O      | FT            | PB2/BOOT                        | -                                                                                               | -             |

| PE7                | -      | -      | 38      | -     | I/O      | FT            | PE7                             | -                                                                                               | TMR1_ETR      |

| PE8                | -      | -      | 39      | -     | I/O      | FT            | PE8                             | -                                                                                               | TMR1_CH1N     |

| PE9                | -      | -      | 40      | -     | I/O      | FT            | PE9                             | -                                                                                               | TMR1_CH1      |

| PE10               | -      | -      | 41      | -     | I/O      | FT            | PE10                            | -                                                                                               | TMR1_CH2N     |

| PE11               | -      | -      | 42      | -     | I/O      | FT            | PE11                            | -                                                                                               | TMR1_CH2      |

| PE12               | -      | -      | 43      | -     | I/O      | FT            | PE12                            | -                                                                                               | TMR1_CH3N     |

| PE13               | -      | -      | 44      | -     | I/O      | FT            | PE13                            | -                                                                                               | TMR1_CH3      |

| PE14               | -      | -      | 45      | -     | I/O      | FT            | PE14                            | -                                                                                               | TMR1_CH4      |

| PE15               | -      | -      | 46      | -     | I/O      | FT            | PE15                            | -                                                                                               | TMR1_BKIN     |

| PB10               | 21     | 29     | 47      | -     | I/O      | FT            | PB10                            | I <sup>2</sup> C2_SCL/<br>I <sup>2</sup> C4_SCL/<br>USART3_TX <sup>(6)</sup>                    | TMR2_CH3      |

| PB11               | 22     | 30     | 48      | -     | I/O      | FT            | PB11                            | I <sup>2</sup> C2_SDA/<br>I <sup>2</sup> C4_SDA/<br>USART3_RX <sup>(6)</sup>                    | TMR2_CH4      |

| V <sub>SS</sub> _1 | 23     | 31     | 49      | 18    | S        | -             | V <sub>SS</sub> _1              | -                                                                                               | -             |

| V <sub>DD</sub> _1 | 24     | 32     | 50      | 19    | S        | -             | V <sub>DD</sub> _1              | -                                                                                               | -             |

| PB12               | 25     | 33     | 51      | 1     | I/O      | FT            | PB12                            | SPI2_NSS/<br>I <sup>2</sup> C2_SMBAI/<br>USART3_CK <sup>(6)</sup> /<br>TMR1_BKIN <sup>(6)</sup> |               |

| PB13               | 26     | 34     | 52      | -     | I/O      | FT            | PB13                            | SPI2_SCK/ USART3_CTS <sup>(6)</sup> / TMR1_CH1N <sup>(6)</sup> / QSPI_IO0                       |               |

| PB14               | 27     | 35     | 53      | -     | I/O      | FT            | PB14                            | SPI2_MISO/<br>USART3_RTS <sup>(6)</sup> /<br>TMR1_CH2N <sup>(6)</sup> /                         |               |

|          |        |        |         |       |          |               | T                               | SEMICONDUCTOR                                                                          |                         |  |

|----------|--------|--------|---------|-------|----------|---------------|---------------------------------|----------------------------------------------------------------------------------------|-------------------------|--|

|          |        | Pi     | ns      |       |          | (2)           | Main<br>Function <sup>(3)</sup> | Alternate func                                                                         | tions                   |  |

| Pin Name | LQFP48 | LQFP64 | LQFP100 | QFN36 | Type (1) | I/O level (2) | (after reset)                   | Default                                                                                | Remap                   |  |

|          |        |        |         |       |          |               |                                 | QSPI_IO1                                                                               |                         |  |

| PB15     | 28     | 36     | 54      | -     | I/O      | FT            | PB15                            | SPI2_MOSI/<br>TMR1_CH3N <sup>(6)</sup> /<br>QSPI_IO2                                   | -                       |  |

| PD8      | -      | ı      | 55      | -     | I/O      | FT            | PD8                             | QSPI_IO3                                                                               | USART3_TX               |  |

| PD9      | -      | -      | 56      | -     | I/O      | FT            | PD9                             | -                                                                                      | USART3_RX               |  |

| PD10     | -      | -      | 57      | -     | I/O      | FT            | PD10                            | QSPI_CLK                                                                               | USART3_CK               |  |

| PD11     | -      | -      | 58      | -     | I/O      | FT            | PD11                            | -                                                                                      | USART3_CTS              |  |

| PD12     | -      | -      | 59      | -     | I/O      | FT            | PD12                            | QSPI_SS_N                                                                              | TMR4_CH1/<br>USART3_RTS |  |

| PD13     | -      | -      | 60      | -     | I/O      | FT            | PD13                            | -                                                                                      | TMR4_CH2                |  |

| PD14     | -      | -      | 61      | -     | I/O      | FT            | PD14                            | -                                                                                      | TMR4_CH3                |  |

| PD15     | -      | -      | 62      | -     | I/O      | FT            | PD15                            | -                                                                                      | TMR4_CH4                |  |

| PC6      | -      | 37     | 63      | -     | I/O      | FT            | PC6                             | -                                                                                      | TMR3_CH1                |  |

| PC7      | -      | 38     | 64      | -     | I/O      | FT            | PC7                             | -                                                                                      | TMR3_CH2                |  |

| PC8      | -      | 39     | 65      | -     | I/O      | FT            | PC8                             | -                                                                                      | TMR3_CH3                |  |

| PC9      | -      | 40     | 66      | -     | I/O      | FT            | PC9                             | -                                                                                      | TMR3_CH4                |  |

| PA8      | 29     | 41     | 67      | 20    | I/O      | FT            | PA8                             | USART1_CK/<br>TMR1_CH1 <sup>(6)</sup> /<br>MCO                                         | -                       |  |

| PA9      | 30     | 42     | 68      | 21    | I/O      | FT            | PA9                             | USART1_TX <sup>(6)</sup> /<br>TMR1_CH2 <sup>(6)</sup>                                  | -                       |  |

| PA10     | 31     | 43     | 69      | 22    | I/O      | FT            | PA10                            | USART1_RX <sup>(6)</sup> /<br>TMR1_CH3 <sup>(6)</sup>                                  | -                       |  |

| PA11     | 32     | 44     | 70      | 23    | I/O      | FT            | PA11                            | USART1_CTS/USBD1D<br>M/<br>USBD2DM/ CAN_RX <sup>(6)</sup> /<br>TMR1_CH4 <sup>(6)</sup> | -                       |  |

| PA12     | 33     | 45     | 71      | 24    | I/O      | FT            | PA12                            | USART1_RTS/                                                                            | -                       |  |

|                    | _      |        |         |       |          |               | SEMICONDUCTOR        |                                                                  |                                           |

|--------------------|--------|--------|---------|-------|----------|---------------|----------------------|------------------------------------------------------------------|-------------------------------------------|

|                    |        | Pi     | ns      |       |          | 1 (2)         | Main<br>Function (3) | Alternate fund                                                   | tions                                     |

| Pin Name           | LQFP48 | LQFP64 | LQFP100 | QFN36 | Type (1) | I/O level (2) | (after reset)        | Default                                                          | Remap                                     |

|                    |        |        |         |       |          |               |                      | USBD1DP/USBD2DP/ CAN_TX <sup>(6)</sup> / TMR1_ETR <sup>(6)</sup> |                                           |

| PA13               | 34     | 46     | 72      | 25    | I/O      | FT            | JTMS/<br>SWDIO       | -                                                                | PA13                                      |

| Disconnected       | -      | -      | 73      | -     | -        | 1             | -                    | Disconnected                                                     | -                                         |

| V <sub>SS</sub> _2 | 35     | 47     | 74      | 26    | S        |               | V <sub>SS</sub> _2   | -                                                                | -                                         |

| V <sub>DD</sub> _2 | 36     | 48     | 75      | 27    | S        |               | V <sub>DD</sub> _2   | -                                                                | -                                         |

| PA14               | 37     | 49     | 76      | 28    | I/O      | FT            | JTCK/<br>SWCLK       | -                                                                | PA14                                      |

| PA15               | 38     | 50     | 77      | 29    | 1/0      | FT            | JTDI                 | -                                                                | TMR2_CH1_E<br>TR/PA15/<br>SPI1_NSS        |

| PC10               | -      | 51     | 78      | -     | I/O      | FT            | PC10                 | -                                                                | USART3_TX                                 |

| PC11               | -      | 52     | 79      | -     | I/O      | FT            | PC11                 | -                                                                | USART3_RX                                 |

| PC12               | -      | 53     | 80      | -     | I/O      | FT            | PC12                 | -                                                                | USART3_CK                                 |

| PD0                | -      | -      | 81      | 2     | I/O      | FT            | PD0                  | -                                                                | CAN_RX                                    |

| PD1                | -      | -      | 82      | 3     | I/O      | FT            | PD1                  | -                                                                | CAN_TX                                    |

| PD2                | -      | 54     | 83      | -     | I/O      | FT            | PD2                  | TMR3_ETR                                                         | -                                         |

| PD3                | -      | -      | 84      | -     | I/O      | FT            | PD3                  | -                                                                | USART2_CTS                                |

| PD4                | -      | -      | 85      | -     | I/O      | FT            | PD4                  | -                                                                | USART2_RTS                                |

| PD5                | -      | -      | 86      | -     | I/O      | FT            | PD5                  | -                                                                | USART2_TX                                 |

| PD6                | -      | -      | 87      | -     | I/O      | FT            | PD6                  | <u> </u>                                                         | USART2_RX                                 |

| PD7                | -      | -      | 88      | -     | I/O      | FT            | PD7                  | -                                                                | USART2_CK                                 |

| PB3                | 39     | 55     | 89      | 30    | I/O      | FT            | JTDO                 | -                                                                | PB3/<br>TRACESWO<br>TMR2_CH2/<br>SPI1_SCK |

|                    |        | Pi     | ns      |       |          | (2)           | Main<br>Function <sup>(3)</sup> | Alternate func                                               | tions                                                       |

|--------------------|--------|--------|---------|-------|----------|---------------|---------------------------------|--------------------------------------------------------------|-------------------------------------------------------------|

| Pin Name           | LQFP48 | LQFP64 | LQFP100 | QFN36 | Type (1) | I/O level (2) | (after<br>reset)                | Default                                                      | Remap                                                       |

|                    |        |        |         |       |          |               |                                 |                                                              | PB4/                                                        |