#### **MAX14945**

## 2.75kV<sub>RMS</sub> Isolated 500kbps Half-Duplex RS-485/ RS-422 Transceiver with ±30kV ESD Protection

#### **General Description**

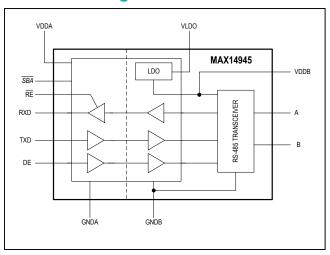

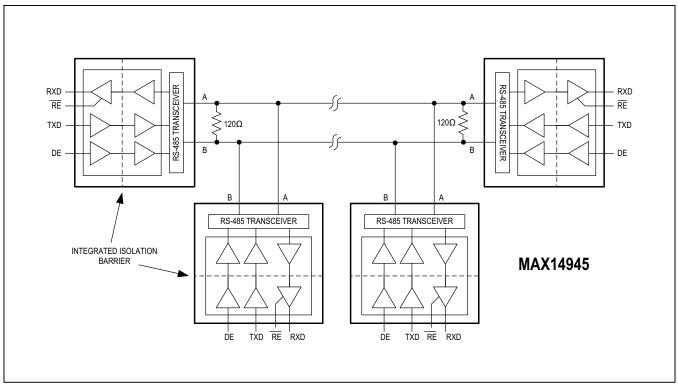

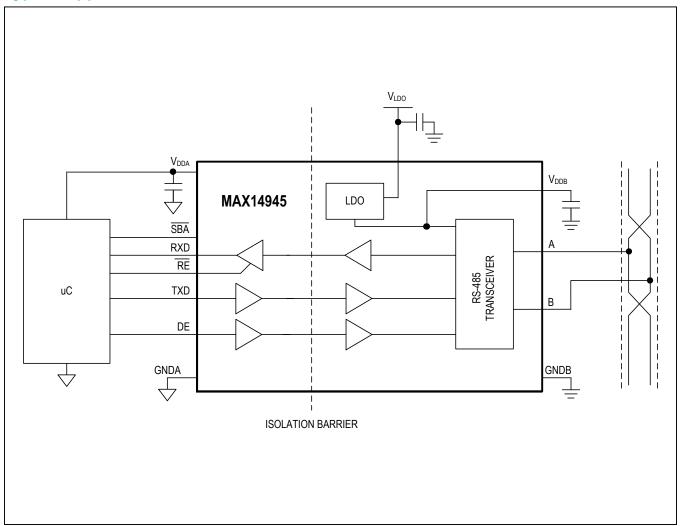

The MAX14945 isolated RS-485/RS-422 transceiver provides 2750V<sub>RMS</sub> (60s) of galvanic isolation between the cable side (RS-485/RS-422 driver/receiver side) and the UART side of the device. Isolation improves communication by breaking ground loops and reduces noise when there are large differences in ground potential between ports. Signals are passed across the isolation barrier through integrated high-voltage capacitors. This device allows for robust communication at any speed up to 500kbps.

The device includes one half-duplex drive/receive channel. The receiver is 1/8-unit load, allowing up to 256 transceivers on a common bus.

Integrated true fail-safe circuitry ensures a logic-high on the receiver output when inputs are shorted or open. Undervoltage lockout disables the driver when the cable side or UART side power supplies are below functional levels.

The driver outputs/receiver inputs are protected from ±30kV electrostatic discharge (ESD) to GNDB on the cable side, as specified by the Human Body Model (HBM).

The MAX14945 is available in a wide body 16-pin SO package and operates over the -40°C to +85°C temperature range.

#### **Benefits and Features**

- High-Performance Transceiver Enables Flexible Designs

- Integrated LDO for Cable-Side Power

- Compliant with RS-485 EIA/TIA-485 Standard

- 500kbps Maximum Data Rate

- · Allows Up to 256 Devices on the Bus

- Integrated Protection Ensures Robust Communication

- ±30kV ESD (HBM) on Driver Outputs/Receiver Inputs

- 2.75kV<sub>RMS</sub> Withstand-Isolation Voltage for 60s (V<sub>ISO</sub>)

- 630VPEAK Maximum Repetitive Peak-Isolation Voltage (V<sub>IORM</sub>)

- 445V<sub>RMS</sub> Maximum Working-Isolation Voltage (V<sub>IOWM</sub>)

- > 30 Years Lifetime at Rated Working Voltage

- Withstands ±10kV Surge per IEC 61000-4-5

- · Thermal Shutdown

#### **Safety Regulatory Approvals**

- UL According to UL1577

- cUL According to CSA Bulletin 5A

#### **Applications**

- Industrial Automation Equipment

- Programmable Logic Controllers

- HVAC

- Power Meters

### **Functional Diagram**

$\frac{\textit{Ordering Information/Selector Guide}}{\textit{sheet}} \textit{ appears at end of data}$

### **Absolute Maximum Ratings**

| V <sub>DDA</sub> to GNDA0.3V to                | +6V Continuous Power Dissipation (T <sub>A</sub> = +70°C) |

|------------------------------------------------|-----------------------------------------------------------|

| V <sub>DDB</sub> to GNDB0.3V to                | +6V 16-pin Wide SOIC                                      |

| V <sub>LDO</sub> to GNDB0.3V to +              |                                                           |

| TXD, DE, RE to GNDA0.3V to                     | +6V Operating Temperature Range40°C to +85°C              |

| SBA, RXD to GNDA0.3V to (V <sub>DDA</sub> + 0. | .3V) Junction Temperature+150°C                           |

| A, B to GNDB8V to +                            | 13V Storage Temperature Range65°C to +150°C               |

| Short Circuit Duration (RXD, SBA to GNDA,      | Lead Temperature (soldering, 10s)+300°C                   |

| A, B, V <sub>DDB</sub> to GNDB)Continu         |                                                           |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Package Thermal Characteristics (Note 1)**

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ )......71°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )......23°C/W

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

#### **DC Electrical Characteristics**

$(V_{DDA}-V_{GNDA}=1.71V\ to\ 5.5V,\ V_{DDB}-V_{GNDB}=4.5V\ to\ 5.5V,\ T_{A}=T_{MIN}\ to\ T_{MAX},\ unless otherwise\ noted.$  Typical values are at  $V_{DDA}-V_{GNDA}=3.3V,\ V_{DDB}-V_{GNDB}=5V,\ V_{GNDA}=V_{GNDB},\ and\ T_{A}=+25^{\circ}C.)\ (Notes\ 2,\ 3)$

| PARAMETER                      | SYMBOL               | CONDITIONS                                                                              | MIN  | TYP  | MAX  | UNITS |  |

|--------------------------------|----------------------|-----------------------------------------------------------------------------------------|------|------|------|-------|--|

| POWER                          |                      |                                                                                         |      |      |      |       |  |

| Supply Voltage                 | $V_{DDA}$            |                                                                                         | 1.71 |      | 5.5  | V     |  |

| Supply Voltage                 | $V_{DDB}$            |                                                                                         |      |      | 5.5  | V     |  |

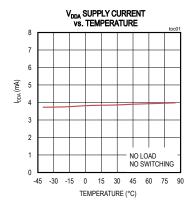

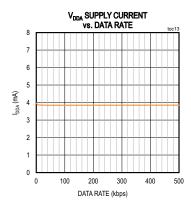

| Supply Current                 | I <sub>DDA</sub>     | V <sub>DDA</sub> = 5V, DE = high, $\overline{RE}$ = TXD = low, RXD unconnected, no load |      | 4    | 6.6  | mA    |  |

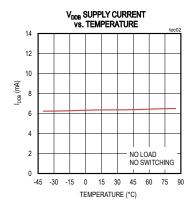

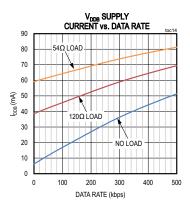

| опри оптен                     | I <sub>DDB</sub>     | DE = high, $\overline{RE}$ = TXD = low, RXD unconnected, no load, V <sub>DDB</sub> = 5V |      | 6.3  | 12.5 | III/A |  |

| Undervoltage-Lockout Threshold | $V_{UVLOA}$          | V <sub>DDA</sub> rising                                                                 | 1.50 | 1.58 | 1.65 | V     |  |

| Ondervokage-Lockout Threshold  | $V_{UVLOB}$          | V <sub>DDB</sub> rising                                                                 | 2.55 | 2.7  | 2.85 |       |  |

| Undervoltage-Lockout           | V <sub>UVHYSTA</sub> |                                                                                         |      | 50   |      | mV    |  |

| Threshold Hysteresis           | V <sub>UVHYSTB</sub> |                                                                                         |      | 200  |      |       |  |

| LDO                            |                      |                                                                                         |      |      |      |       |  |

| LDO Supply Voltage             | $V_{LDO}$            | Relative to GNDB, LDO is on (Note 4)                                                    | 4.68 |      | 14   | V     |  |

| LDO Supply Current             | I <sub>LDO</sub>     | DE = high, $\overline{RE}$ = TXD = low, no load, $V_{LDO}$ = 5.5V                       |      | 6.5  | 12.9 | mA    |  |

| LDO Output Voltage             | $V_{DDB}$            |                                                                                         | 4.5  | 5    | 5.5  | V     |  |

| LDO Current Limit              |                      |                                                                                         |      | 300  |      | mA    |  |

| Load Regulation                |                      | V <sub>LDO</sub> = 5.68V, I <sub>LOAD</sub> = 20mA to 40mA                              |      | 0.19 | 1.7  | mV/mA |  |

| Line Regulation                |                      | V <sub>LDO</sub> = 5.68V to 14V, I <sub>LOAD</sub> = 20mA                               |      | 0.12 | 1.8  | mV/V  |  |

# **DC Electrical Characteristics (continued)**

$(V_{DDA}-V_{GNDA}=1.71 V\ to\ 5.5 V,\ V_{DDB}-V_{GNDB}=4.5 V\ to\ 5.5 V,\ T_{A}=T_{MIN}\ to\ T_{MAX},\ unless\ otherwise\ noted.$  Typical values are at  $V_{DDA}-V_{GNDA}=3.3 V,\ V_{DDB}-V_{GNDB}=5 V,\ V_{GNDA}=V_{GNDB},\ and\ T_{A}=+25^{\circ}C.)$  (Notes 2, 3)

| PARAMETER                                                    | SYMBOL             | CONE                                            | DITIONS                             | MIN                        | TYP                 | MAX  | UNITS |  |

|--------------------------------------------------------------|--------------------|-------------------------------------------------|-------------------------------------|----------------------------|---------------------|------|-------|--|

| Dropout Voltage                                              |                    | V <sub>LDO</sub> = 4.68V, I <sub>DI</sub>       | DB = -120mA                         |                            | 100                 | 180  | mV    |  |

| Load Capacitance                                             |                    | Nominal value                                   |                                     | 1                          |                     | 10   | μF    |  |

| LOGIC INTERFACE (TXD, RXD                                    | , DE, RE, SBA)     |                                                 |                                     | 1                          |                     |      |       |  |

| Input High Voltage                                           | VIH                | RE, TXD, DE to                                  | 2.25V ≤ V <sub>DDA</sub> ≤ 5.5V     | 0.7 x<br>V <sub>DDA</sub>  |                     |      | · V   |  |

| input riigir voitage                                         | VIН                | GNDA                                            | 1.71V ≤ V <sub>DDA</sub> ≤<br>1.89V | 0.78 x<br>V <sub>DDA</sub> |                     |      | v     |  |

| Input Low Voltage                                            | V <sub>IL</sub>    | RE, TXD, DE to                                  | 2.25V ≤ V <sub>DDA</sub> ≤ 5.5V     |                            |                     | 0.8  | V     |  |

| input Low Voltage                                            | ۷IL                | GNDA                                            | 1.71V ≤ V <sub>DDA</sub> ≤ 1.89V    |                            |                     | 0.6  | V     |  |

| Input Hysteresis                                             | VHYS               | RE, TXD, DE to G                                | NDA                                 |                            | 220                 |      | mV    |  |

| Input Capacitance                                            | C <sub>IN</sub>    | RE, TXD, DE, f = 1                              | 1MHz                                |                            | 2                   |      | pF    |  |

| Input Pullup Current                                         | l <sub>PU</sub>    | TXD                                             |                                     | -10                        | -4.5                | -1.5 | μA    |  |

| Input Pulldown Current                                       | $I_{PD}$           | DE, RE                                          |                                     | 1.5                        | 4.5                 | 10   | μA    |  |

| SBA Pullup Resistance                                        | R <sub>SBA</sub>   |                                                 |                                     | 3                          | 5                   | 8    | kΩ    |  |

| Output Voltage High                                          | Voн                | RXD to GNDA, IO                                 | UT = -4mA                           | V <sub>DDA</sub><br>-0.4   |                     |      | V     |  |

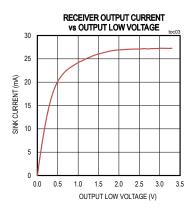

|                                                              |                    | RXD to GNDA, IO                                 | UT = 4mA                            |                            |                     | 0.40 | 40    |  |

| Output Voltage Low                                           | V <sub>OL</sub>    | SBA to GNDA, IOI                                | <sub>JT</sub> = 4mA                 |                            |                     | 0.45 | V     |  |

| Short-Circuit Output Pullup<br>Current                       | <sup>I</sup> SH_PU | 0V ≤ V <sub>RXD</sub> ≤ V <sub>DD</sub>         | OA, RE = low                        | -42                        |                     |      | mA    |  |

| 0, 10, 10, 10, 10, 11,                                       |                    | 0V ≤ V <sub>RXD</sub> ≤ V <sub>DD</sub>         | $_{OA}$ , $\overline{RE}$ = low     |                            |                     | +40  |       |  |

| Short-Circuit Output Pulldown<br>Current                     | <sup>I</sup> SH_PD | 0V ≤ V <del>SBA</del> ≤ VDD<br>ered and working | A, side B is pow-                   |                            |                     | +60  | mA    |  |

| Three-State Output Current                                   | loz                | 0V ≤ V <sub>RXD</sub> ≤ V <sub>DD</sub>         | A, RE = high                        | -1                         |                     | +1   | μA    |  |

| DRIVER                                                       | <u> </u>           | I.                                              |                                     | l                          |                     |      | l     |  |

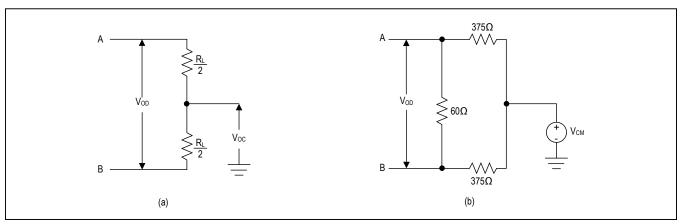

|                                                              |                    | $R_L$ = 54Ω, TXD = 1<br>Figure 1a               | high or low,                        | 2                          |                     |      |       |  |

| Differential Driver Output                                   | IVODI              | $R_L$ = 100Ω, TXD = Figure 1a                   | high or low,                        | 3                          |                     |      | V     |  |

|                                                              |                    | -7V ≤ V <sub>CM</sub> ≤ +12\                    | /, Figure 1b                        | 1.5                        |                     | 5    |       |  |

| Change in Magnitude of<br>Differential Driver Output Voltage | ΔV <sub>OD</sub>   | $R_L = 54\Omega \text{ (Note 5)}$               |                                     |                            |                     | 0.2  | V     |  |

| Driver Common Mode Output<br>Voltage                         | Voc                | R <sub>L</sub> = 54Ω                            |                                     |                            | V <sub>DDB</sub> /2 | 3    | V     |  |

## **DC Electrical Characteristics (continued)**

$(V_{DDA}-V_{GNDA}=1.71 V\ to\ 5.5 V,\ V_{DDB}-V_{GNDB}=4.5 V\ to\ 5.5 V,\ T_{A}=T_{MIN}\ to\ T_{MAX},\ unless\ otherwise\ noted.$  Typical values are at  $V_{DDA}-V_{GNDA}=3.3 V,\ V_{DDB}-V_{GNDB}=5 V,\ V_{GNDA}=V_{GNDB},\ and\ T_{A}=+25^{\circ}C.)\ (Notes\ 2,\ 3)$

| PARAMETER                                  | SYMBOL            | CONE                                                           | DITIONS                       | MIN  | TYP  | MAX  | UNITS |  |

|--------------------------------------------|-------------------|----------------------------------------------------------------|-------------------------------|------|------|------|-------|--|

| Change in Magnitude of Common-Mode Voltage | ΔV <sub>OC</sub>  | $R_L$ = 54Ω (Note 5)                                           | R <sub>L</sub> = 54Ω (Note 5) |      |      | 0.2  | V     |  |

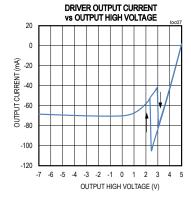

| Driver Short-Circuit Output                | losp              | GNDB≤V <sub>OUT</sub> ≤+1                                      | 2V, output low (Note 6)       | +40  |      | +250 | mA    |  |

| Current                                    |                   | -7V ≤ V <sub>OUT</sub> ≤ V <sub>DD</sub>                       | B, output high (Note 6)       | -250 |      | -40  |       |  |

| Driver Short-Circuit Foldback              | lospe             | (V <sub>DDB</sub> – 1V) ≤ V <sub>C</sub><br>output low (Note 6 |                               | +20  |      |      | mA    |  |

| Output Current                             | OODI              | -7V ≤ V <sub>OUT</sub> ≤ +1V,                                  | output high (Note 6)          |      |      | -20  |       |  |

| RECEIVER                                   |                   |                                                                |                               |      |      |      |       |  |

|                                            |                   | DE = low, V <sub>DDB</sub>                                     | V <sub>IN</sub> = +12V        |      |      | +125 |       |  |

| Input Current (A and B)                    | IA, IB            | = GNDB or 5.5V V <sub>IN</sub> = -7V                           |                               | -100 |      |      | μA    |  |

| Receiver Differential Threshold<br>Voltage | V <sub>TH</sub>   | -7V ≤ V <sub>CM</sub> ≤ +12V                                   | ,                             | -200 | -125 | -50  | mV    |  |

| Receiver Input Hysteresis                  | $\Delta V_{TH}$   | V <sub>CM</sub> = 0V                                           |                               |      | 15   |      | mV    |  |

| Receiver Input Resistance                  | R <sub>IN</sub>   | -7V ≤ V <sub>CM</sub> ≤ +12V                                   | /, DE = low                   | 96   |      |      | kΩ    |  |

| PROTECTION                                 |                   |                                                                |                               |      |      |      |       |  |

| Thermal-Shutdown Threshold                 | T <sub>SHDN</sub> | Temperature Risin                                              | g                             |      | +160 |      | °C    |  |

| Thermal-Shutdown Hysteresis                | T <sub>HYST</sub> |                                                                |                               |      | 15   |      | °C    |  |

|                                            |                   | Human Body Mode                                                | el                            |      | ±30  |      |       |  |

| ESD Protection (A and B Pins to GNDB)      |                   | IEC 61000-4-2 Air                                              | Gap Discharge                 |      | ±15  |      | kV    |  |

| (A Cana D I into to Crabb)                 |                   | IEC 61000-4-2 Contact Discharge                                |                               |      | ±10  |      |       |  |

| ESD Protection (All Other Pins)            |                   | Human Body Mode                                                | el                            |      | ±4   |      | kV    |  |

#### **Switching Electrical Characteristics**

$(V_{DDA} - V_{GNDA} = 1.71V \text{ to } 5.5V, V_{DDB} - V_{GNDB} = 4.5V \text{ to } 5.5V, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } V_{DDA} - V_{GNDA} = 3.3V, V_{DDB} - V_{GNDB} = 5V, V_{GNDA} = V_{GNDB}, \text{ and } T_A = +25^{\circ}\text{C.}) \text{ (Note 7)}$

| PARAMETER                                       | SYMBOL                               | CONDITIONS                                                | MIN | TYP | MAX  | UNITS |

|-------------------------------------------------|--------------------------------------|-----------------------------------------------------------|-----|-----|------|-------|

| DYNAMIC                                         |                                      |                                                           |     |     |      |       |

| Common Mode Transient<br>Immunity               | СМТІ                                 | (Note 8)                                                  |     | 35  |      | kV/μs |

| Glitch Rejection                                |                                      | TXD, DE, RXD                                              | 10  | 17  | 29   | ns    |

| DRIVER                                          |                                      |                                                           |     |     |      |       |

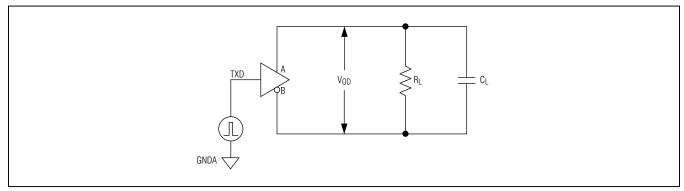

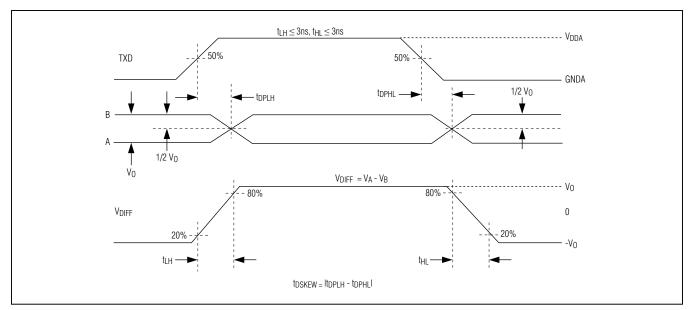

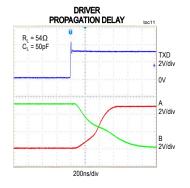

| Driver Propagation Delay                        | <sup>t</sup> DPLH, <sup>t</sup> DPHL | $R_L$ = 54 $\Omega$ , $C_L$ = 50pF, Figure 2 and Figure 3 |     |     | 1040 | ns    |

| Differential Driver Output Skew   tDPLH - tDPHL | <sup>t</sup> DSKEW                   | $R_L$ = 54 $\Omega$ , $C_L$ = 50pF, Figure 2 and Figure 3 |     |     | 144  | ns    |

| Driver Differential Output Rise or Fall Time    | t <sub>LH</sub> , t <sub>HL</sub>    | $R_L$ = 54 $\Omega$ , $C_L$ = 50pF, Figure 2 and Figure 3 |     |     | 900  | ns    |

| Maximum Data Rate                               | DR <sub>MAX</sub>                    |                                                           | 500 |     |      | kbps  |

| Driver Enable to Output High                    | <sup>t</sup> DZH                     | $R_L$ = 500Ω, $C_L$ = 50pF, Figure 4                      |     |     | 2540 | ns    |

| Driver Enable to Output Low                     | t <sub>DZL</sub>                     | $R_L = 500\Omega$ , $C_L = 50pF$ , Figure 5               |     |     | 2540 | ns    |

| Driver Disable Time from Low                    | t <sub>DLZ</sub>                     | $R_L$ = 500Ω, $C_L$ = 50pF, Figure 5                      |     |     | 140  | ns    |

| Driver Disable Time from High                   | t <sub>DHZ</sub>                     | $R_L$ = 500Ω, $C_L$ = 50pF, Figure 4                      |     |     | 140  | ns    |

| RECEIVER                                        |                                      |                                                           |     |     |      |       |

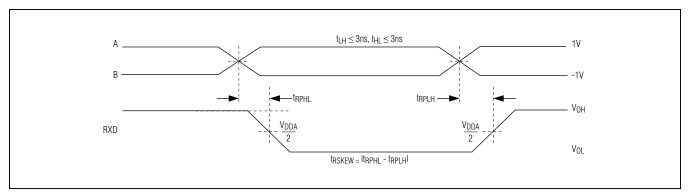

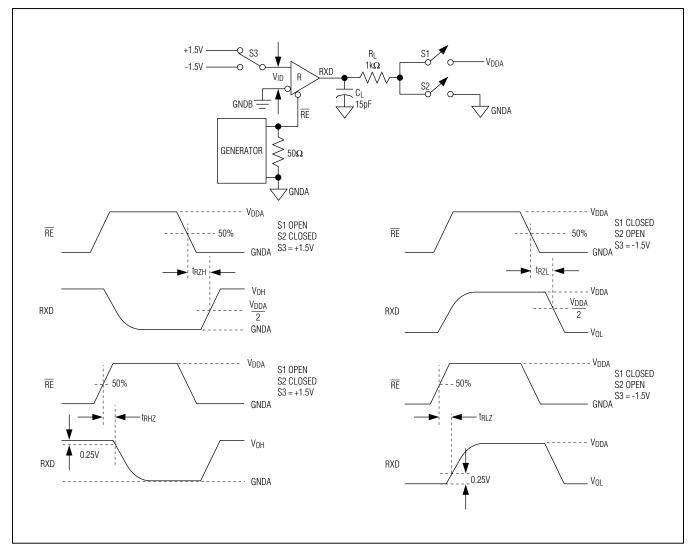

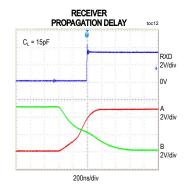

| Receiver Propagation Delay                      | <sup>t</sup> RPLH, <sup>t</sup> RPHL | C <sub>L</sub> = 15pF, Figure 6 and 7 (Note 9)            |     |     | 240  | ns    |

| Receiver Output Skew<br> tRPLH - tRPHL          | tRSKEW                               | C <sub>L</sub> = 15pF, Figure 6 and 7<br>(Note 9)         |     |     | 34   | ns    |

| Maximum Data Rate                               | DR <sub>MAX</sub>                    |                                                           | 500 |     |      | kbps  |

| Receiver Enable to Output High                  | <sup>t</sup> RZH                     | $R_L = 1k\Omega$ , $C_L = 15pF$ , S2 closed, Figure 8     |     |     | 20   | ns    |

| Receiver Enable to Output Low                   | <sup>t</sup> RZL                     | $R_L$ = 1k $\Omega$ , $C_L$ = 15pF, S1 closed, Figure 8   |     |     | 30   | ns    |

| Receiver Disable Time From Low                  | t <sub>RLZ</sub>                     | $R_L$ = 1k $\Omega$ , $C_L$ = 15pF, S1 closed, Figure 8   |     |     | 20   | ns    |

| Receiver Disable Time From High                 | <sup>t</sup> RHZ                     | $R_L$ = 1k $\Omega$ , $C_L$ = 15pF, S2 closed, Figure 8   |     |     | 20   | ns    |

- Note 2: All devices are 100% production tested at  $T_A = +25$ °C. Specifications over temperature are guaranteed by design.

- **Note 3:** All currents into the device are positive. All currents out of the device are negative. All voltages are referenced to their respective ground (GNDA or GNDB), unless otherwise noted.

- Note 4: V<sub>LDO</sub> max indicates voltage capability of the circuit. Power dissipation requirements may limit V<sub>LDO</sub> max to a lower value.

- **Note 5:**  $\Delta V_{OD}$  and  $\Delta V_{OC}$  are the changes in  $V_{OD}$  and  $V_{OC}$ , respectively, when the TXD input changes state.

- Note 6: The short circuit output current applies to the peak current just prior to foldback current limiting.

- Note 7: Not production tested. Guaranteed by design.

- **Note 8:** CMTI is the maximum sustainable common-mode voltage slew rate while maintaining the correct output states. CMTI applies to both rising and falling common-mode voltage edges. Tested with the transient generator connected between GNDA and GNDB.

- Note 9: Capacitive load includes test probe and fixture capacitance.

### **Insulation Characteristics**

| PARAMETER                                 | SYMBOL          | CONDITIONS                                                                 | VALUE     | UNITS            |

|-------------------------------------------|-----------------|----------------------------------------------------------------------------|-----------|------------------|

| Partial Discharge Test Voltage            | V <sub>PR</sub> | Method B1 = V <sub>IORM</sub> x 1.875<br>(t = 1s, partial discharge < 5pC) | 1182      | V <sub>P</sub>   |

| Maximum Repetitive Peak Withstand Voltage | VIORM           | Peak voltage for 50 yrs, min (Note 7)                                      | 630       | V <sub>P</sub>   |

| Maximum Working Isolation Voltage         | VIOWM           | (Note 7)                                                                   | 445       | V <sub>RMS</sub> |

| Maximum Transient Isolation Voltage       | VIOTM           | t = 1s                                                                     | 4600      | VP               |

| Maximum Withstand Isolation Voltage       | VISO            | t = 60s, f = 60Hz (Note 7, 8)                                              | 2750      | VRMS             |

| Maximum Surge Isolation Voltage           | VISOM           | IEC 61000-4-5, 1.2/50μs                                                    | 10        | kV               |

| Insulation Resistance                     | RS              | T <sub>A</sub> = +150°C, V <sub>IO</sub> = 500V                            | >109      | Ω                |

| Barrier Capacitance Input to Output       | CIO             |                                                                            | 2         | pF               |

| Creepage Distance                         | CPG             | Wide SO                                                                    | 8         | mm               |

| Clearance Distance                        | CLR             | Wide SO                                                                    | 8         | mm               |

| Internal Clearance                        |                 | Distance through insulation                                                | 0.015     | mm               |

| Comparitive Tracking Resistance Index     | CTI             | Material Group II (IEC 60112)                                              | 575       |                  |

| Climatic Category                         |                 |                                                                            | 40/125/21 |                  |

| Pollution Degree (DIN VDE 0110, Table 1)  |                 |                                                                            | 2         |                  |

$\label{eq:Note 10: V_IORM, V_IOWM, and V_ISO} \ \text{are defined by the IEC 60747-5-5 standard.}$   $\label{eq:Note 11: Product is qualified at V_ISO} \ \text{for 60 seconds. 100\% production tested at 120\% of V_ISO} \ \text{for 1 second.}$

## **Safety Regulatory Approvals**

| UL                                                                          |

|-----------------------------------------------------------------------------|

| The MAX14945 is certified under UL1577. For more details, see File E351759. |

| Rate up to 2750V <sub>RMS</sub> isolation voltage for basic insulation.     |

| olli.                                                                       |

The MAX14945 is certified under UL1577. For more details, see File E351759. Rate up to 2750V<sub>RMS</sub> isolation voltage for basic insulation.

Figure 1. Driver DC Test Load

Figure 2. Driver Timing Test Circuit

Figure 3. Driver Propagation Delays

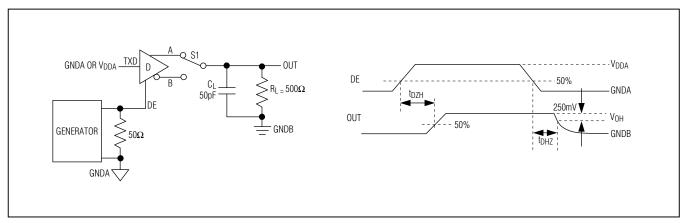

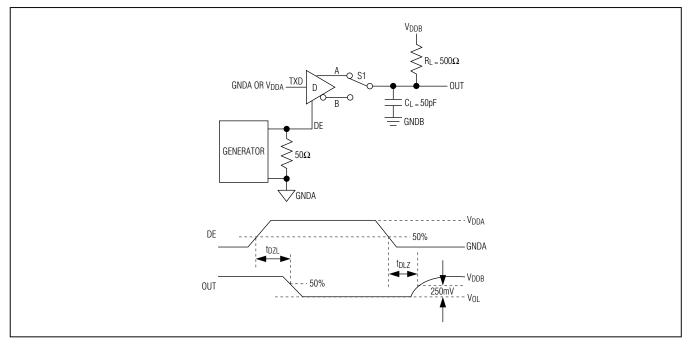

Figure 4. Driver Enable and Disable Times ( $t_{DHZ}$ ,  $t_{DZH}$ )

Figure 5. Driver Enable and Disable Times ( $t_{DZL}$ ,  $t_{DLZ}$ )

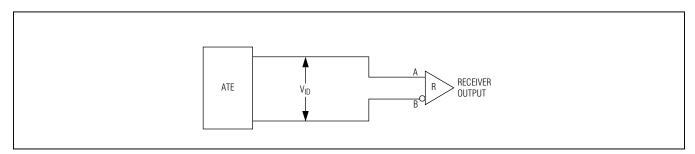

Figure 6. Receiver Propagation Delay Test Circuit

Figure 7. Receiver Propagation Delays

Figure 8. Receiver Enable and Disable Times

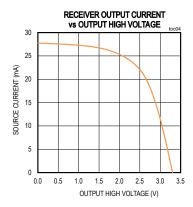

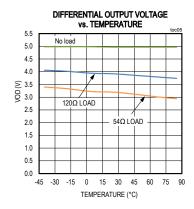

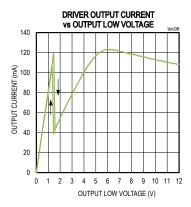

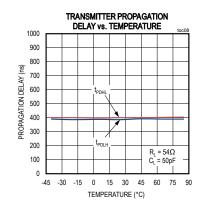

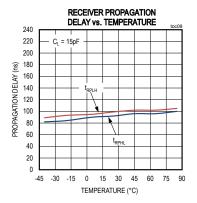

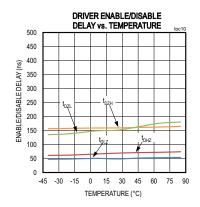

## **Typical Operating Characteristics**

(VDDA - VGNDA = 3.3V, VDDB - VGNDB = 5V, VGNDA = VGNDB, and TA = +25°C, unless otherwise noted.)

## **Typical Operating Characteristics (continued)**

(VDDA – VGNDA = 3.3V, VDDB – VGNDB = 5V, VGNDA = VGNDB, and TA = +25°C, unless otherwise noted.)

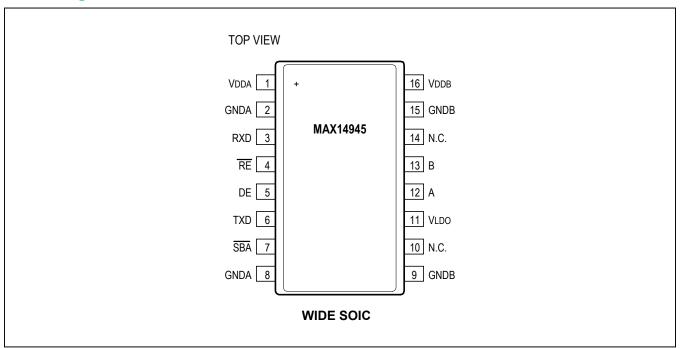

# **Pin Configuration**

# **Pin Description**

| PIN  | NAME             | REFERENCE | FUNCTION                                                                                                                                                                                                                                                                                           |

|------|------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | V <sub>DDA</sub> | GNDA      | UART/Logic-Side Power Input. Bypass $V_{\mbox{DDA}}$ to GNDA with both 0.1µF and 1µF capacitors as close to the device as possible.                                                                                                                                                                |

| 2, 8 | GNDA             | _         | UART/Logic-Side Ground. GNDA is the ground reference for digital signals.                                                                                                                                                                                                                          |

| 3    | RXD              | GNDA      | Receiver Data Output. Drive $\overline{RE}$ low to enable RXD. With $\overline{RE}$ low, RXD is high when $(V_A - V_B) > -50 \text{mV}$ and is low when $(V_A - V_B) < -200 \text{mV}$ . RXD is high when $V_{DDB}$ is less than $V_{UVLOB}$ . RXD is high impedance when $\overline{RE}$ is high. |

| 4    | RE               | GNDA      | Receiver Output Enable. Drive $\overline{RE}$ low or connect to GNDA to enable RXD. Drive $\overline{RE}$ high to disable RXD. RXD is high-impedance when $\overline{RE}$ is high. $\overline{RE}$ has an internal 4.5μA pulldown to GNDA.                                                         |

# **Pin Description (continued)**

| PIN    | NAME             | REFERENCE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                   |

|--------|------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5      | DE               | GNDA      | Driver Output Enable. Drive DE high to enable bus driver outputs A and B. Drive DE low or connect to GNDA to disable A and B. A and B are high impedance when DE is low. DE has an internal 4.5µA pulldown to GNDA.                                                                                                                                                                        |

| 6      | TXD              | GNDA      | Driver Input. With DE high, a low on TXD forces the noninverting output (A) low and the inverting output (B) high. Similarly, a high on TXD forces the noninverting output high and the inverting output low. TXD has an internal 4.5µA pullup to V <sub>DDA</sub> .                                                                                                                       |

| 7      | SBA              | GNDA      | Side B Active Indicator Output. $\overline{SBA}$ asserts low when side B is powered and working. $\overline{SBA}$ has an internal $5k\Omega$ pullup resistor to $V_{DDA}$ .                                                                                                                                                                                                                |

| 9, 15  | GNDB             | _         | Cable-Side Ground. GNDB is the ground reference for the internal LDO and the RS-485/RS-422 bus signals.                                                                                                                                                                                                                                                                                    |

| 10, 14 | N.C.             | _         | No Connection. Not internally connected.                                                                                                                                                                                                                                                                                                                                                   |

| 11     | V <sub>LDO</sub> | GNDB      | LDO Power Input. Connect a minimum voltage of 4.68V to $V_{LDO}$ to power the cable-side of the transceiver. Bypass $V_{LDO}$ to GNDB with both 0.1 $\mu$ F and 1 $\mu$ F capacitors as close to the device as possible. To disable the internal LDO, leave $V_{LDO}$ unconnected or connect to GNDB.                                                                                      |

| 12     | Α                | GNDB      | Noninverting Receiver Input and Noninverting Driver Output                                                                                                                                                                                                                                                                                                                                 |

| 13     | В                | GNDB      | Inverting Receiver Input and Inverting Driver Output                                                                                                                                                                                                                                                                                                                                       |

| 16     | V <sub>DDB</sub> | GNDB      | Cable-Side Power Input/Isolated LDO Power Output. Bypass $V_{DDB}$ to GNDB with both 0.1µF and 1µF capacitor as close as possible to the device. $V_{DDB}$ is the output of the internal LDO when power is applied to $V_{LDO}$ . When the internal LDO is not used ( $V_{LDO}$ is unconnected or connected to GNDB), $V_{DDB}$ is the positive supply input for the cable-side of the IC. |

### **Function Tables**

| TRANSMITTING         |                      |     |      |        |        |  |

|----------------------|----------------------|-----|------|--------|--------|--|

|                      | INP                  | OUT | PUTS |        |        |  |

| V <sub>DDA</sub>     | V <sub>DDB</sub>     | DE  | TXD  | Α      | В      |  |

| ≥ V <sub>UVLOA</sub> | ≥ V <sub>UVLOB</sub> | 1   | 1    | 1      | 0      |  |

| ≥ V <sub>UVLOA</sub> | ≥ V <sub>UVLOB</sub> | 1   | 0    | 0      | 1      |  |

| ≥ V <sub>UVLOA</sub> | ≥ V <sub>UVLOB</sub> | 0   | X    | High-Z | High-Z |  |

| < V <sub>UVLOA</sub> | ≥ V <sub>UVLOB</sub> | Х   | X    | High-Z | High-Z |  |

| ≥ V <sub>UVLOA</sub> | < V <sub>UVLOB</sub> | Х   | Х    | High-Z | High-Z |  |

| < V <sub>UVLOA</sub> | < V <sub>UVLOB</sub> | Х   | Х    | High-Z | High-Z |  |

<sup>\*</sup>Note: Drive DE low to disable the transmitter outputs. Drive DE high to enable the transmitter outputs. DE has an internal pull-down to GNDA.

X = Don't care

|                      | RECEIVING            |     |                                    |         |  |  |  |

|----------------------|----------------------|-----|------------------------------------|---------|--|--|--|

|                      | INP                  | UTS |                                    | OUTPUTS |  |  |  |

| V <sub>DDA</sub>     | V <sub>DDB</sub>     | RE  | (V <sub>A</sub> - V <sub>B</sub> ) | RXD     |  |  |  |

| ≥ V <sub>UVLOA</sub> | ≥ V <sub>UVLOB</sub> | 0   | > -50mV                            | 1       |  |  |  |

| ≥ V <sub>UVLOA</sub> | ≥ V <sub>UVLOB</sub> | 0   | < -200mV                           | 0       |  |  |  |

| ≥ V <sub>UVLOA</sub> | ≥ V <sub>UVLOB</sub> | 0   | Open/Short                         | 1       |  |  |  |

| ≥ V <sub>UVLOA</sub> | ≥ V <sub>UVLOB</sub> | 1   | Х                                  | High-Z  |  |  |  |

| < V <sub>UVLOA</sub> | ≥ V <sub>UVLOB</sub> | Х   | Х                                  | High-Z  |  |  |  |

| ≥ V <sub>UVLOA</sub> | < V <sub>UVLOB</sub> | 0   | X                                  | 1       |  |  |  |

| < V <sub>UVLOA</sub> | < V <sub>UVLOB</sub> | Х   | Х                                  | High-Z  |  |  |  |

<sup>\*</sup>Note: Drive  $\overline{RE}$  high to disable the receiver output. Drive  $\overline{RE}$  low to enable to receiver output.  $\overline{RE}$  has an internal pull-down to GNDA.

X = Don't care

| SBA                  |                      |      |  |  |  |

|----------------------|----------------------|------|--|--|--|

| V <sub>DDA</sub>     | $V_{DDB}$            | SBA  |  |  |  |

| < V <sub>UVLOA</sub> | < V <sub>UVLOB</sub> | High |  |  |  |

| < V <sub>UVLOA</sub> | ≥ V <sub>UVLOB</sub> | High |  |  |  |

| ≥ V <sub>UVLOA</sub> | < V <sub>UVLOB</sub> | High |  |  |  |

| ≥ V <sub>UVLOA</sub> | ≥V <sub>UVLOB</sub>  | Low  |  |  |  |

#### **Detailed Description**

The MAX14945 isolated RS-485/RS-422 transceiver provides  $2750V_{RMS}$  (60s) of galvanic isolation between the RS-485/RS-422 cable side of the transceiver and the UART side. This device allows up to 500kbps communication across an isolation barrier when a large potential exists between grounds on each side of the barrier.

#### Isolation

Data isolation is achieved using integrated capacitive isolation that allows data transmission between the UART-side and the cabel-side of the transceiver.

#### **Integrated LDO**

The device includes an internal low-dropout regulator with a set 5V (typ) output that is used to power the cable-side of the IC. The output of the LDO is  $V_{DDB}$ . The LDO has a 300mA (typ) current limit. If the LDO is unused, connect  $V_{LDO}$  to GNDB and apply +5V directly to  $V_{DDB}$ .

### True Fail-Safe

The device guarantees a logic-high on the receiver output when the receiver inputs are shorted or open, or when connected to a terminated transmission line with all drivers disabled. The receiver threshold is fixed between -50mV and -200mV. If the differential receiver input voltage ( $V_A - V_B$ ) is greater than or equal to -50mV, RXD is logic-high. In the case of a terminated bus with all transmitters disabled, the receiver's differential input voltage is pulled to zero by the termination resistors. Due to the receiver thresholds of the MAX14945, this results in a logic-high at RXD.

#### **Driver Output Protection**

Two mechanisms prevent excessive output current and power dissipation caused by faults or bus contention. The first, a foldback current limit on the output stage, provides immediate protection against short circuits over the entire common-mode voltage range. The second, a thermal-shutdown circuit, forces the driver outputs into a high-impedance state if the die temperature exceeds +160°C (typ).

#### **Thermal Shutdown**

The device is protected from overtemperature damage by integrated thermal shutdown circuitry. When the junction temperature (T<sub>J</sub>) exceeds +160°C (typ), the driver outputs go high-impedance. The device resumes normal operation when T<sub>J</sub> falls below +145°C (typ).

### **Applications Information**

#### 256 Transceivers on the Bus

The standard RS-485 receiver input impedance is one unit load. A standard driver can drive up to 32 unit-loads. The MAX14945 transceiver has a 1/8-unit load receiver, which allows up to 256 transceivers, connected in parallel, on one communication line. Connect any combination of these devices, and/or other RS-485 devices, for a maximum of 32 unit-loads to the line.

#### Typical Application

The MAX14945 transceiver is designed for bidirectional data communications on multipoint bus transmission lines. Figure 9 shows a typical network application circuit. To minimize reflections, the bus should be terminated at both ends in its characteristics impedance, and stub lengths off the main line should be kept as short as possible.

Figure 9. Typical Isolated Half-Duplex RS-485 Application

#### **Layout Considerations**

It is recommended to design an isolation, or keep-out channel underneath the isolator that is free from ground and signal planes. Any galvanic or metallic connection between the cable-side and UART-side defeats the isolation.

Ensure that the decoupling capacitors between  $V_{DDA}$  and GNDA and between  $V_{LDO}$ ,  $V_{DDB}$ , and GNDB are located as close as possible to the IC to minimize inductance.

Route important signal lines close to the ground plane to minimize possible external influences. On the cable-side of the device, it is good practice to have the bus connectors and termination resistor as close as possible to the A and B pins.

#### **Extended ESD Protection**

ESD protection structures are incorporated on all pins to protect against electrostatic discharge encountered during handling and assembly. The driver outputs and receiver inputs of the MAX14945 have extra protection against static electricity to both the UART-side and cableside ground references. The ESD structures withstand high-ESD events during normal operation and when powered down. After an ESD event, the devices keep working without latch-up or damage.

Bypass  $V_{DDA}$  to GNDA and bypass  $V_{DDB}$  and  $V_{LDO}$  to GNDB with 0.1µF and 1µF capacitors to ensure maximum ESD protection.

ESD protection can be tested in various ways. The transmitter outputs and receiver inputs of the MAX14945 are characterized for protection to the cable-side ground (GNDB) to the following limits:

- ±30kV HBM

- ±15kV using the Air-Gap Discharge method specified in IEC 61000-4-2

- ±10kV using the Contact Discharge method specified in IEC 61000-4-2

#### **ESD Test Conditions**

ESD performance depends on a variety of conditions. Contact Maxim for a reliability report that documents test setup, test methodology, and test results.

#### **Human Body Model (HBM)**

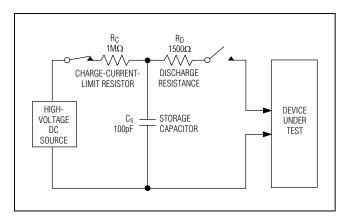

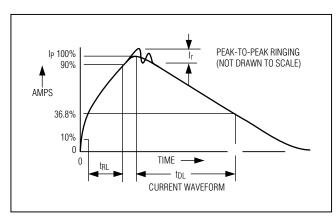

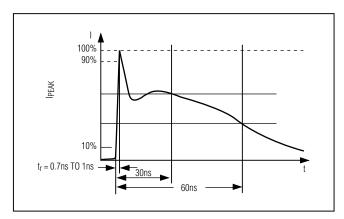

<u>Figure 10</u> shows the HBM test model, while <u>Figure 11</u> shows the current waveform it generates when discharged in a low-impedance state. This model consists of a 100pF capacitor charged to the ESD voltage of interest, which is then discharged into the test device through a 1.5kΩ resistor.

#### IEC 61000-4-2

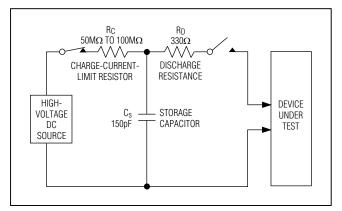

The IEC 61000-4-2 standard covers ESD testing and performance of finished equipment. However, it does not specifically refer to integrated circuits. The MAX14945 help in designing equipment to meet IEC 61000-4-2 without the need for additional ESD protection components.

The major difference between tests done using the HBM and IEC 61000-4-2 is higher peak current in IEC 61000-4-2 because series resistance is lower in the IEC 61000-4-2 model. Hence, the ESD withstand voltage measured to IEC 61000-4-2 is generally lower than that measured using the HBM.

<u>Figure 12</u> shows the IEC 61000-4-2 model and <u>Figure 13</u> shows the current waveform for IEC 61000-4-2 ESD Contact Discharge Test.

Figure 10. Human Body ESD Test Model

Figure 11. Human Body Current Waveform

Figure 12. IEC 61000-4-2 ESD Test Model

Figure 13. IEC 61000-4-2 ESD Generator Current Waveform

# **Typical Application Circuit**

## **Ordering Information/Selector Guide**

| PART          | TEMP RANGE     | PIN-<br>PACKAGE |  |

|---------------|----------------|-----------------|--|

| MAX14945EWE+  | -40°C to +85°C | 16 SOIC (W)     |  |

| MAX14945EWE+T | -40°C to +85°C | 16 SOIC (W)     |  |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package. T = Tape and reel.

# **Chip Information**

PROCESS: BiCMOS

## **Package Information**

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE | PACKAGE | OUTLINE | LAND PATTERN |

|---------|---------|---------|--------------|

| TYPE    | CODE    | NO.     | NO.          |

| 16 SOIC | W16M+9  | 21-0042 | 91-0107      |

### MAX14945

## 5kV Isolated 500kbps Half-Duplex RS-485/ RS-422 Transceiver with ±30kV ESD Protection

### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                      | PAGES<br>CHANGED |

|--------------------|------------------|----------------------------------|------------------|

| 0                  | 11/15            | Initial release                  | _                |

| 1                  | 1/17             | Updated pending safety approvals | 1, 6             |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.