# **Quad SPST +70V Analog Switches**

#### **General Description**

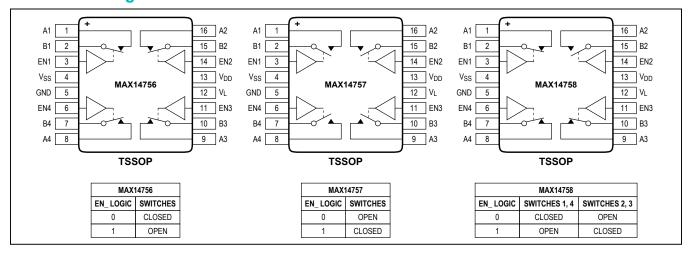

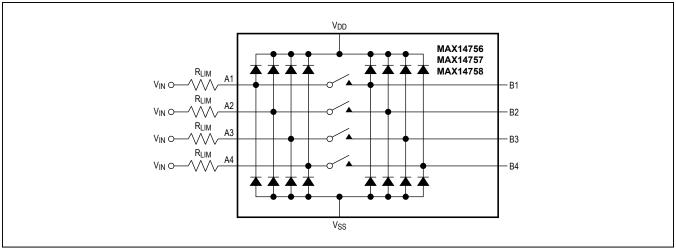

The MAX14756/MAX14757/MAX14758 are analog switches with a low on-resistance of  $10\Omega$  (max) that conduct equally well in both directions. All devices have a rail-to-rail analog-signal range. They operate with a single +10V to +70V supply in unipolar applications or ±35V dual supplies in bipolar applications. The bipolar supplies can be offset and do not have to be symmetrical.

The MAX14756 is a quad normally closed (NC) single-pole/single-throw (SPST) switch, the MAX14757 is a quad normally open (NO) SPST switch, and the MAX14758 has two NO and two NC SPST switches. These switches have  $5\Omega$  (typ) on-resistances and low on-leakage currents of 0.01nA (typ). The on-resistance flatness is  $0.004\Omega$  (typ).

The devices are suitable for a multitude of analog signal routing and switching applications. They are specified over an extended temperature range of -40°C to +85°C, but can be operated up to +125°C with elevated leakage currents.

#### **Applications**

- Industrial Control Systems

- Instrumentation

- Battery Management

- Environmental Control Systems

- Medical Systems

- ATE System

- Audio Signal Routing/Switching

#### **Features**

- Single-Supply Operation from +10V to +70V

- Bipolar-Supply Operation Up to ±35V

- On-Resistance of 10Ω (max)

- R<sub>ON</sub> Flatness of 0.004Ω (typ)

- 2.5nA (max) Off-Leakage Currents at +85°C

- Overvoltage/Undervoltage Clamping Through Protection Diodes

- 500µA (typ) Supply Current

- TSSOP 16-Pin Package

- -40°C to +85°C Ambient Temperature Range

- Functionally Compatible to DG411, DG412, and DG413

- Functionally Operational Up to +125°C

### **Ordering Information**

| PART         | FUNCTION             | TEMP<br>RANGE     | PIN-<br>PACKAGE |

|--------------|----------------------|-------------------|-----------------|

| MAX14756EUE+ | Quad NC<br>SPST      | -40°C to<br>+85°C | 16 TSSOP        |

| MAX14757EUE+ | Quad NO<br>SPST      | -40°C to<br>+85°C | 16 TSSOP        |

| MAX14758EUE+ | Dual NO +<br>NC SPST | -40°C to<br>+85°C | 16 TSSOP        |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

# **Functional Diagrams**

# Quad SPST +70V Analog Switches

### **Absolute Maximum Ratings**

| V <sub>DD</sub> to V <sub>SS</sub>   | 0.3V to +72V                                |

|--------------------------------------|---------------------------------------------|

| V <sub>SS</sub> to GND               | 36V to +0.3V                                |

| V <sub>I</sub> , EN_ to GND0.3V to t | he lesser of (+12V, V <sub>DD</sub> + 0.3V) |

| A_, B_ to V <sub>SS</sub>            | 0.3V to (V <sub>DD</sub> + 2V) or 100mA     |

|                                      | (whichever occurs first)                    |

| Continuous Current into A_, B        | ±100mA                                      |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                |

|-------------------------------------------------------|----------------|

| TSSOP (derate 11.1mW/°C above +70°C)                  | 889mW          |

| Operating Temperature Range                           | 40°C to +85°C  |

| Storage Temperature Range                             | 65°C to +150°C |

| Junction Temperature                                  | +150°C         |

| Lead Temperature (soldering, 10s)                     | +300°C         |

| Soldering Temperature (reflow)                        | +260°C         |

## **Package Thermal Characteristics (Note 1)**

**TSSOP**

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ )......90°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )......27°C/W

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Electrical Characteristics—Dual Supplies**

$(V_{DD}$  = +35V,  $V_{SS}$  = -35V,  $V_{GND}$  = 0V,  $V_{L}$  = +3.3V,  $T_{A}$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_{A}$  = +25°C.)

| PARAMETER                                  | SYMBOL                           | CONDITIONS                                                                                              | MIN             | TYP   | MAX             | UNITS |  |  |

|--------------------------------------------|----------------------------------|---------------------------------------------------------------------------------------------------------|-----------------|-------|-----------------|-------|--|--|

| POWER SUPPLY                               |                                  |                                                                                                         |                 |       |                 |       |  |  |

| V <sub>DD</sub> Supply-Voltage Range       | V <sub>DD</sub>                  |                                                                                                         | +10             |       | +35             | V     |  |  |

| V <sub>SS</sub> Supply-Voltage Range       | V <sub>SS</sub>                  |                                                                                                         | -10             |       | -35             | V     |  |  |

| V <sub>L</sub> Logic Supply-Voltage Range  | $V_{L}$                          |                                                                                                         | +1.6            |       | +11             | V     |  |  |

| V Supply Current                           | I <sub>DD(OFF)</sub>             | $V_{EN}$ to switch off state, $V_{A}$ , $V_{B}$ = +20V                                                  |                 | 200   | 450             |       |  |  |

| V <sub>DD</sub> Supply Current             | I <sub>DD(ON)</sub>              | $V_{EN}$ to switch on state, $V_A$ , $V_B$ = +20V                                                       |                 | 500   | 800             | μA    |  |  |

| Van Supply Current                         | I <sub>SS(OFF)</sub>             | $V_{EN}$ to switch off state, $V_{A}$ , $V_{B}$ = +20V                                                  |                 | 200   | 450             |       |  |  |

| V <sub>SS</sub> Supply Current             | I <sub>SS(ON)</sub>              | $V_{EN}$ to switch on state, $V_A$ , $V_B$ = +20V                                                       |                 | 500   | 800             | μA    |  |  |

| V <sub>L</sub> Current                     | ΙL                               | $V_L = +11V$ , $V_{EN1} = V_{EN2} = V_{EN3} = V_{EN4} = (0.25 \text{ x V}_L)$ or $(0.75 \text{ x V}_L)$ |                 |       | 0.4             | mA    |  |  |

| SWITCH                                     | ,                                |                                                                                                         | ,               |       |                 | ,     |  |  |

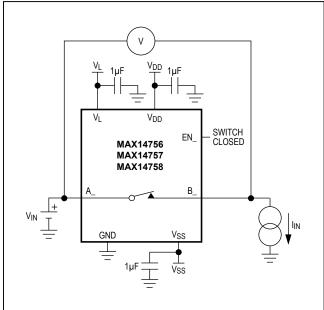

| Analog-Signal Range                        | V <sub>A</sub> , V <sub>B</sub>  | Figure 1                                                                                                | V <sub>SS</sub> |       | V <sub>DD</sub> | V     |  |  |

| Current Through Switch                     | I <sub>A_,</sub> I <sub>B_</sub> | V <sub>A</sub> _, V <sub>B</sub> _ = +20V                                                               | -50             |       | +50             | mA    |  |  |

| On-Resistance                              | R <sub>ON</sub>                  | $I_A$ , $I_B$ = 10mA, $V_A$ , $V_B$ = ±20V, Figure 1                                                    |                 | 5     | 10              | Ω     |  |  |

| On-Resistance Matching<br>Between Channels | ΔR <sub>ON</sub>                 | I <sub>A_</sub> , I <sub>B_</sub> = 10mA, V <sub>A_</sub> , V <sub>B_</sub> = ±20V, 0V<br>(Note 2)      |                 | 0.3   | 0.5             | Ω     |  |  |

| On-Resistance Flatness                     | R <sub>FLAT(ON)</sub>            | $I_A$ , $I_B$ = 10mA, $V_A$ , $V_B$ = ±20V                                                              |                 | 0.004 |                 | Ω     |  |  |

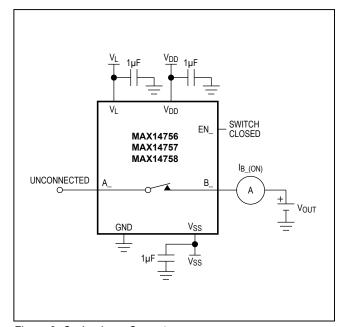

|                                            |                                  | V <sub>B</sub> = ±20V, V <sub>A</sub> = unconnected, Figure 2                                           | -5              |       | +5              |       |  |  |

| On-Leakage Current                         | I <sub>A/B_(ON)</sub>            | V <sub>B</sub> _ = ±20V, V <sub>A</sub> _ = unconnected,<br>T <sub>A</sub> = +25°C, Figure 2            |                 | 0.01  |                 | nA    |  |  |

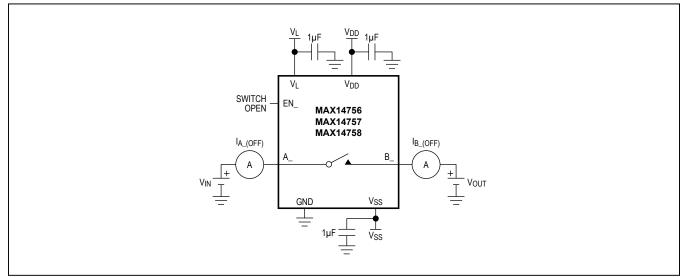

|                                            |                                  | V <sub>B</sub> = ±20V, V <sub>A</sub> = -20V, <u>Figure 3</u>                                           | -2.5            |       | +2.5            |       |  |  |

| Off-Leakage Current                        | I <sub>A/B_(OFF)</sub>           | $V_{B_{-}}$ = ±20V, $V_{A_{-}}$ = -20V, $T_{A}$ = +25°C,<br>Figure 3                                    |                 | 0.01  |                 | nA    |  |  |

## **Electrical Characteristics—Dual Supplies (continued)**

$(V_{DD}$  = +35V,  $V_{SS}$  = -35V,  $V_{GND}$  = 0V,  $V_{L}$  = +3.3V,  $T_{A}$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $T_{A}$  = +25°C.)

| PARAMETER                                      | SYMBOL           | CONDITIONS                                                                                         | MIN                      | TYP   | MAX                      | UNITS |  |

|------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------|--------------------------|-------|--------------------------|-------|--|

| LOGIC (EN1, EN2, EN3, EN4)                     |                  |                                                                                                    |                          |       |                          |       |  |

| Input-Voltage Low                              | V <sub>IL</sub>  |                                                                                                    |                          |       | 0.25 x<br>V <sub>L</sub> | V     |  |

| Input-Voltage High                             | V <sub>IH</sub>  |                                                                                                    | 0.75 x<br>V <sub>L</sub> |       |                          | V     |  |

| Input Leakage Current                          |                  | V <sub>EN</sub> = 0V or V <sub>L</sub>                                                             | -1                       |       | +1                       | μA    |  |

| DYNAMIC CHARACTERISTICS                        |                  |                                                                                                    |                          |       |                          |       |  |

| V <sub>DD</sub> /V <sub>SS</sub> Power-On Time |                  | $R_L = 10k\Omega$                                                                                  |                          | 1     |                          | μs    |  |

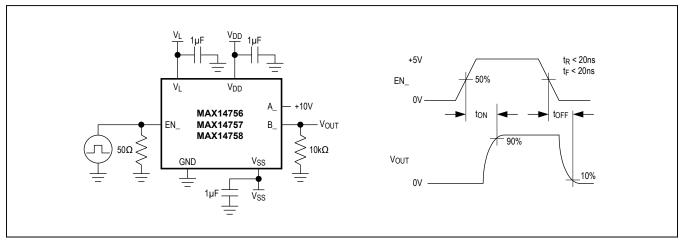

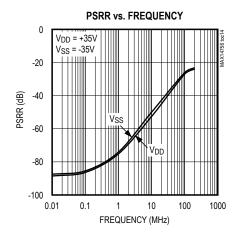

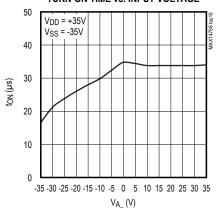

| Enable Turn-On Time                            | t <sub>ON</sub>  | $V_{A}$ , $V_{B}$ = ±10V, $R_{L}$ = 10k $\Omega$ , Figure 4                                        |                          | 35    | 60                       | μs    |  |

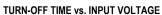

| Enable Turn-Off Time                           | t <sub>OFF</sub> | $V_A$ , $V_B = \pm 10V$ , $R_L = 10k\Omega$ , Figure 4                                             |                          | 2     | 3                        | μs    |  |

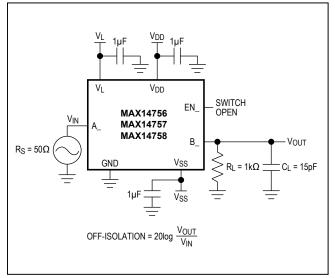

| Off-Isolation                                  | V <sub>ISO</sub> | $V_{A\_}$ , $V_{B\_}$ = 1V RMS, f = 100kHz, $R_L$ = 1k $\Omega$ , $C_L$ = 15pF, Figure 5           |                          | 65    |                          | dB    |  |

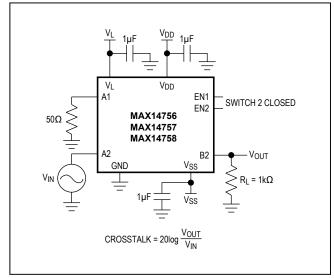

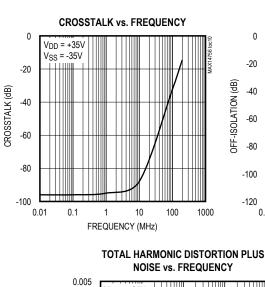

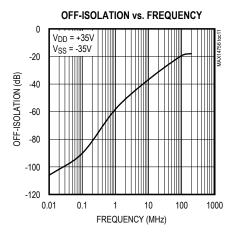

| Crosstalk                                      | V <sub>CT</sub>  | $R_S = R_L = 1k\Omega$ , Figure 6                                                                  |                          | 96    |                          | dB    |  |

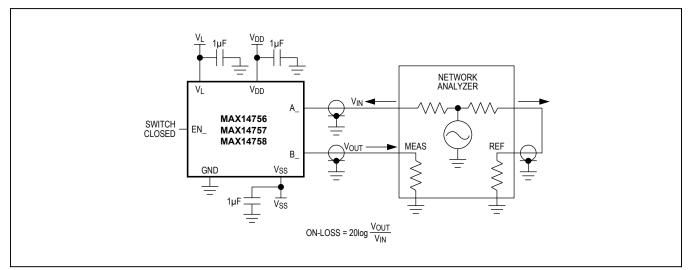

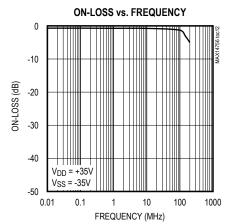

| -3dB Bandwidth                                 | BW               | $R_S$ = 50Ω, $R_L$ = 1kΩ, Figure 7                                                                 |                          | 145   |                          | MHz   |  |

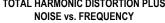

| Total Harmonic Distortion Plus<br>Noise        | THD+N            | $R_S = R_L = 1k\Omega$ , $f = 20Hz$ to $20kHz$                                                     |                          | 0.001 |                          | %     |  |

| Charge Injection                               | Q                | A_, B_ = GND, C <sub>L</sub> = 1nF, Figure 8                                                       |                          | 580   |                          | рC    |  |

| Switch-On Capacitance                          | C <sub>IN</sub>  | V <sub>DD</sub> = +50V, V <sub>SS</sub> = 0V, V <sub>A</sub> _, V <sub>B</sub> _= +4V,<br>f = 1MHz |                          | 40    |                          | pF    |  |

| Switch-Off Capacitance                         | C <sub>IN</sub>  | V <sub>DD</sub> = +50V, V <sub>SS</sub> = 0V, V <sub>A</sub> _, V <sub>B</sub> _= +4V,<br>f = 1MHz |                          | 35    |                          | pF    |  |

## **DC Electrical Characteristics—Single Supply**

$(V_{DD} = +70V, V_{SS} = V_{GND} = 0V, V_L = +3.3V, T_A = -40^{\circ}C$  to  $+85^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                                  | SYMBOL                 | CONDITIONS                                                                                         | MIN  | TYP | MAX  | UNITS |

|--------------------------------------------|------------------------|----------------------------------------------------------------------------------------------------|------|-----|------|-------|

| POWER SUPPLY                               |                        |                                                                                                    |      |     |      |       |

| V <sub>DD</sub> Supply-Voltage Range       | V <sub>DD</sub>        |                                                                                                    | +10  |     | +70  | V     |

| SWITCH                                     |                        |                                                                                                    |      |     |      |       |

| On-Resistance                              | R <sub>ON</sub>        | I <sub>A</sub> _ = 10mA, V <sub>A</sub> _, V <sub>B</sub> _= +20V, <u>Figure 1</u>                 |      | 5   | 10   | Ω     |

| On-Resistance Matching<br>Between Channels | DR <sub>ON</sub>       | I <sub>A_</sub> , I <sub>B_</sub> = 10mA, V <sub>A_</sub> , V <sub>B_</sub> = +70V, 0V<br>(Note 2) |      | 0.3 | 0.5  | Ω     |

| Off-Leakage Current                        | I <sub>A/B_(OFF)</sub> | V <sub>B</sub> _= +40V, V <sub>A</sub> _= +10V, <u>Figure 3</u>                                    | -2.5 |     | +2.5 | nA    |

Note 2: Guaranteed by design; not production tested.

Note 3: All parameters in single-supply operation are expected to be the same as in dual-supply operation.

# **Test Circuits/Timing Diagrams**

Figure 1. On-Resistance Measurement

Figure 2. On-Leakage Current

Figure 3. Off-Leakage Current

# **Test Circuits/Timing Diagrams (continued)**

Figure 4. Enable Switching Time

Figure 5. Off-Isolation

Figure 6. Crosstalk

# **Test Circuits/Timing Diagrams (continued)**

Figure 7. Frequency Response

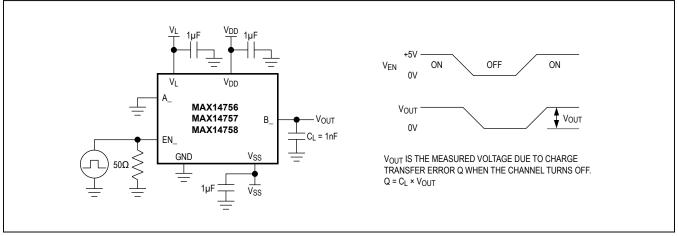

Figure 8. Charge Injection

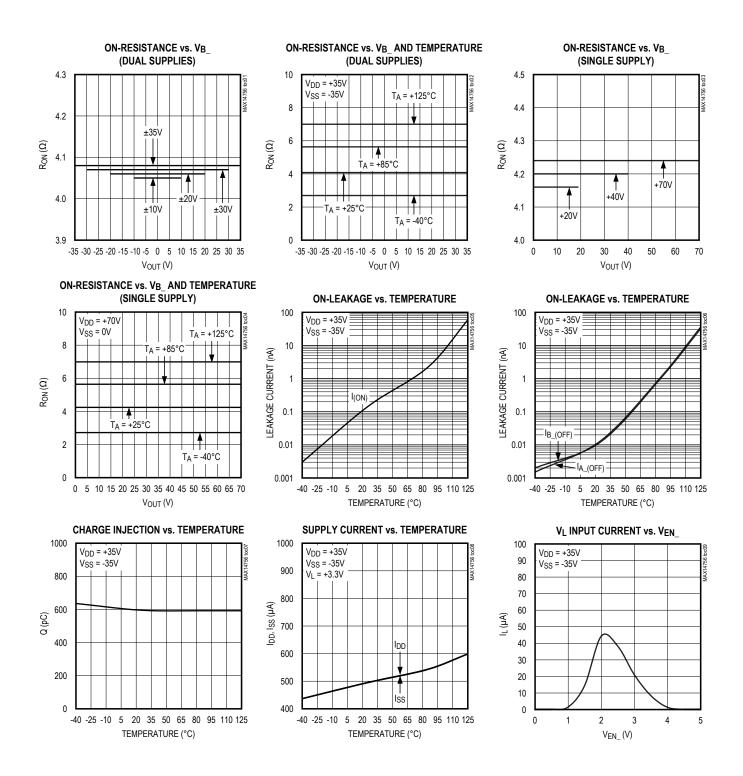

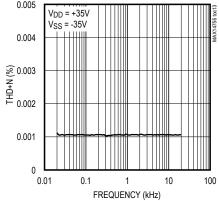

### **Typical Operating Characteristics**

$(T_A = +25^{\circ}C, V_L = +3.3V, unless otherwise noted.)$

# **Typical Operating Characteristics (continued)**

$(T_A = +25^{\circ}C, V_L = +3.3V, unless otherwise noted.)$

#### **TURN-ON TIME vs. INPUT VOLTAGE**

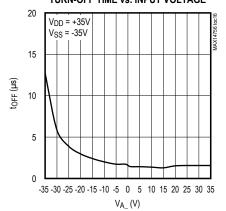

# **Pin Configuration**

# **Pin Description**

| PIN | NAME            | FUNCTION                                                                                                                                               |

|-----|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | A1              | Terminal A of Switch 1                                                                                                                                 |

| 2   | B1              | Terminal B of Switch 1                                                                                                                                 |

| 3   | EN1             | Enable Input of Switch 1. When EN1 is driven high, the switch's state (NO/NC) changes (see <u>Table 1</u> , <u>Table 2</u> , and <u>Table 3</u> ).     |

| 4   | V <sub>SS</sub> | Negative Supply Voltage. Bypass $V_{SS}$ to GND with a $1\mu F$ ceramic capacitor (100V rated) as close as possible to the pin.                        |

| 5   | GND             | Ground                                                                                                                                                 |

| 6   | EN4             | Enable Input of Switch 4. When EN4 is driven high, the switch's state (NO/NC) changes (see <u>Table 1</u> , <u>Table 2</u> , and <u>Table 3</u> ).     |

| 7   | B4              | Terminal B of Switch 4                                                                                                                                 |

| 8   | A4              | Terminal A of Switch 4                                                                                                                                 |

| 9   | A3              | Terminal A of Switch 3                                                                                                                                 |

| 10  | В3              | Terminal B of Switch 3                                                                                                                                 |

| 11  | EN3             | Enable Input of Switch 3. When EN3 is driven high, the switch's state (NO/NC) changes (see see <u>Table 1</u> , <u>Table 2</u> , and <u>Table 3</u> ). |

| 12  | $V_{L}$         | Logic Supply Voltage. Bypass V <sub>L</sub> to GND with a 1μF ceramic capacitor as close as possible to the pin.                                       |

| 13  | V <sub>DD</sub> | Positive Supply Voltage. Bypass $V_{DD}$ to GND with a $1\mu F$ ceramic capacitor (100V rated) as close as possible to the pin.                        |

| 14  | EN2             | Enable Input of Switch 2. When EN2 is driven high, the switch's state (NO/NC) changes (see see <u>Table 1</u> , <u>Table 2</u> , and <u>Table 3</u> ). |

| 15  | B2              | Terminal B of Switch 2                                                                                                                                 |

| 16  | A2              | Terminal A of Switch 2                                                                                                                                 |

#### **Detailed Description**

The MAX14756/MAX14757/MAX14758 are analog switches with low on-resistance of  $10\Omega$  (max) that conduct equally well in both directions. All devices have a rail-to-rail analog-signal range. They operate with a single +70V supply in unipolar applications or  $\pm 35$ V dual supplies in bipolar applications. The bipolar supplies can be offset and do not have to be symmetrical.

The MAX14756 is a quad NC SPST switch, the MAX14757 is a quad NO SPST switch, and the MAX14758 has two NO and two NC SPST switches. These switches have  $5\Omega$  (typ) on-resistances and low on-leakage currents of 5nA (max). The on-resistance flatness is  $0.004\Omega$  (typ). These devices are suitable for a multitude of analog-signal routing and switching applications, and are functonally operational up to  $+125^{\circ}C$  with increased leakage currents.

### **Applications Information**

#### **Low-Distortion Audio**

The MAX14756/MAX14757/MAX14758 switches, having low  $R_{ON}$  and very low  $R_{ON}$  variation with signal amplitude, are well suited for low-distortion audio applications. The *Typical Operating Characteristics* section shows Total Harmonic Distortion (THD) vs. Frequency graphs for several signal amplitudes.

#### Current Through the Switches

The current flowing through every switch must be limited to  $\pm 50$ mA for normal operation. If the current exceeds this limit, an internal leakage current flows from the switch to V<sub>SS</sub>. Larger input currents do not destroy the device, as long as the *Absolute Maximum Ratings* are not exceeded.

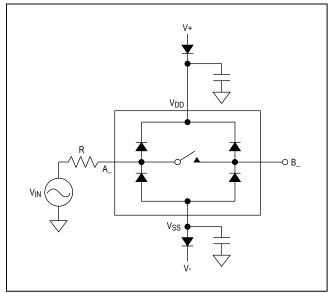

#### Input-Voltage Clamping

For applications that require input voltages beyond the supplies rails, the internal input diodes to  $V_{DD}$  and  $V_{SS}$  can be used to limit the input voltages. As shown in Figure 9, series resistors can be employed at the inputs to limit the currents flowing into the diodes during undervoltage and overvoltage conditions. Choose the limiting resistors such that the input currents are limited to IIN\_(MAX) = 100mA. The values of the current-limit resistors can be calculated as the larger of  $R_{LIM^+}$  and  $R_{LIM^-}$ .

$$R_{LIM+} = \frac{V_{IN}(MAX) - V_{DD}}{I_{IN}\_(MAX)}$$

$$R_{LIM-} = \frac{V_{SS} - V_{IN}(MIN)}{I_{IN} \ (MAX)}$$

Table 1. MAX14756 Truth Table

| LO  | GIC | SWI   | тсн    |

|-----|-----|-------|--------|

| EN1 | 0   | A1/B1 | Closed |

| EN2 | 0   | A2/B2 | Closed |

| EN3 | 0   | A3/B3 | Closed |

| EN4 | 0   | A4/B4 | Closed |

| EN1 | 1   | A1/B1 | Open   |

| EN2 | 1   | A2/B2 | Open   |

| EN3 | 1   | A3/B3 | Open   |

| EN4 | 1   | A4/B4 | Open   |

Table 2. MAX14757 Truth Table

| LO  | GIC | SWI   | тсн    |

|-----|-----|-------|--------|

| EN1 | 0   | A1/B1 | Open   |

| EN2 | 0   | A2/B2 | Open   |

| EN3 | 0   | A3/B3 | Open   |

| EN4 | 0   | A4/B4 | Open   |

| EN1 | 1   | A1/B1 | Closed |

| EN2 | 1   | A2/B2 | Closed |

| EN3 | 1   | A3/B3 | Closed |

| EN4 | 1   | A4/B4 | Closed |

Table 3. MAX14758 Truth Table

| LOGIC |   | SWITCH     |        |  |

|-------|---|------------|--------|--|

| EN1   | 0 | A1/B1      | Closed |  |

| EN2   | 0 | A2/B2      | Open   |  |

| EN3   | 0 | A3/B3      | Open   |  |

| EN4   | 0 | A4/B4      | Closed |  |

| EN1   | 1 | A1/B1      | Open   |  |

| EN2   | 1 | A2/B2      | Closed |  |

| EN3   | 1 | A3/B3      | Closed |  |

| EN4   | 1 | A4/B4 Open |        |  |

During an undervoltage or overvoltage condition, the input impedance is equal to  $R_{LIM}$ . The additional power dissipation due to the fault currents needs to be calculated. During an overvoltage or undervoltage clamping condition on one switch input, the other switches of the MAX14756/MAX14757/MAX14758 operate normally.

#### Beyond-the-Rail Input

If input voltages are expected to go beyond the supply voltages, but within the absolute maximum supply voltages of the MAX14756/MAX14757/MAX14758, add two diodes in series with the supplies as shown in Figure 10.

Figure 9. Input Overvoltage and Undervoltage Clamping

Figure 10. Beyond-the-Rail Application

During undervoltage and overvoltage events, the internal diodes pull  $V_{DD}/V_{SS}$  supplies up/down. An advantage of this scheme is that the input impedance is high and currents do not flow though the MAX14756/MAX14757/MAX14758 during overvoltage and undervoltage events. The input voltages must be limited to the voltages specified in the *Absolute Maximum Ratings* section.

#### **Chip Information**

PROCESS: BiCMOS

#### **Package Information**

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE  | PACKAGE | OUTLINE        | LAND           |

|----------|---------|----------------|----------------|

| TYPE     | CODE    | NO.            | PATTERN NO.    |

| 16 TSSOP | U16+1   | <u>21-0066</u> | <u>90-0117</u> |

# Quad SPST +70V Analog Switches

# **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                          | PAGES<br>CHANGED |

|--------------------|------------------|------------------------------------------------------|------------------|

| 0                  | 12/10            | Initial release                                      | _                |

| 1                  | 11/14            | Removed automotive reference in Applications section | 1                |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.