### 9334/DM9334 8-Bit Addressable Latch

#### **General Description**

The DM9334 is a high speed 8-bit Addressable Latch designed for general purpose storage applications in digital systems. It is a multifunctional device capable of storing single line data in eight addressable latches, and being a one-of-eight decoder and demultiplexer with active level high outputs. The device also incorporates an active level low common clear for resetting all latches, as well as an active level low enable.

The DM9334 has four modes of operation which are shown in the mode selection table. In the addressable latch mode, data on the data line (D) is written into the addressed latch. The addressed latch will follow the data input with all non-addressed latches remaining in their previous states. In the memory mode, all latches remain in their previous state and are unaffected by the data or address inputs.

In the one-of-eight decoding or demultiplexing mode, the addressed output will follow the state of the D input with all other inputs in the low state. In the clear mode all outputs are low and unaffected by the address and data inputs.

When operating the device as an addressable latch, changing more than one bit of the address could impose a transient wrong address. Therefore, this should only be done while in the memory mode.

The function tables summarize the operation of the product.

#### **Features**

- Common clear

- Easily expandable

- Random (addressable) data entry

- Serial to parallel capability

- 8 bits of storage/output of each bit available

- Active high demultiplexing/decoding capability

- Alternate Military/Aerospace device (9334) is available.

Contact a National Semiconductor Sales Office/Distributor for specifications.

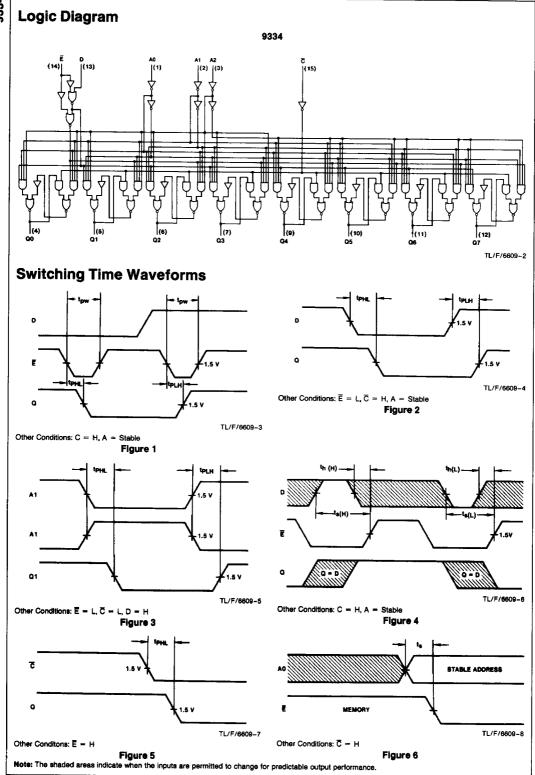

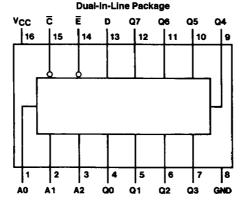

#### **Connection Diagram**

TL/F/6609-1

Order Number 9334DMQB, 9334FMQB, DM9334J or DM9334N See NS Package Number J16A, N16E or W16A

#### **Absolute Maximum Ratings (Note)**

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage 7V Input Voltage 5.5V

Operating Free Air Temperature Range

Military −55°C to +125°C Commercial 0° to +70°C

Storage Temperature Range -65°C to +150°C

Note: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the "Electrical Characteristics" table are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

#### **Recommended Operating Conditions**

| Symbol          | Par                                 | rameter                      |     | Military |      |     | Commercial |     |       |

|-----------------|-------------------------------------|------------------------------|-----|----------|------|-----|------------|-----|-------|

| Gymbol          | rai                                 |                              | Min | Nom      | Max  | Min | Nom        | Max | Units |

| Vcc             | Supply Voltage                      | 4.5                          | 5   | 5.5      | 4.75 | 5   | 5.25       | ٧   |       |

| V <sub>IH</sub> | High Level Input \                  | 2                            |     |          | 2    |     |            | ٧   |       |

| V <sub>IŁ</sub> | Low Level Input V                   |                              |     | 0.8      |      |     | 0.8        | ٧   |       |

| Іон             | High Level Outpu                    |                              |     | -0.8     |      |     | -0.8       | mA  |       |

| l <sub>OL</sub> | Low Level Output                    |                              |     | 16       |      |     | 16         | mA  |       |

| tw              | ENABLE Pulse W<br>(Fig. 1) (Note 4) | 19                           | 13  |          | 19   | 13  |            | ns  |       |

| tsu             | Setup Time                          | Data 1 (Fig. 4)              | 20  | 13       |      | 20  | 13         |     | ns    |

|                 | (Note 4)                            | Data 0 (Fig. 4)              | 20  | 14       |      | 20  | 14         |     |       |

|                 |                                     | Address (Fig. 6)<br>(Note 1) | 10  | 5        |      | 10  | 5          |     |       |

| tH              | Hold Time                           | Data 1 (Fig. 4)              | 0   | -10      |      | 0   | -10        |     | ns    |

|                 | (Note 4)                            | Data 0 (Fig. 4)              | 0   | -13      |      | 0   | -13        |     |       |

| TA              | Free Air Operating Temperature      |                              | -55 |          | 125  | 0   |            | 70  | °C    |

## Electrical Characteristics over recommended operating free air temperature range (unless otherwise noted)

| Symbol          | Parameter                            | Condi                                                                                            | lions   | Min | Typ<br>(Note 2) | Max   | Units |

|-----------------|--------------------------------------|--------------------------------------------------------------------------------------------------|---------|-----|-----------------|-------|-------|

| VI              | Input Clamp Voltage                  | $V_{CC} = Min, I_{I} = -12 \text{ mA}$ $V_{CC} = Min, I_{OH} = Max$ $V_{IL} = Max, V_{IH} = Min$ |         |     |                 | -1.5  | ٧     |

| V <sub>OH</sub> | High Level Output<br>Voltage         |                                                                                                  |         | 2.4 | 3.6             |       | ٧     |

| V <sub>OL</sub> | Low Level Output<br>Voltage          | $V_{CC} = Min, I_{OL}$ $V_{IH} = Min, V_{IL}$                                                    | •       |     | 0.2             | 0.4   | v     |

| lı              | Input Current @ Max<br>Input Voltage | V <sub>CC</sub> = Max, V <sub>I</sub>                                                            | = 5.5V  |     |                 | 1     | mA    |

| l <sub>IH</sub> | High Level Input                     | V <sub>CC</sub> = Max                                                                            | Ē Input |     |                 | 60    | μА    |

|                 | Current                              | $V_I = 2.4V$                                                                                     | Others  |     |                 | 40    |       |

| I <sub>IL</sub> | Low Level Input                      | V <sub>CC</sub> = Max                                                                            | E Input |     |                 | -2.4  | mA    |

|                 | Current                              | $V_I = 0.4V$                                                                                     | Others  |     |                 | -1.6  |       |

| los             | Short Circuit                        | V <sub>CC</sub> = Max                                                                            | MIL     | -30 |                 | - 100 | mA    |

|                 | Output Current                       | (Note 3)                                                                                         | СОМ     | -30 |                 | -100  |       |

| loc             | Supply Current                       | V <sub>CC</sub> = Max                                                                            | -       |     | 56              | 86    | mA    |

Note 1: The ADDRESS setup time is the time before the negative ENABLE transition that the ADDRESS must be stable so that the correct latch is addressed without affecting the other latches.

Note 2: All typicals are at  $V_{CC} = 5V$ ,  $T_A = 25$ °C.

Note 3: Not more than one output should be shorted at a time, and the duration should not exceed one second.

Note 4:  $T_A = 25^{\circ}C$  and  $V_{CC} = 5V$ .

#

| Symbol           | Parameter                                          | From (Input)                 | $R_L = 400\Omega$ , $C_L = 15 pF$ |     | Units |

|------------------|----------------------------------------------------|------------------------------|-----------------------------------|-----|-------|

| Syllibol         | rai ailletei                                       | To (Output)                  | Min                               | Max |       |

| tpLH             | Propagation Delay Time<br>Low to High Level Output | Enable to<br>Output, Fig. 1  |                                   | 28  | ns    |

| tPHL             | Propagation Delay Time<br>High to Low Level Output | Enable to<br>Output, Fig. 1  |                                   | 27  | ns    |

| t <sub>PLH</sub> | Propagation Delay Time<br>Low to High Level Output | Data to<br>Output, Fig. 2    |                                   | 35  | ns    |

| t <sub>PHL</sub> | Propagation Delay Time<br>High to Low Level Output | Data to<br>Output, Fig. 2    |                                   | 28  | ns    |

| t <sub>PLH</sub> | Propagation Delay Time<br>Low to High Level Output | Address to<br>Output, Fig. 3 |                                   | 35  | ns    |

| <sup>t</sup> PHL | Propagation Delay Time<br>High to Low Level Output | Address to<br>Output, Fig. 3 |                                   | 35  | ns    |

| <sup>t</sup> PHL | Propagation Delay Time<br>High to Low Level Output | Clear to<br>Output, Fig. 5   |                                   | 31  | ns    |

## **Function Tables**

| Ē | C | Mode                  |

|---|---|-----------------------|

| L | Н | Addressable Latch     |

| Н | Н | Memory                |

| L | L | Active High Eight     |

|   |   | Channel Demultiplexer |

| Н | L | Clear                 |

| Mode        | Present Output States |           |    |    |           |                  |                  |                  |    |    | puts | In |   |   |

|-------------|-----------------------|-----------|----|----|-----------|------------------|------------------|------------------|----|----|------|----|---|---|

| illouc      | Q7                    | Q6        | Q5 | Q4 | Q3        | Q2               | Q1               | Q0               | A2 | A1 | A0   | D  | Ē | c |

| Clear       | L                     | L         | L  | L  | L         | L                | L                | L                | Х  | Х  | Х    | х  | I | L |

|             | L                     | L         | L  | L  | L         | L                | L                | L                | L  | L  | L    | L  | L | L |

|             | L                     | L         | L  | L  | L         | L                | L                | Н                | L  | L  | L    | Н  | L | L |

|             | L                     | L         | L  | L  | L         | L                | L                | L                | L  | L  | Н    | L  | L | L |

|             | L                     | L         | L  | L  | L         | L                | Н                | L                | L  | L  | н    | Н  | L | L |

| Demultiplex |                       |           |    |    | •         |                  |                  |                  |    | •  |      | •  | • | • |

|             |                       |           |    |    | •         |                  |                  |                  |    | •  |      | •  | • | • |

|             |                       |           |    |    | •         |                  |                  |                  |    | •  |      | •  | • | • |

|             | Н                     | L         | L  | L  | L         | L                | L                | L                | Н  | Н  | Н    | н  | L | L |

| Memory      | ·                     |           |    |    |           |                  |                  | $Q_{N-1}$        | Х  | Х  | Х    | х  | Η | Н |

|             |                       |           |    |    | $Q_{N-1}$ | Q <sub>N-1</sub> | Q <sub>N-1</sub> | L                | L  | L  | L    | L  | L | Н |

|             |                       |           |    |    | ,, ,      | $Q_{N-1}$        | $Q_{N-1}$        | н                | L  | L  | L    | н  | L | н |

|             |                       |           |    |    |           | $Q_{N-1}$        | ï.               | $Q_{N-1}$        | L  | L  | н    | L  | L | Н |

| Addressable |                       |           |    |    |           | $Q_{N-1}$        | н                | $Q_{N-1}$        | L  | L  | Н    | н  | L | Н |

| Latch       |                       |           |    |    |           | •                |                  | '' '             |    | •  |      | •  | • | • |

|             |                       |           |    |    |           | •                |                  |                  |    | •  |      | •  | • | • |

|             |                       |           |    |    |           | •                |                  |                  |    | •  |      | •  | • | • |

|             | L                     | $Q_{N-1}$ |    |    |           |                  |                  | Q <sub>N-1</sub> | Н  | Н  | Н    | L  | L | Н |

|             | Н                     | $Q_{N-1}$ |    |    |           |                  |                  | $Q_{N-1}$        | Н  | Н  | Н    | н  | L | н |

X = Don't Care Condition

L = Low Voltage Level

H = High Voltage Level

$Q_{N-1}$  = Previous Output State