# **DS3885 BTL Arbitration Transceiver MIL-STD-883**

### **General Description**

The DS3885 is one in a series of transceivers designed specifically for the implementation of high performance Futurebus+ and proprietary bus interfaces. The DS3885 Arbitration Transceiver is designed to conform to IEEE 1194.1 (Backplane Transceiver Logic-BTL). The Arbitration Transceiver incorporates the competition logic internally which simplifies the implementation of a Futurebus+ application by minimizing the on board logic required.

The DS3885 driver output configuration is an NPN open collector which allows Wired-OR connection on the bus. Each driver output incorporates a Schottky diode in series with its collector to isolate the transistor output capacitance from the bus thus reducing the bus loading in the inactive state.

The BTL drivers also have high sink current capability to comply with the bus loading requirements defined within IEEE 1194.1 BTL specification.

Backplane Transceiver Logic (BTL) is a signaling standard that was invented and first introduced by National Semicon-(Continued)

### **Features**

- 9-bit inverting BTL transceiver

- Meets IEEE 1194.1 standard on Backplane Transceiver Logic (BTL)

PRELIMINARY

March 1994

- Includes on chip competition logic and parity checking

- Supports live insertion

- Glitch free power-up/down protection

- Typically less than 5 pF bus-port capacitance

- Low bus-port voltage swing (typically 1V) at 80 mA

- Open collector bus-port output allows Wired-OR

- connection Individual bus-port ground pins minimize ground bounce

- Controlled rise and fall time to reduce noise coupling to adjacent lines

- TTL compatible driver and control inputs

- Built in bandgap reference with separate  $QV_{CC}$  and QGND pins for precise receiver thresholds

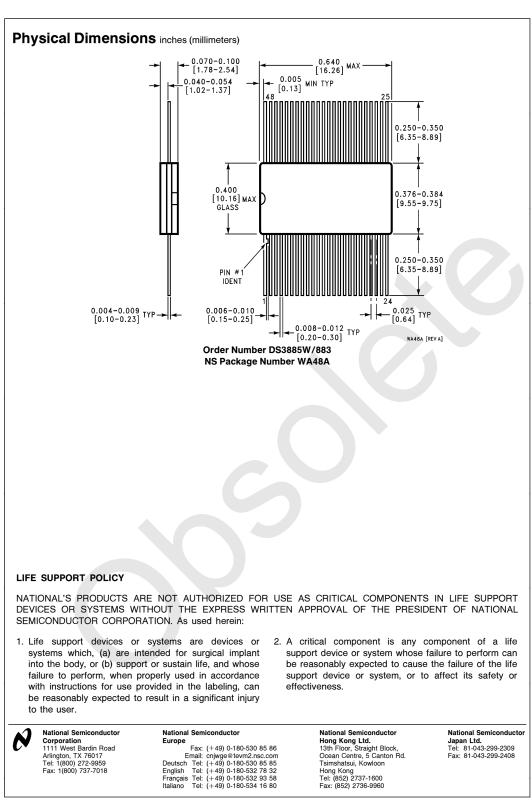

- Product offered in glass sealed CERPAK package style

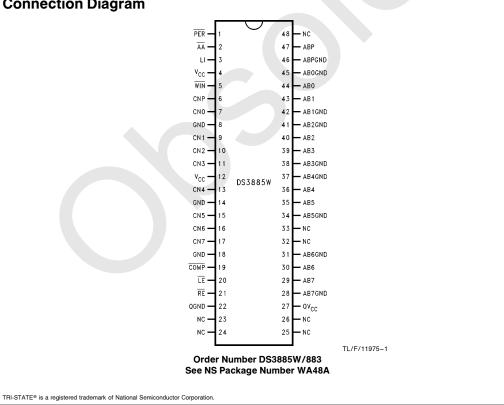

## **Connection Diagram**

© 1995 National Semiconductor Corporation TL/F/11975 RRD-B30M105/Printed in U. S. A.

### General Description (Continued)

ductor, then developed by the IEEE to enhance the performance of backplane buses. BTL compatible transceivers feature low output capacitance drivers to minimize bus loading, a 1V nominal signal swing for reduced power consumption and receivers with precision thresholds for maximum noise immunity. BTL eliminates settling time delays that severely limit TTL bus performance, and thus provide significantly higher bus transfer rates. The backplane bus is intended to be operated with termination resistors (selected to match the bus impedance) connected to 2.1V at both ends. The low voltage is typically 1V.

Separate ground pins are provided for each BTL output to minimize induced ground noise during simultaneous switching.

The transceiver's control and driver inputs are designed with high impedance PNP input structures and are fully TTL compatible.

The receiver is a high speed comparator that utilizes a bandgap reference for precision threshold control allowing maximum noise immunity to the BTL 1V signaling level. Separate  $QV_{CC}$  and QGND pins are provided to minimize the effects of high current switching noise. The output is TRI-STATE® and fully TTL compatible.

The signals ab < 7:0> designate the arbitration bus number which this transceiver places on the bus. The signal names AB < 7:0> designate the open collector Wired-OR signals on the backplane bus.

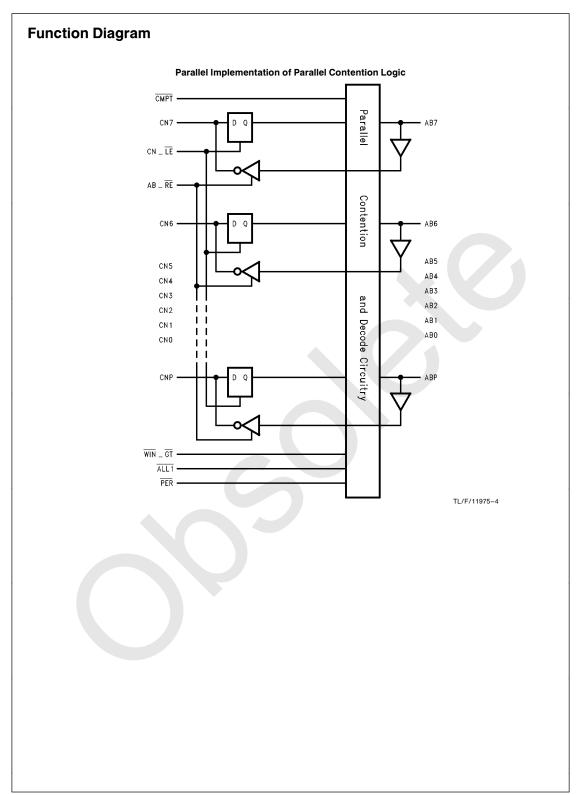

The DS3885 implements an odd parity check on the arbitration bus bits AB<7:0>, with ABP being the parity bit. The signal  $\overrightarrow{PER}$  will indicate the parity check result. For a quick indication of current bus conditions, the bus status block generates  $\overrightarrow{ALL1}$  (all asserted) status when all bits (AB<7:0>) are asserted by any module. This signal is used by the DS3875 Arbitration Controller to detect the Arbitration message number (during phase 1) or the powerfail message number (during phase 2).

To latch the arbitration number into the transceiver, it is placed onto the CN <7:0> port, and the CN\_LE signal is asserted. When the CMPT signal is asserted, the arbitration number is placed on the bus lines AB <7:0>. The WIN\_GT signal serves two purposes during the arbitration cycle. If the CMPT signal is not asserted during the arbitration cycle, the transceiver compares its internally latched number to the number on the AB <7:0> bus lines. If the internal number on the transceiver is greater than or equal to the number on the AB <7:0> lines, the WIN\_GT signal is asserted. However, if the CMPT signal is asserted, the transceiver participates in the competition. If the transceiver wins the arbitration, the WIN\_GT signal is asserted to confirm the winning. The AB\_RE signal is used to enable the on-chip receiver outputs.

The DS3885 supports live insertion as defined in IEEE 896.2 through the LI (Live Insertion) pin. To implement live insertion the LI pin should be connected to the live insertion power connector. If this function is not supported the LI pin must be tied to the  $V_{\rm CC}$  pin. The DS3885 also provides glitch free power-up/down protection during power sequencing.

The DS3885 has two types of power connections in addition to the LI pin. They are the Logic V<sub>CC</sub> (V<sub>CC</sub>) and the Quiet V<sub>CC</sub> (QV<sub>CC</sub>). There are two V<sub>CC</sub> pins on the DS3885 that provide the supply voltage for the logic and control circuitry. Multiple power pins reduce the effects of package inductance and thereby minimize switching noise. As these pins are common to the V<sub>CC</sub> bus internal to the device, a voltage difference between V<sub>CC</sub> and QV<sub>CC</sub> should never exceed  $\pm 0.5V$  because of ESD circuitry.

Additionally, the ESD circuitry between the V<sub>CC</sub> pins and all other pins except for BTL I/O's and LI pins requires that any voltage on these pins should not exceed the voltage on V<sub>CC</sub> + 0.5V

There are three different types of ground pins on the DS3885. They are the logic ground (GND), BTL grounds (AB0GND–AB7GND/ABPGND) and the Bandgap reference ground (QGND). All of these reference pins are isolated within the chip to minimize the effects of high current switching transients. For optimum performance the QGND should be returned to the connector through a quiet channel that does not carry transient switching current. The GND and AB0GND–AB7GND/ABPGND should be connected to the nearest backplane ground pin with the shortest possible path.

Since many different grounding schemes could be implemented and ESD circuitry exists on the DS3885, it is important to note that any voltage difference between ground pins, QGND, GND or AB0GND-AB7GND and ABPGND should not exceed  $\pm 0.5V$  including power-up/down sequencing.

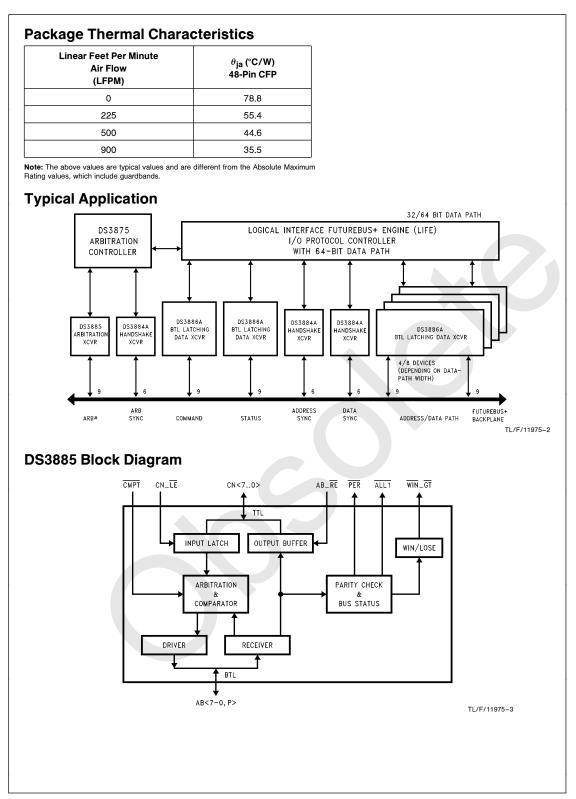

Two additional transceivers are included in the military Futurebus + family. The DS3884A BTL Handshake Transceiver features selectable Wired-OR glitch filtering. The DS3886A BTL 9-bit Latching Data Transceiver contains edge triggered latches in the driver which may be bypassed during a fall-through mode. In addition, the device contains a transparent latch in the receiver section.

The DS3875 Arbitration Controller included in the Futurebus+ family supports all the required and optional modes for Futurebus+ arbitration protocol. It is designed to be used in conjunction with the DS3884A and DS3885 transceivers.

The LOGICAL INTERFACE FUTUREBUS+ ENGINE (LIFE) is a high performance Futurebus+ Protocol Controller designed for IEEE 896.1. The LIFE will handle all handshaking signals between the Futurebus+ and the local bus interface. The Protocol Controller supports the Futurebus+ compelled mode data transfer as both master and slave. The Protocol Controller can be configured to operate in compliance to IEEE 896.2 Profile B mode. The LIFE is IEEE 896.5 compatible. The LIFE incorporates a DMA controller and 64-bit FIFO's for fast queuing.

All of the transceivers are offered in 48-pin CERPAK high density package styles.

## Absolute Maximum Ratings (Notes 1 and 2)

The 883 specifications are written to reflect the Reliability Electrical Test Specifications (RETS) established by National Semiconductor for this product. For a copy of the latest RETS please contact your local National Semiconductor sales office or distributor.

| Supply Voltage                   | 6.5V        |

|----------------------------------|-------------|

| Control Input Voltage            | 6.5V        |

| Driver Input and Receiver Output | 5.5V        |

| Receiver Input Current           | $\pm$ 15 mA |

| Bus Termination Voltage          | 2.4V        |

| Power Dissipation at 125°C       | 0.58W       |

|                                  |             |

Storage Temperature Range -65°C to +150°C Lead Temperature (Soldering, 4 sec.)

# Recommended Operating Conditions

| •    |                           |                      |

|------|---------------------------|----------------------|

| Min  | Мах                       | Units                |

| 4.5  | 5.5                       | V                    |

| 2.06 | 2.14                      | V                    |

| -55  | + 125                     | °C                   |

|      | <b>Min</b><br>4.5<br>2.06 | MinMax4.55.52.062.14 |

260°C

## DC Electrical Characteristics (Notes 2 and 3) $T_A = -55^{\circ}C$ to $+125^{\circ}C$ , $V_{CC} = 5V \pm 10\%$

| Symbol            | Parameter                                  | Conditions                                                                                                                                                                   | Min  | Тур      | Max       | Units          |

|-------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|-----------|----------------|

| DRIVER A          | ND CONTROL INPUT (CNn CNF                  | P, CN_LE, CMPT, and AB_RE)                                                                                                                                                   |      |          |           |                |

| VIH               | Minimum Input High Voltage                 |                                                                                                                                                                              | 2.0  |          |           | V              |

| VIL               | Maximum Input Low Voltage                  |                                                                                                                                                                              |      |          | 0.8       | V              |

| <u>կ</u>          | Input Leakage Current                      | $V_{IN} = V_{CC} = 5.5V$                                                                                                                                                     |      |          | 100       | μA             |

| Чн                | Input High Current                         | $V_{IN} = 2.4V$                                                                                                                                                              |      |          | 40        | μA             |

| Ι <sub>ΙL</sub>   | Input Low Current                          | $V_{IN} = 0.5V$                                                                                                                                                              |      |          | -100      | μA             |

| V <sub>CL</sub>   | Input Diode Clamp Voltage                  | $I_{CLAMP} = -12 \text{ mA}$                                                                                                                                                 |      |          | -1.2      | V              |

| DRIVER O          | UTPUT/RECEIVER INPUT (ABr                  | n and ABP)                                                                                                                                                                   |      |          |           |                |

| V <sub>OLB</sub>  | Output Low Bus Voltage<br>(Note 5)         | $\frac{\text{CNn} = \text{AB}_{\overline{\text{RE}}} = 2.4\text{V}, \text{CN}_{\overline{\text{LE}}} = \overline{\text{CMPT}} = 0.5\text{V}}{\text{I}_{OL} = 80 \text{ mA}}$ | 0.75 | 1.0      | 1.1       | ۷              |

| I <sub>OLBZ</sub> | Output Low Bus Current                     | $\overline{\text{CMPT}} = \text{AB}_\overline{\text{RE}} = 2.4\text{V}, \text{ABn} = 0.75\text{V}$                                                                           |      |          | -100      | μΑ             |

| I <sub>OHBZ</sub> | Output High Bus Current                    | $\overline{\text{CMPT}} = \text{AB}_\overline{\text{RE}} = 2.4\text{V}, \text{ABn} = 2.1\text{V}$                                                                            |      |          | 100       | μΑ             |

| V <sub>TH</sub>   | Receiver Input Threshold                   |                                                                                                                                                                              | 1.47 | 1.55     | 1.62      | V              |

| V <sub>CLP</sub>  | Positive Clamp Voltage                     | $V_{CC} = Max \text{ or } 0V, I_{ABn} = 1 \text{ mA}$                                                                                                                        | 2.4  | 3.4      | 4.5       | V              |

|                   |                                            | $V_{CC} = Max \text{ or } 0V, I_{ABn} = 10 \text{ mA}$                                                                                                                       | 2.9  | 3.9      | 5.0       | V              |

| V <sub>CLN</sub>  | Negative Clamp Voltage                     | $I_{CLAMP} = -12 \text{ mA}$                                                                                                                                                 |      |          | -1.2      | V              |

| RECEIVER          | ROUTPUT (CNn, CNP, ALL1, PE                | R, and WIN_GT)                                                                                                                                                               |      |          |           |                |

| V <sub>OH</sub>   | Voltage Output High                        |                                                                                                                                                                              | 2.4  | 3.2      |           | V              |

| V <sub>OL</sub>   | Voltage Output Low                         |                                                                                                                                                                              |      | 0.35     | 0.5       | V              |

|                   |                                            |                                                                                                                                                                              |      | 0.30     | 0.4       | v              |

| I <sub>OZ</sub>   | TRI-STATE Leakge Current                   | $CNn = CNP = 2.4V, = 2.4V, AB\_\overline{RE} = 2.4V$                                                                                                                         |      |          | 40        | μA             |

|                   |                                            | $CNn = CNP = 0.5V, AB \overline{RE} = 2.4V$                                                                                                                                  |      |          | -100      | μΑ             |

| I <sub>OS</sub>   | Output Short Circuit Current               | ABn = 1.1V, AB_RE = 0.5V<br><u>CMPT</u> = CN_LE = 2.4V (Note 4)                                                                                                              | -40  | -70      | -100      | mA             |

|                   |                                            |                                                                                                                                                                              |      |          |           |                |

|                   | URRENT                                     |                                                                                                                                                                              |      |          |           |                |

| SUPPLY C          | Supply Current: Includes V <sub>CC</sub> , | $\overline{\text{CMPT}} = \text{CN}_{\overline{\text{LE}}} = 0.5\text{V}, \text{All CNn} = \text{AB}_{\overline{\text{RE}}} = 2.4\text{V}$                                   |      | 75       | 100       | mA             |

|                   |                                            | $\overline{\text{CMPT}} = \text{CN\_LE} = 0.5\text{V}, \text{All CNn} = \text{AB\_RE} = 2.4\text{V}$ $\overline{\text{CMPT}} = \text{CN\_LE} = \text{AB\_RE} = 2.4\text{V}$  |      | 75<br>26 | 100<br>40 |                |

|                   | Supply Current: Includes V <sub>CC</sub> , |                                                                                                                                                                              |      |          |           | mA<br>mA<br>mA |

## DC Electrical Characteristics (Notes 2 and 3) T\_A = $-55^{\circ}$ C to $+125^{\circ}$ C, V<sub>CC</sub> = 5V $\pm 10\%$ (Continued)

Note 1: Absolute Maximum Ratings are those beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits. The tables of "Electrical Characteristics" provide conditions for actual device operation.

Note 2: All input and/or output pins shall not exceed  $V_{CC}$  + 0.5V and shall not exceed the absolute maximum rating at any time, including power-up and power-down. This prevents the ESD structure from being damaged due to excessive currents flowing from the input and/or output pins to  $QV_{CC}$  and  $V_{CC}$ . There is a diode between each input and/or output to  $V_{CC}$  which is forward biased when incorrect sequencing is applied. LI and Bn pins do not have power sequencing requirements with respect to  $V_{CC}$  and  $QV_{CC}$ .

Note 3: All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to device ground unless otherwise specified. All typical values are specified under these conditions:  $V_{CC} = 5V$  and  $T_A = 25^{\circ}C$ , unless otherwise stated.

Note 4: Only one output should be shorted at a time, and duration of the short not to exceed one second.

Note 5: Referenced to appropriate signal ground. Do not exceed maximum power dissipation of package.

## AC Electrical Characteristics $T_A = -55^{\circ}C$ to $+125^{\circ}C$ , $V_{CC} = 5V \pm 10\%$ (Note 6)

| Symbol           | Parame                                                                                                                                                                                             | ter                                                          | Conditions                                                                                                                                                                                                       | Min | Тур | Max | Units |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

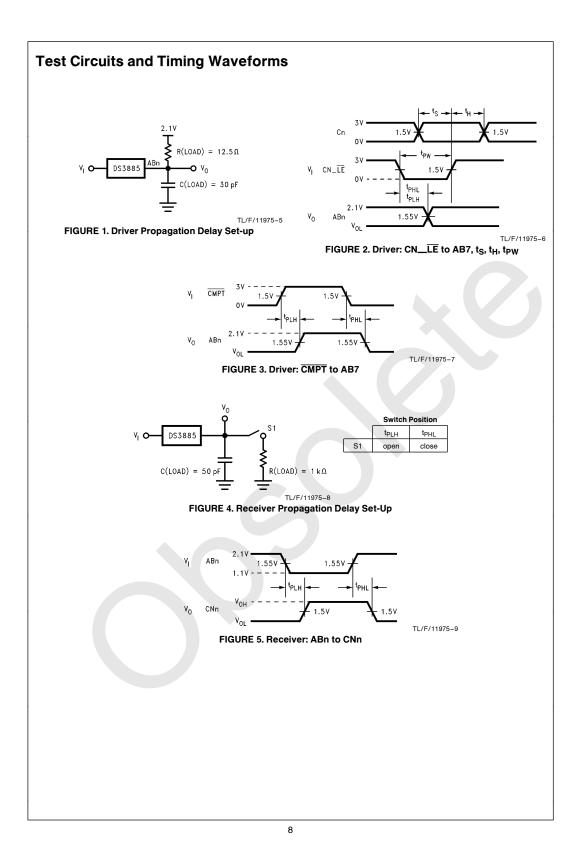

| DRIVER (#        | Figures 1 and 2)                                                                                                                                                                                   |                                                              |                                                                                                                                                                                                                  |     |     |     |       |

| t <sub>PHL</sub> | CN_TE to AB7 P                                                                                                                                                                                     | ropagation Delay                                             | $\overline{\text{CMPT}} = 0\text{V}, \text{AB}_\overline{\text{RE}} = 3\text{V}$                                                                                                                                 | 7   | 13  | 18  | ns    |

| t <sub>PLH</sub> |                                                                                                                                                                                                    |                                                              |                                                                                                                                                                                                                  | 6   | 10  | 24  | ns    |

| t <sub>r</sub>   | Transition Time—Rise                                                                                                                                                                               | /Fall                                                        | $AB\_\overline{RE} = 3V, \overline{CMPT} = CN\_\overline{LE} = 0$                                                                                                                                                |     | 3   |     | ns    |

| t <sub>f</sub>   | 20% to 80%                                                                                                                                                                                         |                                                              | $AB\_\overline{RE} = 3V, \overline{CMPT} = CN\_\overline{LE} = 0$                                                                                                                                                |     | 1   |     | ns    |

| DRIVER T         | IMING REQUIREMENT                                                                                                                                                                                  | <b>S</b> ( <i>Figures 1</i> and <i>2</i>                     | )                                                                                                                                                                                                                |     |     |     |       |

| ts               | CNn to CN_LE                                                                                                                                                                                       | Set-Up Time                                                  | $AB\_\overline{RE} = 3V, \overline{CMPT} = 0V$                                                                                                                                                                   | 9   |     |     | ns    |

| t <sub>H</sub>   | CN_LE to CNn                                                                                                                                                                                       | Hold Time                                                    | $AB\_\overline{RE} = 3V, \overline{CMPT} = 0V$                                                                                                                                                                   | 0   |     |     | ns    |

| t <sub>PW</sub>  | CN_LE Pulse Width                                                                                                                                                                                  |                                                              | $AB\_\overline{RE} = 3V, \overline{CMPT} = 0V$                                                                                                                                                                   | 15  |     |     | ns    |

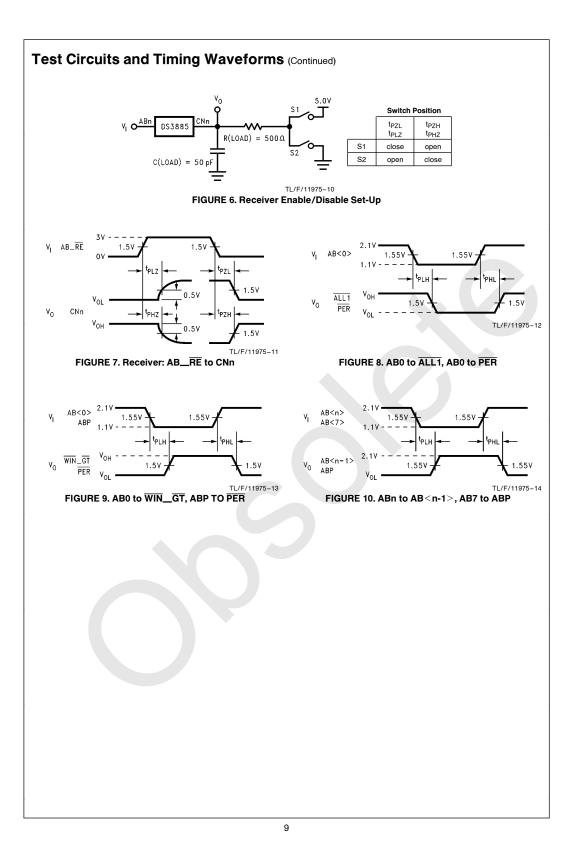

| RECEIVER         | 3                                                                                                                                                                                                  |                                                              |                                                                                                                                                                                                                  |     |     |     |       |

| t <sub>PHL</sub> | ABn to CNn P                                                                                                                                                                                       | ropagation Delay                                             | $AB\_\overline{RE} = 0V, \overline{CMPT} = CN\_\overline{LE} = 3V$                                                                                                                                               | 5   | 13  | 22  | ns    |

| t <sub>PLH</sub> |                                                                                                                                                                                                    |                                                              | (Figures 4 and 5)                                                                                                                                                                                                |     | 15  | 23  | ns    |

| t <sub>PLZ</sub> | AB_RE to CNn                                                                                                                                                                                       | Disable Time                                                 | $\overline{\text{CMPT}} = \text{CN}_{\overline{\text{LE}}} = 3\text{V}, \text{ABn} = 2.1\text{V}$                                                                                                                | 3   | 6   | 12  | ns    |

| t <sub>PZL</sub> |                                                                                                                                                                                                    | Enable Time                                                  | (Figures 6 and 7)                                                                                                                                                                                                |     | 9   | 13  | ns    |

| t <sub>PHZ</sub> |                                                                                                                                                                                                    | Disable Time                                                 | $\overline{\text{CMPT}} = \text{CN}_{\overline{\text{LE}}} = 3\text{V}, \text{ABn} = 1.1\text{V}$                                                                                                                | 4   | 7   | 13  | ns    |

| t <sub>PZH</sub> |                                                                                                                                                                                                    | Enable Time                                                  | (Figures 6 and 7)                                                                                                                                                                                                |     | 6   | 11  | ns    |

| OTHERS           |                                                                                                                                                                                                    |                                                              |                                                                                                                                                                                                                  |     | 1   | 1   |       |

| t <sub>PHL</sub> | AB0 to ALL1 P                                                                                                                                                                                      | ropagation Delay                                             | AB <7:1> = 1.1V                                                                                                                                                                                                  | 7   | 16  | 28  | ns    |

| t <sub>PLH</sub> | All Asserted Condition                                                                                                                                                                             |                                                              | (Figures 4 and 8)                                                                                                                                                                                                | 7   | 16  | 26  | ns    |

| t <sub>PHL</sub> | AB0 to WIN_GT P                                                                                                                                                                                    | ropagation Delay                                             | gation Delay $\overline{\text{CMPT}} = \text{CN}_{\overline{\text{LE}}} = 0\text{V}, \text{AB}_{\overline{\text{RE}}} = 3\text{V},$                                                                              | 6   | 14  | 23  | ns    |

| t <sub>PLH</sub> | CN_LE to CNn Hold Time   CN_LE Pulse Width   ABn to CNn Propagation Delay   AB_RE to CNn Disable Time   Enable Time Disable Time   AB0 to ALL1 Propagation Delay   AB0 to WIN_GT Propagation Delay | CN < 7:0> = 0V<br>AB < 7:0> = 2.1V ( <i>Figures 4</i> and 9) | 6                                                                                                                                                                                                                | 14  | 23  | ns  |       |

| t <sub>PHL</sub> |                                                                                                                                                                                                    |                                                              | $\overline{\text{CMPT}} = \text{AB}_\overline{\text{RE}} = 3\text{V}, \text{CN}_\overline{\text{LE}} = 0\text{V},$                                                                                               | 6   | 16  | 27  | ns    |

| t <sub>PLH</sub> |                                                                                                                                                                                                    |                                                              | CN <7:1> = 0V, CN0 = 3V $AB <7:0> = 2.1V  (Figures 4  and  9)$                                                                                                                                                   |     | 16  | 26  | ns    |

| t <sub>PHL</sub> | ABP to PER P                                                                                                                                                                                       | ropagation Delay                                             | $\overline{\text{CMPT}} = \text{CN}_{\overline{\text{LE}}} = \text{AB}_{\overline{\text{RE}}} = 3\text{V},$                                                                                                      | 6   | 13  | 23  | ns    |

| t <sub>PLH</sub> |                                                                                                                                                                                                    |                                                              | AB <7:1> = 1.1V, AB0 = 2.1V<br>( <i>Figures 4</i> and <i>8</i> )                                                                                                                                                 |     | 13  | 23  | ns    |

| t <sub>PHL</sub> |                                                                                                                                                                                                    |                                                              | $\label{eq:constraint} \begin{split} \hline \hline \hline CMPT &= CN\_LE = 0V, AB\_RE = 3V, \\ CNn &= 0V, CN < n-1 > = 3V, \\ CN < 7:n+1 > = 0V, AB < 7:n+1 > = 2.1V \\ (Figures 1 \text{ and } 10) \end{split}$ | 5   | 12  | 22  | ns    |

| t <sub>PLH</sub> |                                                                                                                                                                                                    |                                                              |                                                                                                                                                                                                                  | 3   | 13  | 28  | ns    |

| t <sub>PHL</sub> | CMPT to AB7 P                                                                                                                                                                                      | ropagation Delay                                             | $CN\_\overline{LE} = 0V, AB\_\overline{RE} = CN7 = 3V$                                                                                                                                                           | 4   | 8   | 14  | ns    |

| tPLH             |                                                                                                                                                                                                    |                                                              | ( <i>Figures 1</i> and <i>3</i> )                                                                                                                                                                                | 5   | 9   | 22  | ns    |

| t <sub>PHL</sub> | AB7 to ABP P                                                                                                                                                                                       | ropagation Delay                                             | $\overline{\text{CMPT}} = \text{CN}_{\overline{\text{LE}}} = \text{OV}, \text{AB}_{\overline{\text{RE}}} = \text{CNP} = \text{3V},$                                                                              |     | 36  | 60  | ns    |

| t <sub>PLH</sub> |                                                                                                                                                                                                    |                                                              | CN <7:0> = 0V ( <i>Figures 1</i> and <i>10</i> )                                                                                                                                                                 |     | 36  | 65  | ns    |

| Symbol               |                              | Parame                | ter              | Conditions                                                                                                                                                                                                                                                  | Min           | Тур               | Max           | Units   |  |

|----------------------|------------------------------|-----------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------|---------------|---------|--|

| RAMETERS             | NOT TES                      | TED                   |                  |                                                                                                                                                                                                                                                             |               |                   |               |         |  |

| Coutput              | Capa                         | citance at Bn         |                  | (Note 7)                                                                                                                                                                                                                                                    |               | 5                 |               | pF      |  |

| t <sub>NR</sub>      | Noise                        | Rejection             |                  | (Note 8)                                                                                                                                                                                                                                                    |               | 1                 |               | ns      |  |

| Note 7: This para    | ameter is te<br>ameter is te | sted during device ch | -                | 1194.0 BTL Backplane Design measurement revealed that the                                                                                                                                                                                                   |               | lly reject 1 ns p | oulse width.  |         |  |

| Pin Name             | -                            | Number of<br>Pins     | Input/<br>Output | Description                                                                                                                                                                                                                                                 |               |                   |               |         |  |

| ALL1                 |                              | 1                     | 0                | TTL—All asserted (A logic "1" indicates that all the competition bits are asserted.)                                                                                                                                                                        |               |                   |               |         |  |

| AB<7:0>              |                              | 8                     | I/O              | BTL—Futurebus + W                                                                                                                                                                                                                                           | /ired-OR co   | mpetition bits    | 6             |         |  |

| ABP                  |                              | 1                     | I/O              | BTL—Futurebus + W                                                                                                                                                                                                                                           | /ired-OR co   | mpetition par     | rity bit      |         |  |

| AB<7:0> a<br>ABP GND | nd                           | 9                     | NA               | Parallel driver ground<br>switching of driver ou                                                                                                                                                                                                            |               |                   | e due to high | current |  |

| CN<7:0>              |                              | 8                     | I/O              | TTL TRI-STATE—Mo                                                                                                                                                                                                                                            | dule compe    | etition bits      |               |         |  |

| CNP                  |                              | 1                     | I                | TTL TRI-STATE—Mo                                                                                                                                                                                                                                            | dule compe    | etition parity I  | oit           |         |  |

| CMPT                 |                              | 1                     | Ι                | TTL—Competition bit (A logic "0" indicates that the module will compete in the arbitration.)                                                                                                                                                                |               |                   |               |         |  |

| GND                  |                              | 3                     | NA               | Ground for switching                                                                                                                                                                                                                                        | circuits. (No | ote 9)            |               |         |  |

| CN_LE                |                              | 1                     | Ι                | TTL—CNn latch enable (A logic "0" indicates that the CN <n> logic states are latched with corresponding parity bit).</n>                                                                                                                                    |               |                   |               |         |  |

| LI                   |                              | 1                     | NA               | Power supply for live insertion. Boards that require live insertion should connect LI to the live insertion pin on the connector. (Note 10)                                                                                                                 |               |                   |               |         |  |

| NC                   |                              | 7                     | NA               | No connect                                                                                                                                                                                                                                                  |               |                   |               |         |  |

| PER                  |                              | 1                     | 0                | TTL—ABn odd parity                                                                                                                                                                                                                                          | (A logic "0'  | ' indicates pa    | arity error)  |         |  |

| AB_RE                |                              | 1                     |                  | TTL—Receiver Enab                                                                                                                                                                                                                                           | le (A logic " | 0" enables r      | eceivers)     |         |  |

| QGND                 |                              | 1                     | NA               | Ground for receiver input bandgap reference and non-switching circuits. (Note 9)                                                                                                                                                                            |               |                   |               |         |  |

| QV <sub>CC</sub>     |                              | 1                     | NA               | V <sub>CC</sub> supply for bandgap reference and non-switching circuits.<br>(Note 2)                                                                                                                                                                        |               |                   |               |         |  |

| V <sub>CC</sub>      |                              | 2                     | NA               | V <sub>CC</sub> supply for switch                                                                                                                                                                                                                           | ing circuits. | (Note 10)         |               |         |  |

| WIN_GT               |                              | 1                     | 0                | TTL—Win signal (active low). During competition, WIN_GT<br>indicates that the module has won the competition. For a module<br>not participating in the competition, WIN_GT indicates that the<br>module has a number which is greater than winner's number. |               |                   |               |         |  |

Note 9: The multiplicity of parallel ground paths, reduces the effective inductance of bonding wires and leads, which then reduces the noise caused by transients on the ground path. The various ground pins can be tied together provided that the external ground has low inductance (i.e., ground plane with power pins and many signal pins connected to the backplane ground). If the external ground floats considerably during transients, precautionary steps should be taken to prevent QGND from moving with reference to the backplane ground. The receiver threshold should have the same ground reference as the signal coming from the backplane. A voltage offset between their grounds will degrade the noise margin.

Note 10: The same considerations for ground are used for  $V_{CC}$  in reducing lead inductance. (See Note 9)  $QV_{CC}$  and  $V_{CC}$  should be tied together externally. If live insertion is not supported, the LI pin can be tied together with  $QV_{CC}$  and  $V_{CC}$ .

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications