# DP8440-40/DP8440-25/DP8441-40/DP8441-25 microCMOS Programmable 16/64 Mbit **Dynamic RAM Controller/Driver**

# **General Description**

The DP8440/41 Dynamic RAM Controllers provide an easy interface between dynamic RAM arrays and 8-, 16-, 32- and 64-bit microprocessors. The DP8440/41 DRAM Controllers generate all necessary control and timing signals to successfully interface and design dynamic memory systems. With significant enhancements over the DP8420/21/22 predecessors, the DP8440/41 are suitable for high performance memory systems. These controllers support page and burst accesses for fast page, static column and nibble DRAMs. Refreshes and accesses are arbitrated on chip. RAS low time during refresh and RAS precharge time are quaranteed by these controllers. Separate precharge counters for each RAS output avoid delayed back to back accesses due to precharge when using memory interleaving. Programmable features make the DP8440/41 DRAM Con-

trollers flexible enough to fit many memory systems.

#### **Features**

- 40 MHz and 25 MHz operation

- Page detection

- Automatic CPU burst accesses

- Support 1/4/16/64 Mbits DRAMs

- High capacitance drivers for RAS, CAS, WE and Q outputs

- Support for fast page, static column and nibble mode **DRAMs**

- High precision PLL based delay line

- Byte enable for word size up to 32 bits on the DP8440 or 64 bits on the DP8441

- Automatic Internal Refresh

- Staggered RAS-Only refresh

- Burst and CAS-before-RAS refresh

- Error scrubbing during refresh

- TRI-STATE® outputs

- Easy interface to all major microprocessors

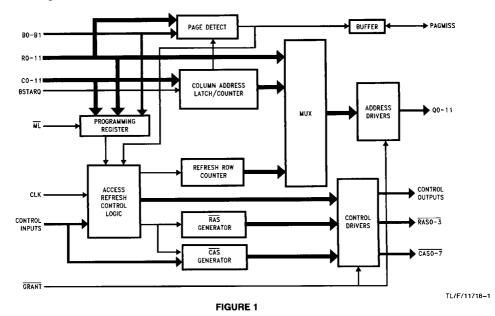

# **Block Diagram**

TRI-STATE® is a registered trademark of National Semiconductor Corporation

| DRAM<br>Controller | Maximum Clock<br>Frequency | Package<br>Type | Bus Width<br>Supporting | Largest DRAM<br>Possible |

|--------------------|----------------------------|-----------------|-------------------------|--------------------------|

| DP8440V-40         | 40 MHz                     | 84-Pin PLCC     | 8, 16, 32               | 16 Mbits                 |

| DP8440VLJ-40       | 40 MHz                     | 100-Pin PQFP    | 8, 16, 32               | 16 Mbits                 |

| DP8440VLJ-25       | 25 MHz                     | 100-Pin PQFP    | 8, 16, 32               | 16 Mbits                 |

| DP8441VLJ-40       | 40 MHz                     | 100-Pin PQFP    | 8, 16, 32, 64           | 64 Mbits                 |

| DP8441VLJ-25       | 25 MHz                     | 100-Pin PQFP    | 8, 16, 32, 64           | 64 Mbits                 |

## **Table of Contents**

#### 1.0 CONNECTION DIAGRAMS

#### 2.0 FUNCTIONAL INTRODUCTION

#### 3.0 SIGNAL DESCRIPTION

- 3.1 Address and Control Signals

- 3.2 DRAM Control Signals

- 3.3 Refresh Signals

- 3.4 Reset and Programming Signals

- 3.5 Clock Inputs

- 3.6 Power Signals and Capacitor Input

## 4.0 PROGRAMMING AND RESETTING

- 4.1 Reset

- 4.2 Programming Sequence

- 4.3 Programming Selection Bits

#### 5.0 ACCESS MODES

- 5.1 Opening Access

- 5.2 Normal Mode

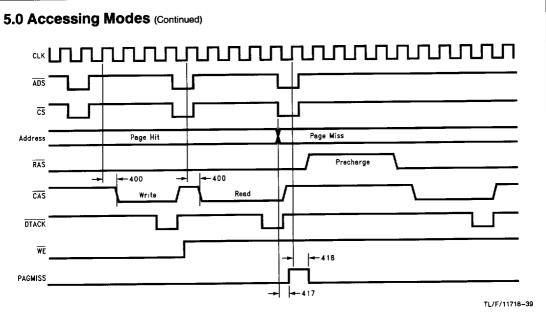

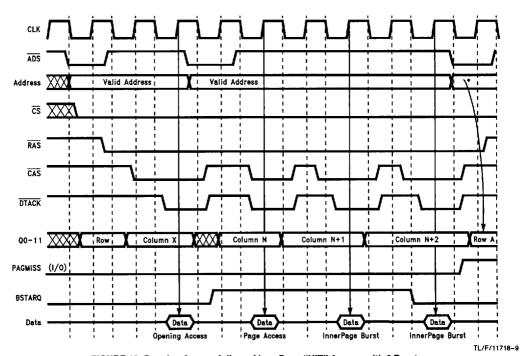

- 5.3 Page Mode

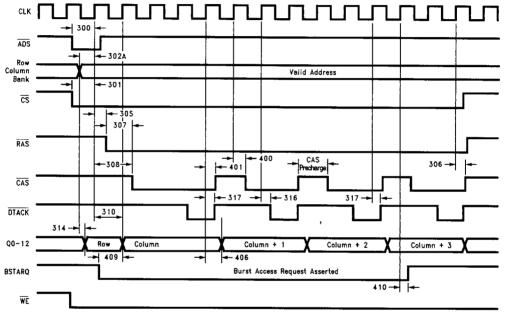

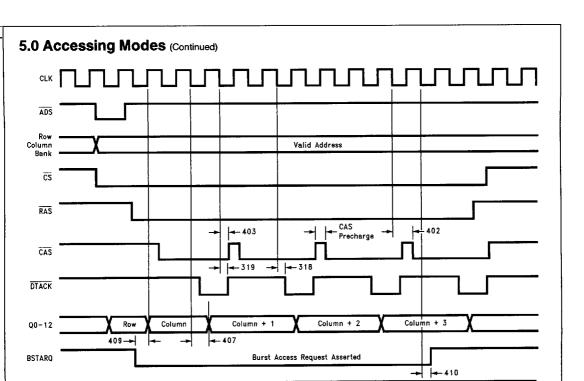

- 5.4 Burst Access

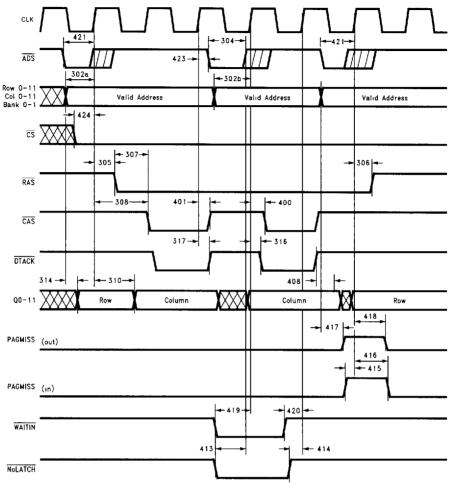

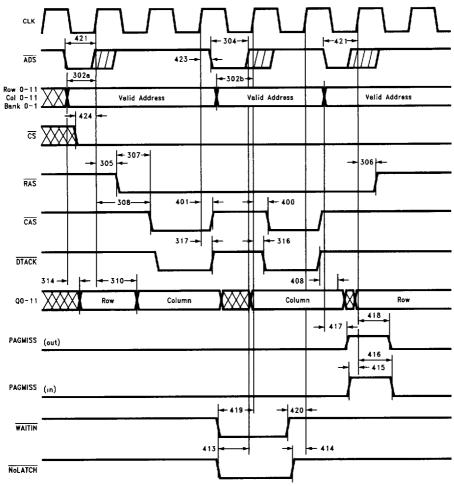

- 5.5 Inner Page Burst Access

#### 6.0 REFRESH MODES

- 6.1 Auto-Internal Refresh

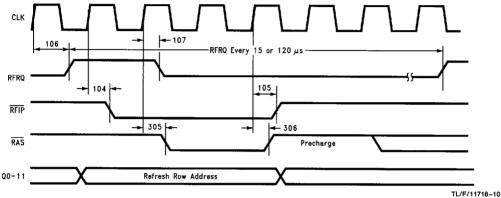

- 6.2 Externally Controlled Refresh

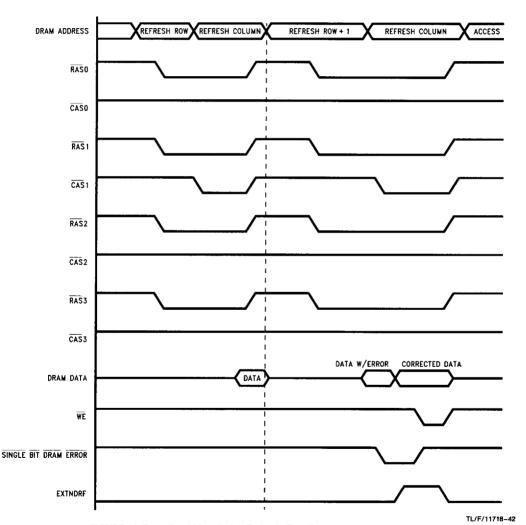

- 6.3 Error Scrubbing during Refresh

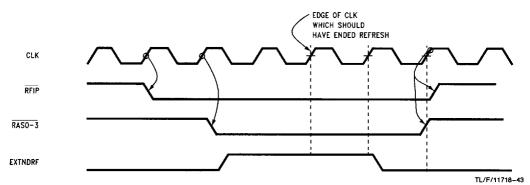

- 6.4 Extending Refresh

- 6.5 Refresh Types

#### 7.0 WAIT SUPPORT

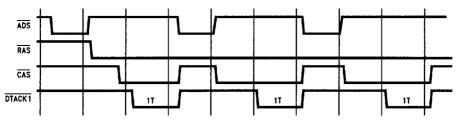

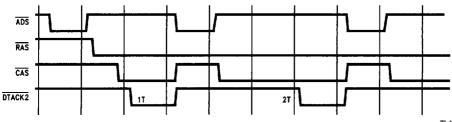

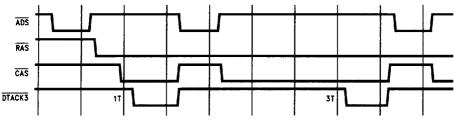

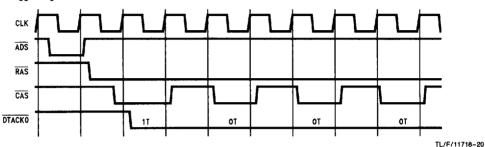

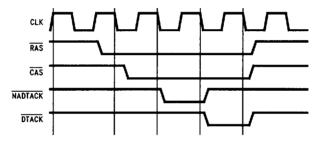

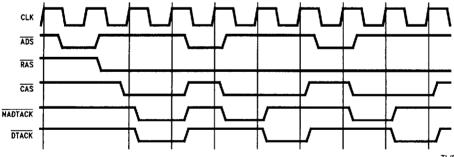

- 7.1 DTACK During Opening Access

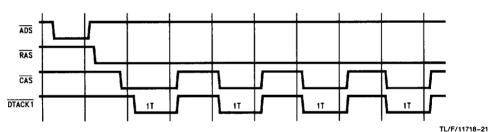

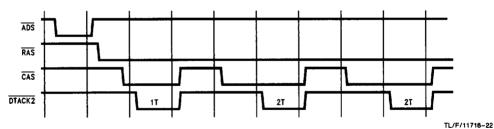

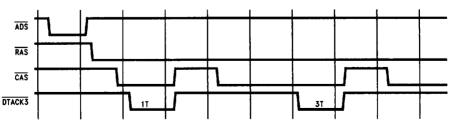

- 7.2 DTACK During Page Access

- 7.3 DTACK During Burst Access

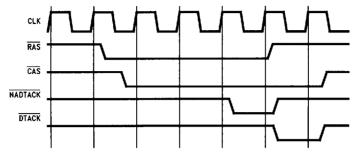

- 7.4 Next Address or Early DTACK Support

#### **8.0 ABSOLUTE MAXIMUM RATINGS**

#### 9.0 DC ELECTRICAL CHARACTERISTICS

### 10.0 LOAD CAPACITANCE

### 11.0 AC TIMING PARAMETERS

#### 12.0 AC TIMING WAVEFORMS

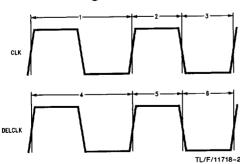

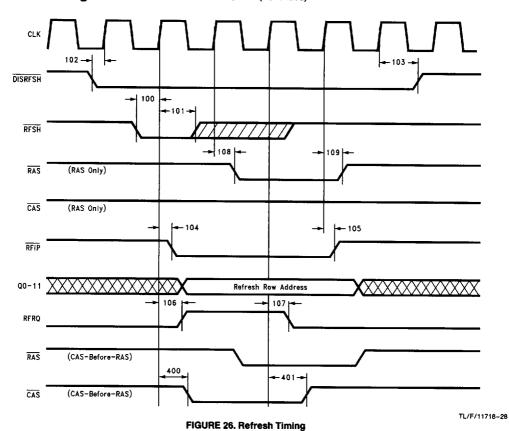

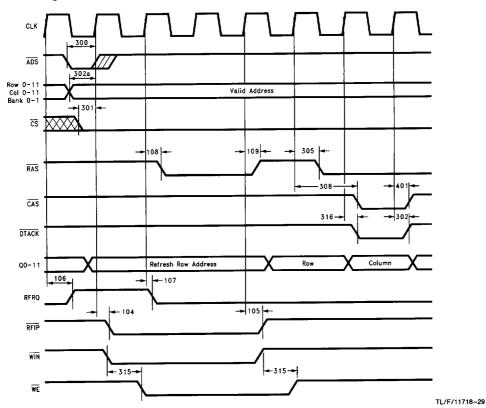

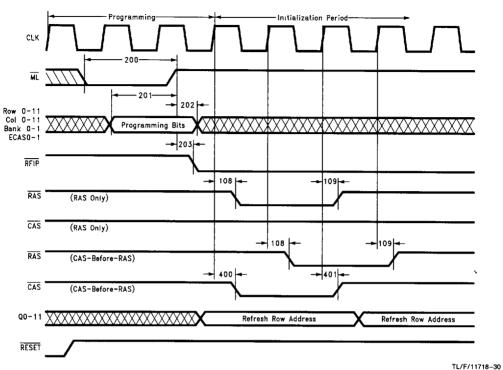

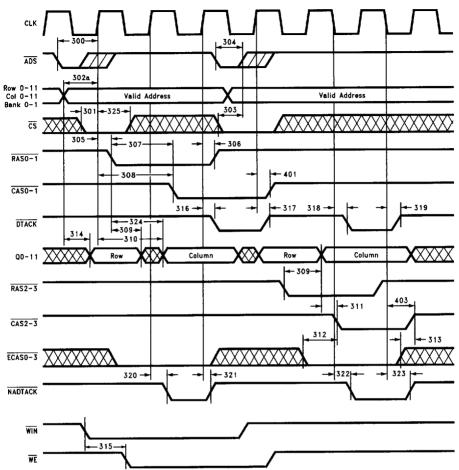

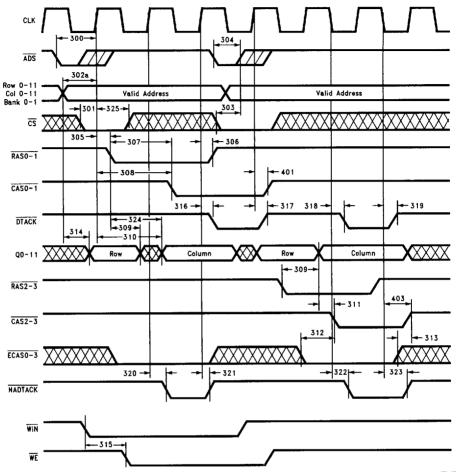

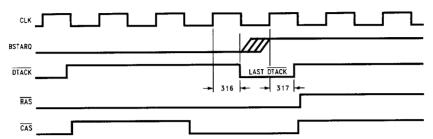

CLK and DECLK Timing Refresh Timing

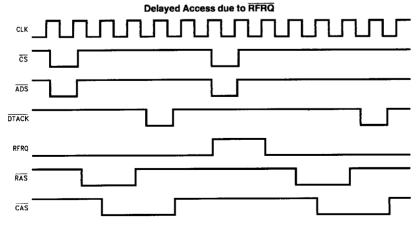

Refresh and Access Timing

Programming and Initialization Period Timing

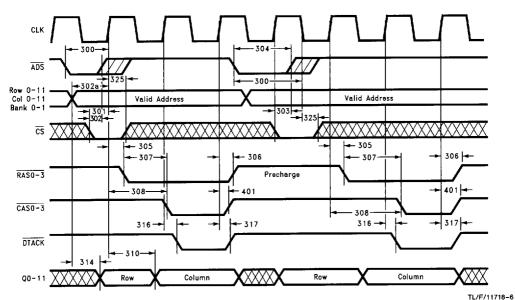

Normal Mode Access Timing

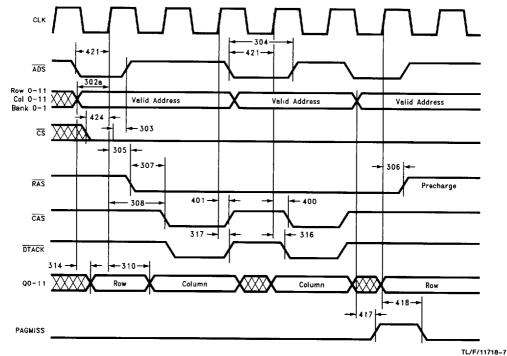

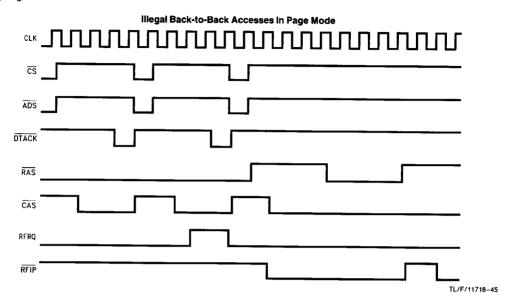

Page Mode Access Timing

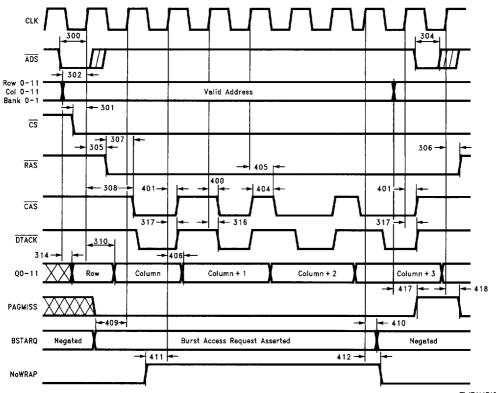

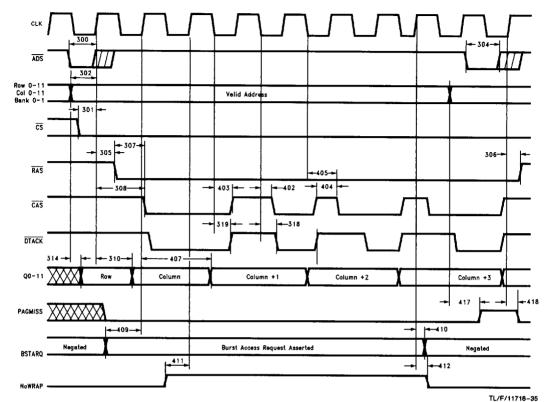

**Burst Mode Access Timing**

#### 13.0 ERRATA

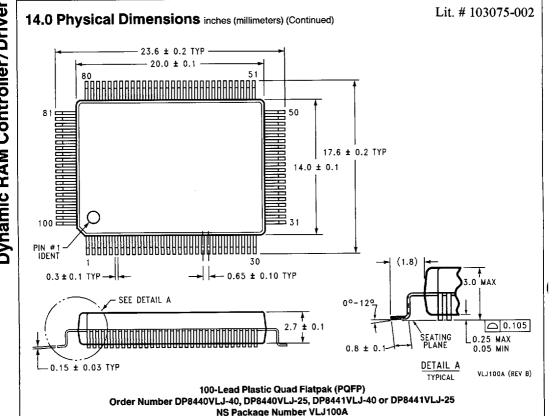

#### 14.0 PHYSICAL DIMENSIONS

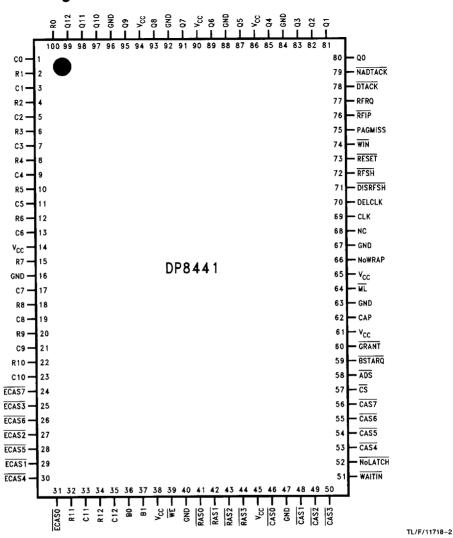

# 1.0 Connection Diagrams

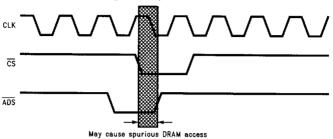

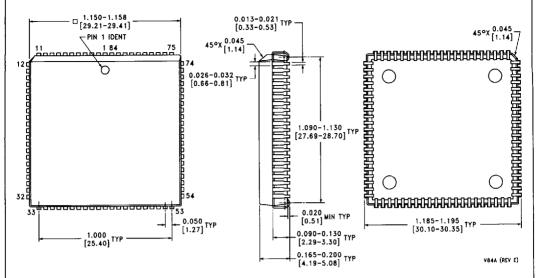

Top View FIGURE 2

Order Number DP8441VLJ-40 (40 MHz Operation), DP8441VLJ-25 (25 MHz Operation) See NS Package Number VLJ100A

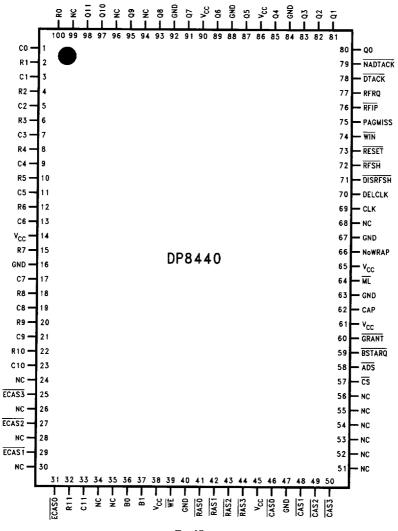

# 1.0 Connection Diagrams (Continued)

TL/F/11718-38

Top View FIGURE 3

Order Number DP8440VLJ-40 (40 MHz Operation), DP8440VLJ-25 (25 MHz Operation)

See NS Package Number VLJ100A

#### 1.0 Connection Diagrams (Continued) - NADTACK - DTACK C2 -13 R3 -- RFRQ - RFIP C3 -70 - PAGMISS R4 -16 - WIN 17 69 C4 — 68 - RESET R5 -- RFSH C5 -19 - DISRFSH R6 - 20 C6 - 21 - DELCLK DP8440 V<sub>CC</sub> → 22 - CLK R7 - 23 - GND GND - 24 62 - NoWRAP C7 - 25 - V<sub>CC</sub> - ML 60 C8 -27 59 - GND R9 -- 28 58 - CAP C9 - 29 - V<sub>CC</sub> - GRANT R10 - 30 C10 - 31 55 - BSTARO ECAS3 - 32 - ADS 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 C 2 3 40 41

**Top View** FIGURE 4

GND | RASS | RASS | RASS | CASS | CAS

TL/F/11718-3

Order Number DP8440V-40 (40 MHz Operation) See NS Package Number V84A

5

### 2.0 Functional Introduction

Reset and Programming: After the power up, the DP8440/41 must be reset and programmed before it can be used to access the DRAM. The chip is programmed through the address bus.

Initialization Period: After programming, the DP8440/41 enter a 60 ms initialization period. During this time the DP8440/41 perform refreshes to the DRAM. Further warm up cycles are unnecessary. The user must wait until the initialization is over to access the memory.

Modes of Operation: The DP8440/41 are synchronous DRAM controllers. Every access is synchronized to the system clock. The controllers can be programmed in Page Mode or Normal Mode. Burst accesses are dynamically requested through the input BSTARQ.

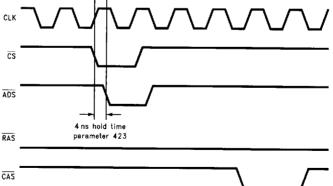

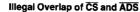

Opening Access: They involve a new row address. Regardless of the access mode programmed, opening accesses behave in the same way. ADS and CS initiate and qualify every access. After asserting the ADS, the DP8440/41 will assert RAS from the next rising edge of the CLK. The DP8440/41 will hold the row address on the DRAM address bus and guarantee that the row address is held for the Row Address Hold Time (t<sub>RAH</sub>) programmed. The DRAM controller will then switch the internal multiplexor to place the column address on the DRAM address bus and assert CAS. DTACK will wait the programmed number of wait states before asserting to indicate the end of the access.

**Normal Access:** If the controller is programmed in Normal Mode (B1 = 1),  $\overline{RAS}$  will assert and negate after the programmed  $\overline{RAS}$  low time. The user can perform burst access if desired.

Page Access: The DP8440/41 have an internal page comparator. This feature enables the user to do a series of accesses without negating RAS for as long as the row address remains unchanged. The user needs to provide a new address for every access. The page comparator can also be programmed as an input. This is beneficial for CPUs that have an internal page comparator. The user can do burst accesses while in page if desired.

Burst Access: These controllers can also generate new addresses to burst a specific number of locations. The user can choose to burst in a wrap around fashion for 2, 4, 8, 16 locations. Or, if the input NoWRAP is asserted, the controller will burst consecutive locations and the column address will not wrap around. The controller must be programmed in Latch Mode to generate the burst addresses.

Refresh Modes: The DP8440/41 can perform Automatic Internal Refreshes, or Externally Controlled Refreshes. During a long page access the controller can queue up to six refresh requests and burst refresh the addresses missed when the access finishes.

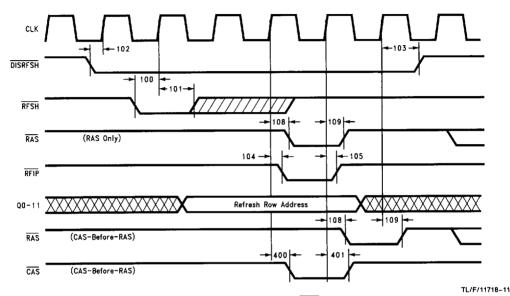

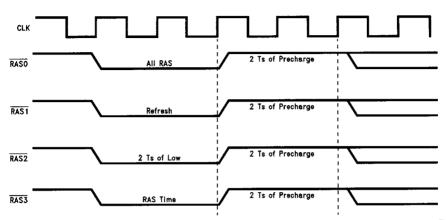

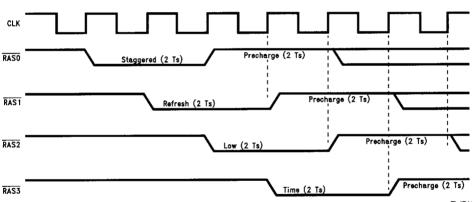

Refresh Types: The DP8440/41 can be programmed to do all RAS Refresh, Staggered Refresh, Error Scrubbing during Refresh or CAS-before-RAS refresh.

Wait Support: These controllers provide wait logic for all three types of accesses. The user needs to program the desired number of wait states for opening, page and burst accesses.

RAS and CAS Configurations: The RAS outputs can be programmed to drive one, two or four banks of memory and the CAS drivers can be programmed for byte writing in buses up to 64 bits wide.

TRI-STATE Outputs and Multiporting: The GRANT input can be used for multi-porting. When high this input will TRI-STATE the outputs, allowing another controller to drive the DRAM.

Other Features: Independent RAS precharge counters allow memory interleaving, thus back to back access to different memory banks is not delayed due to precharge.

The output NADTACK can be used to pipeline one address, getting the next access to start one clock early.

The input NoWRAP will increment the address during a burst access in a linear fashion. This is convenient for graphics or long page access.

**Terminology:** This paragraph explains the terminology used in this data sheet. The terms negated and asserted are used. For example, ECASO asserted means the ECASO input is at logic 0. The term NoWRAP asserted means that NoWRAP is at logic 1.

# 3.0 Signal Descriptions

# 3.1 ADDRESS AND CONTROL SIGNALS

| Pin<br>Name         | Device (if not<br>Applicable to All) | Input/<br>Output | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------|--------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R0-11<br>R0-12      | DP8440<br>DP8441                     | ı                | ROW ADDRESS: These inputs are used to specify the row address during an access to the DRAM. They are also used to program the chip when ML is asserted.                                                                                                                                                                                                                                                                                                        |

| C0-11<br>C0-12      | DP8440<br>DP8441                     | ı                | COLUMN ADDRESS: These inputs are used to specify the column address during an access to the DRAM. They are also used to program the chip when ML is asserted.                                                                                                                                                                                                                                                                                                  |

| B0-B1               |                                      | I                | BANK SELECT: Depending on programming, these inputs are used to select group RAS and CAS outputs to assert during an access. They are also used to program the chip when the ML is asserted.                                                                                                                                                                                                                                                                   |

| ECAS0-3<br>ECAS0-7  | DP8440<br>DP8441                     | ı                | ENABLE CAS: These inputs asserted enable a single or group of CAS outputs. In combination with the B0, B1 and the programming selection, these inputs select which CAS outputs will assert during an access. The ECAS signals can also be used to toggle a group of CAS outputs during page or burst mode accesses. They are also used to program the chip when ML is asserted.                                                                                |

| NoWRAP<br>(EXTNDRF) |                                      | l                | NO WRAP: Asserting this signal causes the column address to be incremented sequentially by one. The column address will not wrap around if NoWRAP is asserted. When RFIP is asserted, this signal is an EXTNDRF, used to extend refresh by any number of CLK periods until EXTNDRF is negated.                                                                                                                                                                 |

| NoLATCH             | DP8441                               | -                | COLUMN ADDRESS LATCH DISABLE: This input will disable ADS from latching the column address when Latch Mode is selected.                                                                                                                                                                                                                                                                                                                                        |

| ADS                 |                                      | _                | <b>ADDRESS STROBE:</b> This input starts every access. Depending on programming this input could latch the column address from the rising edge.                                                                                                                                                                                                                                                                                                                |

| cs                  |                                      | -                | CHIP SELECT: This input signal must be asserted to enable ADS to start an access.                                                                                                                                                                                                                                                                                                                                                                              |

| DTACK               |                                      | 0                | DATA TRANSFER ACKNOWLEDGE: This output can be programmed to insert wait states into a CPU access cycle. DTACK negated signifies a wait condition, when asserted signifies that the access has taken place. This signal can be delayed a number of positive or negative edges of clock. During burst accesses, DTACK transitions increment the column address.                                                                                                  |

| NADTACK             |                                      | 0                | <b>NEXT ADDRESS or EARLY DTACK:</b> This output asserts one clock cycle before DTACK. This output can be used to request the next address in a sort of pipelining fashion or it provides more time when DTACK needs to be generated externally.                                                                                                                                                                                                                |

| WAITIN              | DP8441                               | 1                | WAIT INPUT: This input asserted delays DTACK for one extra clock period.                                                                                                                                                                                                                                                                                                                                                                                       |

| GRANT               |                                      | l                | <b>MEMORY ACCESS GRANT:</b> The GRANT input functions as an output enable. If negated, it forces the outputs to a TRI-STATE condition.                                                                                                                                                                                                                                                                                                                         |

| PAGMISS             |                                      | 1/0              | PAGE MISS: When programmed as an output, this signal asserts when either the row or the bank address changes from the previous access cycle or the column address has been incremented beyond the page boundary. If this pin is programmed as an input, it is the responsibility of the system to tell the controller if the next access is within the page. Useful for CPUs with internal page comparators, PAGMISS is valid only if ADS and CS are asserted. |

| BSTARQ/<br>BSTARQ   |                                      | I                | <b>BURST ACCESS REQUEST:</b> This input enables the Burst Access Mode. This input can be programmed to be active high or active low.                                                                                                                                                                                                                                                                                                                           |

# 3.0 Signal Descriptions (Continued)

### 3.2 DRAM CONTROL SIGNALS

| Pin<br>Name      | Device (if not<br>Applicable to All) | input/<br>Output | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------|--------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Q0-11<br>Q0-12   | DP8440<br>DP8441                     | 0                | <b>DRAM ADDRESS:</b> These output signals are the multiplexed outputs of the R0–11/12 and C0–11/12 and form the DRAM address bus. These outputs contain the refresh address whenever $\overline{\text{RFIP}}$ is asserted. They have high capacitive drivers with 20 $\Omega$ s series damping resistors.                                                                                                                                                          |

| RAS0-3           |                                      | 0                | ROW ADDRESS STROBES: These outputs are asserted to latch the row address contained on the outputs Q0-11/12 into the DRAM. When RFIP is asserted, the RAS outputs are used to latch the refresh row address contained on the Q0-11/12 outputs into the DRAM. These outputs have high capacitive drivers with 20Ω series damping resistors.                                                                                                                          |

| CAS0-3<br>CAS0-7 | DP8440<br>DP8441                     | 0                | <b>COLUMN ADDRESS STROBES:</b> These outputs are asserted to latch the column address contained on the outputs Q0–11/12 into the DRAM. When RFIP is asserted and $\overline{\text{CAS}}$ -before- $\overline{\text{RAS}}$ refresh is selected, the $\overline{\text{CAS}}$ outputs will assert 1T (one clock period) before the $\overline{\text{RAS}}$ outputs are asserted. These outputs have high capacitive drivers with $20\Omega$ series damping resistors. |

| WE               |                                      | 0                | WRITE ENABLE: This output asserted specifies a write operation to the DRAM. When negated, this output specifies a read operation to the DRAM. This output has a high capacitive driver and a $20\Omega$ series damping resistor.                                                                                                                                                                                                                                   |

| WIN              |                                      | I                | WRITE ENABLE IN: This input is used to signify a write operation to the DRAM. The WE output will follow this input. Also, this input controls the precharge time for Read and Write during Burst Mode Access.                                                                                                                                                                                                                                                      |

### 3.3 REFRESH SIGNALS

| Pin<br>Name | Device (if not<br>Applicable to Ali) | Input/<br>Output | Description                                                                                                                                                                                                                                                                                                                                                         |

|-------------|--------------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

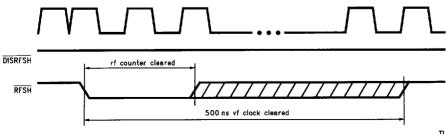

| RFRQ        |                                      | 0                | REFRESH REQUEST: When RFRQ is asserted, it specifies that 15 µs or 120 µs have passed. If DISRFSH is negated and the controller is not into an access cycle, the DP8440/41 will perform an internal refresh. If DISRFSH is asserted, RFRQ can be used to externally request a refresh by asserting the input RFSH.                                                  |

| RFIP        |                                      | 0                | REFRESH IN PROGRESS: This output is asserted prior to a refresh cycle and is negated when all the RAS outputs are negated for that refresh.                                                                                                                                                                                                                         |

| RFSH        |                                      | 1                | REFRESH: This input asserted with DISRFSH already asserted will request a refresh. If this input is continually asserted, the DP8440/41 will perform refresh cycles in a burst refresh fashion until the input is negated. If RFSH is asserted with DISRFSH negated, the internal refresh address counter is cleared. This technique is useful for burst refreshes. |

| DISRFSH     |                                      | ı                | DISABLE REFRESH: This input is used to disable internal refreshes and must be asserted when using RFSH for externally requested refreshes.                                                                                                                                                                                                                          |

# 3.4 RESET AND PROGRAMMING SIGNALS

| Pin<br>Name | Device (if not Applicable to All) | Input/<br>Output | Description                                                                                                                                                                                                                                                   |

|-------------|-----------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ML          |                                   | ı                | MODE LOAD: This input signal, when low, enables the internal programming register that stores the programming information.                                                                                                                                    |

| RESET       |                                   | l                | SYSTEM RESET: Reset forces the DP8440/41 to be set at a known state. V <sub>CC</sub> , CLK and DELCLK have to reach their proper DC and AC specifications for at least 1 ms before negating the RESET signal. All outputs are negated when RESET is asserted. |

# 3.0 Signal Descriptions (Continued)

# 3.5 CLOCK INPUTS

| Pin<br>Name | Device (if not<br>Applicable to All) | Input/<br>Output | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------|--------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK         |                                      | I                | SYSTEM CLOCK: This input may be in the range of 500 kHz to 40 MHz. This input is generally a constant frequency but it may be controlled externally to change frequencies for some arbitrary reason. This input provides the clock to the internal state machine that arbitrates between accesses and refreshes. This clock's positive edges and negative edges are used to extend the DTACK signal. This clock is also used as a reference for the RAS precharge time, the RAS low during refresh time and CAS precharge time.                                                                                                                                                                                                                                                                                                                                   |

| DELCLK      |                                      | ı                | DELAY LINE CLOCK: The clock input DELCLK, may be in the range of 10 MHz to 40 MHz and should be a multiple of 2 to have the DP8440/41 switching characteristics hold. If DELCLK is not one of the above frequencies, the accuracy of the internal delay line will suffer. This happens because the phase lock loop that generates the delay line assumes an input clock frequency multiple of 2 MHz.  For example, if DELCLK input is 17 MHz and we choose to divide by 8 (program bits C0-3), this will produce 2.125 MHz which is 6.25% off of 2 MHz. Therefore, the DP8440/41 delay line will produce delays that are shorter (faster delays) than intended. If divide by 9 was chosen, the delay line would produce longer delays (slower delays) than intended (1.89 MHz instead of 2 MHz). This clock is also divided to create the internal refresh clock. |

### 3.6 POWER SIGNALS AND CAPACITOR INPUT

| Pin<br>Name     | Device (if not<br>Applicable to All) | Input/<br>Output | Description                                                                                                                                                                                    |

|-----------------|--------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub> |                                      | ı                | POWER: Supply Voltage.                                                                                                                                                                         |

| GND             |                                      | ı                | GROUND: Supply Voltage Reference.                                                                                                                                                              |

| CAP             |                                      | I                | <b>CAPACITOR:</b> This input is used by the internal PLL for stabilization. The value of the ceramic capacitor should be 0.1 $\mu$ F and it should be connected between this input and ground. |

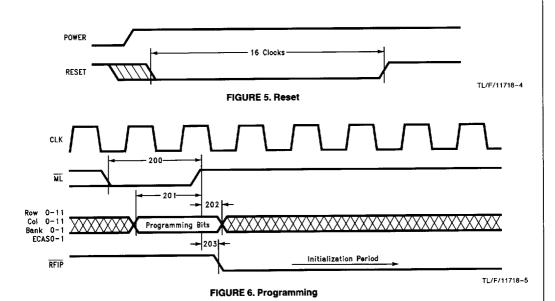

# 4.0 Programming and Resetting

#### 4.1 RESET

After power up, the DP8440/41 must be reset and programmed before it can be used to access the DRAM. Reset is accomplished by asserting the input  $\overline{\text{RESET}}$  for at least 16 positive edges of CLK after V<sub>CC</sub> stabilizes. After reset, the part can be programmed.

#### **4.2 PROGRAMMING**

Programming is accomplished by presenting a valid programming selection on the row, column, bank selects and  $\overline{\text{ECAS}}$  inputs and toggling the  $\overline{\text{ML}}$  input from low to high.

When  $\overline{\text{ML}}$  goes high the part is programmed. After the first programming after a reset the part will enter a 60 ms initialization period. During this period the controller will refresh the memory, so further DRAM warm up cycles are not necessary. The user can program the part on the fly by pulsing  $\overline{\text{ML}}$  low and high (provided that no refresh is in progress) while a valid programming selection is on the address bus. The part will not enter the initialization period when it is only re-programmed.

|           | AND PREC | HARGE TIN |

|-----------|----------|-----------|

| R1        | R0       |           |

| 0         | 0        | 2T        |

| 0         | 1        | 3T        |

| 1         | 0        | 4T        |

| 1         | 1        | 5T        |

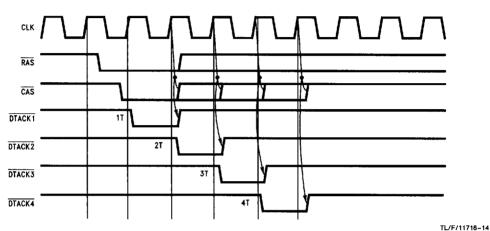

| TACK DUI  | RING OPE | NING ACCE |

| R3        | R2       | T         |

| 0         | 0        | 1T        |

| Ō         | 1        | 2T        |

| 1         | 0        | 3T        |

| 1         | 1        | 4T        |

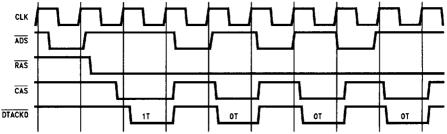

| TACK DUI  | RING BUF | ST ACCESS |

| R5        | R4       |           |

| 0         | 0        | от        |

| 0         | 1        | 1T        |

| 1         | 0        | 2T        |

| 1         | 1        | 3T        |

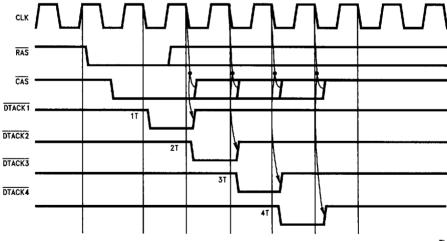

| TACK DU   | RING PAG | E ACCESS  |

| R7        | R6       |           |

| 0         | 0        | OT.       |

| 0         | 1        | 1T        |

| 1         | 0        | 2T        |

| 1         | 1        | зт        |

| PAGE SIZE | SELECT   | ,         |

| R9        | R8       | 1         |

| 0         | 0        | 512       |

| 0         | 1        | 1024      |

| 1         | 0        | 2048      |

| 1         | 1        | 4096      |

| WRAP ARO  |          | •         |

| R11       | R10      | _         |

| 0         | 0        | 2         |

| 0         | 1        | 4         |

| 1<br>1    | 0<br>1   | 8<br>16   |

| '         |          | 10        |

| 1         | 1        | I         |

|       |          |         |                    |          | (          | Continued)       | <del></del>       |                     |     |                                       |                                        |

|-------|----------|---------|--------------------|----------|------------|------------------|-------------------|---------------------|-----|---------------------------------------|----------------------------------------|

| IVISO |          |         |                    |          |            |                  |                   |                     |     | -                                     |                                        |

| C3    | C2       | C1      | CO                 |          |            |                  |                   |                     |     |                                       |                                        |

| 0     | 0        | 0       | 0<br>1             | 20<br>19 |            |                  |                   |                     |     |                                       |                                        |

| 0     | 0        | 1       | o                  | 18       |            |                  |                   |                     |     |                                       |                                        |

| Ö     | o        | 1       | 1                  | 17       |            |                  |                   |                     |     |                                       |                                        |

| 0     | 1        | Ö       | Ö                  | 16       |            |                  |                   |                     |     |                                       |                                        |

| 0     | 1        | 0       | 1                  | 15       |            |                  |                   |                     |     |                                       |                                        |

| 0     | 1        | 1       | 0                  | 14       |            |                  |                   |                     |     |                                       |                                        |

| 0     | 1        | 1       | 1                  | 13       |            |                  |                   |                     |     |                                       |                                        |

| 1     | 0        | 0       | 0                  | 12       |            |                  |                   |                     |     |                                       |                                        |

| 1     | 0        | 0       | 1                  | 11       |            |                  |                   |                     |     |                                       |                                        |

| 1     | 0        | 1       | 0                  | 10       |            |                  |                   |                     |     |                                       |                                        |

| 1     | 0        | 1<br>0  | 1 0                | 8        |            |                  |                   |                     |     |                                       |                                        |

| 1     | 1        | 0       | 1                  | 7        |            |                  |                   |                     |     |                                       |                                        |

| 1     | 1        | 1       | Ö                  | 6        |            |                  |                   |                     |     |                                       |                                        |

| 1     | 1        | 1       | 1                  | 5        |            |                  |                   |                     |     |                                       |                                        |

| RAS   | AND      | CAS C   | ONFIG              | URATIO   | ONS        | AND REF          | RESH BEHAVIOR     | l                   |     |                                       |                                        |

| 5 C4  |          | -       |                    |          |            |                  |                   |                     |     |                                       |                                        |

| 0     | All F    | AS and  | all CA             | S are se | elect      | ed. B0 and       | B1 are not used.  | All RAS refresh.    |     |                                       |                                        |

|       |          |         |                    |          |            |                  |                   |                     |     |                                       |                                        |

| ) 1   | ا ا      | C6 = C  | Non E              | rror     | В1         | B0 is            | not Used          | If C6 = 1 Error     | В1  |                                       | B0 is Not Used                         |

| , ,   | 1 1      |         |                    | ted. All |            |                  | 31101 0300        | Scrubbing Selected. |     | · · · · · · · · · · · · · · · · · · · | and CAS0-1, CAS4-                      |

|       |          |         | ected. 2           |          | 1          | RAS0-1<br>RAS2-3 |                   | All RAS Refresh.    | 1   |                                       | and CAS2-1, CAS4-<br>and CAS2-3, CAS6- |

|       | s        | aggere  | d Refre            | sh.      | <b>'</b> ' | NA32-3           |                   | CAS Pairs Selected. |     | 111/02-0                              | and 0A02-0, 0A00-                      |

|       | -        |         |                    |          | 1          | I                |                   | L.,                 | ·   | •                                     |                                        |

|       | ╁        |         |                    |          |            |                  |                   |                     |     |                                       |                                        |

|       | [        |         |                    |          | -          |                  |                   | If C6 = 1 Error     | В1  | В0                                    |                                        |

| 1 0   | 1 1      |         | Non E              |          | B1         | B0               |                   | Scrubbing Selected. | _   | Т                                     | T                                      |

|       | 1 1      |         | g Selec<br>Selecte |          | 0          | 0                | RAS0              | All RAS Refresh.    | ١ ٠ | 0                                     | RASO, CASO-4                           |

|       | , ,      |         | taggere            |          | 0          | 1                | RAS1              | CAS Pairs           | 0   | 1                                     | RAS1, CAS1-5                           |

|       | 1 1      | efresh. | uggo. c            | •        | 1 1        | 0                | RAS2              | Selected.           | 1   | 0                                     | RAS2, CAS2-6<br>RAS3, CAS3-7           |

|       | Ľ        |         |                    |          | 1          | 1                | RAS3              |                     | ٠,  | <u> </u>                              | nA33, CA33-7                           |

|       |          |         |                    |          |            |                  |                   |                     |     |                                       | <del>.</del> .                         |

|       |          |         |                    |          | _          |                  | <del></del> -     |                     | F   |                                       |                                        |

| 1 1   | If       | C6 = 0  | Non E              | rror     | В1         | B0 is            | not used.         | If C6 = 1 Error     | B1  |                                       | B0 is not used.                        |

|       | 1 1      |         | g. 2-Ste           | -        | 0          | RAS0-1 a         | nd CAS0,1,4,5     | Scrubbing Selected. | 0   | RAS0-1                                | and CAS0,1,4,5                         |

|       |          |         | d Refre            |          | 1          | 1                | nd CAS2,3,6,7     | All RAS Refresh.    | 1   | RAS2-3                                | and CAS2,3,6,7                         |

|       | c        | AS Pair | s Selec            | ted.     |            |                  |                   | CAS Pairs Selected. |     |                                       |                                        |

|       | _        |         |                    |          |            |                  |                   |                     |     |                                       |                                        |

| 2BVE  | <br>  QC | IIRRIN  | G MOD              | E SELE   | СТ         |                  |                   |                     |     |                                       |                                        |

|       | JUH      | JUDIN   | G MOD              | _ JELE   | - V I      |                  |                   |                     |     |                                       |                                        |

| C6    |          | I D -   | .f., .h. /l        | Nam For  | C          |                  |                   |                     |     |                                       |                                        |

|       |          |         |                    |          |            | crubbing)        | lo Staggered Ref  | resh)               |     |                                       |                                        |

| 1 1   |          | いいいいい   | UVII DI            | しついっしゃ   |            | -, 170 and 1     | io olaggered itel | · •••••             |     |                                       |                                        |

**.** 6501128 0080206 551 📟

|            | Jramming<br>OGRAMMING SI |              | 40/41 (Continued) ontinued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|--------------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ROW ADD    | PRESS HOLD TI            | ME SELECT t  | RAH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| C7         |                          |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0          | 10 ns<br>15 ns           |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|            | INPUT OR OUT             | DIIT SEI ECT |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| C8         | 114701011001             | FOI SELECT   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0          | Input                    |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1          | Output                   |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CAS PRE    | CHARGE DURIN             | IG BURST     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| C9         | Read Cycle               | Write Cycle  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0<br>1     | 1½T<br>1T                | 1T<br>2T     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|            | MODE SELECT              |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| C10        | MODE GELEG               | !            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0          | RAS Only Refr            | esh          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1_         | CAS-before-R/            | AS Refresh   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |