# LC<sup>2</sup>MOS Complete Embedded Servo Front Ends for HDD

# AD7773/AD7775\*

#### **FEATURES**

10-Bit, 3 μs ADC

Two DACs with Output Amplifiers

One 10-Bit, 4 μs Settling DAC

One 8-Bit, 3 μs Settling DAC

Fully Integrated Burst Demodulator

Power-Down Mode

+5 V Only

Fast Interface Port

28-Pin SOIC Package

APPLICATIONS

Embedded Serve For HDD

Combined Dedicated/Embedded Servo

GENERAL DESCRIPTION

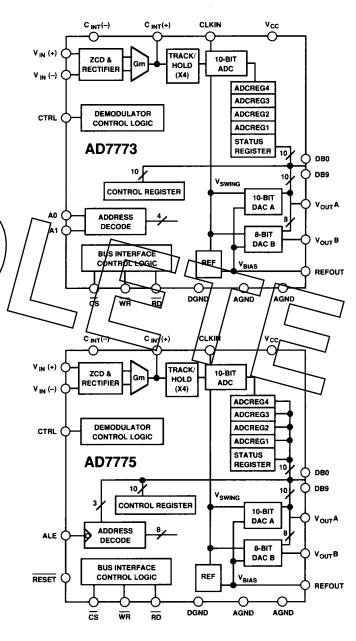

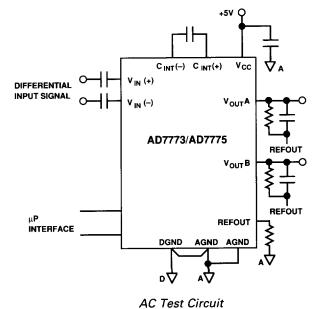

The AD 7773 and AD 7775 provide all the functionality accessary to implement the servo demodulator and head positioning tasks in embedded servo systems. A power down mode which turns all the linear circuitry OFF enhances the use of the AD 7773 and AD 7775 in portable systems.

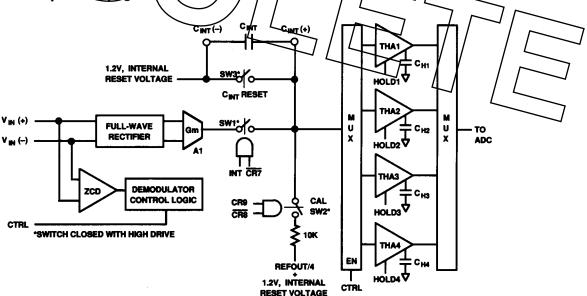

The demodulator channel can capture high speed servo data from a variety of embedded servo patterns. Up to four sequential servo burst signals can be synchronously demodulated, full-wave rectified and integrated. At the end of a burst period the integrated output voltage, representing the amplitude of a captured burst, is sampled and held on one of four internal track/hold amplifiers prior to conversion. After conversion the digitized burst signals from the ADC are fed to four 10-bit wide data registers.

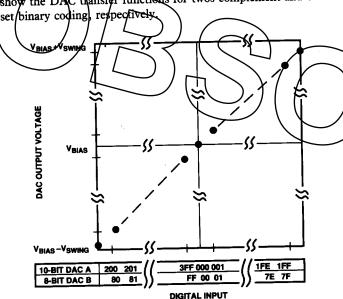

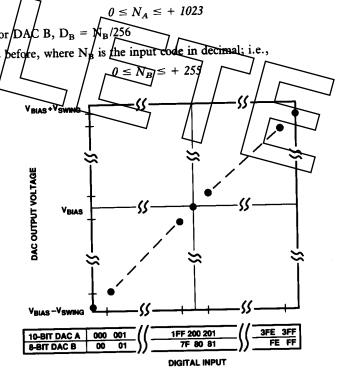

The AD7773 and AD7775 also contain two independent voltage-output DACs: one with 10-bit resolution and one with 8-bit resolution. The two DACs produce output signals of the form  $V_{\rm BIAS} \pm V_{\rm SWING}$  where  $V_{\rm BIAS}$  and  $V_{\rm SWING}$  are internally generated on-chip. The  $V_{\rm BIAS}$  signal is available externally on the REFOUT pin.

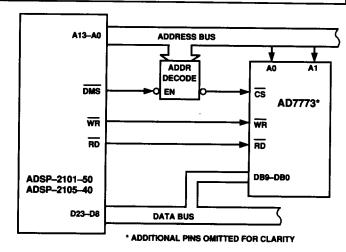

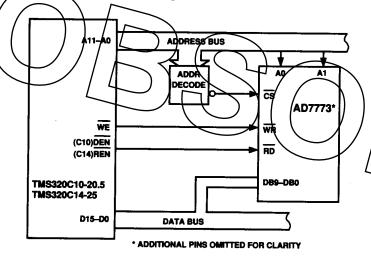

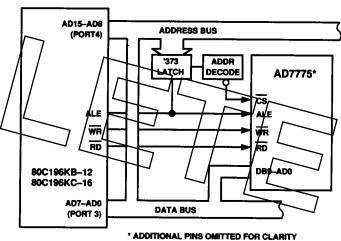

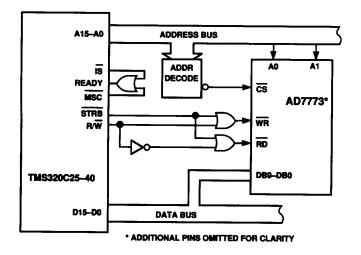

The devices are easily interfaced to popular DSP processors and microcontrollers. The AD7773 has a 10-bit data port with separate address pins. The AD7775 has a 10-bit multiplexed address/data bus with an ALE input to latch the address.

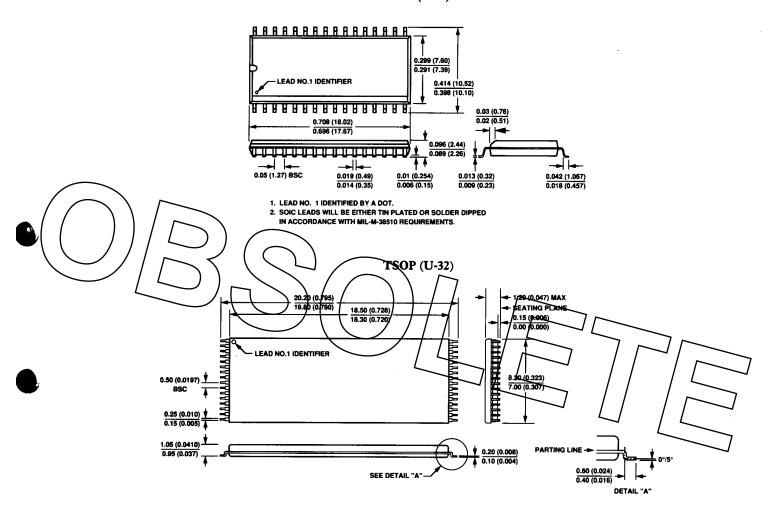

The AD7773 and AD7775 are fabricated in linear compatible CMOS (LC<sup>2</sup>CMOS), an advanced, mixed technology process that combines precision bipolar circuits with low power CMOS logic. The devices are available in 28-pin SOIC packages and 32-pin TSOPs.

\*Protected by U.S. Patent No. 4,990,916.

#### **FUNCTIONAL BLOCK DIAGRAMS**

#### REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 Fax: 617/326-8703 Twx: 710/394-6577

Telex: 924491 Cable: ANALOG NORWOODMASS

# AD7773/AD7775 — SPECIFICATIONS $(V_{CC} = +5 \text{ V} \pm 5\%; \text{AGND} = \text{DGND} = 0 \text{ V}; \text{CLKIN} = 6.67 \text{ MHz};$ $C_{INT} = 200 \text{ pF; Burst Frequency} = 5 \text{ MHz; Cycles Integrated} = 4. \text{ All specifications } T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise stated.})$

| Parameter                                         | J Version <sup>1</sup>      |                      | Conditions/Comments                                          |

|---------------------------------------------------|-----------------------------|----------------------|--------------------------------------------------------------|

| DEMODULATOR CHANNEL                               |                             |                      | All AC Test Waveforms are Sinusoidal. Minimum                |

| DEMODULATION CHARACT                              |                             |                      | Signal Frequency Is 2 MHz.                                   |

| ADC Resolution                                    | 10                          | Bits                 | -                                                            |

| Demodulator Channel Gain, G <sub>CH</sub>         | 7 -                         | LSB/V p-p min        | Channel Gain is (384 ± 32) LSB/V p-p                         |

| Demodulator Chamier Cam, CH                       |                             | LSB/V p-p max        |                                                              |

| Intercept of Transfer Function on                 |                             |                      |                                                              |

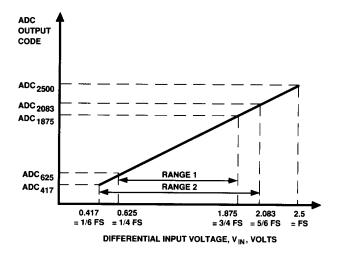

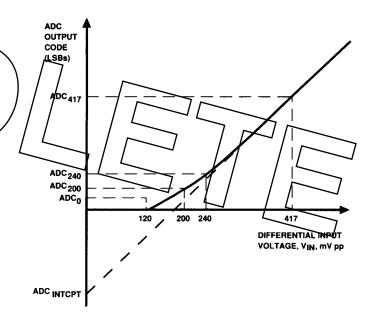

| ADC Code Axis, ADC <sub>INTCPT</sub>              | -137/+35                    | LSB min/max          | See Terminology & Figure 19                                  |

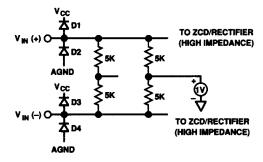

| Differential Input Resistance                     | 4/6.5                       | kΩ min/max           | Typically 5 kΩ; Measured at DC; See Terminology              |

| Differential Input Capacitance <sup>2</sup>       | 1/4                         | pF min/max           |                                                              |

| Common-Mode Input Resistance                      |                             | kΩ min/max           | Typically 2.5 kΩ; Measured at DC; See Terminology            |

| Common-Mode Input Capacitance <sup>2</sup>        | 5/15                        | pF min/max           |                                                              |

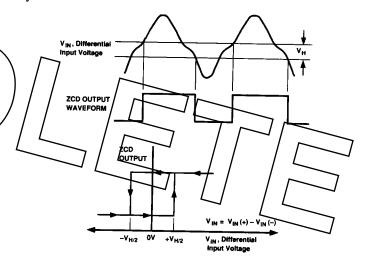

| ZCD Differential Hysteresis, V <sub>H</sub>       | 40/120                      | mV p–p min/max       | Typically 55 mV; See Figure 20 under Design                  |

| 202 21101 111111 21,                              | l                           |                      | Information                                                  |

| Frequency Response to Pulse Harmonics             |                             |                      |                                                              |

| 2pd Harmonics                                     | ±10                         | % typ                | See Terminology                                              |

| Brd Harmonids                                     | 1                           | % typ                |                                                              |

| Common-Mode Rejection Ratio <sup>2</sup>          | 1."                         | dB min               | See Terminology                                              |

| Power Supply Rejection Ratio                      | 7 \                         | dB min               | See Terminology                                              |

| Channel Noise Level <sup>2</sup>                  | 42 ( )                      | dB min               | See Terminology                                              |

| Composite Noise Rejection <sup>2</sup>            | 38                          | dB min               | Referenced to Half-Scale; See Terminology                    |

| V <sub>IN</sub> , Differential Input Signal Range | $\backslash \backslash / /$ | \ \\\\               |                                                              |

| for Guaranteed Positive Slope                     | 0.24/2.26                   | V p-p min/max/       | See Terminology                                              |

| ADC Code for 0 mV p-p                             | $\sim$ $/$ $\sim$           |                      |                                                              |

| Differential Input Voltage, ADC <sub>0</sub>      | +35                         | LSB max /            | See Figure 19                                                |

| ADC Code for 240 mV p-p                           |                             |                      | A - a - a la - a - a - a - a - a - a - a                     |

| Differential Input Voltage, ADC <sub>240</sub>    | $ADC_{200} + 4$             | LSB min              | ADC 200 Is ADC Code for 200 my p-p Differential              |

|                                                   |                             | _                    | Input Voltage                                                |

| ADC Code for 417 mV p-p                           |                             |                      |                                                              |

| Differential Input Voltage, ADC <sub>417</sub>    | $ADC_0 + 10$                | LSB min              |                                                              |

| ADC Code for 2260 mV p-p                          | 1                           |                      | ADC Is ADC Code for 2500 mV m in Differential                |

| Differential Input Voltage, ADC <sub>2260</sub>   | $ADC_{2500} - 4$            | LSB min              | ADC <sub>2500</sub> Is ADC Code for 2500 mV p-p Differential |

|                                                   |                             |                      | Input Voltage                                                |

| ADC Code for 2500 mV p-p                          | 1022                        | I CD                 |                                                              |

| Differential Input Voltage, ADC <sub>2500</sub>   | 1022                        | LSB max              |                                                              |

| Voltage Change Across C <sub>INT</sub> for        | DEFOITE/2                   | X7 +                 |                                                              |

| Full-Scale ADC Range                              | REFOUT/2                    | V typ                |                                                              |

| Gm, Transconductance from V <sub>IN</sub> to      | 0.277/0.207                 |                      |                                                              |

| $I_{OUT}$ at $C_{INT}(+)$                         | 0.277/0.306                 | mS min/max           | 0.625 V to 1.875 V; See Terminology                          |

| Relative Accuracy                                 | ±4                          | LSB max              | 0.417 V to 2.083 V                                           |

|                                                   | ±8                          | LSB max              | Guaranteed Monotonic to 9 Bits; See Terminology              |

| Differential Nonlinearity                         | -1.3/+2                     | LSB max<br>LSB max   | Measured at Half-Scale; See Terminology                      |

| Channel Mismatch                                  | 10                          | LSB max              | See Terminology                                              |

| Crosstalk Between Bursts                          | 5                           |                      | Per Captured Burst; See Terminology                          |

| ADC Conversion Time                               | 14 T <sub>CLKIN</sub>       | μs max<br>μs min/max | Period of Input Clock CLKIN                                  |

| T <sub>CLKIN</sub>                                | 0.15/0.5                    | 1.                   | Minimum High Time for CLKIN                                  |

| T <sub>CLKIN</sub> High <sup>2</sup>              | 60                          | ns min               | Minimum Low Time for CLKIN                                   |

| T <sub>CLKIN</sub> Low <sup>2</sup>               | 60                          | ns min               | THE TOTAL PROPERTY.                                          |

| Output Coding                                     | Unipolar Binary             |                      |                                                              |

| ANALOG OUTPUTS <sup>3</sup>                       |                             | <u></u>              | Applies to Both DACs                                         |

| Output Voltage Range                              | $V_{BIAS} - V_{SWING}$      | <sub>s</sub>  V min  |                                                              |

| •                                                 | $V_{BIAS} + V_{SWING}$      | V max                | , m · ·                                                      |

| Digital-to-Analog Glitch Impulse <sup>2</sup>     | 15                          | nV sec typ           | See Terminology                                              |

| Digital Feedthrough <sup>2</sup>                  | 1                           | nV sec typ           | See Terminology                                              |

| DC Output Impedance <sup>2</sup>                  | 5                           | $\Omega$ max         | Typically $0.5 \Omega$                                       |

| Short-Circuit Current <sup>2</sup>                | 20                          | mA max               | See Terminology                                              |

| Power Supply Rejection Ratio <sup>2</sup>         | 20                          | dB min               | See Terminology                                              |

| Input Coding                                      | Offset Binary/2s            | Complement           | Programmable via Location CR6 of the Control                 |

| •                                                 | I                           | i                    | Register                                                     |

| Parameter                                                                                                                                                                                                        | J Version <sup>1</sup> | Units                              | Conditions/Comments                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------|

| ANALOG OUTPUTS <sup>3</sup> (Continued)                                                                                                                                                                          |                        |                                    |                                                                                                       |

| DAC A                                                                                                                                                                                                            |                        |                                    |                                                                                                       |

| Resolution                                                                                                                                                                                                       | 10                     | Bits                               |                                                                                                       |

| Output Voltage Settling Time <sup>2</sup>                                                                                                                                                                        | 4                      | μs max                             | Settling Time to Within ±1/2 LSB of Final Value;<br>Typically 2.0 μs                                  |

| Relative Accuracy                                                                                                                                                                                                | ±1                     | LSB max                            |                                                                                                       |

| Differential Nonlinearity                                                                                                                                                                                        | ±1                     | LSB max                            | Guaranteed Monotonic                                                                                  |

| Bias Offset Error                                                                                                                                                                                                | ±20                    | LSB max                            |                                                                                                       |

| Plus or Minus Full-Scale Error                                                                                                                                                                                   | ±16                    | LSB max                            | Referenced to REFOUT/2                                                                                |

| DAC B                                                                                                                                                                                                            |                        |                                    |                                                                                                       |

| Resolution 2                                                                                                                                                                                                     | 8                      | Bits                               | 0 1' TT' WY'LL A 10 T OD 0 TT                                                                         |

| Output Voltage Settling Time <sup>2</sup>                                                                                                                                                                        | 3                      | μs max                             | Settling Time to Within ±1/2 LSB of Final Value;<br>Typically 2.0 μs                                  |

| Relative Accuracy                                                                                                                                                                                                | ±1                     | LSB max                            |                                                                                                       |

| Differential Nonlinearity                                                                                                                                                                                        | <u>±1</u>              | LSB max                            | Guaranteed Monotonic                                                                                  |

| Bias Offset Error                                                                                                                                                                                                | ±6                     | LSB max                            | n 4 1 nmovem                                                                                          |

| Plus or Minus Full-Scale Error                                                                                                                                                                                   | ±6                     | LSB max                            | Referenced to REFOUT/2.                                                                               |

| LOGIC INPUTS/  CS, WR, RD, CTRL, CLKIN,  RESET & ALE (AD7775),  A0 & A1 (AD7773)  Input Low Voltage, V <sub>INI</sub> Input High Voltage, V <sub>INI</sub> Input Leakage Current  Input Capacitance <sup>2</sup> | 0.8<br>3.4<br>10<br>10 | V max<br>V min<br>µA max<br>pF max |                                                                                                       |

| LOGIC OUTPUTS DB0-DB9 (AD7773) AD0-DB9 (AD7775) V <sub>OL</sub> , Output Low Voltage V <sub>OH</sub> , Output High Voltage Floating State Leakage Current Floating State Capacitance <sup>2</sup>                | 0.4<br>4.0<br>10       | V max<br>V min<br>µA max<br>pF max | $I_{SINK} = 1.6 \text{ mA}$ $I_{SOURCE} = 200 \mu\text{A}$                                            |

| POWER REQUIREMENTS                                                                                                                                                                                               |                        |                                    |                                                                                                       |

| V <sub>CC</sub> Range                                                                                                                                                                                            | 4.75/5.25              | V min/V max                        | For Specified Performance                                                                             |

| I <sub>CC</sub> , Normal Mode <sup>4</sup>                                                                                                                                                                       | 30                     | mA max                             | Control Register Locations CR8 = CR9 = Logic High                                                     |

| I <sub>CC</sub> , Power Down Mode <sup>5</sup>                                                                                                                                                                   | 1.5                    | mA max                             | Control Register Locations CR8 = Logic High,<br>CR9 = Logic Low; All Linear Circuitry OFF             |

| Power-Up Time to Operational                                                                                                                                                                                     |                        |                                    |                                                                                                       |

| Specifications <sup>2</sup>                                                                                                                                                                                      | 500                    | μs max                             | From Power Down Mode                                                                                  |

| DAC REFERENCE INPUTS                                                                                                                                                                                             |                        |                                    |                                                                                                       |

| V <sub>BIAS</sub> for both DACs                                                                                                                                                                                  | REFOUT                 | V                                  | Internally Connected. Available Externally on REFOUT Pin                                              |

| V <sub>SWING</sub> for both DACs                                                                                                                                                                                 | REFOUT/2               | $ \mathbf{v} $                     | Internally Connected                                                                                  |

| REFERENCE OUTPUT <sup>6</sup>                                                                                                                                                                                    |                        |                                    |                                                                                                       |

| REFOUT                                                                                                                                                                                                           | 2.1/2.2                | V min/max                          |                                                                                                       |

| Reference Load Change                                                                                                                                                                                            | ±3                     | mV max                             | For Reference Load Current Change of 0 to ±500 µA                                                     |

|                                                                                                                                                                                                                  | ±5                     | mV max                             | For Reference Load Current Change of 0 to ±2 mA<br>Reference Load Should Not Change During Conversion |

#### NOTES

<sup>&</sup>lt;sup>1</sup>Temperature range as follows: J Version: 0°C to +70°C.

<sup>&</sup>lt;sup>2</sup>Guaranteed by design, not production tested.

<sup>3</sup>Output load of 10k||100 pF is referenced to REFOUT.

Output total of tokillow pr is referenced to REPOUT.

Input signal levels are as follows:  $V_{INL} = 0.85 \text{ V}$ ,  $V_{INH} = 2.35 \text{ V}$ ;  $\overline{CS} = \overline{WR} = \overline{RD} = \overline{RESET}$  (AD7775 only) = A0, A1 (AD7773 only) =  $V_{INH}$ ; ALE (AD7775 Only) = CTRL =  $V_{INL}$ ; CLKIN = 6.67 MHz at 50% Mark-Space ratio between  $V_{INL}$  &  $V_{INH}$ ; no conversion in progress and data bus, DB0-DB9 (AD7773 Only), AD0-DB9 (AD7775 only), tied to 0 V.

Input signal levels are as follows:  $V_{INL}$  = 0 V,  $V_{INH}$  =  $V_{CC}$ ;  $\overline{CS} = \overline{WR} = \overline{RD} = \overline{RESET}$  (AD7775 only) = A0, A1 (AD7773 Only) =  $V_{INH}$ ; ALE (AD7775 only) = CTRL = CLKIN =  $V_{INL}$ ; data bus, DB0-DB9 (AD7773 only), AD0-AD9 (AD7775 only) tied to 0 V.

<sup>&</sup>lt;sup>6</sup>For capacitive loads greater than 100 pF a series resistor is required.

Specifications subject to change without notice.

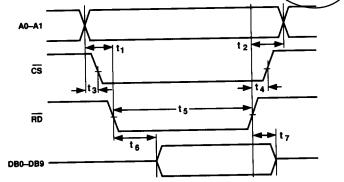

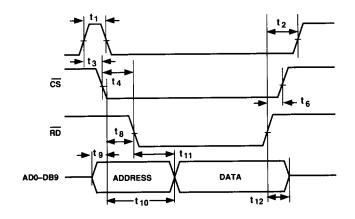

# INTERFACE TIMING CHARACTERISTICS — AD7773 $^{1,\ 2}$ ( $v_{cc}=\pm 5\ v\pm 5\%$ ; agnd = Dgnd = 0 V)

| Parameter                                                                                                                                                                                                                                                                                                            | Label                                                                                                    | Limit at T <sub>MIN</sub> , T <sub>MAX</sub>          | Units                                                                 | Test Conditions/Comments        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------|---------------------------------|

| INTERFACE TIMING  Address Setup to WR or RD Falling Edge  Address Hold after WR or RD Rising Edge  Address Setup to CS Falling Edge  WR or RD Rising Edge to CS Rising Edge  WR or RD Pulse Width  CS or RD Active to Valid Data <sup>3</sup> Bus Relinquish Time after RD <sup>4</sup> Data Valid to WR Rising Edge | t <sub>1</sub> t <sub>2</sub> t <sub>3</sub> t <sub>4</sub> t <sub>5</sub> t <sub>6</sub> t <sub>7</sub> | 4<br>0<br>9<br>0<br>53<br><b>60</b><br>10<br>22<br>55 | ns min ns min ns min ns min ns min ns min ns max ns min ns max ns min | Timed from Whichever Occurs Las |

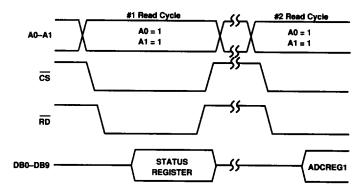

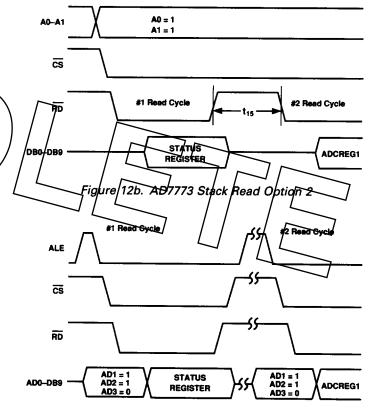

| Data Valid after WR Rising Edge Delay Time Retween Stack Reads                                                                                                                                                                                                                                                       | t <sub>9</sub>                                                                                           | 100                                                   | ns min                                                                | See Figure 12b                  |

See Figures 1 and 4.

Training Specifications in bold print are 100% production tested. All other times are sample tested at +25°C to ensure compliance. All input signals are specified with tr = tr = 5 ns (10% to 90% of 5 V) and timed from a voltage level of 1.6 V.

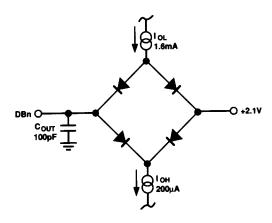

This measured with the load circuit of Figure 3 and defined as the time required for an output to cross 0.8 V or 2.4 V.

This measured with the load circuit of rigure v and defined as the time requires for an output to cross 0.8 v or 2.4 v.

4t<sub>7</sub> is derived from the measured time taken by the data outputs to charge 0.5 V when loaded with the circuit of Figure 3. The measured time is then extrapolated back to remove the effects of charging of discharging the 100 pF capacitor. This means that the time t<sub>7</sub> quoted above is the true bus relinquish time of the device and, as such, is independent of the external bus loading capacitance.

the device and, as such, is independent of the external bus loading capacitance. Specifications subject to change without notice.

Figure 1. Read Cycle Timing for AD7773 Interface

Figure 2. Write Cycle Timing for AD7773 Interface

Figure 3. Load Circuit for Bus Timing Characteristics

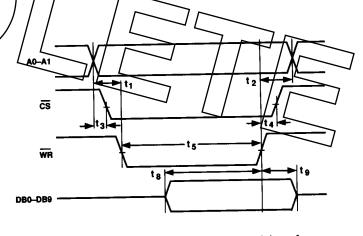

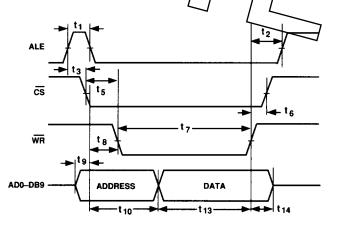

# INTERFACE TIMING CHARACTERISTICS — AD7775 $^{1,~2}$ ( $v_{cc} = +5$ v $\pm$ 5%; agnd = dgnd = 0 v)

| Parameter                                 | Label           | Limit at<br>T <sub>MIN</sub> to T <sub>MAX</sub> | Units  | Test Conditions/Comments    |

|-------------------------------------------|-----------------|--------------------------------------------------|--------|-----------------------------|

| INTERFACE TIMING                          |                 |                                                  |        |                             |

| ALE Pulse Width                           | t <sub>1</sub>  | 50                                               | ns min |                             |

| WR or RD Rising Edge to ALE Rising Edge   | t <sub>2</sub>  | 50                                               | ns min |                             |

| ALE Rising Edge to CS Falling Edge        | t <sub>3</sub>  | 22                                               | ns min |                             |

| CS Falling Edge to RD Falling Edge        | t <sub>4</sub>  | 60                                               | ns min |                             |

| CS Falling Edge to WR Falling Edge        | t <sub>5</sub>  | 30                                               | ns min |                             |

| WR or RD Rising Edge to CS Rising Edge    | t <sub>6</sub>  | 0                                                | ns min |                             |

| WR Pulse Width                            | t <sub>7</sub>  | 53                                               | ns min |                             |

| ALE Falling Edge to WR or RD Falling Edge | t <sub>8</sub>  | 22                                               | ns min |                             |

| Address Setup to ALE Falling Edge         | t <sub>9</sub>  | 47                                               | ns min |                             |

| Address Hold after ALE Falling Edge       | t <sub>10</sub> | 22                                               | ns min |                             |

| RD Active to Valid Data <sup>3</sup>      | t <sub>11</sub> | 75                                               | ns max | Measured with $t_4 = 60$ ns |

| Bus Relinquish Time after RD4             | t <sub>12</sub> | 10                                               | ns min |                             |

|                                           |                 | 62                                               | ns max |                             |

| Data Valid to WR Rising Edge              | t <sub>13</sub> | 55                                               | ns min |                             |

| Data Valid after WR Rising Edge           | tı              | 10                                               | ns min |                             |

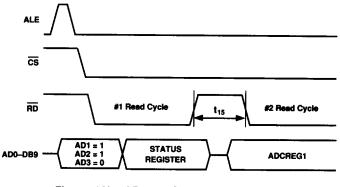

| Delay Time Between Stack Reads            | t <sub>15</sub> | 100                                              | ns min | See Figure 13b              |

See Figures 4 and 5.

Timing specifications in **bold print** are 100% production tested. All other times are sample tested at +25/C to ensure compliance. All input signals are specified with  $t_r = t_f = 5$  ns (10% to 90% of 5 V) and timed from a voltage level of y.6 V.

with  $t_r = t_f = 5$  ns (10% to 90% of 5 V) and timed from a voltage level of 1.0 V.

3 Data access time depends directly on  $t_4$ , the  $\overline{\text{CS}}$  to  $\overline{\text{RD}}$  setup time, e.g.,  $t_1 = \sqrt{35} + t_4$ . Time  $t_{11}$  is measured with the load circuit of Figure 3 and is defined as the time required for an output to cross 0.8 V or 2.4 V.

<sup>4</sup>t<sub>12</sub> is derived from the measured time taken by the data outputs to change 0.5 V when loaded with the circuit of Figure 3. The measured number is then extrapolated back to remove the effects of charging or discharging the 100 pF capacitor. This means that the time t<sub>12</sub> quoted above is the true bus relinquish time of the device and, as such, is independent of external bus loading capacitance.

Specifications subject to change without notice.

NOTES

Figure 4. Read Cycle Timing for AD7775

Figure 5. Write Cycle Timing for AD7775

# DEMODULATOR TIMING CHARACTERISTICS<sup>1</sup> ( $v_{cc} = +5 \text{ V} \pm 5\%$ ; agnd = dgnd = 0 v)

| Parameter                                                                                          | Label                                                 | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> | Units                       | Test Conditions/Comments                                                                                                     |

|----------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------|

| RESET Rising Edge to CTRL Rising Edge <sup>2</sup> WR Rising Edge to CTRL Rising Edge <sup>2</sup> | <u>-</u>                                              | 100<br>200                                   | ns min<br>ns min            | For AD7775 Only Applies Only after a Write Instruction to the Control Register                                               |

| RESET Pulse Width <sup>2</sup>                                                                     | _                                                     | 100                                          | ns min                      | For AD7775 Only                                                                                                              |

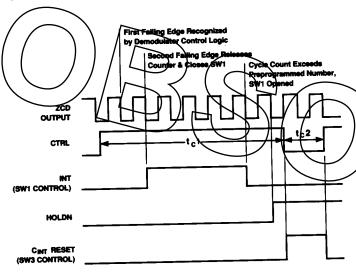

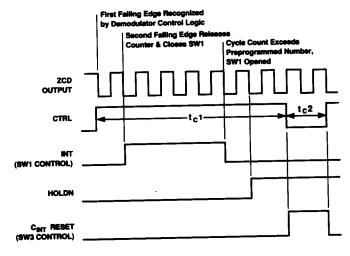

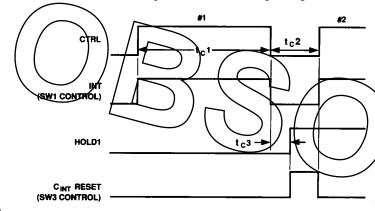

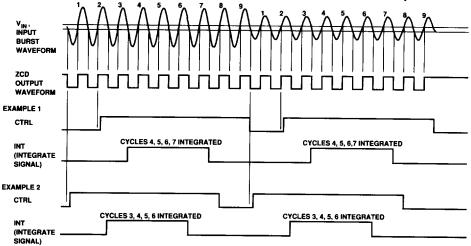

| SYNCHRONOUS DETECTOR MODE <sup>3</sup><br>CTRL High Time                                           | t <sub>C1</sub>                                       | $(N + 3.5) t_{CYC}$                          | ns min                      | Minimum N for Guaranteed Performance Is 4,<br>Maximum N Is 15. Programmable via Locations<br>CR0-CR3 of the Control Register |

| CTRL Low Time <sup>2</sup> Input Signal Period                                                     | t <sub>C2</sub><br>t <sub>CYC</sub>                   | 1.5 t <sub>CYC</sub><br>200<br>500           | ns min<br>ns min<br>ns max  | Fundamental Input Frequency Must Lie Between 2 MHz and 5 MHz                                                                 |

| GATED DETECTOR MODE <sup>4</sup> CTRL High Time CTRL Low Time <sup>2</sup> Input Signal Frequency  | t <sub>C1</sub><br>t <sub>C2</sub><br>f <sub>IN</sub> | 800<br>600 + 0.375 t <sub>C</sub> 1<br>5     | ns min<br>ns min<br>MHz max | Corresponds to 200 ns Minimum Input Signal<br>Period                                                                         |

| CALIBRATION MODES  CTRL High Time  CTRL Low Time                                                   | t <sub>C2</sub>                                       | 800                                          | ns min                      | Assumes Internal Calibration Voltage Has<br>Settled; See Under Circuit Description for<br>Calibration Mode                   |

| NOTES                                                                                              | 1                                                     | V) and 3See I                                | Figures &a and 8b.          |                                                                                                                              |

<sup>1</sup>All input signals are specified with ir = tf = timed from a voltage level of 1.6 V. <sup>2</sup>Sample tested at +25°C to ensure compliance.

ABSOLUTE MAXIMUM RATINGS\* V to AGND or DGND -0.3 V AGND to DGND Digital Inputs to DGND -0.3 V Digital Outputs to DGND -0.3 -0.3 Analog Inputs to AGND Analog Outputs to AGND Operating Temperature Range Commercial (J Version) . . . . . . . . . . 0°C to +70°C Junction Temperature . . . . . . . . . . . . . . . . . . +150°C Storage Temperature Range .....-65°C to +150°C Power Dissipation, SOIC . . . . . . . . . . . . . . . . . 1 W Lead Temperature (Soldering, 10 secs) .....+300°C θ<sub>IA</sub> Thermal Impedance . . . . . . . . . . . . . . . . . 80°C/W Lead Temperature (Soldering, 10 secs) .....+235°C \*Stresses above those listed under "Absolute Maximum Ratings" may cause

permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Only one Absolute Maximum Rating may be applied at any one time.

#### CAUTION \_

ESD (electrostatic discharge) sensitive device. The digital control inputs are diode protected; however, permanent damage may occur on unconnected devices subject to high energy electrostatic fields. Unused devices must be stored in conductive foam or shunts. The protective foam should be discharged to the destination socket before devices are inserted.

REV. A

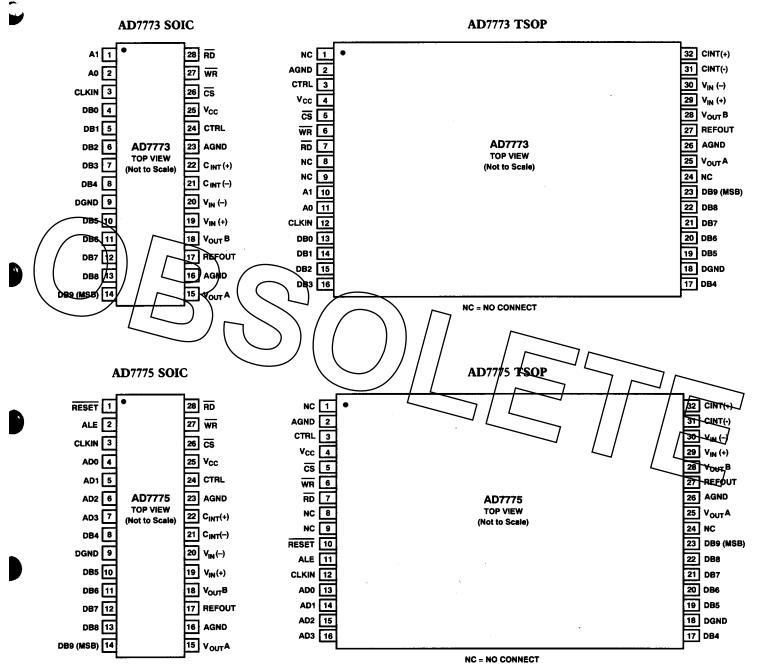

#### PIN CONFIGURATIONS

#### **ORDERING GUIDE**

| Model    | Temperature Range | Package Option    |

|----------|-------------------|-------------------|

| AD7773JR | 0°C to +70°C      | R-28 <sup>1</sup> |

| AD7773JU | 0°C to +70°C      | U-32 <sup>2</sup> |

| AD7775JR | 0°C to +70°C      | R-28              |

| AD7775JU | 0°C to +70°C      | U-32              |

#### **NOTES**

<sup>1</sup>R = Small Outline IC (SOIC).

<sup>&</sup>lt;sup>2</sup>U = Thin Small Outline Package (TSOP).

# SOIC PIN FUNCTION DESCRIPTION

| Pin           | Mnemonic                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power Supplie | es                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 25            | $V_{CC}$                     | +5 V Power Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 9             | DGND                         | Digital Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 16 & 23       | AGND                         | Analog Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Microprocess  | or Interface                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 28            | $\overline{\text{RD}}$       | Read Input (Active Low). When active it is used in conjunction with $\overline{CS}$ to read data over the Input/Output bus. See the truth tables for Microprocessor Interfacing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 27            | $\overline{WR}$              | Write Input (Active Low). When active it is used in conjunction with $\overline{CS}$ to write data over the Input/Output bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 26            | CS                           | Chip Select Input (Active Low). The device is selected when this input is low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Microprocess  | or Interface—AI              | 07773 Only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4-8&          | DB0-DB4                      | Input/Output Data Bus. A 10-bit wide bidirectional data port over which data is transferred                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10-14         | DB5-DB9                      | into or out of the AD7773. DB0 is the Least Significant Bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2             | A0                           | Address Inputs A0 and A1 select one of four registers. See Table I for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1 )           | $\int \frac{d^2}{d^2} \int$  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| - \           | sor Interface – AL           | 2775 Only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4-8-&         | AD0-DB4                      | Multiplexed Address/Data Input/Output Bus. An ALE signal is used to demultiplex the bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|               |                              | After the falling edge of ALE the address/present on AD0-AD3 must be removed and WR or RD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |