# PM-7545/PM-7645

12-BIT BUFFERED MULTIPLYING CMOS D/A CONVERTERS

#### Precision Monolithics Inc.

#### **FEATURES**

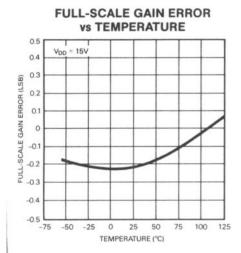

- Preadjusted Full Scale . . . . ±1 LSB Maximum Gain Error

- Low Gain Temperature Coefficient ......... 2ppm/°C

- Small 20-Pin 0.3" Wide DIP

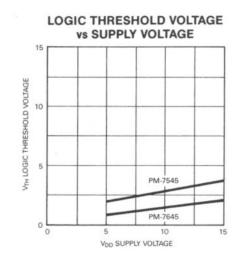

- PM-7545 TTL Compatible for V<sub>DD</sub> = 5V

- PM-7645 TTL and 5V CMOS Compatible for V<sub>DD</sub> = 15V

- High ESD Resistance

# ORDERING INFORMATION†

|                                                 | PACKAGE: 20-PIN                       |                                                |                                              |  |  |  |  |

|-------------------------------------------------|---------------------------------------|------------------------------------------------|----------------------------------------------|--|--|--|--|

| MAXIMUM<br>GAIN ERROR<br>T <sub>A</sub> = +25°C | MILITARY* TEMPERATURE -55°C to +125°C | INDUSTRIAL<br>TEMPERATURE<br>-25°C to<br>+85°C | COMMERCIAL<br>TEMPERATURE<br>0°C to<br>+70°C |  |  |  |  |

| ±1 LSB                                          | PM7545AR                              | PM7545ER                                       | PM7545GP                                     |  |  |  |  |

| ±3 LSB                                          | PM7545BR                              | PM7545FR                                       | PM7545HP                                     |  |  |  |  |

| ±3 LSB                                          | -                                     | -                                              | PM7545HPC††                                  |  |  |  |  |

| ±1 LSB                                          | PM7645AR                              | PM7645ER                                       | PM7645GP                                     |  |  |  |  |

| ±3 LSB                                          | PM7645BR                              | PM7645FR                                       | PM7645HP                                     |  |  |  |  |

- For devices processed in total compliance to MIL-STD-883, add /883 after part number. Consult factory for 883 data sheet.

- † Burn-in is available on commercial and industrial temperature range parts in cerdip, plastic dip, and TO-can packages. For ordering information, see 1988 Data Book, Section 2.

- †† For availability and burn-in information on SO and PLCC packages, contact your local sales office.

#### **CROSS REFERENCE**

| PMI      | ADI       | TEMPERATURE<br>RANGE |

|----------|-----------|----------------------|

| PM7545AR | AD7545GUD |                      |

| PM7545BR | AD7545UD  | AAII ITA DV          |

| PM7545BR | AD7545TD  | MILITARY             |

| PM7545BR | AD7545SD  |                      |

| PM7545ER | AD7545GCQ |                      |

| PM7545FR | AD7545CQ  | INDUIGEDIAL          |

| PM7545FR | AD7545BQ  | INDUSTRIAL           |

| PM7545FR | AD7545AQ  |                      |

| PM7545GP | AD7545GLN |                      |

| PM7545HP | AD7545LN  | 001414500141         |

| PM7545HP | AD7545KN  | COMMERCIAL           |

| PM7545HP | AD7545JN  |                      |

|          |           |                      |

# GENERAL DESCRIPTION

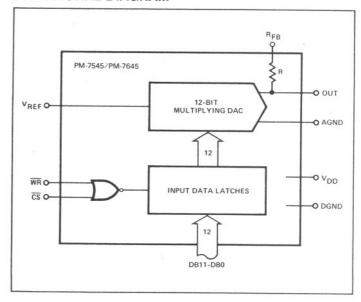

The PM-7545/PM-7645 are 12-bit CMOS multiplying DACs with internal data latches. Digital data is input in a 12-bit wide data format, while CS and WR control inputs are active low. During this time the latches are transparent allowing digital inputs direct connection to the DAC. When WR is returned to logic high, the current data word in the latch is saved.

The PM-7545 operates from 5 to 15 volt power supplies, offering TTL logic compatibility at  $V_{DD}$  of 5V and CMOS logic compatibility at  $V_{DD}$  of 15V. The PM-7645 is specified for operation at  $V_{DD}$  of 15V, offering TTL logic input compatibility.

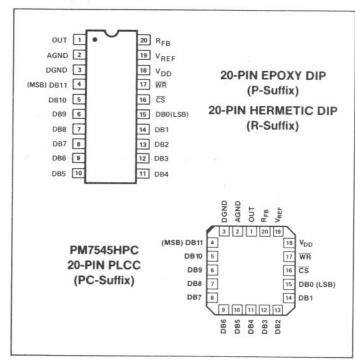

#### **PIN CONNECTIONS**

#### **FUNCTIONAL DIAGRAM**

11

# **ABSOLUTE MAXIMUM RATINGS**

| (T <sub>A</sub> = 25°C unless otherwise noted.)    |

|----------------------------------------------------|

| V <sub>DD</sub> to DGND0.3V, +17V                  |

| Digital Input Voltage to DGND0.3V, V <sub>DD</sub> |

| AGND to DGND0.3V, V <sub>DD</sub>                  |

| V <sub>RFB</sub> , V <sub>REF</sub> to DGND ±25V   |

| V <sub>PIN 1</sub> to DGND0.3V, V <sub>DD</sub>    |

| Power Dissipation (Any Package) to +75°C 450mW     |

| Derates Above +75°C by 6mW/°C                      |

| Operating Temperature Range                        |

| Military (AR, BR) Grades55°C to +125°C             |

| Industrial (ER, FR) Grades25°C to +85°C            |

| Commercial (GP, HP, HPC) Grades 0°C to +70°C       |

| Dice Junction Temperature +150°C                   |

| Storage Temperature65°C to +150°C                  |

| Lead Temperature (Soldering, 60 sec) +300°C        |

#### CAUTION:

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation at or above this specification is not implied. Exposure to above maximum rating conditions for extended periods may affect device reliability.

M-754

nted.

ARAM

EFER

out F

(Pin

NALC

utpu

(No1 C<sub>OL</sub>

nput

hput

DE SWI' (N Chij

- 2. Do not apply voltages higher than  $V_{\rm DD}$  or less than GND potential on any terminal except  $V_{\rm REF}$ .

- The digital inputs are zener protected, however, permanent damage may occur on unprotected units from high-energy electrostatic fields. Keep units in conductive foam at all times until ready to use. Use proper anti-static handling procedures.

- 4. Remove power before inserting or removing units from their sockets.

**ELECTRICAL CHARACTERISTICS** at  $V_{DD}$ =+5V,  $V_{REF}$ =+10V,  $V_{OUT}$ =0V, AGND=DGND=0V;  $T_A$ =-55°C to +125°C apply for PM-7545AR/BR,  $T_A$ =-25°C to +85°C apply for PM-7545ER/FR,  $T_A$ =0°C to +70°C apply for PM-7545GP/HP/HPC, unless otherwise noted. 15V operating characteristics are shown on the following pages.

|                                                               |                   |                                                                                          |     |       | PM-7545A/E/G |   |     | PM-7545B/F/H |           |            |

|---------------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------|-----|-------|--------------|---|-----|--------------|-----------|------------|

| PARAMETER                                                     | SYMBOL            | CONDITIONS                                                                               | MIN | TYP   | MAX          | N | IIN | TYP          | MAX       | UNITS      |

| STATIC ACCURACY                                               |                   |                                                                                          |     |       |              |   |     |              |           |            |

| Resolution                                                    | N                 |                                                                                          | 12  |       | _            |   | 12  |              | _         | Bits       |

| Relative<br>Accuracy                                          | INL               | T <sub>A</sub> = Full Temp. Range                                                        | _   | same. | ±1/2         |   | _   | -            | ±1/2      | LSB        |

| Differential<br>Nonlinearity                                  | DNL               | T <sub>A</sub> = Full Temp. Range<br>(Note 1)                                            | _   | _     | ±1           |   | _   | _            | ±1        | LSB        |

| Gain Error                                                    | 0                 | T <sub>A</sub> = +25°C                                                                   | _   | _     | ±1           |   | _   | _            | ±3        | LSB        |

| (Notes 2, 3)                                                  | G <sub>FSE</sub>  | T <sub>A</sub> = Full Temp. Range                                                        |     |       | ±2           |   |     |              | ±4        |            |

| Gain Temperature Coefficient $\Delta Gain/\Delta Temperature$ | TCG <sub>FS</sub> | (Note 4)                                                                                 | -   | ±2    | ±5           | 9 | _   | ±2           | ±5        | ppm/°C     |

| DC Supply Rejection $\Delta Gain/\Delta V_{DD}$ PSS           | DOC               | $T_A = +25^{\circ}C$                                                                     | _   | _     | 0.002        |   | -   | _            | 0.002     | %/%        |

|                                                               | PSS               | $T_A = +25^{\circ}C$<br>$T_A = Full Temp. Range (\Delta V_{DD} = \pm 5\%)$               | _   |       | 0.004        |   | _   |              | 0.004     |            |

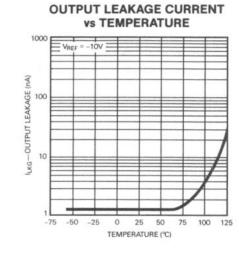

| Output Leakage                                                |                   | $T_A = +25$ °C, $\overline{WR} = \overline{CS} = 0V$ ,<br>All Digital Inputs = 0V        | -   | _     | 10           |   | _   | _            | 10        | nA         |

| Current at OUT                                                | ILKG              | T <sub>A</sub> = Full Temp. Range                                                        |     |       |              |   |     |              |           |            |

|                                                               |                   | A/B Versions                                                                             | -   | _     | 200          |   | -   | _            | 200<br>50 |            |

|                                                               |                   | E/F/G/H Versions                                                                         |     |       | 50           |   |     |              | 50        |            |

| DYNAMIC PERFORMAN                                             | CE                |                                                                                          |     |       |              |   |     |              |           |            |

| Propagation Delay                                             | t <sub>pD</sub>   | $T_A = +25$ °C                                                                           | -   | _     | 300          |   | _   | _            | 300       | ns         |

| (Notes 4, 5, 6, 7)                                            | -ро               | (OUT Load = $100\Omega$ , $C_{EXT} = 13pF$ )                                             |     |       |              |   |     |              |           |            |

| Current Settling Time                                         | t <sub>s</sub>    | $T_A$ = Full Temp. Range<br>(To 1/2 LSB) (Note 4)<br>$I_{OUT}$ Load = 100 $\Omega$       | -   | -     | 1            | n | _   | _            | 1         | μ\$        |

| District Observe                                              |                   | T <sub>A</sub> = +25°C                                                                   |     |       | 300          |   |     | _            | 300       |            |

| Digital Charge<br>Injection                                   | Q                 | T <sub>A</sub> = Full Temp. Range<br>V <sub>REF</sub> = AGND (Note 4)                    | -   | _     | 400          |   | _   | _            | 400       | nVs        |

| AC Feedthrough<br>at I <sub>OUT</sub>                         | FT                | $T_A = Full$ Temp. Range<br>$V_{REF} = \pm 10V$ , $f = 10kHz$<br>All Digital Inputs = 0V |     | 5     | _            |   | _   | 5            | -         | $mV_{p-p}$ |

# PMI)

**ELECTRICAL CHARACTERISTICS** at  $V_{DD}$ =+5V,  $V_{REF}$ =+10V,  $V_{OUT}$ =0V, AGND=DGND=0V;  $T_A$ =-55°C to +125°C apply for PM-7545AR/BR,  $T_A$ =-25°C to +85°C apply for PM-7545ER/FR,  $T_A$ =0°C to +70°C apply for PM-7545GP/HP/HPC, unless otherwise noted. 15V operating characteristics are shown on the following pages. (Continued)

|                                         |                                      |                                                                                                                                      | PM-7545A/E/G |            |           | PM         | 1-7545B/   | PM-7545B/F/H |      |  |

|-----------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------|------------|-----------|------------|------------|--------------|------|--|

| PARAMETER                               | SYMBOL                               | CONDITIONS                                                                                                                           | MIN          | TYP        | MAX       | MIN        | TYP        | MAX          | UNIT |  |

| REFERENCE INPUT                         |                                      |                                                                                                                                      |              |            |           |            |            |              |      |  |

| Input Resistance<br>(Pin 19 to GND)     | R <sub>REF</sub>                     | T <sub>A</sub> = Full Temp. Range<br>Input Resistance                                                                                | 7            | 11         | 15        | 7          | 11         | 15           | kΩ   |  |

| ANALOG OUTPUTS                          |                                      |                                                                                                                                      |              |            |           |            |            |              | - 19 |  |

| Output Capacitance<br>(Note 4)<br>COUT  | C <sub>OUT</sub>                     | $T_A = Full Temp. Range$ $DB0-DB11 = 0V, \overline{WR} = \overline{CS} = 0V$ $DB0-DB11 = V_{DD}, \overline{WR} = \overline{CS} = 0V$ | _            | _          | 70<br>150 | _          | _          | 70<br>150    | pF   |  |

| DIGITAL INPUTS                          |                                      | ,                                                                                                                                    |              |            |           |            |            |              |      |  |

| Input High Voltage<br>Input Low Voltage | V <sub>INH</sub><br>V <sub>INL</sub> | T <sub>A</sub> = Full Temp. Range                                                                                                    | 2.4          | _          | 0.8       | 2.4        | _          | 0.8          | V    |  |

| Input Current                           | I <sub>IN</sub>                      | T <sub>A</sub> = +25°C<br>T <sub>A</sub> = Full Temp. Range                                                                          |              | _          | 1<br>10   | _          | _          | 1<br>10      | μΑ   |  |

| Input Capacitance<br>DB0-DB11, WR, CS   | C <sub>IN</sub>                      | T <sub>A</sub> = Full Temp. Range<br>V <sub>IN</sub> = 0 (Note 4)                                                                    | _            | -          | 8         | _          | _          | 8            | pF   |  |

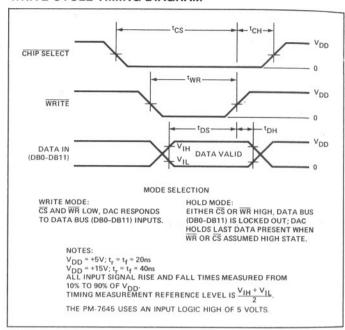

| SWITCHING CHARACT<br>(Notes 4, 8, 9)    | ERISTICS                             | See Timing Diagram                                                                                                                   |              |            |           |            |            |              |      |  |

| Chip Select to<br>Write Setup Time      | t <sub>CS</sub>                      | T <sub>A</sub> = +25°C<br>T <sub>A</sub> = Full Temp. Range                                                                          | 280<br>380   | 200<br>270 | _         | 280<br>380 | 200<br>270 | _            | ns   |  |

| Chip Select to<br>Write Hold Time       | t <sub>CH</sub>                      | T <sub>A</sub> = Full Temp. Range                                                                                                    | 0            | _          | _         | 0          | _          | _            | ns   |  |

| Write Pulse<br>Width                    | t <sub>WR</sub>                      | T <sub>A</sub> = +25°C<br>T <sub>A</sub> = Full Temp. Range                                                                          | 250<br>380   | 175<br>270 | -         | 250<br>380 | 175<br>270 | _            | ns   |  |

| Data Setup<br>Time                      | t <sub>DS</sub>                      | T <sub>A</sub> = +25°C<br>T <sub>A</sub> = Full Temp. Range                                                                          | 140<br>210   | 100<br>150 | _         | 140<br>210 | 100<br>150 | _            | ns   |  |

| Data Hold Time                          | t <sub>DH</sub>                      | T <sub>A</sub> = Full Temp. Range                                                                                                    | 10           |            | _         | 10         | _          | -            | ns   |  |

| POWER SUPPLY                            |                                      |                                                                                                                                      |              |            |           |            |            |              |      |  |

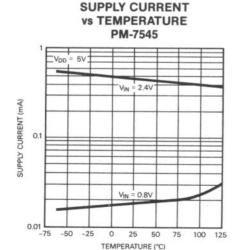

| Supply Current —                        | I <sub>DD</sub>                      | T <sub>A</sub> = Full Temp. Range<br>(All Digital Inputs V <sub>INL</sub> or V <sub>INH</sub> )                                      | _            | _          | 2         | _          | _          | 2            | mA   |  |

| очррну очнепі —                         | I <sub>DD</sub>                      | T <sub>A</sub> = +25°C<br>T <sub>A</sub> = Full Temp. Range<br>(All Digital Inputs 0V or V <sub>DD</sub> )                           | _            | 2<br>5     | 100       | _          | 2 5        | 100<br>100   | μΑ   |  |

#### NOTES:

- 1. 12-bit monotonic over full temperature range.

- 2. Includes the effects of 5ppm max. gain T.C.

- 3. Using internal R<sub>FB</sub>. DAC register loaded with 1111 1111 1111. Gain error is adjustable using the circuits of Figures 4 and 5.

- 4. GUARANTEED and NOT TESTED.

- 5. From digital input change to 90% of final analog output.

- 6. All digital inputs = 0V to  $V_{DD}$ ; or  $V_{DD}$  to 0V.

- Logic inputs are MOS gates, typical input current (at +25°C) is less than 1nA.

- 8. Sample tested at +25°C to ensure compliance.

- 9. Chip select  $\overline{CS}$  must be coincident or present before and/or after write  $\overline{WR}$ ; that is,  $t_{CS} \ge t_{WR}, t_{CH} \ge 0$ .

**ELECTRICAL CHARACTERISTICS** at  $V_{DD}$ =+15V,  $V_{REF}$ =+10V,  $V_{OUT}$ =0V, AGND=DGND=0V;  $T_A$ =-55°C to +125°C apply for PM-7545/PM-7645AR/BR,  $T_A$ =-25°C to +85°C apply for PM-7545/PM-7645ER/FR,  $T_A$ =0°C to +70°C apply for PM-7545/PM-7645GP/HP and PM-7545HPC, unless otherwise noted.

|                                                       |                                      |                                                                                                                                         |      | -7545A/<br>-7645A/ |                |      | -7545B/<br>-7645B/ |                |                   |

|-------------------------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|----------------|------|--------------------|----------------|-------------------|

| PARAMETER                                             | SYMBOL                               | CONDITIONS                                                                                                                              | MIN  | TYP                | MAX            | MIN  | TYP                | MAX            | UNITS             |

| STATIC ACCURACY                                       |                                      |                                                                                                                                         |      |                    |                |      |                    |                |                   |

| Resolution                                            | N                                    |                                                                                                                                         | 12   | _                  | _              | 12   | _                  | _              | Bits              |

| Relative<br>Accuracy                                  | INL                                  | T <sub>A</sub> = Full Temp. Range                                                                                                       | -    |                    | ±1/2           | _    | _                  | ±1/2           | LSB               |

| Differential<br>Nonlinearity                          | DNL                                  | T <sub>A</sub> = Full Temp. Range<br>(Note 1)                                                                                           | _    | _                  | ±1             | _    | _                  | ±1             | LSB               |

| Gain Error<br>(Notes 2, 3)                            | G <sub>FSE</sub>                     | T <sub>A</sub> = +25°C<br>T <sub>A</sub> = Full Temp. Range                                                                             | _    | _                  | ±1<br>±2       | _    | _                  | ±3<br>±4       | LSB               |

| Gain Temperature<br>Coefficient<br>ΔGain/ΔTemperature | TCG <sub>FS</sub>                    | (Note 4)                                                                                                                                | -    | ±2                 | ±5             | _    | ±2                 | ±5             | ppm/°C            |

| DC Supply Rejection<br>ΔGain/ΔV <sub>DD</sub>         | PSS                                  | $T_A = +25$ °C<br>$T_A = Full Temp. Range (\Delta V_{DD} = \pm 5\%)$                                                                    | _    | _                  | 0.002<br>0.004 | =    | _                  | 0.002<br>0.004 | %/%               |

| Output Leakage                                        |                                      | $T_A = +25^{\circ}C$ , $\overrightarrow{WR} = \overrightarrow{CS} = 0V$ ,<br>All Digital Inputs = $0V$                                  | -    | _                  | 10             | _    | _                  | 10             |                   |

| Current at OUT                                        | I <sub>LKG</sub> -                   | T <sub>A</sub> = Full Temp. Range<br>A/B Versions<br>E/F/G/H Versions                                                                   | _    | _                  | 200<br>50      | _    | _                  | 200<br>50      | nA                |

| DYNAMIC PERFORMAN                                     | CE                                   |                                                                                                                                         |      |                    |                |      |                    |                |                   |

| Propagation Delay<br>(Notes 4, 5, 6, 7)               | t <sub>pD</sub>                      | $T_A = +25$ °C<br>(OUT Load = 100 $\Omega$ , $C_{EXT} = 13$ pF)                                                                         | _    | _                  | 250            | -    | _                  | 250            | ns                |

| Current Settling Time                                 | t <sub>s</sub>                       | $T_A$ = Full Temp. Range<br>(To 1/2 LSB) (Note 4)<br>$I_{OUT}$ Load = 100 $\Omega$                                                      | -    | _                  | 1              | _    | _                  | 1              | μS                |

| Digital Charge<br>Injection                           | Q                                    | T <sub>A</sub> = +25°C<br>T <sub>A</sub> = Full Temp. Range<br>V <sub>REF</sub> = AGND (Note 4)                                         | _    |                    | 250<br>300     | _    | _                  | 250<br>300     | nVs               |

| AC Feedthrough<br>at I <sub>OUT</sub>                 | FT                                   | $T_A$ = Full Temp. Range<br>$V_{REF}$ = ±10V, f = 10kHz<br>All Digital Inputs = 0V                                                      | _    | 5                  | <b>—</b> )     | _    | 5                  | _              | mV <sub>p-p</sub> |

| REFERENCE INPUT                                       |                                      |                                                                                                                                         |      |                    |                |      |                    |                |                   |

| Input Resistance<br>(Pin 19 to GND)                   | R <sub>REF</sub>                     | T <sub>A</sub> = Full Temp. Range<br>Input Resistance                                                                                   | 7    | 11                 | 15             | 7    | 11                 | 15             | kΩ                |

| ANALOG OUTPUTS                                        |                                      |                                                                                                                                         |      |                    |                |      |                    |                |                   |

| Output Capacitance<br>(Note 4)<br>C <sub>OUT</sub>    | C <sub>OUT</sub>                     | $T_A = Full Temp. Range$ DB0-DB11 = 0V, $\overline{WR} = \overline{CS} = 0V$ DB0-DB11 = $V_{DD}$ , $\overline{WR} = \overline{CS} = 0V$ | _    | _                  | 60<br>120      | _    | _                  | 60<br>120      | pF                |

| DIGITAL INPUTS                                        |                                      |                                                                                                                                         |      |                    |                |      |                    |                |                   |

| Input High Voltage<br>Input Low Voltage               | V <sub>INH</sub><br>V <sub>INL</sub> | T <sub>A</sub> = Full Temp. Range, PM-7545                                                                                              | 13.5 | _                  | <br>1.5        | 13.5 | _                  | _<br>1.5       | ٧                 |

| Input High Voltage<br>Input Low Voltage               | V <sub>INH</sub><br>V <sub>INL</sub> | T <sub>A</sub> = Full Temp. Range, PM-7645                                                                                              | 2.4  | _                  | 0.8            | 2.4  | _                  | 0.8            | V                 |

| Input Current                                         | I <sub>IN</sub>                      | T <sub>A</sub> = +25°C<br>T <sub>A</sub> = Full Temp. Range                                                                             | _    | _                  | 1<br>10        | _    | _                  | 1<br>10        | μΑ                |

| Input Capacitance<br>DB0—DB11, WR, CS                 | C <sub>IN</sub>                      | T <sub>A</sub> = Full Temp. Range<br>V <sub>IN</sub> = 0 (Note 4)                                                                       | -    | -                  | 8              | _    | _                  | 8              | pF                |

**ELECTRICAL CHARACTERISTICS** at  $V_{DD}$ =+15V,  $V_{REF}$ =+10V,  $V_{OUT}$ =0V, AGND=DGND=0V;  $T_A$ =-55°C to +125°C apply for PM-7545/PM-7645AR/BR,  $T_A$ =-25°C to +85°C apply for PM-7545/PM-7645ER/FR,  $T_A$ =0°C to +70°C apply for PM-7545/PM-7645GP/HP and PM-7545HPC, unless otherwise noted. (Continued)

|                                     |                 |                                                                                                            |            | PM-7545A/E/G<br>PM-7645A/E/G |     |            | -7545B/F<br>-7645B/F |            |       |

|-------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------|------------|------------------------------|-----|------------|----------------------|------------|-------|

| PARAMETER                           | SYMBOL          | CONDITIONS                                                                                                 | MIN        | TYP                          | MAX | MIN        | TYP                  | MAX        | UNITS |

| POWER SUPPLY                        |                 |                                                                                                            |            |                              |     |            |                      |            |       |

|                                     | I <sub>DD</sub> | T <sub>A</sub> = Full Temp. Range<br>(All Digital Inputs V <sub>INL</sub> or V <sub>INH</sub> )            | _          | · <u>-</u> -                 | 2   |            | _                    | 2          | mA    |

| Supply Current                      | I <sub>DD</sub> | T <sub>A</sub> = +25°C<br>T <sub>A</sub> = Full Temp. Range<br>(All Digital Inputs 0V or V <sub>DD</sub> ) | =          | 2<br>5                       | 100 | =          | 5                    | 100        | μΑ    |

| SWITCHING CHARAC<br>(Notes 4, 8, 9) | TERISTICS       | See Timing Diagram                                                                                         | PN         | N-7545 A/E/                  | /G  | PN         | 1-7545 B/F           | / <b>H</b> |       |

| Chip Select to<br>Write Setup Time  | t <sub>CS</sub> | T <sub>A</sub> = +25°C<br>T <sub>A</sub> = Full Temp. Range                                                | 180<br>200 | 120<br>150                   |     | 180<br>200 | 120<br>150           | Ξ          | ns    |

| Chip Select to<br>Write Hold Time   | <sup>t</sup> CH | T <sub>A</sub> = Full Temp. Range                                                                          | 0          | _                            | _   | 0          | _                    | _          | ns    |

| Write Pulse<br>Width                | t <sub>WR</sub> | T <sub>A</sub> = +25°C<br>T <sub>A</sub> = Full Temp. Range                                                | 160<br>240 | 100<br>170                   | _   | 160<br>240 | 100<br>170           | _          | ns    |

| Data Setup<br>Time                  | t <sub>DS</sub> | T <sub>A</sub> = +25°C<br>T <sub>A</sub> = Full Temp. Range                                                | 90<br>120  | 60<br>80                     | _   | 90<br>120  | 60<br>80             | _          | ns    |

| Data Hold Time                      | t <sub>DH</sub> | T <sub>A</sub> = Full Temp. Range                                                                          | 10         |                              | -   | 10         | _                    | _          | ns    |

| SWITCHING CHARAC<br>(Notes 4, 8, 9) | TERISTICS       | See Timing Diagram                                                                                         | PN         | 1-7645 A/E                   | /G  | PN         | 1-7645 B/F           | / <b>H</b> |       |

| Chip Select to<br>Write Setup Time  | tcs             | T <sub>A</sub> = +25°C<br>T <sub>A</sub> = Full Temp. Range                                                | 150<br>210 |                              | _   | 150<br>210 | _                    | _          | ns    |

| Chip Select to<br>Write Hold Time   | <sup>t</sup> cH | T <sub>A</sub> = Full Temp. Range                                                                          | 0          | _                            | _   | 0          | _                    | _          | ns    |

| Write Pulse<br>Width                | t <sub>WR</sub> | T <sub>A</sub> = +25°C<br>T <sub>A</sub> = Full Temp. Range                                                | 150<br>210 | _                            | _   | 150<br>210 | _                    | _          | ns    |

| Data Setup<br>Time                  | t <sub>DS</sub> | T <sub>A</sub> = +25°C<br>T <sub>A</sub> = Full Temp. Range                                                | 225<br>300 | _                            | _   | 225<br>300 | _                    | _          | ns    |

| Data Hold Time                      | t <sub>DH</sub> | T <sub>A</sub> = Full Temp. Range                                                                          | 10         | -                            | _   | 10         | _                    | _          | ns    |

## NOTES:

- 1. 12-bit monotonic over full temperature range.

- Includes the effects of 5ppm max. gain T.C.

- Using internal R<sub>FB</sub>. DAC register loaded with 1111 1111 1111. Gain error is adjustable using the circuits of Figures 4 and 5.

- 4. GUARANTEED and NOT TESTED.

- 5. From digital input change to 90% of final analog output.

- 6. All digital inputs = 0V to  $V_{DD}$ ; or  $V_{DD}$  to 0V.

- Logic inputs are MOS gates, typical input current (at +25°C) is less than 1nA.

- 8. Sample tested at +25°C to ensure compliance.

- 9. Chip select  $\overline{CS}$  must be coincident or present before and/or after write  $\overline{WR}$ ; that is,  $t_{CS} \ge t_{WR}, t_{CH} \ge 0$ .

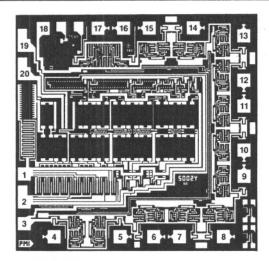

# **DICE CHARACTERISTICS**

DIE SIZE  $0.102 \times 0.100$  inch, 10,200 sq. mils  $(2.59 \times 2.54$ mm, 6.58 sq. mm)

| 1.  | OUT        | 11. | DB4             |

|-----|------------|-----|-----------------|

| 2.  | AGND       | 12. | DB3             |

| 3.  | DGND       | 13. | DB2             |

| 4.  | DB11 (MSB) | 14. | DB1             |

| 5.  | DB10       | 15. | DB0 (LSB        |

| 6.  | DB9        | 16. | CS              |

| 7.  | DB8        | 17. | WR              |

| 8.  | DB7        | 18. | $V_{DD}$        |

| 9.  | DB6        | 19. | VREF            |

| 10. | DB5        | 20. | R <sub>FB</sub> |

|     |            |     |                 |

For additional DICE ordering information, refer to 1988 Data Book, Section 2.

# **WAFER TEST LIMITS** at $T_A = 25$ °C, $V_{DD} = +5$ or +15V, $V_{REF} = +10$ V, $V_{OUT} = 0$ V, AGND = DGND = 0V.

|                                               |                  | PM-7545G/PM-7645G                                                                                   |             |                              |  |  |  |

|-----------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------|-------------|------------------------------|--|--|--|

| PARAMETER                                     | SYMBOL           | CONDITIONS                                                                                          | LIMIT       | UNITS                        |  |  |  |

| Relative Accuracy                             | INL              | Endpoint Linearity Error                                                                            | ±1/2        | LSB MAX                      |  |  |  |

| Differential Nonlinearity                     | DNL              |                                                                                                     | ±1/2        | LSB MAX                      |  |  |  |

| Gain Error                                    | G <sub>FSE</sub> | DAC Latches Loaded with 1111 1111 1111                                                              | ±5          | LSB MAX                      |  |  |  |

| Output Leakage                                | I <sub>LKG</sub> | DAC Latches Loaded with 0000 0000 0000<br>Pad 1                                                     | ±10         | nA MAX                       |  |  |  |

| Input Resistance                              | R <sub>REF</sub> | Pad 19                                                                                              | 7/15        | $k\Omega$ MIN/ $k\Omega$ MAX |  |  |  |

| Digital Input<br>High                         | V <sub>INH</sub> | $V_{DD} = 5V$ $V_{DD} = 15V$ PM-7545 only                                                           | 2.4<br>13.5 | V MIN                        |  |  |  |

| Digital Input<br>Low                          | V <sub>INL</sub> | $V_{DD} = 5V$ $V_{DD} = 15V$ PM-7545 only                                                           | 0.8<br>1.5  | V MAX                        |  |  |  |

| Digital Input<br>High                         | V <sub>INH</sub> | V <sub>DD</sub> = 15V PM-7645 only                                                                  | 2.4         | V MIN                        |  |  |  |

| Digital Input<br>Low                          | V <sub>INL</sub> | V <sub>DD</sub> = 15V PM-7645 only                                                                  | 0.8         | V MAX                        |  |  |  |

| Input Current                                 | I <sub>IN</sub>  | $V_{IN} = 0V \text{ or } V_{DD}$                                                                    | ±1          | μΑ ΜΑΧ                       |  |  |  |

| Supply Current                                | I <sub>DD</sub>  | All Digital Inputs V <sub>INL</sub> or V <sub>INH</sub><br>All Digital Inputs 0V or V <sub>DD</sub> | 2<br>0.1    | mA MAX                       |  |  |  |

| DC Supply Rejection (ΔGain/ΔV <sub>DD</sub> ) | PSS              | $\Delta V_{DD} = \pm 5\%$                                                                           | 0.002       | %/% MAX                      |  |  |  |

#### NOTE:

Electrical tests are performed at wafer probe to the limits shown. Due to variations in assembly methods and normal yield loss, yield after packaging is not guaranteed for standard product dice. Consult factory to negotiate specifications based on dice lot qualification through sample lot assembly and testing.

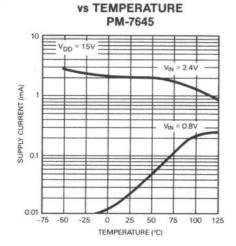

# TYPICAL ELECTRICAL CHARACTERISTICS at V<sub>DD</sub> = +5V or +15V, AGND = DGND = 0V, V<sub>REF</sub> = +10V, OUT = 0V; T<sub>A</sub> = 25°C, unless otherwise noted. (Note 1)

|                                      |                  |                                        | PM-7545G/PM-7645G |       |

|--------------------------------------|------------------|----------------------------------------|-------------------|-------|

| PARAMETER                            | SYMBOL           | CONDITIONS                             | TYPICAL           | UNITS |

| Digital Input Capacitance            | C <sub>IN</sub>  |                                        | 7                 | pF    |

|                                      |                  | DAC Latches Loaded with 0000 0000 0000 | 50                | -5    |

| Output Capacitance                   | C <sub>OUT</sub> | DAC Latches Loaded with 1111 1111 1111 | 110               | pF    |

| Propagation Delay<br>(Notes 2, 3, 4) |                  | V <sub>DD</sub> = 15V                  | 140               |       |

|                                      | <sup>L</sup> pD  | $V_{DD} = 5V$ PM-7545 only             | 230               | ns    |

#### NOTES:

- 1. These characteristics are for design guidance only and are not subject to test.

- 2. From digital input change to 90% of final analog output.

- OUT load = 100Ω, C<sub>EXT</sub> = 13pF.

CS = WR = 0, DB0 to DB11 = 0V to V<sub>DD</sub> or V<sub>DD</sub> to 0V.

### TYPICAL PERFORMANCE CHARACTERISTICS

SUPPLY CURRENT

#### PARAMETER DEFINITIONS

#### RELATIVE ACCURACY

Sometimes referred to as endpoint nonlinearity, and is a measure of the maximum deviation from a straight line passing through the endpoints of the DAC transfer function. Relative Accuracy is measured after the zero and full-scale points have been adjusted, and is normally expressed in LSB or as a percentage of full scale.

#### DIFFERENTIAL NONLINEARITY

This is the difference between the measured change and the ideal change between any two adjacent codes. A differential nonlinearity of  $\pm 1$  LSB maximum over the full operating temperature range will ensure that a device is monotonic (the output will increase for an increase in digital code applied).

#### **GAIN ERROR**

Gain or full scale error is the amount of output error between the ideal output and the actual output. The ideal output is  $V_{\text{REF}}$  minus 1 LSB. The gain error is adjustable to zero using external resistance.

# **OUTPUT CAPACITANCE**

The capacitance from OUT to AGND.

#### PROPAGATION DELAY

This is measured from the digital input change to the analog output current reaching 90% of its final value.

# **DIGITAL CHARGE INJECTION**

This is a measure of the amount of charge injected to the analog output from the digital inputs, when the digital inputs change states. It is the area of the glitch and is specified in nVsec; it is measured with  $V_{\text{REF}} = \text{AGND}$ .

#### **BURN-IN CIRCUIT**

#### LOGIC INFORMATION

#### WRITE CYCLE TIMING DIAGRAM

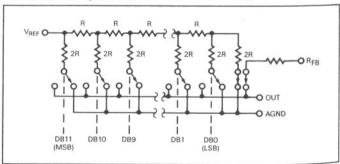

### D/A CONVERTER SECTION

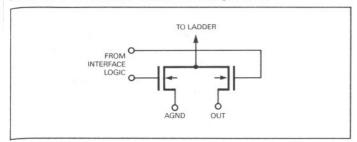

# FIGURE 1: Simplified D/A Circuit of PM-7545

Figure 1 shows a simplified circuit of the D/A Converter section and Figure 2 gives an approximate equivalent switch circuit. R is typically  $11k\Omega$ .

The binary-weighted currents are switched between OUT and AGND by N-channel switches, thus maintaining a constant current in each ladder leg independent of the switch state.

The capacitance at the OUT terminal,  $C_{OUT}$ , is code dependent and varies from 70pF (all switches to AGND) to 150pF (all switches to OUT). One of the current switches is shown in Figure 2.

The input resistance at  $V_{REF}$  (Figure 1) is always equal to  $R_{LDR}$  ( $R_{LDR}$  is the R/2R ladder characteristics resistance and is equal to value "R"). Since the input resistance at the  $V_{REF}$  pin is constant, the reference terminal can be driven by a reference voltage or a reference current, ac or dc, of positive or negative polarity. (If a current source is used, a low-temperature-coefficient external  $R_{FB}$  is recommended to define scale factor.)

The internal feedback resistor (R<sub>FB</sub>) has a normally closed switch in series as shown in Figure 1. This switch improves performance over temperature and power supply rejection; however when the circuit is not powered up the switch assumes an open state.

FIGURE 2: N-Channel Current Steering Switch

#### **DIGITAL SECTION**

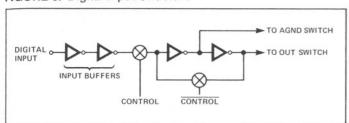

Figure 3 shows the digital structure for one bit. The digital signals CONTROL and  $\overline{\text{CONTROL}}$  are generated from  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$ .

FIGURE 3: Digital Input Structure

The input buffers are simple CMOS inverters designed such that when the PM-7545 is operated with  $V_{DD}$  = 5V, the buffers convert TTL input levels (2.4V and 0.8V) into CMOS logic levels. When the digital input is in the region of 1.0 volts to 6.0 volts, the input buffers operate in their linear region and draw current from the power supply. To minimize power supply currents, it is recommended that the digital input voltages be as close to the supply rails ( $V_{DD}$  and DGND) as is practically possible. The PM-7545 may be operated with any supply voltage in the range  $5 \le V_{DD} \le 15$  volts. With  $V_{DD}$  = +15V, the input logic levels are CMOS compatible only, i.e., 1.5V and 13.5V. The PM-7645 operates with  $V_{DD}$  = 15V only; the buffers convert TTL input levels (2.4V and 0.8V) into CMOS logic levels.

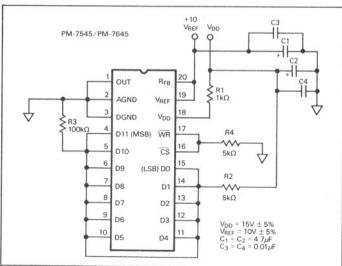

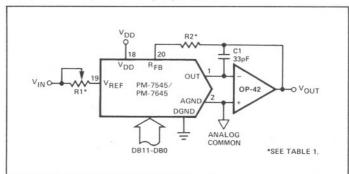

#### **BASIC APPLICATIONS**

Figures 4 and 5 show simple unipolar and bipolar circuits using the PM-7545/PM-7645. Resistor R1 is used to trim for full scale. The following versions (PM-7545AR, PM-7545ER, PM-7545GP) have a guaranteed maximum gain error of  $\pm 1$  LSB at  $\pm 25^{\circ}$  C and  $V_{DD} = \pm 5V$ , and in many applications the gain trim resistors are

not required. Capacitor C1 provides phase compensation and helps prevent overshoot and ringing when using high speed op amps. The circuits of Figures 4 and 5 have constant input impedance at the  $V_{\rm RFF}$  terminal.

The circuit of Figure 4 can either be used as a fixed reference D/A converter so that it provides an analog output voltage in the range 0 to  $-V_{IN}$  (the inversion is introduced by the op amp); or  $V_{IN}$  can be an ac signal in which case the circuit behaves as an attenuator (2-Quadrant Multiplier).  $V_{IN}$  can be any voltage in the range  $-20 \leq V_{IN} \leq +20$  volts (provided the op amp can handle such voltages) since  $V_{REF}$  is permitted to exceed  $V_{DD}$ . Table 2 shows the code relationship for the circuit of Figure 4.

FIGURE 4: Unipolar Binary Operation

TABLE I: Recommended Trim Resistor Value vs. Grades

| TRIM<br>RESISTOR | CR   | HP/FR/BR | GP/ER/AR |

|------------------|------|----------|----------|

| R1               | 200Ω | 100Ω     | 20Ω      |

| R2               | 68Ω  | 33Ω      | 6.8Ω     |

TABLE II: Unipolar Binary Code Table for Circuit of Figure 4

| BINARY NUMBER IN DAC REGISTER |      |      | ANALOG OUTPUT                                                   |

|-------------------------------|------|------|-----------------------------------------------------------------|

| 1111                          | 1111 | 1111 | $-V_{IN}\cdot\left\{\frac{4095}{4096}\right\}$                  |

| 1000                          | 0000 | 0000 | $-V_{IN} \cdot \left\{ \frac{2048}{4096} \right\} = -1/2V_{IN}$ |

| 0000                          | 0000 | 0001 | $-V_{IN} \cdot \left\{ \frac{1}{4096} \right\}$                 |

| 0000                          | 0000 | 0000 | 0 Volts                                                         |

|                               |      |      |                                                                 |

---

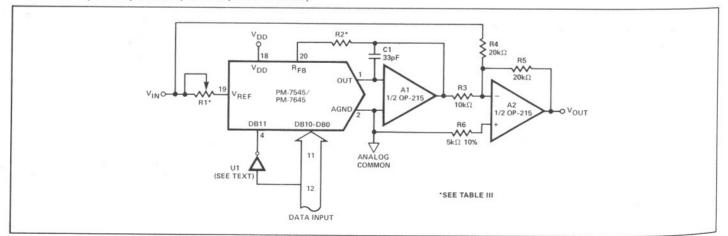

Figure 5 and Table 3 illustrate the recommended circuit and code relationship for bipolar operation. The D/A function itself uses offset binary code. The inverter  $U_1$  on the MSB line, converts 2's-complement input code to offset binary code. The inverter  $U_1$  may be omitted if the inversion is done in software.

R3, R4 and R5 must match within 0.01% and should be the same type of resistors (preferably wire-wound or metal foil), so that their temperature coefficients match. Mismatch of R3 value to R4 causes both offset and full scale error. Mismatch of R5 to R4 and R3 causes full scale error.

TABLE III:

2's Complement Code Table for Circuit of Figure 5

| DATA INPUT |      |      | ANALOG OUTPUT                                      |

|------------|------|------|----------------------------------------------------|

| 0111       | 1111 | 1111 | $+V_{IN} \cdot \left\{ \frac{2047}{2048} \right\}$ |

| 0000       | 0000 | 0001 | $+V_{IN} \cdot \left\{ \frac{1}{2048} \right\}$    |

| 0000       | 0000 | 0000 | 0 Volts                                            |

| 1111       | 1111 | 1111 | $-V_{IN} \cdot \left\{ \frac{1}{2048} \right\}$    |

| 1000       | 0000 | 0000 | $-V_{IN} \cdot \left\{ \frac{2048}{2048} \right\}$ |

#### **APPLICATION HINTS**

Output Offset: CMOS D/A converters exhibit a code-dependent output resistance that causes a code-dependent error voltage at the output of the amplifier. The maximum amplitude of this offset, which adds to the D/A converter nonlinearity, is 0.67  $V_{OS}$  where  $V_{OS}$  is the amplifier input-offset voltage. To maintain monotonic operation, it is recommended that  $V_{OS}$  be no greater than 10% of 1 LSB over the temperature range of operation.

General Ground Management: AC or transient voltages between AGND and DGND can cause noise injection into the analog output. The simplest method of ensuring that voltages at AGND and DGND are equal is to tie AGND and DGND together at the PM-7545/PM-7645. It is recommended that two diodes (1N914 or equivalent) be connected in inverse parallel between AGND and DGND pins in complex systems where AGND and DGND tie on the backplane.

**Digital Glitches:** When  $\overline{WR}$  and  $\overline{CS}$  are both low, the latches are transparent and the D/A converter inputs follow the data inputs. Some bus systems do not always have data valid for the whole period during which  $\overline{WR}$  is low. This will allow invalid data to briefly appear at the DAC inputs during the write cycle. This can cause unwanted glitches at the DAC output. Retiming the write pulse  $\overline{WR}$ , so that it only occurs when data is valid, will eliminate the problem.

FIGURE 5: Bipolar Operation (2's Complement Code)

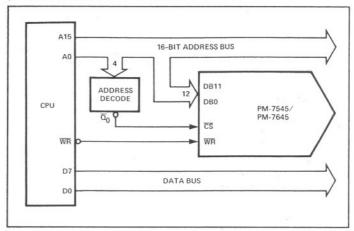

# INTERFACING THE PM-7545/PM-7645 TO MICROPROCESSORS

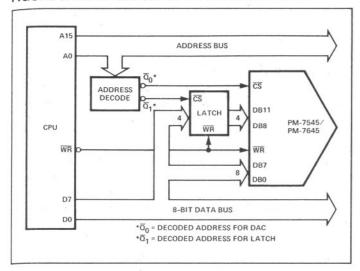

The PM-7545 can be directly interfaced to either an 8 or 16-bit microprocessor via its 12-bit wide data latch using the  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  control signals.

An 8-bit processor interface configuration is shown in Figure 6. It uses two memory addresses, one for the lower 8-bits and one for the upper 4-bits of data into the DAC via the latch.

FIGURE 6: 8-Bit Processor to PM-7545/7645 Interface

Connection to an 8-bit processor with a full 16-bit wide address bus (such as the 6800, 8080, Z80) is shown in Figure 7. The 12 lower address lines are fed directly to the PM-7545; this allows the PM-7545 to use 4k bytes for its address location. The address field of the instruction is organized so that the lower 12-bits contain the DAC data. Data is written into the DAC using a single write instruction.

**FIGURE 7:** Connecting the PM-7545/7645 to an 8-Bit Microprocessor via the Address Bus