## MAXIM

### **Direct-Conversion Tuner IC** for Digital DBS Applications

### **General Description**

The MAX2102<sup>†</sup> is a low-cost direct-conversion tuner IC designed for use in digital direct-broadcast satellite (DBS) television set-top box units. Its direct-conversion architecture reduces system cost compared to devices with IF-based architectures.

The MAX2102 directly tunes L-band signals to baseband using a broadband I/Q downconverter. Operating frequency range spans from at least 950MHz to 2150MHz.

The IC includes an LNA with AGC, two downconverter mixers, an oscillator buffer with 90° quadrature generator and prescaler, and baseband amplifiers.

#### **Applications**

DirecTV, PrimeStar, EchoStar DBS Tuners

**DVB-Compliant DBS Tuners**

Cellular Basestations

Wireless Local Loop

**Broadband Systems**

**LMDS**

#### Features

- ♦ Low-Cost Bipolar Design, Lowest Cost Architecture

- ♦ Operates from Single +5V Supply

- ♦ 950MHz to 2150MHz Input Frequency Range\*

- ♦ On-Chip Quadrature Generator, Dual-Modulus Prescaler (/64, /65)

- ♦ Input Levels: -19dBm to -69dBm per Carrier

- ◆ Over 50dB AGC Control Range

- ♦ Noise Figure = 13.2dB; IIP3 = 6.5dBm (at 1450MHz)

- ♦ Automatic Baseband Offset Correction

- ♦ Easy Interface to MAX1002/MAX1003 Dual ADC and Popular Baseband ICs

- ♦ Evaluation Kit Available, Tuner Reference Design Assistance Available

\*Contact factory for MAX2102 versions with expanded frequency

### Ordering Information

| PART       | TEMP. RANGE  | PIN-PACKAGE |

|------------|--------------|-------------|

| MAX2102CWI | 0°C to +70°C | 28 SO       |

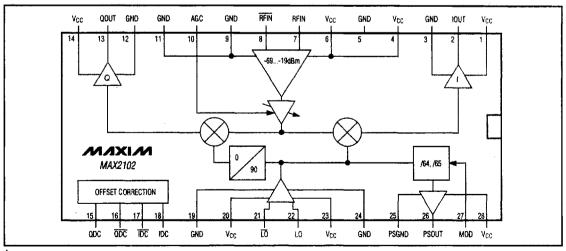

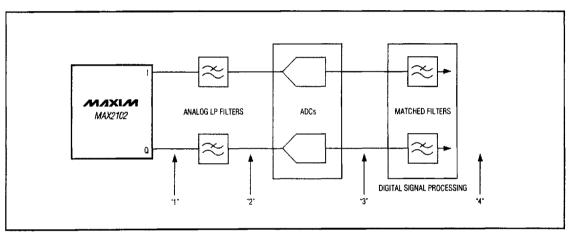

### Functional Diagram

†Patents Pending

MIXLM

Maxim Integrated Products 10-7

10

#### **ABSOLUTE MAXIMUM RATINGS**

| Vcc to GND0.5V                                    | to 7V |

|---------------------------------------------------|-------|

| RFIN to RFIN                                      | ±2V   |

| LO- to LO                                         |       |

| AGC, MOD, RFIN, AFIN, LO, LO to GND0.5V to (VCC + | 0.5V) |

| AGC CURRENT±5                                     | 50mA  |

| IDC to IDC, QDC to QDC                            | ±2V   |

| IOUT or QOUT to GND Short-Circuit Duration        | 0sec  |

| PSOUT to GND Short-Circuit Duration               | None  |

| IDC, IDC, QDC, QDC to GND                                        | 0.5V to (Vcc + 0.5V) |

|------------------------------------------------------------------|----------------------|

| SO (derate 12.50mW/°C above + 70                                 |                      |

| Operating Temperature Range MAX2102CWI                           | 0°C to . 70°C        |

| Junction Temperature                                             |                      |

| Storage Temperature Range<br>Lead Temperature (soldering, 10sec) | -300°C to +165°C     |

| Lead reinperature (soldering, rosect                             | +300 0               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +4.75V \text{ to } +5.25V; \text{ GND} = \text{OV}; \text{PSGND} = \text{GND}; \text{AGC} = 1.3V; \text{MOD} = 0.8V; \text{PRFIN} = \text{OFF}; f_{LO} = 1450.125\text{MHz}; \text{P}_{LO} = -15\text{dBm}; \text{IOUT}, \text{QOUT} = \text{open}; \text{TA} = 0^{\circ}\text{C} \text{ to } +70^{\circ}\text{C}; \text{unless otherwise noted.})$

| PARAMETER                      | CONDITIONS     | MIN  | TYP | MAX  | UNITS |

|--------------------------------|----------------|------|-----|------|-------|

| SUPPLY                         |                |      |     |      |       |

| Supply Voltage                 |                | 4.75 |     | 5.25 | V     |

| Supply Current                 |                |      | 150 | 195  | mA    |

| CONTROL INPUTS, PRESCALER      |                |      |     |      |       |

| MOD Input Low Level            |                |      |     | 8.0  | V     |

| MOD Input High Level           |                | 2.0  |     |      | V     |

| MOD Input Bias Current         | 0V < MOD < Vcc | -80  |     | 10   | μA    |

| AGC Input Bias Current         | 1V < AGC < 4V  | -180 |     | 180  | μA    |

| IOUT, QOUT Common-Mode Voltage |                | 2.2  |     | 2.6  | V     |

#### **AC ELECTRICAL CHARACTERISTICS**

(MAX2102 EV kit circuit (Figure 1);  $V_{CC} = 5V$ ; PSGND = open; MOD = GND;  $f_{RFIN} = 2150MHz$ ;  $P_{RFIN} = -19dBm$ ;  $f_{LO} = 2150.125MHz$ ;  $P_{LO} = -15dBm$  driven single-ended into LO; AGC set via servo loop for  $V_{IOUT} = V_{QOUT} = 0.5Vp$ -p; IOUT, QOUT drives AC-coupled  $100\Omega$  load;  $2k\Omega$  from PSOUT to GND;  $T_{A} = +25^{\circ}C$ ; unless otherwise noted.)

| PARAMETER                               | CONDITIONS                                                                                                                   | MIN | TYP | MAX  | UNITS |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|-------|

| RF FRONT END                            |                                                                                                                              |     |     |      |       |

| RFIN Carrier Frequency Range            | (Note 1)                                                                                                                     | 950 |     | 2150 | MHz   |

| RFIN Maximum Single-Carrier Input Power | Refers to single-carrier power generating VIOUT = VQOUT = 0.5Vp-p. 950MHz < fRFIN < 2150MHz, 950MHz < fLO < 2150MHz (Note 4) | -19 |     |      | dBm   |

| RFIN Minimum Single-Carrier Input Power | Refers to single-carrier power generating Viout = Voout = 0.5Vp-p. 950MHz < frein < 2150MHz, 950MHz < fLo < 2150MHz (Note 4) |     |     | -69  | dBm   |

| AGC Range                               | 1V < VAGC < 4V                                                                                                               | 50  |     |      | dΒ    |

### **AC ELECTRICAL CHARACTERISTICS (continued)**

(MAX2102 EV kit circuit (Figure 1);  $V_{CC}$  = 5V; PSGND = open; MOD = GND;  $f_{RFIN}$  = 2150MHz;  $P_{FIN}$  = -19dBm;  $f_{LO}$  = 2150.125MHz;  $P_{LO}$  = -15dBm driven single-ended into LO; AGC set via servo loop for  $V_{IOUT}$  =  $V_{QOUT}$  = 0.5Vp-p; IOUT, QOUT drives AC-coupled 100 $\Omega$  load;  $2k\Omega$  from PSOUT to GND;  $T_A$  = +25°C; unless otherwise noted.)

| PARAMETER                                            |                                                                                                                          |                                                                      |       |      |       |       |  |  |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------|------|-------|-------|--|--|

| RFIN Input Third-Order Intercept<br>Point            | PRFIN = -19dBm per to<br>VIQUT = VQQUT = 0.5V<br>f1RFIN = 1448.1MHz, fi<br>fLO = 1451MHz                                 |                                                                      |       | 6.5  |       | dBm   |  |  |

| RFIN Input Second-Order Intercept<br>Point           | PRFIN = -19dBm per to<br>VIOUT = VQOUT = 0.5V<br>f1RFIN = 1200MHz, f2F<br>fLO = 951MHz                                   |                                                                      | 15.1  |      | dBm   |       |  |  |

|                                                      | frein = 1441MHz,<br>fLO = 1451MHz                                                                                        | PRFIN = -69dBm                                                       |       | 13.2 |       |       |  |  |

| Noise Figure                                         |                                                                                                                          | PRFIN = -69dBm                                                       | 12.9  |      | dB    |       |  |  |

|                                                      | frein = 2141MHz,<br>fLO = 2151MHz                                                                                        | AGC = 4V, PRFIN set via<br>servo loop for Viout =<br>VQOUT = 0.5Vp-p |       | 11.2 |       |       |  |  |

| Maximum Noise-Figure Variation with AGC Gain Setting | Defined as ANF/AGain single-carrier power ra                                                                             |                                                                      | -0.5  | -    | dB/dB |       |  |  |

| RFIN Worst-Case VSWR across Band                     | fRFIN = 950MHz to 215                                                                                                    |                                                                      | 2.3:1 |      |       |       |  |  |

| Maximum Power of Spurious<br>Downconversion Products | 950MHz < fain < 215<br>2150MHz. Dominated<br>causing downconversi<br>conditions: f <sub>LO</sub> = 1075<br>Prin = -69dBm |                                                                      | 32.3  |      | dBc   |       |  |  |

| LO Lookaga at PEIN                                   | P <sub>LO</sub> = -15dBm, 950MHz < f <sub>LO</sub> < 2150MHz (Note 2)                                                    |                                                                      |       |      | -49   | dDm   |  |  |

| LO Leakage at RFIN                                   | PLO = -15dBm, PLO = -15dBm (differentially driven),<br>950MHz < fLO < 2150MHz (Note 2)                                   |                                                                      |       |      | -54   | - dBm |  |  |

10

### **AC ELECTRICAL CHARACTERISTICS (continued)**

(MAX2102 EV kit circuit (Figure 1);  $V_{CC} = 5V$ ; PSGND = open; MOD = GND;  $f_{RFIN} = 2150MHz$ ;  $P_{RFIN} = -19dBm$ ;  $f_{LO} = 2150.125MHz$ ;  $P_{LO} = -15dBm$  driven single-ended into LO; AGC set via servo loop for  $V_{IOUT} = V_{QOUT} = 0.5Vp$ -p; IOUT, QOUT drives AC-coupled  $100\Omega$  load;  $2k\Omega$  from PSOUT to GND;  $T_A = +25^{\circ}C$ ; unless otherwise noted.)

| PARAMETER                                   | CONDITIONS                                               |                                                                                                                                                                     |      | TYP    | MAX  | UNITS   |

|---------------------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|------|---------|

| OSCILLATOR BUFFER, QUADRAT                  | URE GENERATOR, PRE                                       | SCALER                                                                                                                                                              | ·    |        |      | 1.      |

| LO Input Frequency Range                    | (Note 1)                                                 |                                                                                                                                                                     | 950  |        | 2150 | MHz     |

| LO Input Worst-Case VSWR over Band          | fLO = 950MHz to 2150M<br>MAX2102 EV kit match            | •                                                                                                                                                                   |      | 1.75:1 |      |         |

|                                             | (Note 3)                                                 | <del></del>                                                                                                                                                         | -15  |        | -5   |         |

| LO Input Power Level                        | Refers to power level d<br>(differentially driven) (N    | - · · · · · · · · · · · · · · · · · · ·                                                                                                                             | -15  |        | **** | dBm     |

| RFIN to LO Input Isolation                  | (Notes 4, 5)                                             | · · · · · · · · · · · · · · · · · · ·                                                                                                                               | 28   |        |      | ďΒ      |

| IOUT, QOUT Phase Imbalance                  | 950MHz < fLO < 2150N                                     | 950MHz < f <sub>RFIN</sub> < 2150MHz;<br>950MHz < f <sub>LO</sub> < 2150MHz; P <sub>RFIN</sub> = -40dBm;<br>f <sub>IOUT</sub> , f <sub>QOUT</sub> = 125kHz (Note 4) |      |        |      | degrees |

| Worst-Case Additional Phase                 | nal Phase TA = +25°C to +70°C (Notes 4 and 8)            |                                                                                                                                                                     |      |        | 0.6  |         |

| Imbalance Over Temperature                  | $T_A = +25^{\circ}C \text{ to } +0^{\circ}C \text{ (N)}$ | ote 4)                                                                                                                                                              |      | 0.07   | 1    | degrees |

| IOUT, QOUT Amplitude Imbalance              | 950MHz < fLO < 2150N                                     | 950MHz < f <sub>RFIN</sub> < 2150MHz;<br>950MHz < f <sub>LO</sub> < 2150MHz; P <sub>RFIN</sub> = -40dBm;<br>f <sub>IOUT</sub> , f <sub>QOUT</sub> = 125kHz (Note 4) |      |        |      | dB      |

| B B B                                       | $T_A = 0$ °C to +70°C                                    | MOD = low                                                                                                                                                           | 64   |        | 64   |         |

| Prescaler Divide Ratio                      | (Note 4)                                                 | MOD = high                                                                                                                                                          | 65   |        | 65   |         |

| Prescaler Output Swing at PSOUT             | 2kΩ I I 10pF load                                        |                                                                                                                                                                     | 0.8  |        |      | Vp-p    |

| Prescaler Duty Cycle at PSOUT               | PSOUT load = 2kΩ   1.5                                   | pF (Note 2)                                                                                                                                                         | 35   |        | 65   | %       |

| BASEBAND AC CHARACTERISTIC                  | S                                                        |                                                                                                                                                                     |      |        |      |         |

| IOUT, QOUT Clipping Level                   | PRFIN = -50dBm; AGC                                      | = 4V, V <sub>CC</sub> = 5.0V                                                                                                                                        |      | 2.7    |      | Vp-p    |

| Baseband Bandwidth<br>(at IOUT, QOUT)       | At -3dB attenuation                                      |                                                                                                                                                                     | 94   |        | MHz  |         |

| Baseband Gain Ripple<br>(at IOUT, QOUT)     | 1kHz > fiout, qout > 2<br>2150MHz, 950MHz < fi           |                                                                                                                                                                     | 0.45 | 0.85   | dB   |         |

| Baseband Group Delay Ripple (at IOUT, QOUT) |                                                          | 25MHz, 950MHz < f <sub>RFIN</sub> <<br>_O < 2150MHz (Notes 2, 6)                                                                                                    | ·    | 0.45   |      | ns      |

#### AC ELECTRICAL CHARACTERISTICS (continued)

(MAX2102 EV kit circuit (Figure 1); VCC = 5V; PSGND = open; MOD = GND;  $f_{RFIN}$  = 2150MHz;  $P_{EO}$  = -15dBm driven single-ended into LO; AGC set via servo loop for  $V_{IOUT}$  =  $V_{QOUT}$  = 0.5Vp-p; IOUT, QOUT drives AC-coupled 100 $\Omega$  load;  $2k\Omega$  from PSOUT to GND;  $T_A$  = +25°C; unless otherwise noted.)

| PARAMETER                                                 | CONDITIONS                                                                                                                    | MIN | TYP | MAX | UNITS |

|-----------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| IOUT, QOUT Output Impedance                               | (Note 2)                                                                                                                      |     | 4.7 | 10  | Ω     |

| Maximum IOUT to QOUT Output<br>Impedance Difference       | (Note 2)                                                                                                                      |     | ±1  |     | Ω     |

| Power-Supply Ripple Rejection<br>(measured at IOUT, QOUT) | VCC = 5V + 50mVp-p at 300kHz. Amplitude of 300kHz relative to 500mVp-p measured at IOUT, QOUT. Measured using MAX2102 EV kit. |     | 32  |     | dBc   |

- Note 1: All specifications with guaranteed min/max limits are met within this frequency range. Contact factory for MAX2102 versions with expanded frequency range.

- Note 2: Guaranteed by design and characterization.

- Note 3: IOUT, QOUT Phase and Amplitude Imbalance specifications are met within this LO power range.

- Note 4: Guaranteed by production test and/or design and characterization.

- Note 5: Tested under two conditions: 1) Normal test: PRFIN = -20dBm, and 2) Overdrive test: PRFIN = -5dBm but AGC set via servo loop for VIOUT = VOOUT = 0.5Vp-p for PRFIN = 30dBm.

- Note 6: Includes contribution from front-end gain tilt and delay variations produced by varying frein by ±30MHz.

- Note 7: 1kHz minimum frequency determined by 0.22µF offset-correction capacitors. Different value capacitors yield proportionally different low-frequency cutoffs. Group delay at low frequencies will also be affected. See Applications Information section.

- Note 8: Negative numbers (-0.1°) indicate improvement in quadrature accuracy with increasing temperature.

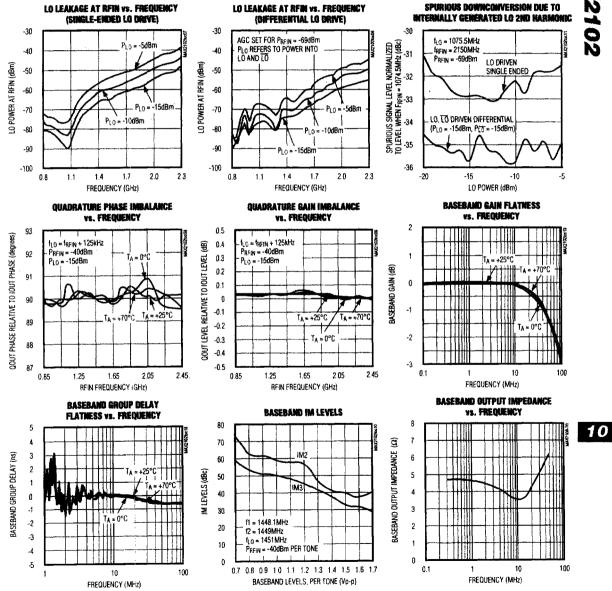

### Typical Operating Characteristics

(MAX2102 EV kit circuit (Figure 1),  $V_{CC}$  = 5V, PSGND = open, MOD = GND, f<sub>RFIN</sub> = 2150MHz, P<sub>RFIN</sub> = -19dBm, f<sub>LO</sub> = 2150.125MHz, P<sub>LO</sub> = -15dBm driven single-ended into LO, AGC set via servo loop for V<sub>IOUT</sub> = V<sub>QOUT</sub> = 0.5Vp-p, IOUT, QOUT drives AC-coupled 100 $\Omega$  load, 2k $\Omega$  from PSOUT to GND, T<sub>A</sub> = +25°C, unless otherwise noted.)

10-11

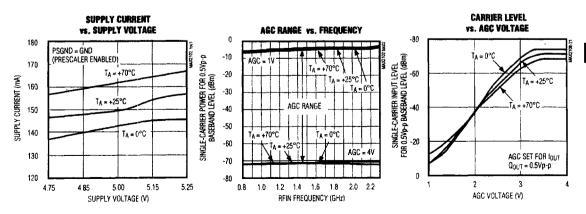

### Typical Operating Characteristics (continued)

(MAX2102 EV kit circuit (Figure 1), V<sub>CC</sub> = 5V, PSGND = open, MOD = GND, f<sub>RFIN</sub> = 2150MHz, P<sub>RFIN</sub> = -19dBm, f<sub>LO</sub> = 2150.125MHz, P<sub>LO</sub> = -15dBm driven single-ended into LO, AGC set via servo loop for V<sub>IOUT</sub> = V<sub>QOUT</sub> = 0.5Vp-p, IOUT, QOUT drives AC-coupled  $100\Omega$  load,  $2k\Omega$  from PSOUT to GND, T<sub>A</sub> = +25°C, unless otherwise noted.)

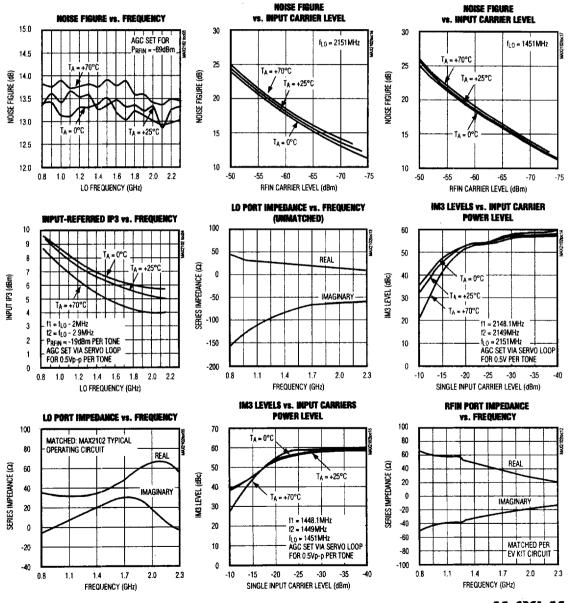

### Typical Operating Characteristics (continued)

(MAX2102 EV kit circuit (Figure 1), Voc = 5V, PSGND = open, MOD = GND, faFin = 2150MHz, PRFin = -19dBm, fLo = 2150.125MHz. PLO = -15dBm driven single-ended into LO, AGC set via servo loop for Viout = VQOUT = 0.5Vp-p, IOUT, QOUT drives AC-coupled  $100\Omega$  load,  $2k\Omega$  from PSOUT to GND,  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted.)

MIXIM

10-13

### Pin Description

| possible. Connect an additional 0.1μF capacitor in parallel with the 10pF capacitor (placement less of 2 IOUT I Channel Baseband Output 3, 12 GND Baseband Ground:  4 VCC RF +5V Supply. Bypass with a 22pF capacitor from this pin to pin 11 (GND), as close to the IC as pos 5. GND Ground (substrate)  6 VCC RF +5V Supply. Bypass with a 22pF capacitor from this pin to pin 9 (GND), as close to the IC as poss 7. RFIN RF Noninverting Input. Couple through a 22pF capacitor directly to a 50Ω signal source.  8 RFIN RF Inverting Input. Connect to a 22pF series capacitor and a 51Ω resistor to ground.  9, 11, 19, 24 GND RF Ground. Connect directly to the ground plane.  10 AGC Automatic Gain-Control Input. Bypass this pin with a 1000pF capacitor close to the pin, to minimize of pling.  13 QOUT Q Channel Baseband Output  14 VCC Baseband +5V Supply. Bypass with a 10pF capacitor from this pin to pin 12 (GND), as close to the IC possible. Connect an additional 0.1μF capacitor in parallel with the 10pF capacitor (placement less or 15 QDC Q Channel Offset-Correction Noninverting Input. Connect a 0.22μF (typ) capacitor between QDC and This capacitor must be placed as close to the IC as possible. See Layout Considerations section.  16 QDC Q Channel Offset-Correction Inverting Input. Connect a 0.22μF (typ) capacitor between QDC and QDC capacitor must be placed as close to the IC as possible. See Layout Considerations section.  17 IDC I Channel Offset-Correction Inverting Input. Connect a 0.22μF (typ) capacitor between IDC and IDC. Taylor of the placed as close to the IC as possible. See Layout Considerations section.  18 IDC I Channel Offset-Correction Noninverting Input. Connect a 0.22μF (typ) capacitor between IDC and IDC. This capacitor must be placed as close to the IC as possible. See Layout Considerations section.  19 VCC RF +5V Supply. Bypass with a 10pF capacitor from this pin to pin 19 (GND) as close to the IC as possible. See Layout Considerations section.                                                                        | PIN   | NAME  | FUNCTION                                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3, 12 GND Baseband Ground:  4 VCC RF +5V Supply. Bypass with a 22pF capacitor from this pin to pin 11 (GND), as close to the IC as pos 5 GND Ground (substrate)  6 VCC RF +5V Supply. Bypass with a 22pF capacitor from this pin to pin 9 (GND), as close to the IC as poss 7 RFIN RF Noninverting Input. Couple through a 22pF capacitor directly to a 50Ω signal source.  8 RFIN RF Inverting Input. Connect to a 22pF series capacitor and a 51Ω resistor to ground.  9, 11, 19, 24 GND RF Ground. Connect directly to the ground plane.  10 AGC Automatic Gain-Control Input. Bypass this pin with a 1000pF capacitor close to the pin, to minimize of pling.  13 QOUT Q Channel Baseband Output  14 VCC Baseband +5V Supply. Bypass with a 10pF capacitor from this pin to pin 12 (GND), as close to the IC possible. Connect an additional 0.1μF capacitor in parallel with the 10pF capacitor (placement less of Q Channel Offset-Correction Noninverting Input. Connect a 0.22μF (typ) capacitor between QDC and This capacitor must be placed as close to the IC as possible. See Layout Considerations section.  16 QDC Q Channel Offset-Correction Inverting Input. Connect a 0.22μF (typ) capacitor between QDC and QDC capacitor must be placed as close to the IC as possible. See Layout Considerations section.  17 IDC I Channel Offset-Correction Inverting Input. Connect a 0.22μF (typ) capacitor between IDC and IDC. 1 capacitor must be placed as close to the IC as possible. See Layout Considerations section.  18 IDC I Channel Offset-Correction Noninverting Input. Connect a 0.22μF (typ) capacitor between IDC and IDC. 1 Channel Offset-Correction Noninverting Input. Connect a 0.22μF (typ) capacitor between IDC and IDC. 1 Channel Offset-Correction Noninverting Input. Connect a 0.22μF (typ) capacitor between IDC and IDC. 1 IDC and   | 1     | Vcc   | Baseband +5V Supply. Bypass with a 10pF capacitor from this pin to pin 3 (GND), as close to the IC as possible. Connect an additional 0.1µF capacitor in parallel with the 10pF capacitor (placement less critical).  |

| 4 VCC RF +5V Supply. Bypass with a 22pF capacitor from this pin to pin 11 (GND), as close to the IC as pos 5 GND Ground (substrate)  6 VCC RF +5V Supply. Bypass with a 22pF capacitor from this pin to pin 9 (GND), as close to the IC as poss 7 RFIN RF Noninverting Input. Couple through a 22pF capacitor directly to a 50Ω signal source.  8 RFIN RF Inverting Input. Connect to a 22pF series capacitor and a 51Ω resistor to ground.  9, 11, 19, 24 GND RF Ground. Connect directly to the ground plane.  10 AGC Automatic Gain-Control Input. Bypass this pin with a 1000pF capacitor close to the pin, to minimize of pling.  13 QOUT Q Channel Baseband Output  14 VCC Baseband +5V Supply. Bypass with a 10pF capacitor from this pin to pin 12 (GND), as close to the IC possible. Connect an additional 0.1μF capacitor in parallel with the 10pF capacitor (placement less or 15 QDC Q Channel Offset-Correction Noninverting Input. Connect a 0.22μF (typ) capacitor between QDC and This capacitor must be placed as close to the IC as possible. See Layout Considerations section.  16 QDC Q Channel Offset-Correction Inverting Input. Connect a 0.22μF (typ) capacitor between QDC and QD capacitor must be placed as close to the IC as possible. See Layout Considerations section.  17 IDC I Channel Offset-Correction Inverting Input. Connect a 0.22μF (typ) capacitor between IDC and QD capacitor must be placed as close to the IC as possible. See Layout Considerations section.  18 IDC I Channel Offset-Correction Noninverting Input. Connect a 0.22μF (typ) capacitor between IDC and IDC 1 capacitor must be placed as close to the IC as possible. See Layout Considerations section.  18 IDC Local-Oscillator Complementary Input Port (Figure 1)  20 Vcc RF +5V Supply. Bypass with a 10pF capacitor from this pin to pin 19 (GND) as close to the IC as possible. PSGND Prescaler Ground. To disable the prescaler, leave this pin open.                                                                                                                                                | 2     | IOUT  | I Channel Baseband Output                                                                                                                                                                                             |

| 5 GND Ground (substrate) 6 VCC RF +5V Supply. Bypass with a 22pF capacitor from this pin to pin 9 (GND), as close to the IC as poss 7 RFIN RF Noninverting Input. Couple through a 22pF capacitor directly to a 50Ω signal source. 8 RFIN RF Inverting Input. Connect to a 22pF series capacitor and a 51Ω resistor to ground. 9, 11, 19, 24 GND RF Ground. Connect directly to the ground plane. 10 AGC Automatic Gain-Control Input. Bypass this pin with a 1000pF capacitor close to the pin, to minimize or pling. 13 QOUT Q Channel Baseband Output 14 VCC Baseband +5V Supply. Bypass with a 10pF capacitor from this pin to pin 12 (GND), as close to the IC possible. Connect an additional 0.1μF capacitor in parallel with the 10pF capacitor (placement less or 15 QDC Q Channel Offset-Correction Noninverting Input. Connect a 0.22μF (typ) capacitor between QDC and This capacitor must be placed as close to the IC as possible. See Layout Considerations section. 16 QDC Q Channel Offset-Correction Inverting Input. Connect a 0.22μF (typ) capacitor between QDC and QDC capacitor must be placed as close to the IC as possible. See Layout Considerations section. 17 IDC I Channel Offset-Correction Inverting Input. Connect a 0.22μF (typ) capacitor between IDC and IDC. 1 Capacitor must be placed as close to the IC as possible. See Layout Considerations section. 18 IDC I Channel Offset-Correction Noninverting Input. Connect a 0.22μF (typ) capacitor between IDC and IDC. 1 This capacitor must be placed as close to the IC as possible. See Layout Considerations section. 20 VCC RF +5V Supply. Bypass with a 10pF capacitor from this pin to pin 19 (GND) as close to the IC as possible. See Layout Considerations section. 21 Local-Oscillator Complementary Input Port (Figure 1) 22 Lo Local-Oscillator Complementary Input Port (Figure 1) 23 VCC RF +5V Supply. Bypass with a 10pF capacitor from this pin to pin 24 (GND) as close to the IC as possible. PSGND Prescaler Ground. To disable the prescaler, leave this pin open.                                                | 3, 12 | GND   | Baseband Ground                                                                                                                                                                                                       |

| 6 Vcc RF +5V Supply. Bypass with a 22pF capacitor from this pin to pin 9 (GND), as close to the IC as poss 7 RFIN RF Noninverting Input. Couple through a 22pF capacitor directly to a 50Ω signal source.  8 RFIN RF Inverting Input. Connect to a 22pF series capacitor and a 51Ω resistor to ground.  9, 11, 19, 24 GND RF Ground. Connect directly to the ground plane.  10 AGC Automatic Gain-Control Input. Bypass this pin with a 1000pF capacitor close to the pin, to minimize concerns and a 51Ω resistor to ground.  11 Vcc Baseband +5V Supply. Bypass with a 10pF capacitor from this pin to pin 12 (GND), as close to the IC possible. Connect an additional 0.1μF capacitor in parallel with the 10pF capacitor (placement less concerns and placed as close to the IC as possible. See Layout Considerations section.  12 QDC Channel Offset-Correction Inverting Input. Connect a 0.22μF (typ) capacitor between QDC and QDC capacitor must be placed as close to the IC as possible. See Layout Considerations section.  13 QDC I Channel Offset-Correction Inverting Input. Connect a 0.22μF (typ) capacitor between QDC and QDC capacitor must be placed as close to the IC as possible. See Layout Considerations section.  14 IDC I Channel Offset-Correction Inverting Input. Connect a 0.22μF (typ) capacitor between IDC and QDC capacitor must be placed as close to the IC as possible. See Layout Considerations section.  18 IDC I Channel Offset-Correction Noninverting Input. Connect a 0.22μF (typ) capacitor between IDC and IDC. This capacitor must be placed as close to the IC as possible. See Layout Considerations section.  19 Vcc RF +5V Supply. Bypass with a 10pF capacitor from this pin to pin 19 (GND) as close to the IC as possible. Confection Input Port (Figure 1)  10 Local-Oscillator Complementary Input Port (Figure 1)  11 Vcc RF +5V Supply. Bypass with a 10pF capacitor from this pin to pin 24 (GND) as close to the IC as possible. PSGND Prescaler Ground. To disable the prescaler, leave this pin open.                                                       | 4     | Vcc   | RF +5V Supply. Bypass with a 22pF capacitor from this pin to pin 11 (GND), as close to the IC as possible.                                                                                                            |

| 7 RFIN RF Noninverting Input. Couple through a 22pF capacitor directly to a 50Ω signal source.  8 RFIN RF Inverting Input. Connect to a 22pF series capacitor and a 51Ω resistor to ground.  9, 11, 19, 24 GND RF Ground. Connect directly to the ground plane.  10 AGC Automatic Gain-Control Input. Bypass this pin with a 1000pF capacitor close to the pin, to minimize or pling.  13 QOUT Q Channel Baseband Output  14 VCC Baseband +5V Supply. Bypass with a 10pF capacitor from this pin to pin 12 (GND), as close to the IC possible. Connect an additional 0.1μF capacitor in parallel with the 10pF capacitor (placement less or DC and This capacitor must be placed as close to the IC as possible. See Layout Considerations section.  16 QDC Channel Offset-Correction Inverting Input. Connect a 0.22μF (typ) capacitor between QDC and QDC capacitor must be placed as close to the IC as possible. See Layout Considerations section.  17 IDC I Channel Offset-Correction Inverting Input. Connect a 0.22μF (typ) capacitor between IDC and QDC capacitor must be placed as close to the IC as possible. See Layout Considerations section.  18 IDC I Channel Offset-Correction Inverting Input. Connect a 0.22μF (typ) capacitor between IDC and IDC. This capacitor must be placed as close to the IC as possible. See Layout Considerations section.  18 IDC I Channel Offset-Correction Noninverting Input. Connect a 0.22μF (typ) capacitor between IDC and IDC. This capacitor must be placed as close to the IC as possible. See Layout Considerations section.  20 VCC RF +5V Supply. Bypass with a 10pF capacitor from this pin to pin 19 (GND) as close to the IC as possible. PSGND Prescaler Ground. To disable the prescaler, leave this pin open.                                                                                                                                                                                                                                                                                                                                              | 5 .   | GND   | Ground (substrate)                                                                                                                                                                                                    |

| 8 RFIN RF Inverting Input. Connect to a 22pF series capacitor and a 51Ω resistor to ground.  9, 11, 19, 24 GND RF Ground. Connect directly to the ground plane.  10 AGC Automatic Gain-Control Input. Bypass this pin with a 1000pF capacitor close to the pin, to minimize conditions of pling.  13 QOUT Q Channel Baseband Output  14 Vcc Baseband +5V Supply. Bypass with a 10pF capacitor from this pin to pin 12 (GND), as close to the IC possible. Connect an additional 0.1μF capacitor in parallel with the 10pF capacitor (placement less or Institute of In  | 6     | Vcc   | RF +5V Supply. Bypass with a 22pF capacitor from this pin to pin 9 (GND), as close to the IC as possible.                                                                                                             |

| 9, 11, 19, 24  GND RF Ground. Connect directly to the ground plane.  10 AGC Automatic Gain-Control Input. Bypass this pin with a 1000pF capacitor close to the pin, to minimize concerns pling.  13 QOUT Q Channel Baseband Output  14 Vcc Baseband +5V Supply. Bypass with a 10pF capacitor from this pin to pin 12 (GND), as close to the IC possible. Connect an additional 0.1µF capacitor in parallel with the 10pF capacitor (placement less or This capacitor must be placed as close to the IC as possible. See Layout Considerations section.  16 QDC Q Channel Offset-Correction Inverting Input. Connect a 0.22µF (typ) capacitor between QDC and This capacitor must be placed as close to the IC as possible. See Layout Considerations section.  17 IDC I Channel Offset-Correction Inverting Input. Connect a 0.22µF (typ) capacitor between IDC and QDC capacitor must be placed as close to the IC as possible. See Layout Considerations section.  18 IDC I Channel Offset-Correction Noninverting Input. Connect a 0.22µF (typ) capacitor between IDC and IDC. 1 capacitor must be placed as close to the IC as possible. See Layout Considerations section.  18 IDC I Channel Offset-Correction Noninverting Input. Connect a 0.22µF (typ) capacitor between IDC and IDC. 1 This capacitor must be placed as close to the IC as possible. See Layout Considerations section.  20 Vcc RF +5V Supply. Bypass with a 10pF capacitor from this pin to pin 19 (GND) as close to the IC as possible. In Local-Oscillator Input Port (Figure 1)  21 LO Local-Oscillator Input Port (Figure 1)  22 Vcc RF +5V Supply. Bypass with a 10pF capacitor from this pin to pin 24 (GND) as close to the IC as possible. PSGND Prescaler Ground. To disable the prescaler, leave this pin open.                                                                                                                                                                                                                                                                                                                            | 7     | RFIN  | RF Noninverting Input. Couple through a 22pF capacitor directly to a $50\Omega$ signal source.                                                                                                                        |

| 19, 24  AGC Automatic Gain-Control Input. Bypass this pin with a 1000pF capacitor close to the pin, to minimize or pling.  AGC Automatic Gain-Control Input. Bypass this pin with a 1000pF capacitor close to the pin, to minimize or pling.  AGC  Automatic Gain-Control Input. Bypass this pin with a 1000pF capacitor close to the pin, to minimize or pling.  AGC  Channel Baseband Output  AGC  Baseband +5V Supply. Bypass with a 10pF capacitor from this pin to pin 12 (GND), as close to the IC possible. Connect an additional 0.1µF capacitor in parallel with the 10pF capacitor (placement less or This capacitor must be placed as close to the IC as possible. See Layout Considerations section.  Channel Offset-Correction Inverting Input. Connect a 0.22µF (typ) capacitor between QDC and QDC capacitor must be placed as close to the IC as possible. See Layout Considerations section.  IDC  I Channel Offset-Correction Inverting Input. Connect a 0.22µF (typ) capacitor between IDC and IDC. To capacitor must be placed as close to the IC as possible. See Layout Considerations section.  IDC  I Channel Offset-Correction Noninverting Input. Connect a 0.22µF (typ) capacitor between IDC and IDC. This capacitor must be placed as close to the IC as possible. See Layout Considerations section.  CO  VCC  RF +5V Supply. Bypass with a 10pF capacitor from this pin to pin 19 (GND) as close to the IC as possible. Conline of the IC as possib | 8     | RFIN  | RF Inverting Input. Connect to a 22pF series capacitor and a 51Ω resistor to ground.                                                                                                                                  |

| pling.  13 QOUT Q Channel Baseband Output  14 VCC Baseband +5V Supply. Bypass with a 10pF capacitor from this pin to pin 12 (GND), as close to the IC possible. Connect an additional 0.1µF capacitor in parallel with the 10pF capacitor (placement less or IC possible. Connect an additional 0.1µF capacitor in parallel with the 10pF capacitor (placement less or IC QC Channel Offset-Correction Noninverting Input. Connect a 0.22µF (typ) capacitor between QDC and This capacitor must be placed as close to the IC as possible. See Layout Considerations section.  16 QDC Q Channel Offset-Correction Inverting Input. Connect a 0.22µF (typ) capacitor between QDC and QDC capacitor must be placed as close to the IC as possible. See Layout Considerations section.  17 IDC I Channel Offset-Correction Inverting Input. Connect a 0.22µF (typ) capacitor between IDC and IDC. 1 Capacitor must be placed as close to the IC as possible. See Layout Considerations section.  18 IDC I Channel Offset-Correction Noninverting Input. Connect a 0.22µF (typ) capacitor between IDC and IDC. 1 This capacitor must be placed as close to the IC as possible. See Layout Considerations section.  20 Vcc RF +5V Supply. Bypass with a 10pF capacitor from this pin to pin 19 (GND) as close to the IC as possible. IC Local-Oscillator Complementary Input Port (Figure 1)  22 LO Local-Oscillator Input Port (Figure 1)  23 Vcc RF +5V Supply. Bypass with a 10pF capacitor from this pin to pin 24 (GND) as close to the IC as possible. Prescaler Ground. To disable the prescaler, leave this pin open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       | GND   | RF Ground. Connect directly to the ground plane.                                                                                                                                                                      |

| 14 Vcc Baseband +5V Supply. Bypass with a 10pF capacitor from this pin to pin 12 (GND), as close to the IC possible. Connect an additional 0.1μF capacitor in parallel with the 10pF capacitor (placement less or IC QC Channel Offset-Correction Noninverting Input. Connect a 0.22μF (typ) capacitor between QDC and This capacitor must be placed as close to the IC as possible. See Layout Considerations section.  16 QC Channel Offset-Correction Inverting Input. Connect a 0.22μF (typ) capacitor between QDC and QC capacitor must be placed as close to the IC as possible. See Layout Considerations section.  17 IDC I Channel Offset-Correction Inverting Input. Connect a 0.22μF (typ) capacitor between IDC and IDC. 1 capacitor must be placed as close to the IC as possible. See Layout Considerations section.  18 IDC I Channel Offset-Correction Noninverting Input. Connect a 0.22μF (typ) capacitor between IDC and IDC. 1 This capacitor must be placed as close to the IC as possible. See Layout Considerations section.  20 Vcc RF +5V Supply. Bypass with a 10pF capacitor from this pin to pin 19 (GND) as close to the IC as possible. IC Local-Oscillator Complementary Input Port (Figure 1)  22 LO Local-Oscillator Input Port (Figure 1)  23 Vcc RF +5V Supply. Bypass with a 10pF capacitor from this pin to pin 24 (GND) as close to the IC as possible. Prescaler Ground. To disable the prescaler, leave this pin open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10    | AGC   | Automatic Gain-Control Input. Bypass this pin with a 1000pF capacitor close to the pin, to minimize coupling.                                                                                                         |

| possible. Connect an additional 0.1µF capacitor in parallel with the 10pF capacitor (placement less or DDC possible. Connect an additional 0.1µF capacitor in parallel with the 10pF capacitor (placement less or DDC possible. Connect and DDC placement less or DDC pl | 13    | QOUT  | Q Channel Baseband Output                                                                                                                                                                                             |

| This capacitor must be placed as close to the IC as possible. See Layout Considerations section.  Q Channel Offset-Correction Inverting Input. Connect a 0.22µF (typ) capacitor between QDC and QDC capacitor must be placed as close to the IC as possible. See Layout Considerations section.  I Channel Offset-Correction Inverting Input. Connect a 0.22µF (typ) capacitor between IDC and IDC. It capacitor must be placed as close to the IC as possible. See Layout Considerations section.  I Channel Offset-Correction Noninverting Input. Connect a 0.22µF (typ) capacitor between IDC and IDC. It channel Offset-Correction Noninverting Input. Connect a 0.22µF (typ) capacitor between IDC and IDC. This capacitor must be placed as close to the IC as possible. See Layout Considerations section.  VCC RF +5V Supply. Bypass with a 10pF capacitor from this pin to pin 19 (GND) as close to the IC as possible. ICO Local-Oscillator Input Port (Figure 1)  LO Local-Oscillator Input Port (Figure 1)  VCC RF +5V Supply. Bypass with a 10pF capacitor from this pin to pin 24 (GND) as close to the IC as possible. Prescaler Ground. To disable the prescaler, leave this pin open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 14    | Vcc   | Baseband +5V Supply. Bypass with a 10pF capacitor from this pin to pin 12 (GND), as close to the IC as possible. Connect an additional 0.1µF capacitor in parallel with the 10pF capacitor (placement less critical). |

| capacitor must be placed as close to the IC as possible. See Layout Considerations section.  IChannel Offset-Correction Inverting Input. Connect a 0.22µF (typ) capacitor between IDC and IDC. It capacitor must be placed as close to the IC as possible. See Layout Considerations section.  IChannel Offset-Correction Noninverting Input. Connect a 0.22µF (typ) capacitor between IDC and IDC. It channel Offset-Correction Noninverting Input. Connect a 0.22µF (typ) capacitor between IDC and IDC and IDC. This capacitor must be placed as close to the IC as possible. See Layout Considerations section.  VCC RF +5V Supply. Bypass with a 10pF capacitor from this pin to pin 19 (GND) as close to the IC as possible. Cocal-Oscillator Complementary Input Port (Figure 1)  LO Local-Oscillator Input Port (Figure 1)  VCC RF +5V Supply. Bypass with a 10pF capacitor from this pin to pin 24 (GND) as close to the IC as possible. Prescaler Ground. To disable the prescaler, leave this pin open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 15    | QDC   | Q Channel Offset-Correction Noninverting Input. Connect a 0.22µF (typ) capacitor between QDC and QDC. This capacitor must be placed as close to the IC as possible. See <i>Layout Considerations</i> section.         |

| capacitor must be placed as close to the IC as possible. See Layout Considerations section.  IChannel Offset-Correction Noninverting Input. Connect a 0.22µF (typ) capacitor between IDC and IC This capacitor must be placed as close to the IC as possible. See Layout Considerations section.  VCC RF +5V Supply. Bypass with a 10pF capacitor from this pin to pin 19 (GND) as close to the IC as possible. See Layout Considerations section.  Local-Oscillator Complementary Input Port (Figure 1)  Local-Oscillator Input Port (Figure 1)  VCC RF +5V Supply. Bypass with a 10pF capacitor from this pin to pin 24 (GND) as close to the IC as possible. See Layout Considerations section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 16    | apc   | Q Channel Offset-Correction Inverting Input. Connect a 0.22µF (typ) capacitor between QDC and QDC. This capacitor must be placed as close to the IC as possible. See Layout Considerations section.                   |

| This capacitor must be placed as close to the IC as possible. See Layout Considerations section.  VCC RF +5V Supply. Bypass with a 10pF capacitor from this pin to pin 19 (GND) as close to the IC as poss  Local-Oscillator Complementary Input Port (Figure 1)  LO Local-Oscillator Input Port (Figure 1)  VCC RF +5V Supply. Bypass with a 10pF capacitor from this pin to pin 24 (GND) as close to the IC as poss  PSGND Prescaler Ground. To disable the prescaler, leave this pin open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 17    | TDC   | I Channel Offset-Correction Inverting Input. Connect a 0.22µF (typ) capacitor between IDC and IDC. This capacitor must be placed as close to the IC as possible. See Layout Considerations section.                   |

| 21 TO Local-Oscillator Complementary Input Port (Figure 1)  22 LO Local-Oscillator Input Port (Figure 1)  23 VCC RF +5V Supply. Bypass with a 10pF capacitor from this pin to pin 24 (GND) as close to the IC as poss  25 PSGND Prescaler Ground. To disable the prescaler, leave this pin open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 18    | IDC   | I Channel Offset-Correction Noninverting Input. Connect a 0.22µF (typ) capacitor between IDC and IDC. This capacitor must be placed as close to the IC as possible. See <i>Layout Considerations</i> section.         |

| 22 LO Local-Oscillator Input Port (Figure 1) 23 VCC RF +5V Supply. Bypass with a 10pF capacitor from this pin to pin 24 (GND) as close to the IC as poss 25 PSGND Prescaler Ground. To disable the prescaler, leave this pin open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20    | Vcc   | RF +5V Supply. Bypass with a 10pF capacitor from this pin to pin 19 (GND) as close to the IC as possible.                                                                                                             |

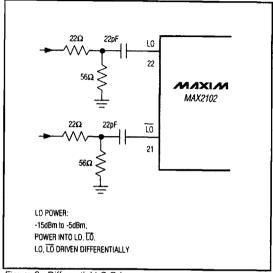

| 23 VCC RF +5V Supply. Bypass with a 10pF capacitor from this pin to pin 24 (GND) as close to the IC as poss 25 PSGND Prescaler Ground. To disable the prescaler, leave this pin open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 21    | LO    | Local-Oscillator Complementary Input Port (Figure 1)                                                                                                                                                                  |

| 25 PSGND Prescaler Ground. To disable the prescaler, leave this pin open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 22    | LO    | Local-Oscillator Input Port (Figure 1)                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 23    | Vcc   | RF +5V Supply. Bypass with a 10pF capacitor from this pin to pin 24 (GND) as close to the IC as possible.                                                                                                             |

| 26 PSOUT Prescaler Output. Drives CMOS load. Connect 2kΩ from this pin to GND (if the prescaler is enabled).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 25    | PSGND | Prescaler Ground. To disable the prescaler, leave this pin open.                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 26    | PSOUT | Prescaler Output. Drives CMOS load. Connect 2kΩ from this pin to GND (if the prescaler is enabled).                                                                                                                   |

| 27 MOD Prescaler Modulus Control. Leave open when the prescaler is disabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 27    | MOD   | Prescaler Modulus Control. Leave open when the prescaler is disabled.                                                                                                                                                 |

| 28 VCC Prescaler +5V Supply. Bypass with a 1000pF capacitor. Must be connected even if the prescaler is dis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 28    | Vcc   | Prescaler +5V Supply. Bypass with a 1000pF capacitor. Must be connected even if the prescaler is disabled.                                                                                                            |

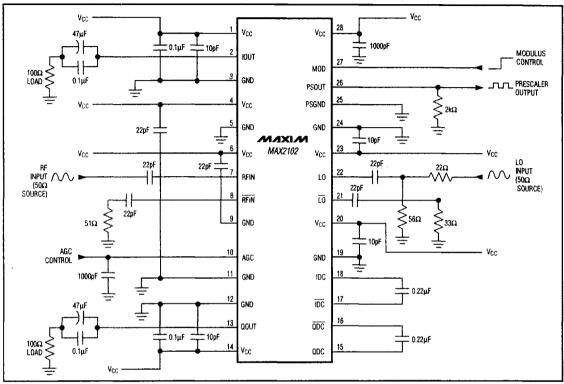

Figure 1. Typical Operating Circuit

#### Detailed Description

The MAX2102 downconverts signals in the range 950MHz to 2150MHz directly to baseband I/Q signals. It is targeted for digital DBS tuner applications where a direct downconversion provides a cost savings over prior-art multiple-conversion approaches. However, the MAX2102 is applicable to any system requiring a broadband I/Q downconversion.

Internally, the MAX2102 consists of a broadband frontend variable gain stage, a quadrature downconverter, an oscillator buffer, high-linearity I and Q baseband amplifiers, and offset correction amplifiers.

The front-end AGC dynamic range is over 50dB. Specifically, the AGC control can be adjusted so that a sine wave at RFIN ranging in power from -69dBm to -19dBm will produce a sine wave at IOUT and QOUT at 500mVp-p levels. The noise figure is lowest when the AGC is at its maximum gain setting (see *Typical Operating Characteristics*). The VSWR at RFIN is unaffected by the AGC setting.

The LO buffer accepts an external LO signal at LO,  $\overline{\text{LO}}$ , and internally limits the signals to provide a consistent on-chip LO level. The LO input drive level should be maintained within the specified limits (see *Applications Information* section).

The quadrature downconverter follows the front-end AGC. Two mixers are driven by the previous stage AGC amplifier output. The mixer LO ports are fed with the two LO signals, which are 90° apart in phase. These quadrature LO signals are generated on-chip using the LO signals from the LO buffer.

The resulting I/Q baseband signals are fed through separate I and Q channel baseband amplifiers. Robust output stages drive IOUT and QOUT. The outputs are capable of driving lowpass filters with  $100\Omega$  characteristic impedance (that is, the equivalent of an AC-coupled,  $100\Omega$  load). The baseband -3dB output bandwidth is over 90MHz.

### \_Applications Information

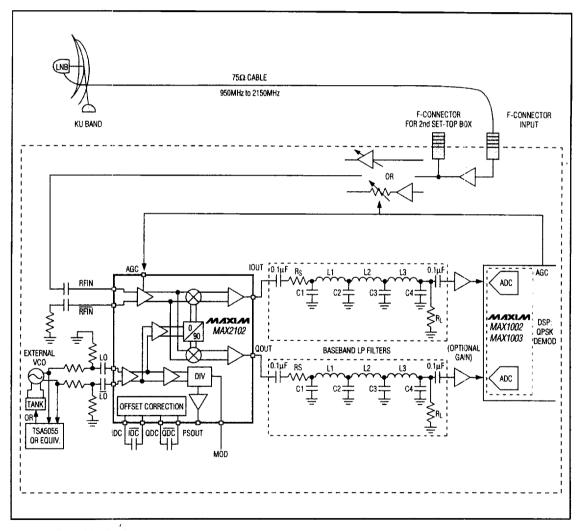

## Front-End Tuner Circuitry for DBS Tuners

In a typical application, the signal path ahead of the MAX2102 will include a discrete LNA/buffer and a PIN-diode attenuator. Alternatively, a dual-gate GaAsFET can serve this function. This circuitry is usually required

in order to meet system noise-figure requirements, may provide a buffered F-connector output, and may also be required to meet stringent LO leakage requirements. The PIN attenuator is typically controlled by the same voltage as the MAX2102 AGC control pin so that, overall, a single AGC line from the baseband processor can control the entire tuner.

Figure 2. Typical Application