### 功能特性

- 工作电压范围：3~5.5V

- 工作电流：

- 256KHz快速模式下8路ADC全开时，65mA

@AVDD，9.6mA@DVDD，<100uA@IOVDD

- 内置ADC与滤波器

- 八通道ADC

- 高精度Delta-Sigma ADC

- 支持5种降采样率，在不同模式下的数据率为：

快速模式：16K/32K/64K/128K/256KHz

中速模式：8K/16K/32K/64K/128KHz

经济模式：2K/4K/8K/16K/32KHz

- 支持连续数据转换

- 系统功能

- 支持引脚控制模式

- 16.38MHz外部输入时钟

- 支持上电自动复位

- 支持低电监测

- SPI 界面：

- 支援标准 4 线或 3 线 SPI 界面

- 支持最高 27MHz 通信时钟

- 支持daisy-chain串接模式

- 支持命令帧奇校验保护

- 支持主动时钟输出模式

- 支持写入及读取操作的 CRC 校验保护

- 工作温度范围：-40~+105°C

- 存储温度范围：-40~+125°C

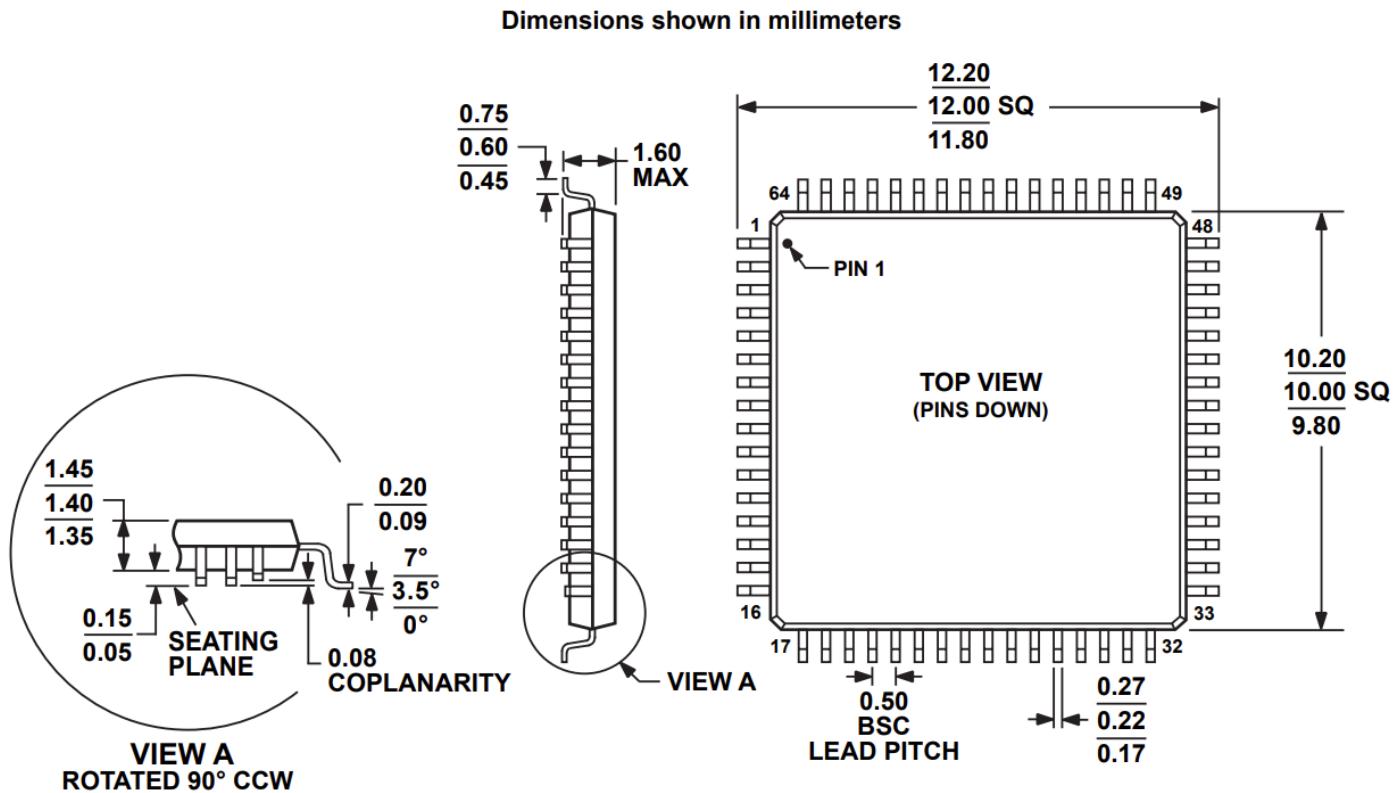

- 封装样式：LQFP-64 10x10 mm

### 应用场景

- 机床/飞机振动监测

- 音频/声呐/电网质量分析

- 液体/气体化学分析

- 医疗设备

- 工业过程控采集

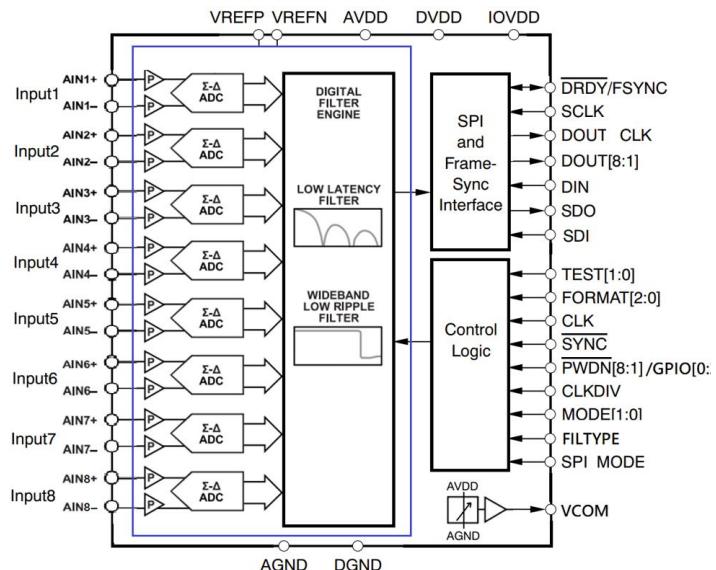

### 功能方块图

### 概述

CS5278为一款 SPI 接口的八通道 ADC 芯片，内置 8 路独立的 24BIT 高精度、中高速 ADC 芯片速度最高可达 256kHz。可用于各类设备、机床、飞机等的振动检测、音频分析、声呐、电网质量分析、医疗设备等各类需要高精度和高速测量的应用场合。

## 目录 TABLE OF CONTENTS

|                              |    |                           |    |

|------------------------------|----|---------------------------|----|

| 功能特性 .....                   | 1  | 5 寄存器描述 .....             | 17 |

| 功能方块图 .....                  | 1  | 5.1 寄存器地址 .....           | 17 |

| 应用场合 .....                   | 1  | 5.2 CONV_CONF0 寄存器 .....  | 27 |

| 概述 .....                     | 1  | 5.3 CONV_CONF1 寄存器 .....  | 19 |

| 修订追踪 .....                   | 2  | 5.5 CONV_CONF2 寄存器 .....  | 19 |

| 1 电器规格特性 .....               | 3  | 5.6 SYS_CONF0 寄存器 .....   | 20 |

| 1.1 极限参数 .....               | 3  | 5.7 SYS_CONF1 寄存器 .....   | 20 |

| 1.2 工作参数 .....               | 3  | 5.8 VERSION_ID 寄存器 .....  | 21 |

| 1.3 GPIO 参数 .....            | 3  | 6 滤波器特性 .....             | 21 |

| 1.4 ADC 性能指标 .....           | 4  | 6.1 宽带滤波器特性 .....         | 21 |

| 1.4.1. 快速模式 ADC 噪声和有效位 ..... | 5  | 6.2 CIC 滤波器特性 .....       | 22 |

| 1.4.2. 中速模式 ADC 噪声和有效位 ..... | 6  | 7 ADC 测试图表 .....          | 23 |

| 1.4.3. 经济模式 ADC 噪声和有效位 ..... | 7  | 7.1 快速模式下的信号频谱和噪声分布 ..... | 23 |

| 2 芯片引脚 .....                 | 8  | 7.2 增益和 Offset 的温漂 .....  | 25 |

| 2.1 引脚定义 .....               | 8  | 7.3 共模抑制比(CMRR) .....     | 26 |

| 3 功能模块描述 .....               | 10 | 8 应用辅助线路 .....            | 27 |

| 3.1 电源管理模块 .....             | 10 | 9 PACKAGING 封装尺寸图 .....   | 28 |

| 3.2 时钟模块 .....               | 10 | 10 参考 DEMO 程序 .....       | 29 |

| 3.3 SPI 模块 .....             | 10 |                           |    |

| 3.4 ADC 和滤波器模块 .....         | 11 |                           |    |

| 3.5 VCOM 偏置输出模块 .....        | 11 |                           |    |

| 3.6 控制模块 .....               | 11 |                           |    |

| 4 SPI 界面协定 .....             | 11 |                           |    |

| 4.1 读写命令帧 .....              | 11 |                           |    |

| 4.2 SPI CRC 校验 .....         | 12 |                           |    |

| 4.3 ADC 转换输出格式 .....         | 12 |                           |    |

| 4.4 SPI 接口复位 .....           | 16 |                           |    |

| 4.5 SPI 界面时序 .....           | 16 |                           |    |

修订追踪 V2.0

2022/12/20 初稿

2023/07/30 Noise Free Bits/SNR 修正

# 1 电器规格特性

## 1.1 极限参数

当外部输入或是环境参数超过下面条件时，很可能会对于芯片造成损坏或是缩短其使用寿命。下表只代表会造成损坏的范围，不代表可以正常工作的范围。

Table 1-1 极限参数表

| Symbol     | Ratings | Min  | Max  | Unit |

|------------|---------|------|------|------|

| AV+/DV+    | 电源电压    | -0.3 | +5.8 | V    |

| IOVDD-DGND | IO 口电压  | -0.3 | +5.8 | V    |

| DVDD-DGND  | 数字核电源电压 | -0.3 | +2.1 | V    |

| Vsig       | 信号输入信号  | -0.3 | +5.8 | V    |

| TS         | 存储温度    | -50  | +150 | °C   |

| TJ         | 工作温度    | -40  | +125 | °C   |

## 1.2 工作参数

Table 1-2 工作参数表

| Symbol   | Parameter | Conditions           | Min  | Typ  | Max  | Unit |

|----------|-----------|----------------------|------|------|------|------|

| AVDD     | 模拟电源电压    |                      | 4.5  | 5    | 5.5  | V    |

| AV+/DV+  | IO 口电压    |                      | 2.5  | 3.3  | 5.5  | V    |

| DVDD     | 数字核电源电压   |                      | 1.62 | 1.8  | 1.98 | V    |

| IACTIVE1 | 快速模式工作电流  | AVDD 电流 · 8 路 ADC 全开 |      | 6.5  |      | mA   |

|          |           | DVDD 电流 · 8 路 ADC 全开 |      | 9.6  |      | mA   |

|          |           | IOVDD 电流             |      | 0.05 |      | mA   |

| IACTIVE2 | 中速模式工作电流  | AVDD 电流 · 8 路 ADC 全开 |      | 33   |      | mA   |

|          |           | DVDD 电流 · 8 路 ADC 全开 |      | 4.9  |      | mA   |

|          |           | IOVDD 电流             |      | 0.05 |      | mA   |

| IACTIVE3 | 经济模式工作电流  | AVDD 电流 · 8 路 ADC 全开 |      | 14.6 |      | mA   |

|          |           | DVDD 电流 · 8 路 ADC 全开 |      | 1.35 |      | mA   |

|          |           | IOVDD 电流             |      | 0.05 |      | mA   |

| IPD      | 休眠电流      | AVDD 电流              |      | 0.6  |      | uA   |

|          |           | DVDD 电流              |      | 2    |      | uA   |

|          |           | IOVDD 电流             |      | 1    |      | uA   |

| TA       | 温度范围      |                      | -40  | 25   | 105  | °C   |

## 1.3 GPIO 参数

Table 1-3 GPIO 参数表

| Symbol | Parameter         | DV+ | Min  | Typ  | Max  | Unit |

|--------|-------------------|-----|------|------|------|------|

| VIH    | 输入信号高阈值           | 5V  | 4    |      | 5.5  | V    |

| VIL    | 输入信号低阈值           | 5V  | -0.3 |      | 1    | V    |

| VT+    | 施密特由低变高电压的阈值      | 5V  | 2.72 | 2.92 | 3.17 | V    |

| VT-    | 施密特由高变低电压的阈值      | 5V  | 1.85 | 2    | 2.17 | V    |

| IIH    | 输入高电平的电流          | 5V  |      |      | +1   | uA   |

| IIL    | 输入低电平的电流          | 5V  | -1   |      |      | uA   |

| VOL    | 输出低电平 (@IOL 电流条件) | 5V  |      |      | 0.4  | V    |

| VOH    | 输出高电平 (@IOH 电流条件) | 5V  | 4    |      |      | V    |

| IOL    | 输出低电平电流@VOL (max) | 5V  | 4.9  | 8.8  | 13.9 | mA   |

| IOH    | 输出高电平电流@VOH (min) | 5V  | 5.5  | 15.6 | 29.9 | mA   |

## 1.4 ADC 性能指标

Table 1-4 ADC 性能指标表

AV<sub>+</sub>=5V DV<sub>+</sub>=1.8V IOVDD=3.3V fclk=16.384KHz VREF<sub>+</sub>=2.5V 条件条件下测试

| Parameter                            | Min  | Typ                   | Max   | Unit          |

|--------------------------------------|------|-----------------------|-------|---------------|

| 精度                                   |      |                       |       |               |

| SNR                                  |      | 见 1.4.X 章节            |       | dB            |

| 有效位数 ( ENOB )                        |      | 见 1.4.X 章节            |       | BIT           |

| SFDR                                 |      | 110                   |       | dB            |

| 零漂 ( Offset )                        |      | 2                     |       | mV            |

| 零漂温漂 ( Offset drift )                |      | 0.5                   |       | uV/°C         |

| 增益误差(Gain error )                    |      | 0.1                   |       | %             |

| 增益温漂 ( Gain drift )                  |      | 1                     | 4     | ppm/°C        |

| 通道隔离度                                |      | 100                   |       | dB            |

| 信号输入                                 |      |                       |       |               |

| 输入信号共模范围                             |      | 2.5                   |       | V             |

| 输入信号幅度                               | -REF |                       | +REF  | REF=REFP-REFN |

| 差分输入电流                               |      | 1@开启信号<br>20@关闭信号     |       | nA            |

| 信号输入阻抗                               |      | 1M@开启信号<br>50K@关闭信号   |       | Ω             |

| 输入共模抑制比 ( CMRR )                     |      | 85                    |       | dB            |

| 基准电压                                 |      |                       |       |               |

| VREF <sub>+</sub> -VREF <sub>-</sub> | 0.5  | 2.5                   | 3.1   | V             |

| 宽带滤波器                                |      |                       |       |               |

| 通带纹波                                 |      | 0.003                 |       | dB            |

| 通带带宽                                 |      | 0.43*f (f 为 ADC 数据率 ) |       | Hz            |

| -3dBd 带宽                             |      | 0.47*f (f 为 ADC 数据率 ) |       | Hz            |

| 群延时                                  |      | 38                    |       | 数据点           |

| 完美建立时间                               |      | 76                    |       | 数据点           |

| CIC 滤波器                              |      |                       |       |               |

| -3dBd 带宽                             |      | 0.17*f (f 为 ADC 数据率 ) |       | Hz            |

| 完美建立时间                               |      | 6                     |       | 数据点           |

| 时钟                                   |      |                       |       |               |

| ADC 转换速率 ( Data Rate )               |      | 256                   | 312.5 | KHz           |

| 输入时钟频率                               |      | 16.384                | 20    | MHz           |

| 电源                                   |      |                       |       |               |

| AV <sub>+</sub> 电源范围                 | 4.5  | 5                     | 5.5   | V             |

| DV <sub>+</sub> 电源范围                 | 1.65 | 1.8                   | 1.95  | V             |

| IOVDD电源范围                            | 1.65 | 3.3/5                 | 5.5   | V             |

| 电源抑制比 ( PSRR )                       |      | 85                    |       | dB            |

## 1.4.1 快速模式ADC 噪声和有效位

Table 1-5 等效输入 RMS RMS 噪声(nV)

AVDD=5V DVDD=1.8V IOVDD=3.3V REF=2.5V 件下测得条件下测试

试

| 数据码率 ( Hz )                  | ENOB@滤波器类型 |         |

|------------------------------|------------|---------|

|                              | 宽带滤波器      | CIC 滤波器 |

| 16000                        | 4.15       | 2.9     |

| 32000                        | 5.87       | 4.11    |

| 64000                        | 8.29       | 5.81    |

| 128000 ( 对应引脚控制模式下 MODE=00 ) | 11.73      | 8.21    |

| 256000 ( 对应引脚控制模式下 MODE=00 ) | 16.59      | 11.61   |

Table 1-6 ENOB

AVDD=5V DVDD=1.8V IOVDD=3.3V REF=2.5V 件下测得条件下测试

| 数据码率 ( Hz )                  | ENOB@滤波器类型 |         |

|------------------------------|------------|---------|

|                              | 宽带滤波器      | CIC 滤波器 |

| 16000                        | 19.7       | 20.2    |

| 32000                        | 19.2       | 19.7    |

| 64000                        | 18.7       | 19.2    |

| 128000 ( 对应引脚控制模式下 MODE=00 ) | 18.2       | 18.7    |

| 256000 ( 对应引脚控制模式下 MODE=00 ) | 17.7       | 18.2    |

Table 1-7 Noise Free Bits

AVDD=5V DVDD=1.8V IOVDD=3.3V REF=2.5V 件下测得条件下测试

| 数据码率 ( Hz )                  | ENOB 波器类型 |         |

|------------------------------|-----------|---------|

|                              | 宽带滤波器     | CIC 滤波器 |

| 16000                        | 17.2      | 17.7    |

| 32000                        | 16.7      | 17.2    |

| 64000                        | 16.2      | 16.7    |

| 128000 ( 对应引脚控制模式下 MODE=00 ) | 15.7      | 16.2    |

| 256000 ( 对应引脚控制模式下 MODE=00 ) | 15.2      | 15.7    |

Table 1-8 SNR

AVDD=5V DVDD=1.8V IOVDD=3.3V REF=2.5V 件下测得条件下测试

| 数据码率 ( Hz )                  | ENOB 波器类型 |         |

|------------------------------|-----------|---------|

|                              | 宽带滤波器     | CIC 滤波器 |

| 16000                        | 115.3     | 118.4   |

| 32000                        | 112.3     | 115.4   |

| 64000                        | 109.3     | 112.4   |

| 128000 ( 对应引脚控制模式下 MODE=00 ) | 106.2     | 109.3   |

| 256000 ( 对应引脚控制模式下 MODE=00 ) | 103.2     | 106.3   |

## 1.4.2 中速模式ADC 噪声和有效位

Table 1-9 等效输入 RMS RMS 噪声(nV)

AVDD=5V DVDD=1.8V IOVDD=3.3V REFP=2.5V 件下测得条件下测试

试

| 数据码率 ( Hz )                 | ENOB@滤波器类型 |         |

|-----------------------------|------------|---------|

|                             | 宽带滤波器      | CIC 滤波器 |

| 8000                        | 3.96       | 2.77    |

| 16000                       | 5.6        | 3.92    |

| 32000                       | 7.92       | 5.54    |

| 64000 ( 对应引脚控制模式下 MODE=10 ) | 11.2       | 57.84   |

| 128000                      | 15.84      | 11.09   |

Table 1-10 ENOB

AVDD=5V DVDD=1.8V IOVDD=3.3V REFP=2.5V 件下测得条件下测试

| 数据码率 ( Hz )                 | ENOB@滤波器类型 |         |

|-----------------------------|------------|---------|

|                             | 宽带滤波器      | CIC 滤波器 |

| 8000                        | 19.8       | 20.3    |

| 16000                       | 19.3       | 19.8    |

| 32000                       | 18.8       | 19.3    |

| 64000 ( 对应引脚控制模式下 MODE=10 ) | 18.3       | 18.8    |

| 128000                      | 17.8       | 18.3    |

Table 1-11 Noise Free Bits

AVDD=5V DVDD=1.8V IOVDD=3.3V REFP=2.5V 件下测得条件下测试

| 数据码率 ( Hz )                 | ENOB@滤波器类型 |         |

|-----------------------------|------------|---------|

|                             | 宽带滤波器      | CIC 滤波器 |

| 8000                        | 17.3       | 17.8    |

| 16000                       | 16.8       | 17.3    |

| 32000                       | 16.3       | 16.8    |

| 64000 ( 对应引脚控制模式下 MODE=10 ) | 15.8       | 16.3    |

| 128000                      | 15.3       | 15.8    |

Table 1-12 SNR

AVDD=5V DVDD=1.8V IOVDD=3.3V REFP=2.5V 件下测得条件下测试

| 数据码率 ( Hz )                 | ENOB@滤波器类型 |         |

|-----------------------------|------------|---------|

|                             | 宽带滤波器      | CIC 滤波器 |

| 8000                        | 115.7      | 118.8   |

| 16000                       | 112.7      | 115.8   |

| 32000                       | 109.7      | 112.8   |

| 64000 ( 对应引脚控制模式下 MODE=10 ) | 106.6      | 109.7   |

| 128000                      | 103.6      | 106.7   |

## 1.5.3. 经济模式ADC 噪声和有效位

Table 1-13 等效输入 RMS RMS 噪声(nV)

AVDD=5V DVDD=1.8V IOVDD=3.3V REF=2.5V 件下测得条件下测试

试

| 数据码率 ( Hz )                 | ENOB@滤波器类型 |         |

|-----------------------------|------------|---------|

|                             | 宽带滤波器      | CIC 滤波器 |

| 2000                        | 3.76       | 2.63    |

| 4000                        | 5.32       | 3.72    |

| 8000                        | 7.52       | 5.27    |

| 16000 ( 对应引脚控制模式下 MODE=11 ) | 10.64      | 7.45    |

| 32000                       | 15.04      | 10.53   |

Table 1-14ENOB

AVDD=5V DVDD=1.8V IOVDD=3.3V REF=2.5V 件下测得条件下测试

| 数据码率 ( Hz )                 | ENOB@滤波器类型 |         |

|-----------------------------|------------|---------|

|                             | 宽带滤波器      | CIC 滤波器 |

| 2000                        | 19.8       | 20.3    |

| 4000                        | 19.3       | 19.8    |

| 8000                        | 18.8       | 19.3    |

| 16000 ( 对应引脚控制模式下 MODE=11 ) | 18.3       | 18.8    |

| 32000                       | 17.8       | 18.3    |

Table 1-15 Noise Free Bits

AVDD=5V DVDD=1.8V IOVDD=3.3V REF=2.5V 件下测得条件下测试

| 数据码率 ( Hz )                 | ENOB@滤波器类型 |         |

|-----------------------------|------------|---------|

|                             | 宽带滤波器      | CIC 滤波器 |

| 2000                        | 17.3       | 17.8    |

| 4000                        | 16.8       | 17.3    |

| 8000                        | 16.3       | 16.8    |

| 16000 ( 对应引脚控制模式下 MODE=11 ) | 15.8       | 16.3    |

| 32000                       | 15.3       | 15.8    |

Table 1-16 SNR

AVDD=5V DVDD=1.8V IOVDD=3.3V REF=2.5V 件下测得条件下测试

| 数据码率 ( Hz )                 | ENOB@滤波器类型 |         |

|-----------------------------|------------|---------|

|                             | 宽带滤波器      | CIC 滤波器 |

| 2000                        | 116.1      | 119.2   |

| 4000                        | 113.1      | 116.2   |

| 8000                        | 110.1      | 113.2   |

| 16000 ( 对应引脚控制模式下 MODE=11 ) | 107.1      | 110.2   |

| 32000                       | 104.1      | 107.2   |

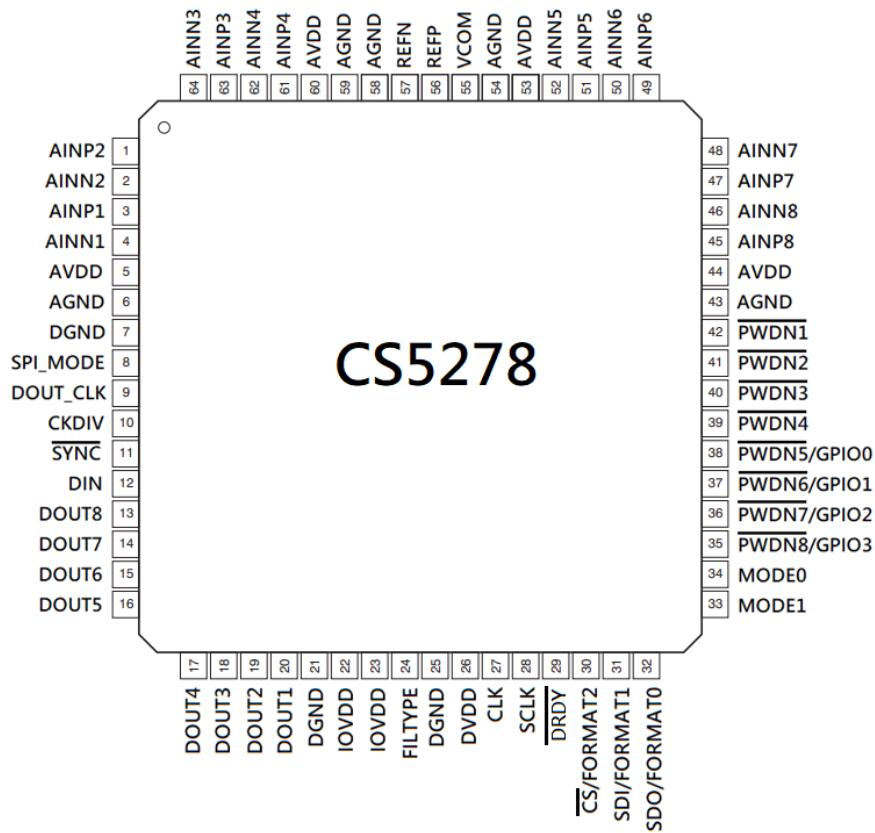

## 2 芯片引脚

### 2.1 引脚定义

Figure 2-1 CS5278 -LQFP64(10X10 )

Table 2-1

| Pin Number    | 名称         | 类型  | 描述                                                                                                                                                                     |

|---------------|------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | AINP2      | 输入  | Input2 ADC 的正端输入信号                                                                                                                                                     |

| 2             | AINN2      | 输入  | Input2 ADC 的负端输入信号                                                                                                                                                     |

| 3             | AINP1      | 输入  | Input1 ADC 的正端输入信号                                                                                                                                                     |

| 4             | AINN1      | 输入  | Input1 ADC 的负端输入信号                                                                                                                                                     |

| 5、44、53、60    | AVDD       | 电源  | 模拟电源 · AVDD 和 AGND 之间接一个 10uF 的瓷片电容                                                                                                                                    |

| 6、43、54、58、59 | AGND       | GND | 模拟地                                                                                                                                                                    |

| 7、21、25       | DGND       | GND | 数字地                                                                                                                                                                    |

| 8             | SPI_MODE   | 输入  | SPI 模式选择 0 : 引脚控制模式 1 : SPI 控制模式                                                                                                                                       |

| 9             | DOUT_CLK   | 输出  | 主动输出模式下 DOUT 的同步时钟 · 仅在 FORMAT=110or111 状态下作为输出数据的同步时钟 · 其他 FORMAT 下为高阻状态。此时钟信号的频率由 DOUT_CKSEL[1 : 0]选择 · 在引脚控制模式下 · DOUT_CKSEL[1 : 0]为默认值 · DOUT_CLK 频率固定为 ADC 时钟频率*2 |

| 10            | CKDIV      | 输入  | 该引脚接高电平时 · CLK 输入的工作时钟将除以 2 倍后再采用 · 一般情况下接地                                                                                                                            |

| 11            | SYNC       | 输入  | 同步信号输入 · 低电平有效。每次有更改控制 IO 状态 ( 引脚控制模式 ) 或更改内部控制寄存器设置 ( SPI 控制模式 ) 后都需要将 SYNC 拉低一次                                                                                      |

| 12            | DIN        | 输入  | Daisy-chain 串接模式输入信号                                                                                                                                                   |

| 13 ~ 20       | DOUT 8 ~ 1 | 输出  | ADC 数据转换输出                                                                                                                                                             |

| 22、23         | IOVDD      | 电源  | 数字 IO 电源 · DVDD 和 DGND 之间接一个 10uF 的瓷片电容。数字 IO 电源需与 MCU 的 IO 电源一致 · 但可以和 AVDD 电源不一致                                                                                     |

| 24            | FILTYPE    | 输入  | 滤波器模式选择 · 此引脚仅在引脚控制模式下有效。SPI 模式时 · 滤波器模式通过配置寄存器实现。0 : 宽带滤波器 1 : CIC 滤波器                                                                                                |

| Pin Number | 名称          | 类型    | 描述                                                                                                                                                                                                                                                                                                              |

|------------|-------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 26         | DVDD        | 电源    | 数字内核电源·由外部输入一个1.8V的电源DVDD和DGND之间接一个10uF瓷片电容。                                                                                                                                                                                                                                                                    |

| 27         | CLK         | 输入    | 片外工作时钟输入CLK输入16.384MHz的时钟·也可以输入16.384MHz+/-50%的其他时钟频率·此时输出的ADC数据率也做相应的比例变化                                                                                                                                                                                                                                      |

| 28         | SCLK        | 输入    | SPI输入时钟                                                                                                                                                                                                                                                                                                         |

| 29         | DRDY        | 输出    | 数据转换完成指示·当数据转换完成后此信号会拉低·当第一个时钟上升沿后会拉高·片外不需接上拉电阻                                                                                                                                                                                                                                                                 |

| 30         | FORMAT2/CSN | 输出    | 引脚控制模式下为FORMAT[2].FORMAT[2:0]的模式帮助见FORMAT寄存器部分的帮助·SPI控制模式下:FORMAT引脚失效·工作模式通过SPI设置;FORMAT[2:0]寄存器的方式实现;SPI控制模式为SPI片选                                                                                                                                                                                             |

| 31         | FORMAT1/SDI | 输入/输出 | 引脚控制模式下为FORMAT[1];SPI控制模式为SPI数据输入                                                                                                                                                                                                                                                                               |

| 32         | FORMAT0/SDO | 输入/输出 | 引脚控制模式下为FORMAT[0];SPI控制模式为SPI数据输出·片外需接10K OHM上拉电阻                                                                                                                                                                                                                                                               |

| 33 ~ 34    | MODE 1 ~ 0  | 输入    | 引脚控制模式下的ADC转换数据率选择·该引脚会控制CONV_CONFO寄存器里的CKSEL和DR位·具体如下:00:CKSEL=00·DR=000;对应8.912MADC工作频率·256KHz数据率·对应快速模式01:CKSEL=00·DR=001;对应8.912MADC工作频率·128KHz数据率·对应快速模式10:CKSEL=01·DR=001;对应4.096MADC工作频率·64KHz数据率·对应中速模式11:CKSEL=10·DR=001;对应1.024MADC工作频率·16KHz数据率·对应经济模式SPI控制模式下该引脚无作用·通过SPI接口配置CKSEL和DR寄存器可实现更灵活的数据选择 |

| 35         | PWDN8/GPIO3 | 输入/输出 | 引脚控制模式下·为ADC8使能控制输入·0=不使能·1=使能;SPI控制模式下·为GPIO3的输出·ADC8使控制通用SPI配置CH8PDN寄存器实现                                                                                                                                                                                                                                     |

| 36         | PWDN7/GPIO2 | 输入/输出 | 引脚控制模式下·为ADC7使能控制输入·0=不使能·1=使能;SPI控制模式下·为GPIO2的输出·ADC7使控制通用SPI配置CH7PDN寄存器实现                                                                                                                                                                                                                                     |

| 37         | PWDN6/GPIO1 | 输入/输出 | 引脚控制模式下·为ADC6使能控制输入·0=不使能·1=使能;SPI控制模式下·为GPIO1的输出·ADC6使控制通用SPI配置CH6PDN寄存器实现                                                                                                                                                                                                                                     |

| 38         | PWDN5/GPIO0 | 输入/输出 | 引脚控制模式下·为ADC5使能控制输入·0=不使能·1=使能;SPI控制模式下·为GPIO0的输出·ADC5使控制通用SPI配置CH5PDN寄存器实现                                                                                                                                                                                                                                     |

| 39         | PWDN4       | 输入/输出 | 引脚控制模式下·为ADC4使能控制输入·0=不使能·1=使能;SPI控制模式下·此引脚无功能·ADC4使控制通过SPI配置CH4PDN寄存器实现                                                                                                                                                                                                                                        |

| 40         | PWDN3       | 输入/输出 | 引脚控制模式下·为ADC3使能控制输入·0=不使能·1=使能;SPI控制模式下·此引脚无功能·ADC3使控制通过SPI配置CH3PDN寄存器实现                                                                                                                                                                                                                                        |

| 41         | PWDN2       | 输入/输出 | 引脚控制模式下·为ADC2使能控制输入·0=不使能·1=使能;SPI控制模式下·此引脚无功能·ADC2使控制通过SPI配置CH2PDN寄存器实现                                                                                                                                                                                                                                        |

| 42         | PWDN1       | 输入/输出 | 引脚控制模式下·为ADC1使能控制输入·0=不使能·1=使能;SPI控制模式下·此引脚无功能·ADC1使控制通过SPI配置CH1PDN寄存器实现                                                                                                                                                                                                                                        |

| 45         | AINP8       | 输入    | Input8 ADC 的正端输入信号                                                                                                                                                                                                                                                                                              |

| 46         | AINN8       | 输入    | Input8 ADC 的负端输入信号                                                                                                                                                                                                                                                                                              |

| 47         | AINP7       | 输入    | Input7 ADC 的正端输入信号                                                                                                                                                                                                                                                                                              |

| 48         | AINN7       | 输入    | Input7 ADC 的负端输入信号                                                                                                                                                                                                                                                                                              |

| 49         | AINP6       | 输入    | Input6 ADC 的正端输入信号                                                                                                                                                                                                                                                                                              |

| 50         | AINN6       | 输入    | Input6 ADC 的负端输入信号                                                                                                                                                                                                                                                                                              |

| 51         | AINP5       | 输入    | Input5 ADC 的正端输入信号                                                                                                                                                                                                                                                                                              |

| 52         | AINN5       | 输入    | Input 5ADC 的负端输入信号                                                                                                                                                                                                                                                                                              |

| 55         | VCOM        | 输出    | AVDD/2偏置电压输出·内部集成驱动电路·可提供+/-5mA的驱动能力·外部接一个0.1uF的去耦电容到AGND                                                                                                                                                                                                                                                       |

| 56         | REFP        | 输入/输出 | 基准电压源正输入端·REFP和REFN之间接10uF+0.1uF串联的瓷片电容                                                                                                                                                                                                                                                                         |

| Pin Number | 名称    | 类型    | 描述                    |

|------------|-------|-------|-----------------------|

| 57         | REFN  | 输入/输出 | 基准电压源负端输入端，一般情况接 AGND |

| 61         | AINP4 | 输入    | Input4 ADC 的正端输入信号    |

| 62         | AINN4 | 输入    | Input4 ADC 的负端输入信号    |

| 63         | AINP3 | 输入    | Input3 ADC 的正端输入信号    |

| 64         | AINN3 | 输入    | Input3 ADC 的负端输入信号    |

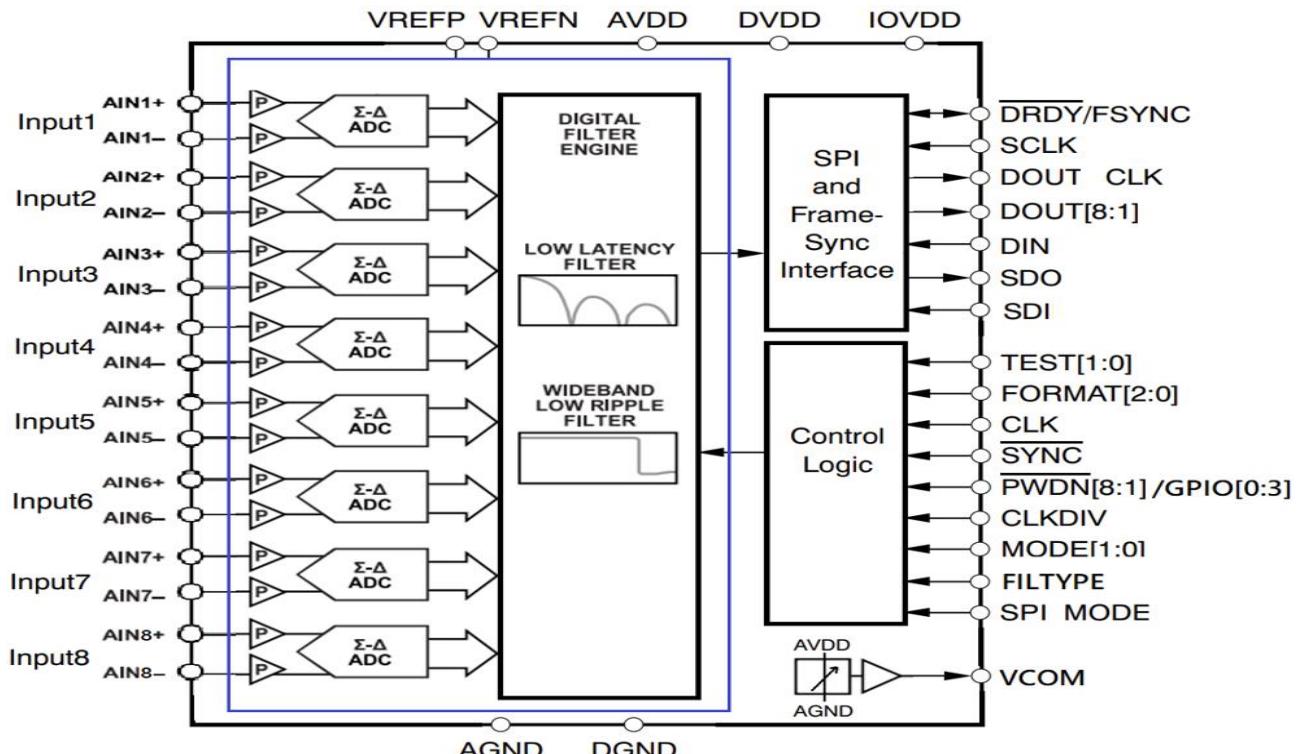

### 3 功能模块描述

Figure 3-1 CS5278 模块功能图

#### 3.1 电源管理模块

芯片由 IOVDD/DVDD/DGND · AVDD/AGND 三组电源供电，其中 DVDD 为数字内核电源，电压 1.8V · IOVDD 为数字 IO 电源，AVDD 为模拟电源，IOVDD 和 AVDD 可以加不同的电压。

#### 3.2 时钟模块

芯片工作时钟由 CLK 引脚提供，默认为 16.384MHz 输入时钟。也可以输入基准频率 +/-50% 的其他时钟频率，此时输出的 ADC 数据率也做相应的比例变化。

#### 3.3 SPI 模块

在引脚 SPI\_MODE=0 ( 引脚控制模式 ) 时，SPI 接口只用来读取 AD 转换数据。此时用到 SCLK、DRDY、DOUTx、DIN ( 仅在 daisy-chain 时 ) 引脚。读取 AD 转换数据还有个主动发送模式，此模式与常见的 SPI 模式有所区别，新增一个主动的输出时钟 DOUT\_CLK.

在引脚 SPI\_MODE=1 ( SPI 控制模式 ) 时，SPI 接口除用来读取 AD 转换数据外，还可用于存取内部控制寄存器，此时 FILTYPE/FORMATx/MODEx/PWDNx 引脚的控制作用无效。

### 3.4 ADC 和滤波器模块

CS5278 芯片内置 8 路独立的高性能 Delta-Sigma ADC 和滤波器模块，CS5278 芯片内置 4 路。ADC 模块的基准电压由外部 REF\_P 和 REF\_N 提供。REF\_P 和 REF\_N 可开启 BUFFER，默认关闭。ADC 输入信号端有 2 个信号 Buffer，默认开启，可通过 SPI 设置关闭。

滤波器有两种，宽带滤波器和 CIC 滤波器，引脚控制模式下通过 FILTYPE 引脚选择，SPI 模块下通过设置寄存器选择。

### 3.5 VCOM 偏置输出模块

芯片内置 AVDD/2 的 VCOM 偏置电压输出模块，该电压内部已有 Buffer，外部可不用再加运放构成的 Buffer。该电压可为外部信号或差分输出的运放提供偏置电压。

### 3.6 控制模块

用于实现 SPI 控制模式和引脚控制模式的切换，包括 FORMATx 和 PWDNx 引脚的切换复用等功能的实现。

## 4. SPI 界面协定

在引脚的 SPI\_MODE=0 ( 引脚控制模式 ) 时，SPI 接口只用来读取 AD 转换数据。此时用到 SCLK、DRDY、DOUTx、DIN ( 尽在 daisy-chain 时 ) 引脚。读取 AD 数据时的波形和协议与 SPI 模式下读取 AD 数据时一致。可参考下面 4.3 章节；读取 AD 转换数据还有主动发送模式，此模式与常见的 SPI 模式有所区别，新增一个主动输出时钟 DOUT\_CLK，可用于 FPGA 等形式的主动读取数据。

在引脚 SPI\_MODE=1 ( SPI 控制模式 ) 时，SPI 接口除用来读取 AD 转换数据外，还可用于存取内部控制寄存器，此时 FILTYPE/FORMATx/MODEx/PWDNx 引脚的控制作用无效。

相比引脚控制模式，SPI 控制模式可提供更多选择：

- ( 1 ) 可提供 8 个 ADC 通道信号的相位校正；

- ( 2 ) 提供 4 个 GPIO 用于控制外部器件；

- ( 3 ) 更灵活的 ADC 工作频率和过采样率选择；

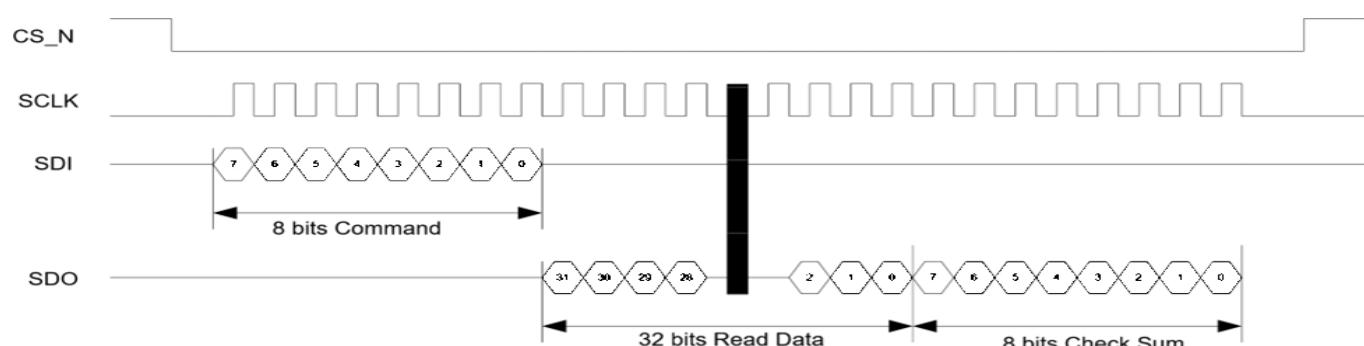

### 4.1 读写命令帧

读写命令帧的第一帧为命令帧，格式如下

Table 4-1 读写命令帧结构

| Bit |   |   |   |      |   |     |    |

|-----|---|---|---|------|---|-----|----|

| 7   | 6 | 5 | 4 | 3    | 2 | 1   | 0  |

| 0   |   |   |   | ADDR |   | R/W | PC |

Table 4-2 读写命令帧各位组意义

| BIT   | 名称   | 描述                                                                                                                                  |

|-------|------|-------------------------------------------------------------------------------------------------------------------------------------|

| 7     | 起始位  | 必须为 0                                                                                                                               |

| 6 : 2 | ADDR | 请参考 Table 4-2                                                                                                                       |

| 1     | R/W  | 读写类型选择<br>0 : 写      1 : 读                                                                                                          |

| 0     | PC   | Bit7 到 Bit1 之奇数同位检查位，当 Bit7~Bit1 有奇数个 1 时，PC 应为 0，当 Bit7~Bit1 有偶数个 1 时，PC 应为 1。若此奇数同位检查位错误，则该命令不被执行，且 SYS_CONF0 中的 ERR_CKS 位置会被置 1。 |

Table 4-3 读写命令帧地址字节汇总

| ADDR      | 暂存器名称      |

|-----------|------------|

| 0x00      | CONV_CONF0 |

| 0x01      | CONV_CONF1 |

| 0x02      | CONV_CONF2 |

| 0x03      | SYS_CONF0  |

| 0x04      | SYS_CONF1  |

| 0x05~0x0D | 保留         |

| 0x0E      | VERSION_ID |

| 0x0F      | 保留         |

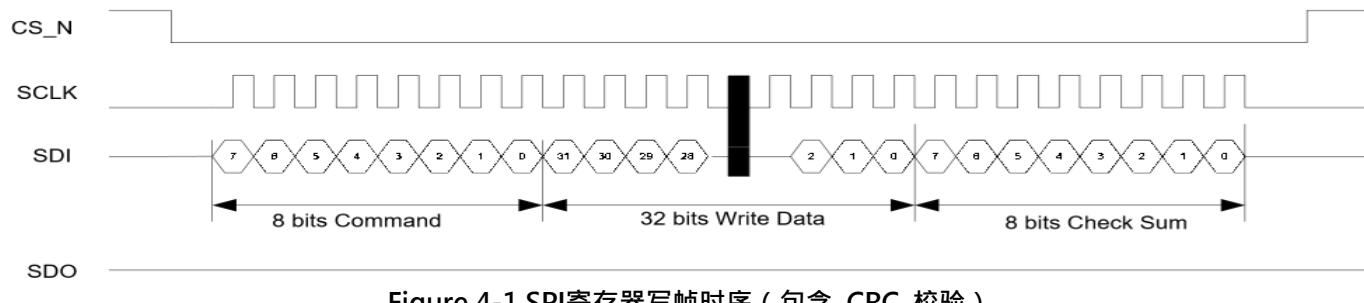

## 4.2 SPI CRC 校验

所有的 SPI 读写命令均包含 CRC 校验 ·CRC 校验帧是针对写入或是读出数据做保护 · 每个 32bits 数据都需要计算其 CRC8 的结果 · CRC8 是参考公式进行运算 :  $X8+X2+X+1$

CRC8 的运算公式可以参考下面的范例程序

```

Shift reg =data;

crc8 = 0x0;

for(i=0 ; i<32;i=i+1 ) {

If((crc8>>7 ) !=(shif reg>>31 ))

Crc8=((crc8<<1^0x07 ) &0xFF;

else

crc8=(crc8<<1 ) &0xFF;

Shif reg <<=1; }

```

举例来说 · 当数据为 0x87654321 的情况 · 其 CRC8 的结果是 0xD5

在每个 32bits 数据后面 · 都需要加上和校验帧 · 若和校验不符合 · 则该命令会被忽略或是该数据为无效数据

下图为单一寄存器写命令在包含和校验的时序

Figure 4-1 SPI寄存器写帧时序 (包含 CRC校验)

Figure 4-2 SPI寄存器写帧时序 (包含 CRC校验)

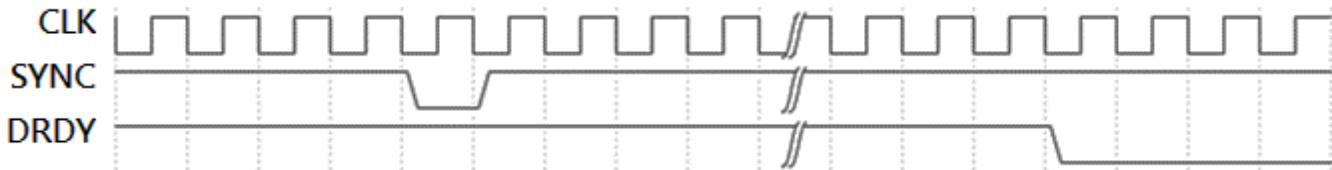

### 4.3.ADC转换输出格式

在开始 ADC 转换之前，需要先通过引脚控制或是 SPI 设置寄存器完成对 ADC 的设置，然后将 SYNC 拉低一个 CLK Cycle 后，设置才会更新进入 ADC 内。

Figure 4-3 SYNC更新时序

在 SYNC 拉低一个 Cycle 后，内部滤波器会重新开始计算，因为滤波器有稳定时间，因此从 SYNC 拉低至第一次数据开始输出，会有一段延时，在不同的 FILTYPEn 下会有不同的延时长度。

| FILTYPEn   | 延时时间    |

|------------|---------|

| 0 (宽带滤波器)  | 78个数据周期 |

| 1 (CIC滤波器) | 6个数据周期  |

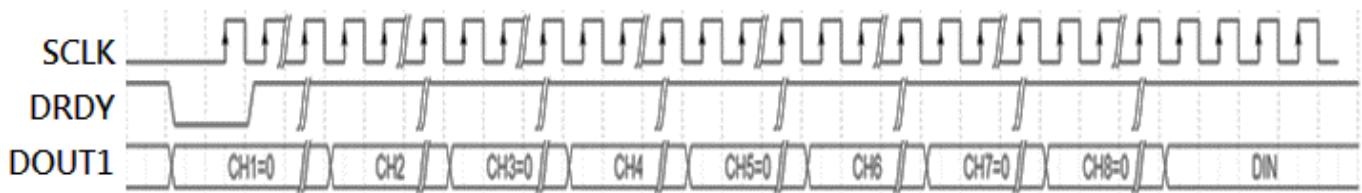

ADC转换输出五种格式，由FORMAT[2 : 0]来决定

| FORMAT[2 : 0] | 格式                                                         |

|---------------|------------------------------------------------------------|

| 0             | SPI 单信道动态模式，由DOUT1输出所有ADC数据，未使能的ADC通道不输出数据，支持daisy-chain串联 |

| 1             | SPI 单信道动态模式，由DOUT1输出所有ADC数据，未使能的ADC通道输出低电平，支持daisy-chain串联 |

| 2             | SPI 多信道模式，由DOUT1~DOUT8输出ADC1~ADC8通道数据                      |

| 3             | 同FORMAT=0                                                  |

| 4             | 同FORMAT=1                                                  |

| 5             | 同FORMAT=2                                                  |

| 6             | 主动多通道魔兽，由DOUT1~DOUT8输出ADC1~ADC8通道数据                        |

| 7             | 主动单通道魔兽，由DOUT1输出所有ADC数据，未使能的ADC通道不输出数据                     |

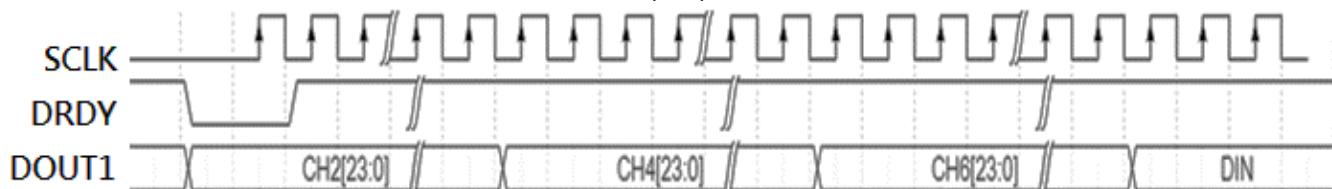

SPI 单信道动态模式如下图，仅会输出已使能的 ADC 数据，可串接多颗芯片，在 SCLK 足够快的情况下，在两次转换完成闲可以持续传送DIN数据，数据均由MAB(bit)开始传送。

Figure 4-4 SPI 单信道动态模式 (CRC\_EN=0, 使能ADC2/4/6)

当开启 CRC 校验后，每笔数据后都会加上 8 bits CRC 组合成 32 bits 数据，请注意，当芯片 daisy-chain 串接时，每颗芯片的CRC使能状态需要相同。

Figure 4-5 SPI 单信道动态模式 (CRC\_EN=1, 使能ADC2/4/6)

SPI 单信道固定模式如下图，所有 ADC 通道数据均会输出，未使能的ADC输出0，可串接多颗芯片，在 SCLK 足够快的情况下，在两次转换完成闲可以持续传送DIN数据。

Figure 4-6 SPI 单信道固定模式 ( CRC\_EN=0, 使能ADC2/4/6 )

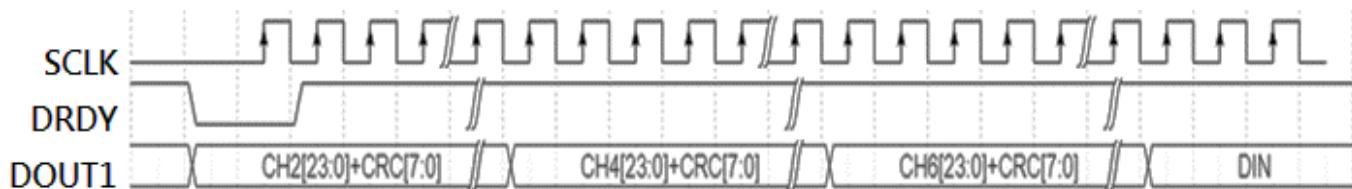

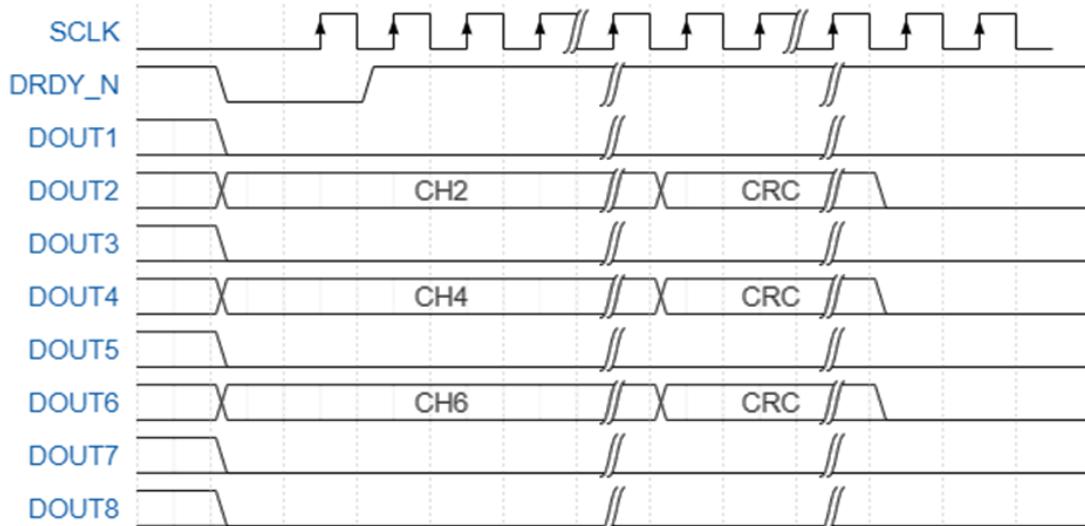

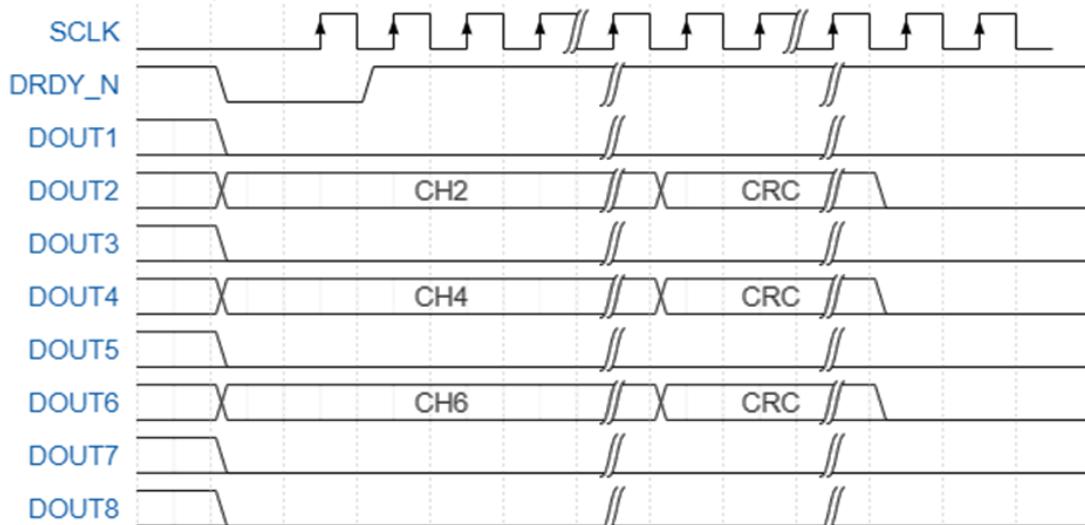

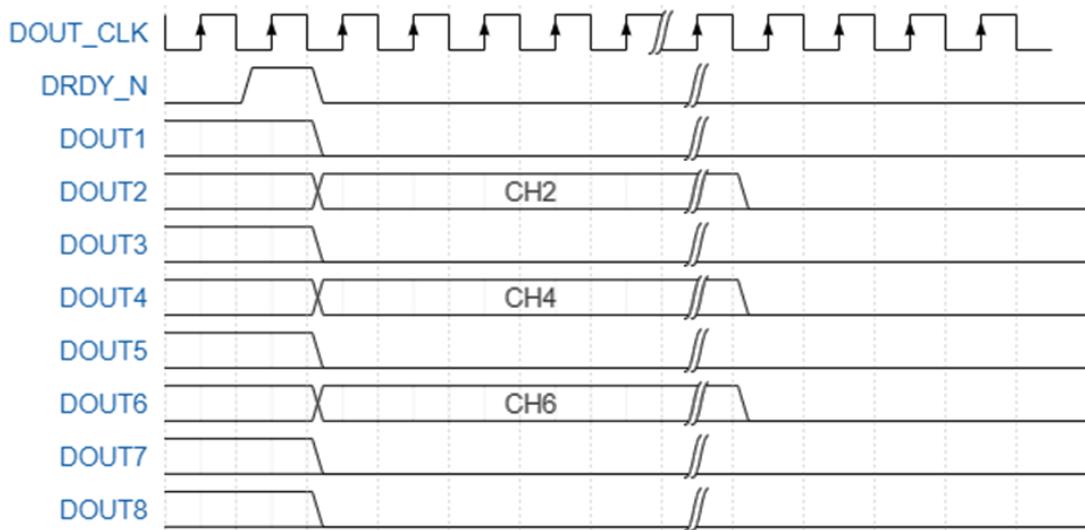

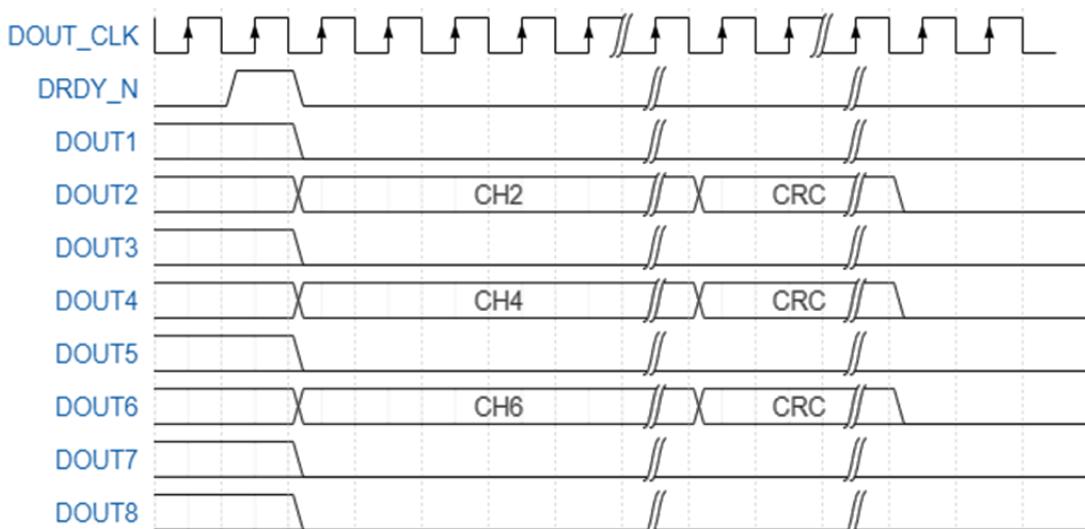

SPI多信道模式如下图，所有ADC输出均会输出，未使能的ADC输出0，不可daisy-chain串联芯片。

Figure 4-7 SPI 多信道模式 ( CRC\_EN=0, 使能ADC2/4/6 )

Figure 4-8 SPI 多信道模式 ( CRC\_EN=1, 使能ADC2/4/6 )

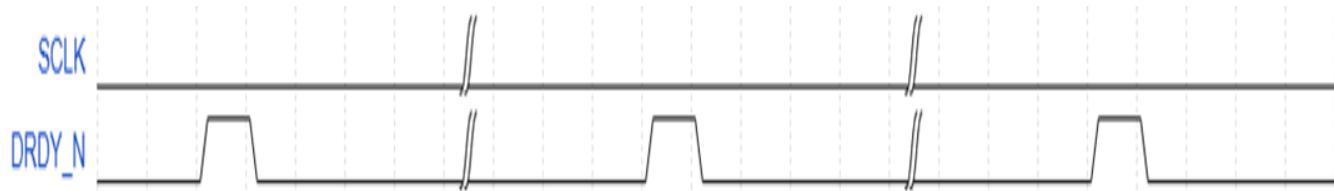

在SPI模式下，若SCLK持续为0，在下笔数据转换完成后DRDY仍会周期性拉高在拉低，拉高频率为转换率。

Figure 4-9 SPI 模式下SCLK为0状况

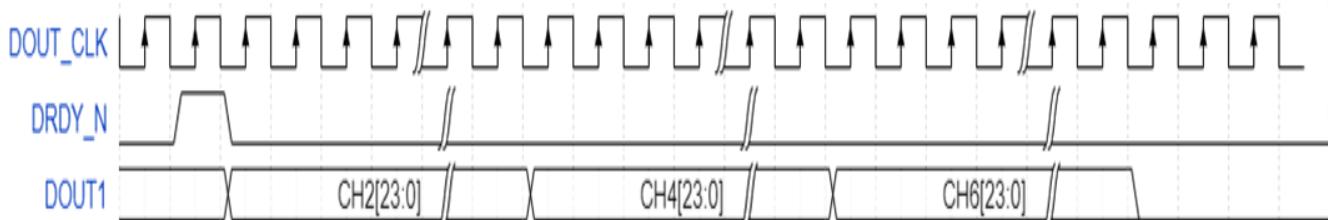

主动多信道模式如下图，此模式下芯片会输出 DOUT\_CLK，所有 ADC 数据输出与 DOUT\_CLK 同步，当 DRDY-拉高后下个时钟开始输出ADC数据的MSB，未使能的ADC输出0，不可daisy-chain串联芯片。

Figure 4-10 SPI 主动多信道模式 ( CRC\_EN=0 · 使能ADC2/4/6 )

Figure 4-11 SPI 主动多信道模式 ( CRC\_EN=1 · 使能ADC2/4/6 )

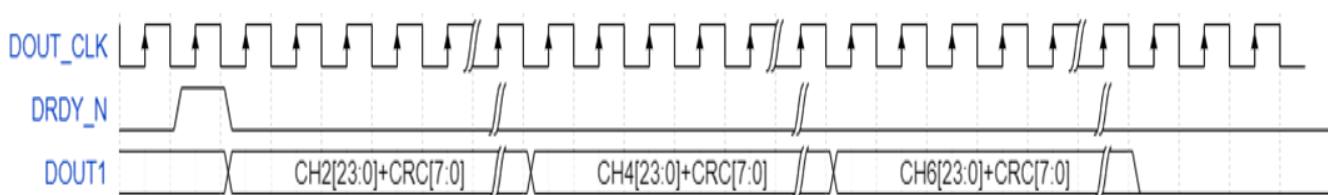

主动单信道动态模式如下图，仅会输出已使能的 ADC 数据，此模式下芯片会输出 DOUT\_CLK，所有 ADC 数据输出与 DOUT\_CLK 同步，当 DRDY 拉高后的下个时钟开始输出最前面 ADC 数据的 MSB，不可串接芯片，DOUT\_CLK 需过快需要的时钟，否则在下次转换完成后会造成数据丢失。

Figure 4-12 SPI 单信道模式 ( CRC\_EN=0 · 使能ADC2/4/6 )

Figure 4-13 SPI 单信道模式 ( CRC\_EN=1 · 使能ADC2/4/6 )

#### 4.4. SPI 接口复位

在四线模式下，也就是 SPI 片选(FORMAT2) 是存在的状况，只要片选被置 1，SPI 接口会回到接收指令状态，所以不需复位指令来做 SPI 接口复位。

在三线模式下，SPI 片选(FORMAT2) 永远接地，首先板子上需要确定 SCLK 不受干扰，建议在板子上对 SCLK 做 10Kohm 下拉，第一次上电完成后，原则上内部 POR 会将 SPI 接口复位，但是建议在 SDI 上打入 Byte0=0x00，Byte1=0xA5，Byte2=0xFF，Byte3=0x5A，连续 32 个时钟的信号强制 SPI 接口复位后再开始使用。0x00A5FF5A 指令可在任何时候生效。复位完成后等待 1us 后可以重新开始操作 SPI 指令。

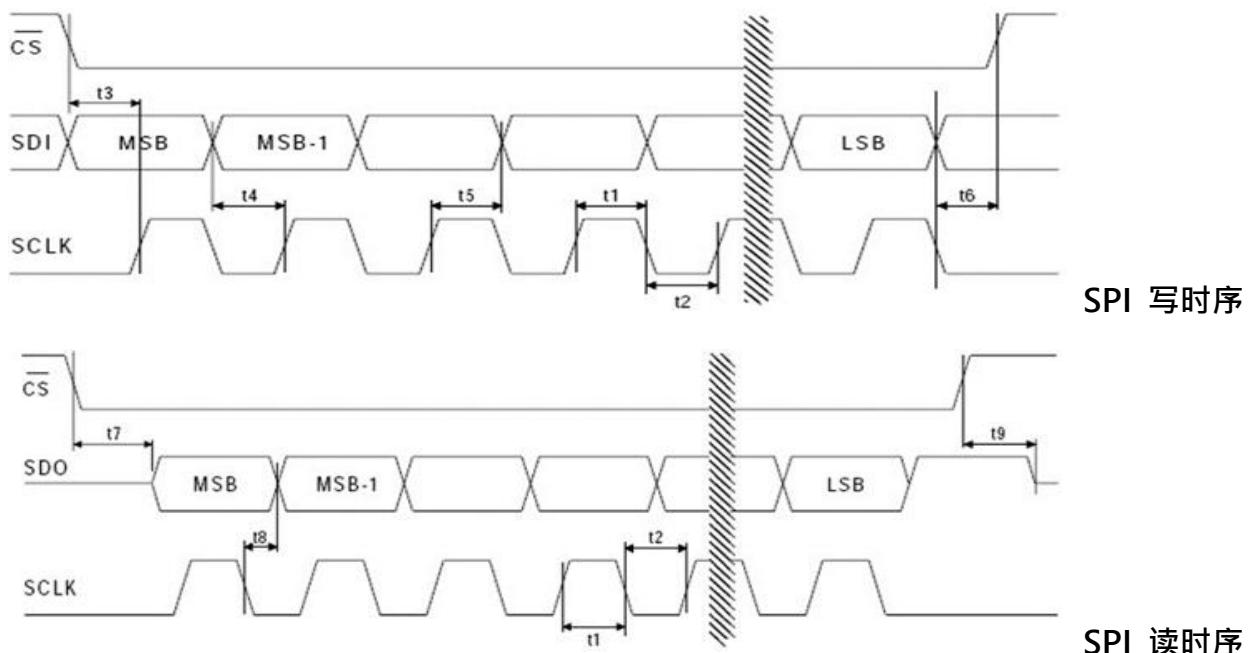

#### 4.5. SPI 接口时序

|                   | 标识    | 最小 | 典型 | 最大 | 单位  |

|-------------------|-------|----|----|----|-----|

| SPI时序             |       |    |    |    |     |

| SPI 时钟频率          | SCK   | 0  |    | 27 | MHz |

| SPI 时钟脉宽          | t1(高) | 17 |    |    | ns  |

|                   | t2(低) | 17 |    |    | ns  |

| SDI写时序            |       |    |    |    |     |

| CS片选到第一个时钟延时      | t3    | 17 |    |    | ns  |

| DATA领先时钟上升沿的建立时间  | t4    | 10 |    |    | ns  |

| DATA在时钟沿后的稳定时间    | t5    | 10 |    |    | ns  |

| 时钟下降沿后到CS上升的延时    | t6    | 17 |    |    | ns  |

| SDO读时序            |       |    |    |    |     |

| CS信号变低到有效数据       | t7    |    |    | 17 | ns  |

| SCK下降沿到新数据输出延时    | t8    |    |    | 10 | ns  |

| CS信号变高到SDO进高阻态的延时 | t9    |    |    | 10 | ns  |

SPI 写入数据的时候，SDI 的数据是在 SCK 的下降沿变化，以便在芯片写入寄存器的时候有足够的建立和保持时间。芯片内部电路在 SCK 上升沿去读取 SDI 数据，并填入相应的内部寄存器中。

SPI 读出数据的时候，CS 下降之后即通过 SDO 送出数据，由 MCU 产生 SCK 去读。SDO 的数据变化是在 SCK 下降沿之后变化。

## 5 寄存器描述

### 5.1 寄存器地址

CS5278内共有7个32 bits寄存器，可以通过读写帧的ADDR，来选择要读取或是写入的位置，下表列出各个寄存器对应的地址与初始值。

Table 5-1 寄存器地址表

| 地址   | 名称         | 类型  | 描述         | 初始值        |

|------|------------|-----|------------|------------|

| 0x00 | CONV_CONF0 | R/W | CONF0设置寄存器 | 0x00000000 |

| 0x01 | CONV_CONF1 | R/W | CONF1设置寄存器 | 0x00000000 |

| 0x02 | CONV_CONF2 | R/W | CONF2设置寄存器 | 0x00000000 |

| 0x03 | SYS_CONF0  | R/W | 系统设置寄存器0   | 0x00000000 |

| 0x04 | SYS_CONF1  | R/W | 系统设置寄存器1   | 0x00000000 |

| 0x0E | VERSION_ID | R   | 芯片版号寄存器    | 0x22012201 |

| 0x0F | 保留         | R/W | 保留         | 0x00000000 |

### 5.2 CONV\_CONF0 寄存器

此寄存器用来控制 SPI 模式下的转换参数

| D31     | D30     | D29        | D28     | D27     | D26       | D25        | D24     |

|---------|---------|------------|---------|---------|-----------|------------|---------|

| CH8_PDN | CH7_PDN | CH6_PDN    | CH5_PDN | CH4_PDN | CH3_PDN   | CH2_PDN    | CH1_PDN |

| D23     | D22     | D21        | D20     | D19     | D18       | D17        | D16     |

|         |         | SHARE_EN   | CRC_EN  |         | REFBUF_EN | SIGBUF_ENN | FILTYPE |

| D15     | D14     | D13        | D12     | D11     | D10       | D9         | D8      |

|         |         | DOUT_CKSEL |         |         | FORMAT    |            |         |

| D7      | D6      | D5         | D4      | D3      | D2        | D1         | D0      |

|         |         | CKSEL      |         |         | DR        |            |         |

Table 5-2CONV\_CONF0 定义

| 位置      | 名称         | 类型  | 描述                                                                                                                                                                       | Default |

|---------|------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 31 : 24 | CHx_PDN    | R/W | ADC通道始能控制，bit24对应ADC1，bit31对应ADC8<br>0：关闭 ADC 通道 x<br>1：使能 ADC 通道 x                                                                                                      | 0x00    |

| 23 : 22 |            |     | 保留                                                                                                                                                                       |         |

| 21      | SHARE_EN   | R/W | SPI SDO(FORMAT0) 与 DOUT1 共享选择<br>0：关闭 SPI SDO ( FORMAT0 ) 与 DOUT1 共享<br>1：开启 SPI SDO ( FORMAT0 ) 与 DOUT1 共享，在 SPI_MODE 下，若没有在进行 SPI 存取时，SPI SDO ( FORMAT0 ) 会输出 DOUT1 的值 | 0x0     |

| 20      | CRC_EN     | R/W | CRC校验控制，此控制位控制SPI输出与主动输出模式下的CRC校验码输出<br>0：关闭CRC校验输出<br>1：使能CRC校验码输出，每个24bits ADC数据输出后会带8bits CRC校验码                                                                      | 0x0     |

| 19      |            |     | 保留                                                                                                                                                                       |         |

| 18      | REFBUF_EN  | R/W | REF Buffer控制<br>0：关闭<br>1：开启                                                                                                                                             | 0x0     |

| 17      | SIGBUF_ENN | R/W | 输入信号BUFFER使能<br>0：打开<br>1：关闭                                                                                                                                             | 0x0     |

| 位置      | 名称         | 类型  | 描述                                                                                                                                                                                                                                                                                                                                                                                                             | Default |

|---------|------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 16      | FILTYPE    | R/W | 滤波器模式选择<br>0：宽带滤波器<br>1：CIC滤波器                                                                                                                                                                                                                                                                                                                                                                                 | 0x0     |

| 15 : 14 |            |     | 保留                                                                                                                                                                                                                                                                                                                                                                                                             |         |

| 13 : 12 | DOUT_CKSEL | R/W | 主动数据输出模式时钟频率选择，仅在FORMAT选择主动输出模式时有输出<br>0 : ADC时钟*2<br>1 : ADC时钟*1<br>2 : ADC时钟/2<br>3 : ADC时钟/4                                                                                                                                                                                                                                                                                                                | 0x0     |

| 11      |            |     | 保留                                                                                                                                                                                                                                                                                                                                                                                                             |         |

| 10 : 8  | FORMAT     | R/W | 输出数据格式选择<br>0 : SPI 单路输出动态模式<br>1 : SPI 单路输出固定模式<br>2 : SPI 平行输出模式<br>3 : SPI 单路输出动态模式 ( 同模式0 )<br>4 : SPI 单路输出固定模式 ( 同模式1 )<br>5 : SPI 平行输出模式 ( 同模式2 )<br>6 : 主动输出平行模式<br>7 : 主动输出单路动态模式                                                                                                                                                                                                                      | 0x0     |

| 7 : 6   |            |     | 保留                                                                                                                                                                                                                                                                                                                                                                                                             |         |

| 5 : 4   | CKSEL      | R/W | ADC工作时钟频率选择，不同的ADC工作时钟频率对应不同的ADC低功耗水平。<br>0 : 对应快速模式，ADC时钟8.192MHz<br>1 : 对应中速模式，ADC时钟4.096MHz<br>2 : 对应经济模式，ADC时钟1.024MHz<br>3 : 对应经济模式，ADC时钟1.024MHz                                                                                                                                                                                                                                                         | 0x0     |

| 3       |            |     | 保留                                                                                                                                                                                                                                                                                                                                                                                                             | 0x0     |

| 2 : 0   | DR         | R/W | 降采样率设置，ADC输出的数据率等于ADC工作频率除以降采样率。两种寄存器组合起来，可以设置不同的ADC数据率。如果ADC时钟8.192MHz，降采样率64，对应128KHz的数据率。ADC时钟4.096MHz，降采样率32，也是对应128KHz的数据率。前者ADC时钟频率高，因此ADC功耗更高，但精度也跟高。如选定数据率之后，可从功耗和精度角度进行选择，想要精度更高，则选更高的ADC工作时钟，更高的降采样率。如需功耗更低，则反之。<br>0 : 32(ADC 8.192MHz时对应256KHz)<br>1 : 64(ADC 8.192MHz时对应128KHz)<br>2 : 128(ADC 8.192MHz时对应64KHz)<br>3 : 256(ADC 8.192MHz时对应32KHz)<br>4 : 512(ADC 8.192MHz时对应16KHz)<br>5~7 : 1/512 | 0x0     |

### 5.3 CONV\_CONF1 寄存器

CONV\_CONF1 用来设置ADC1~ADC4输入信号的相位延时，目的是用于校正因外滤波等因素导致的8个ADC的信号延时差异，可延时的最大范围是DR-2，其中DR是设置的降采样率。寄存器的数值表示延时的ADC工作时钟数。如ADC工作时钟为8.192M，则1个延时等于122.07ns。

即使设置了不同的相位延时，所有ADC最后仍会在同一个时间输出数据。

|               |     |     |     |     |     |     |     |

|---------------|-----|-----|-----|-----|-----|-----|-----|

| D31           | D30 | D29 | D28 | D27 | D26 | D25 | D24 |

| ADC4_SYNC_DLY |     |     |     |     |     |     |     |

| D23           | D22 | D21 | D20 | D19 | D18 | D17 | D16 |

| ADC3_SYNC_DLY |     |     |     |     |     |     |     |

| D15           | D14 | D13 | D12 | D11 | D10 | D9  | D8  |

| ADC2_SYNC_DLY |     |     |     |     |     |     |     |

| D7            | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| ADC1_SYNC_DLY |     |     |     |     |     |     |     |

Table 5-3 CONV\_CONF1 定义

| 位置      | 名称            | 类型  | 描述                                                                                                                                     | Default |

|---------|---------------|-----|----------------------------------------------------------------------------------------------------------------------------------------|---------|

| 31 : 24 | ADC4_SYNC_DLY | R/W | ADC4同步延时，延时的ADC时钟个数与降采样率DR有关。<br>DR=0 : 只允许设置0~30<br>DR=1 : 只允许设置0~64<br>DR=2 : 只允许设置0~126<br>DR=3 : 只允许设置0~254<br>DR=4~7 : 只允许设置0~254 | 0x00    |

| 23 : 16 | ADC3_SYNC_DLY | R/W | ADC3 同步延时                                                                                                                              | 0x00    |

| 15 : 8  | ADC2_SYNC_DLY | R/W | ADC2 同步延时                                                                                                                              | 0x00    |

| 7 : 0   | ADC1_SYNC_DLY | R/W | ADC1 同步延时                                                                                                                              | 0x00    |

### 5.4 CONV\_CONF2 寄存器

CONV\_CONF2 是用来控制 ADC5~ADC8 输入信号的相位延时，说明同上。

|               |     |     |     |     |     |     |     |

|---------------|-----|-----|-----|-----|-----|-----|-----|

| D31           | D30 | D29 | D28 | D27 | D26 | D25 | D24 |

| ADC8_SYNC_DLY |     |     |     |     |     |     |     |

| D23           | D22 | D21 | D20 | D19 | D18 | D17 | D16 |

| ADC7_SYNC_DLY |     |     |     |     |     |     |     |

| D15           | D14 | D13 | D12 | D11 | D10 | D9  | D8  |

| ADC6_SYNC_DLY |     |     |     |     |     |     |     |

| D7            | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| ADC5_SYNC_DLY |     |     |     |     |     |     |     |

Table 5-4 CONV\_CONF1 定义

| 位置      | 名称            | 类型  | 描述        | 初始值  |

|---------|---------------|-----|-----------|------|

| 31 : 24 | ADC8_SYNC_DLY | R/W | ADC8 同步延时 | 0x00 |

| 23 : 16 | ADC7_SYNC_DLY | R/W | ADC7 同步延时 | 0x00 |

| 15 : 8  | ADC6_SYNC_DLY | R/W | ADC6 同步延时 | 0x00 |

| 7 : 0   | ADC5_SYNC_DLY | R/W | ADC5 同步延时 | 0x00 |

## 5.5 SYS\_CONF0 寄存器

### 5.5.1 SYS\_CONF0

| D31       | D30      | D29      | D28      | D27      | D26      | D25      | D24      |

|-----------|----------|----------|----------|----------|----------|----------|----------|

| GPIO_DATA |          |          |          | GPIO_EN  |          |          |          |

| D23       | D22      | D21      | D20      | D19      | D18      | D17      | D16      |

| Reserved  | Reserved | Reserved | Reserved | Reserved | Reserved | Reserved | Reserved |

| D15       | D14      | D13      | D12      | D11      | D10      | D9       | D8       |

| Reserved  | Reserved | Reserved | Reserved | Reserved | Reserved | Reserved | Reserved |

| D7        | D6       | D5       | D4       | D3       | D2       | D1       | D0       |

| SHORT     | Reserved |

Table 5-5.2 SYS\_CONF0 定义

| 位置      | 名称        | 类型  | 描述                                                                                                                                  | Default |

|---------|-----------|-----|-------------------------------------------------------------------------------------------------------------------------------------|---------|

| 31 : 28 | GPIO_DATA | R/W | GPIOx 输出电平选择 Bit28 对应 GPIO(PWDN5_N) · Bit31 对应 GPIO3(PWDN8_N) 此寄存器在 GPIO_EN 为 1 时生效<br>0 : 输出低电平<br>1 : 输出高电平                       | 0x0     |

| 27 : 24 | GPIO_EN   | R/W | GPIO 使能控制 · Bit24 对应 GPIO0 ( PWDN5_N ) · Bit27 对应 GPIO3(PWDN8_N )<br>0 : 关闭 GPIO 功能<br>1 : 使能 GPIO 功能 ( 输出模式 · 输出电平由 GPIO_DATA 控制 ) | 0x0     |

| 23 : 8  | Reserved  | R/W | 保留位 · 必须保持默认 0                                                                                                                      | 0x0     |

| 7       | SHORT     | R/W | ADC 内部短路使能<br>1 : 使能内部短路                                                                                                            | 0x0     |

| 24      | Reserved  | R/W | 保留位 · 必须保持默认0                                                                                                                       | 0x0     |

## 5.6 SYS\_CONF1 寄存器

SYS\_CONF1 寄存器为 SPI 寄存器 CRC 保证寄存器 · 当主控设置完 CONV\_CONF0 与 SYS\_CONF0 后 · 需计算 CRC 校验码写入此寄存器 · 硬件会自动检验是否符合预期 · 若不符合预期 · ADC 输出数据会强制为低电平。

| D31  | D30 | D29 | D28 | D27 | D26 | D25 | D24 |

|------|-----|-----|-----|-----|-----|-----|-----|

|      |     |     |     |     |     |     |     |

| D23  | D22 | D21 | D20 | D19 | D18 | D17 | D16 |

|      |     |     |     |     |     |     |     |

| D15  | D14 | D13 | D12 | D11 | D10 | D9  | D8  |

|      |     |     |     |     |     |     |     |

| D7   | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

| CRC8 |     |     |     |     |     |     |     |

Table 5-6 SYS\_CONF1 定义

| 位置     | 名称   | 类型  | 描述                                                                                   | Default |

|--------|------|-----|--------------------------------------------------------------------------------------|---------|

| 31 : 8 |      |     |                                                                                      |         |

| 7 : 0  | CRC8 | R/W | 主控端计算的 CRC 校验码由 ( CONV_CONF0 · CONV_CONF1 · CONV_CONF2 · SYS_CONF0 ) 总共 128bits 计算出来 | 0x0     |

CRC是参考下面的公式进行运算 :

$X8+X2+X+1$

可以参考SPI读写命令帧的计算方式 · 不同点在与输入数据为128bits · 由CONV\_CONF0[31]开始输入 · 最后一个bit为SYS\_CONF0[0]

## 5.7 VERSION\_ID 寄存器

VERSION\_ID寄存器是用来显示芯片版号

Table 5-7 VERSION\_ID 定义

| 位置     | 名称         | 类型 | 描述   | Default    |

|--------|------------|----|------|------------|

| 31 : 0 | VERSION_ID | R  | 芯片版号 | 0x22012201 |

## 6. 濾波器特性

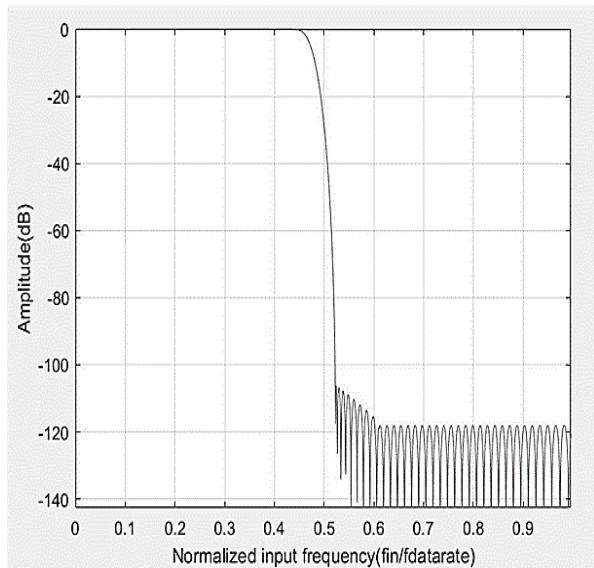

芯片内置两种濾波器，宽带濾波器和 CIC 濾波器。宽带濾波器提供通带范围内优良的增益平坦度，但功耗相比 CIC 濾波器高，且延时较长。如对阶跃响应要求高，但信号频率较低（或对信号增益平坦度要求不高）的应用，可使用CIC濾波器

### 6.1 宽带濾波器

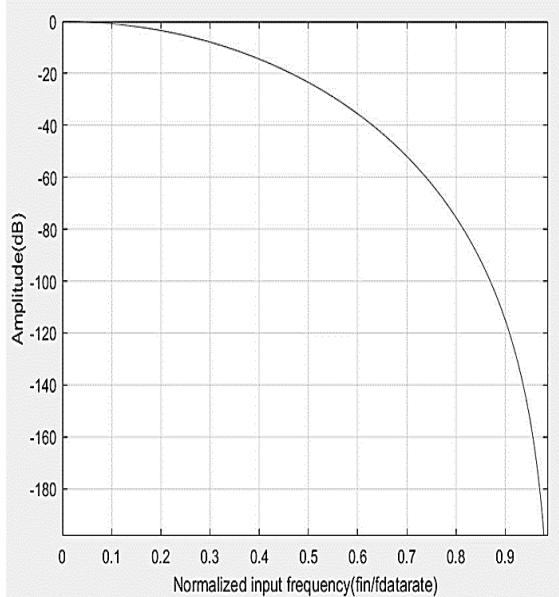

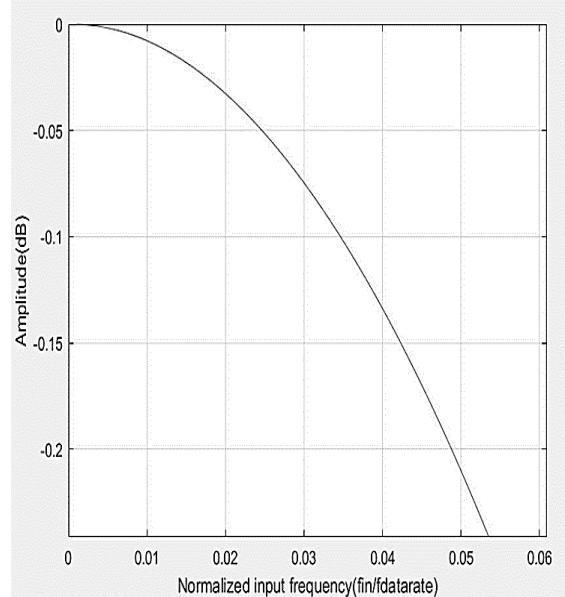

宽带濾波器的幅频曲线如图 6.1 · 6.2 所示，图 6.2 为通带部分的放大图。0.003dB 纹波的通带范围是  $0.43 \times f_{data rate}$ 。

Figure 6-1 宽带濾波器幅频曲线

Figure 6-2 宽带濾波器幅频曲线

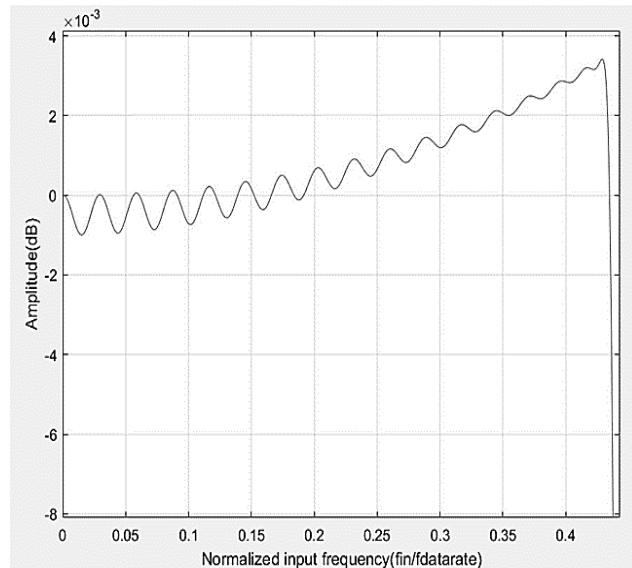

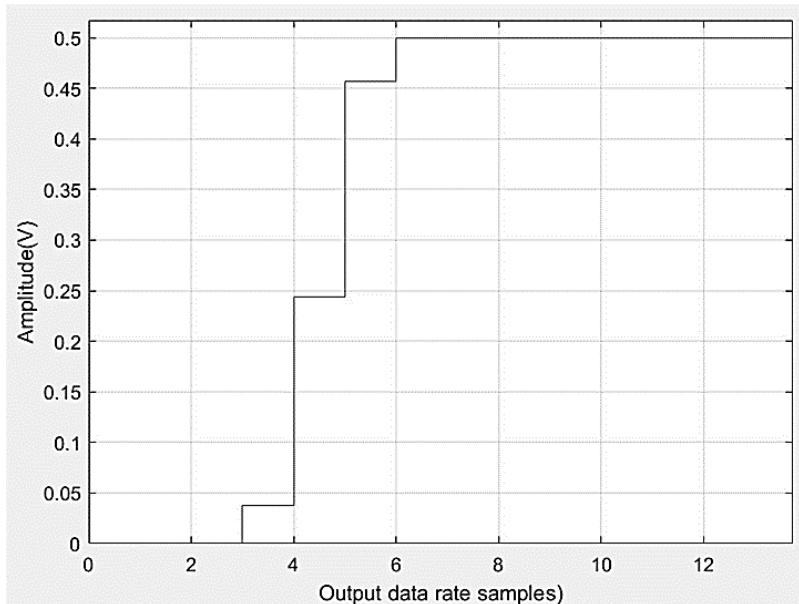

宽带濾波器的阶跃响应曲线如图 6.3 所示，群延时为 38 个数据点，完全精度的建立时间是 76 个数据点。

Figure 6-3 宽带濾波器阶段响应

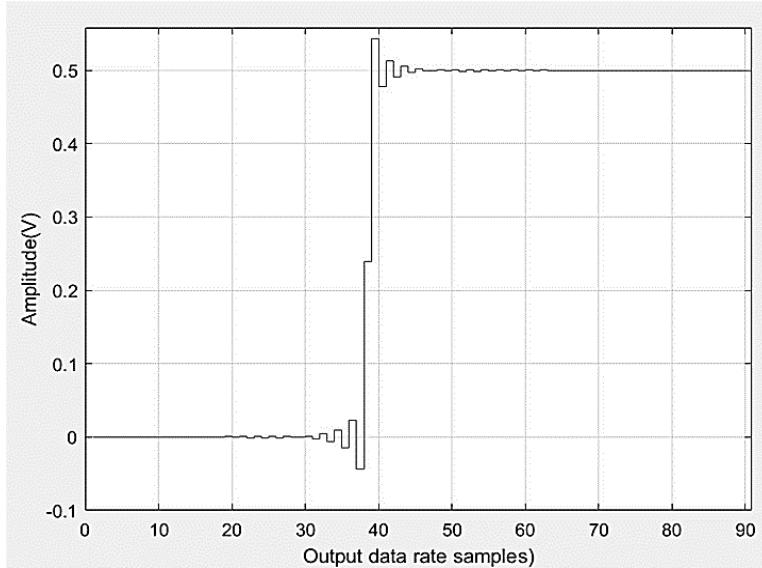

## 6.2 CIC 濾波器

CIC 濾波器的幅频曲线如图 6.4 6.5 所示，图 6.5 为通带部分的放大图。 $\sim 3\text{dB}$  的频率带宽是  $0.17 * f_{\text{data rate}}$ ， $0.1\text{dB}$  的频率带宽是  $0.034 * f_{\text{data rate}}$ 。

Figure 6-4 CRC 濾波器幅频曲线

Figure 6-5 CRC 濾波器幅频曲线

CIC 濾波器的阶跃响应曲线如图 6.6 所示，完全精度的建立时间是 6 个数据点。

Figure 6-6 CRC 濾波器阶段响应

## 7 .ADC 测试图表

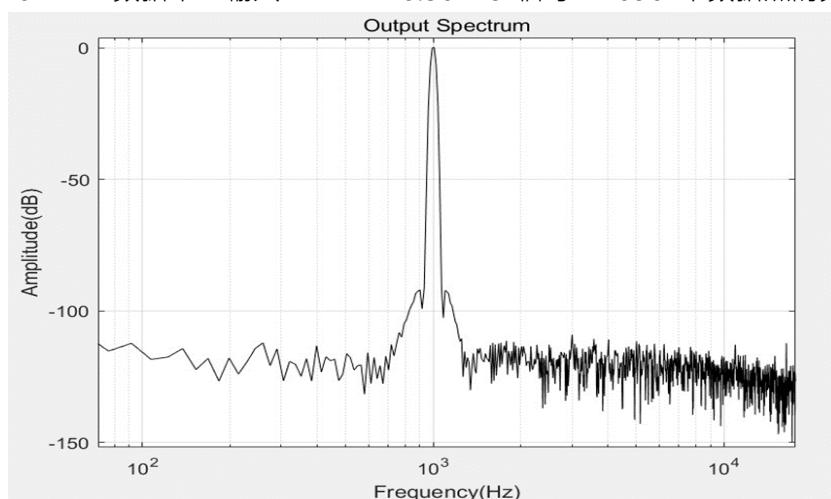

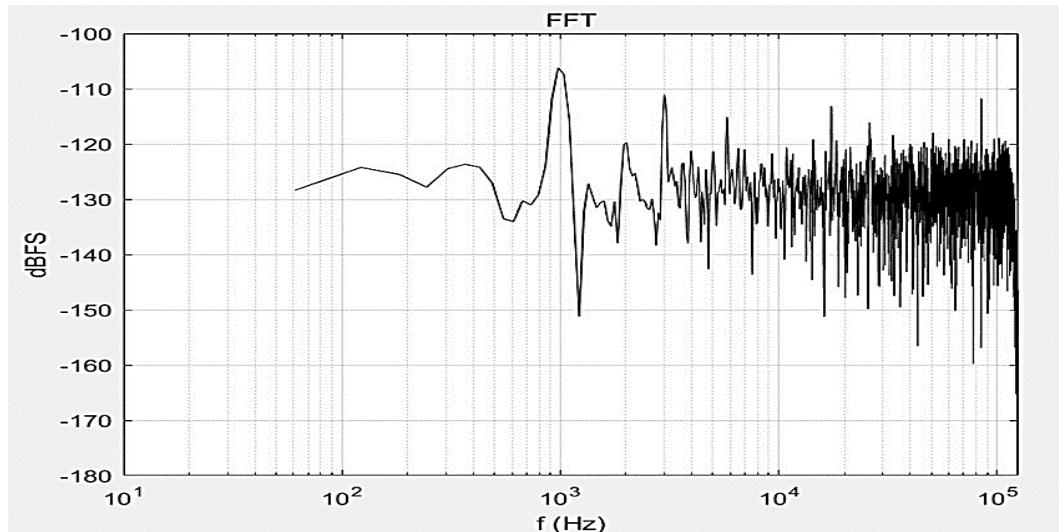

### 7.1 快速模式下的信号频谱和噪声分布

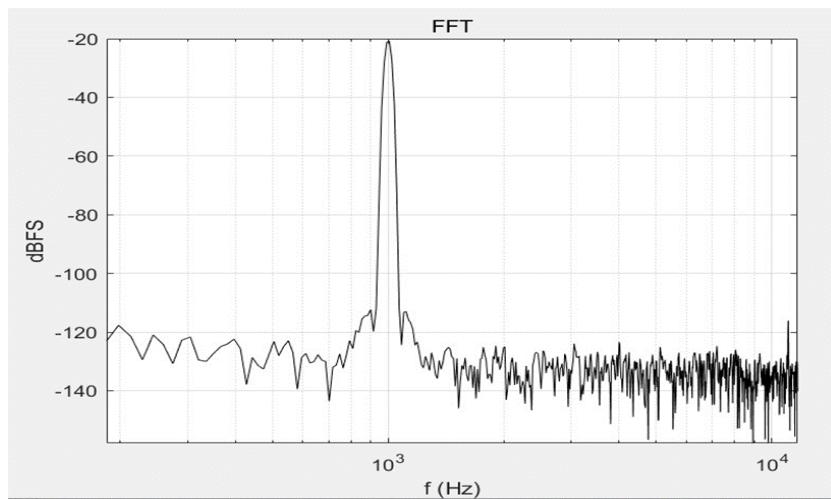

测试条件 : AVDD=DVDD=5V · IOVDD=3.3V · DVDD-1.8V · REFP=2.5V

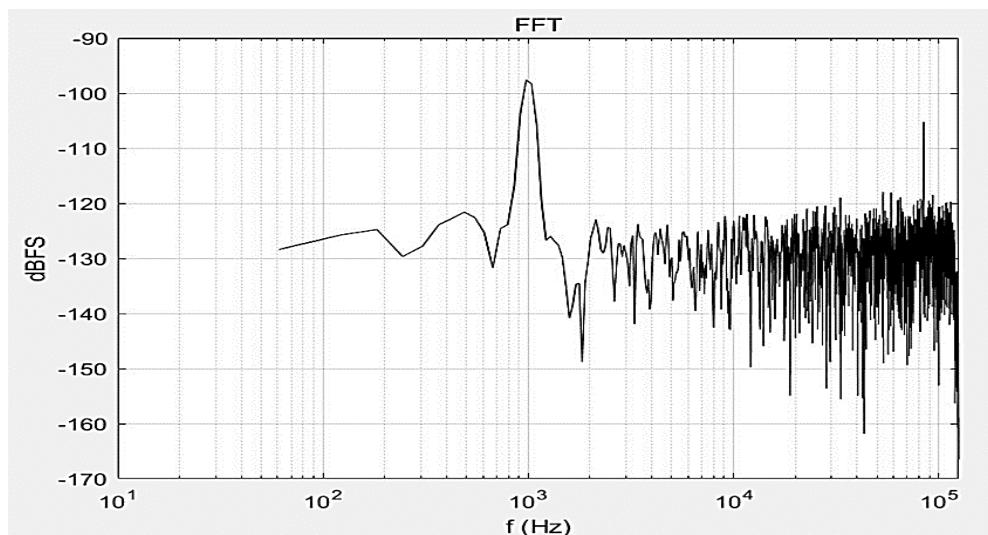

下图为 64kHz 数据率 , 输入 1kHz 、 -0.5dBFS 信号 , 4096 个数据点的频谱图。

下图为 64kHz 数据率 , 输入 1kHz 、 -20dBFS 信号 , 4096 个数据点的频谱图。

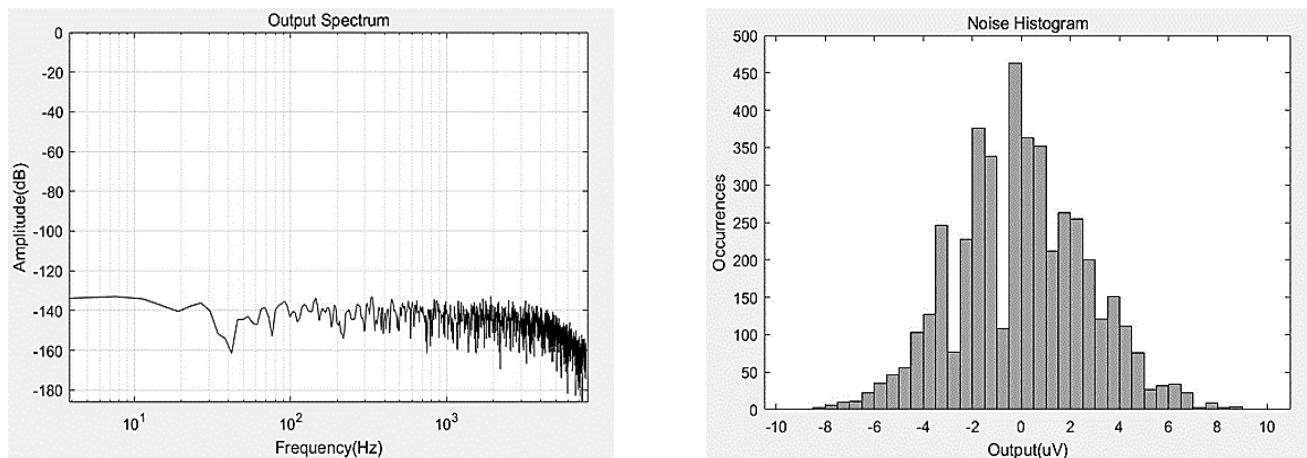

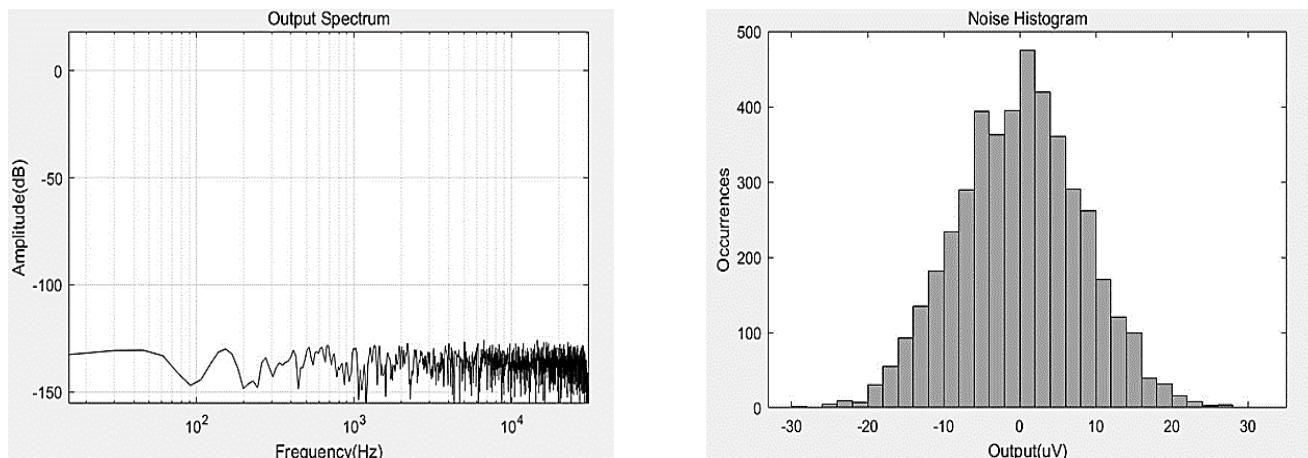

下图为 16KHz 数据率 , CIC 滤波器 , 输入短路 , 4096 个数据点的频谱图和噪声分布图。

下图为64KHz数据率，CIC滤波器，输入短路，4096个数据点的频谱图和噪声分布图。

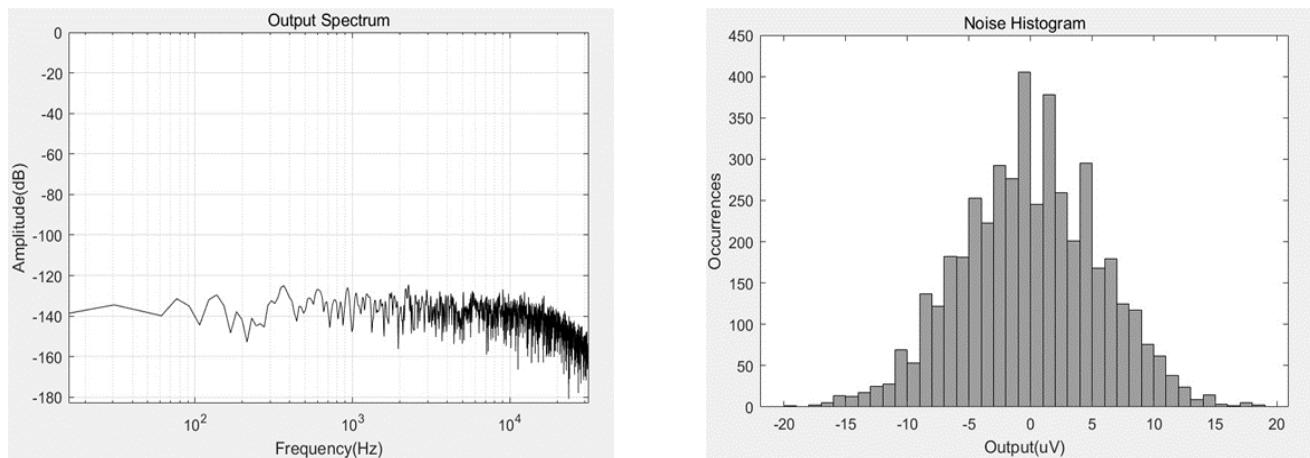

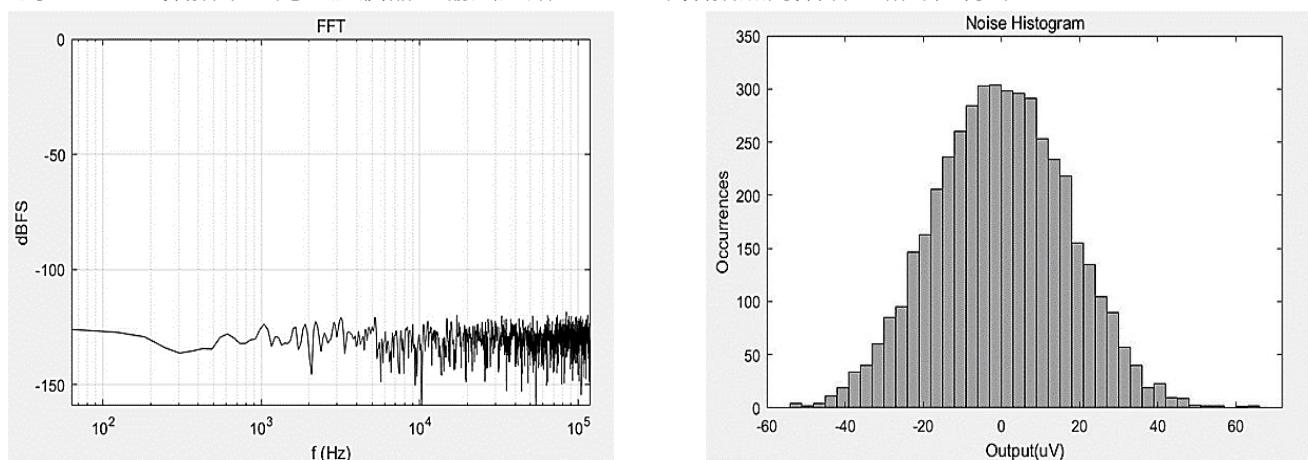

下图为256KHz数据率，CIC滤波器，输入短路，4096个数据点的频谱图和噪声分布图。

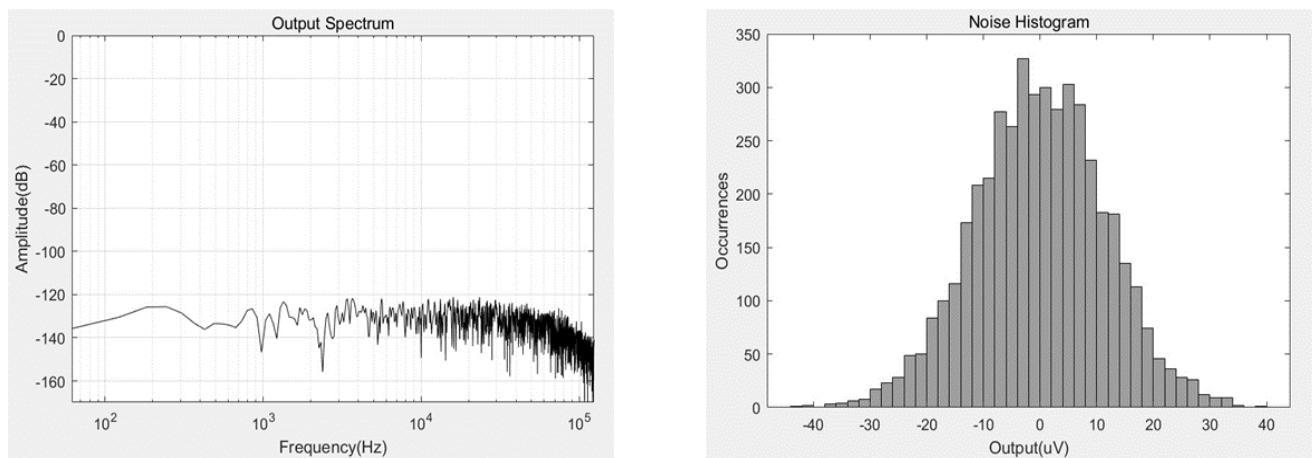

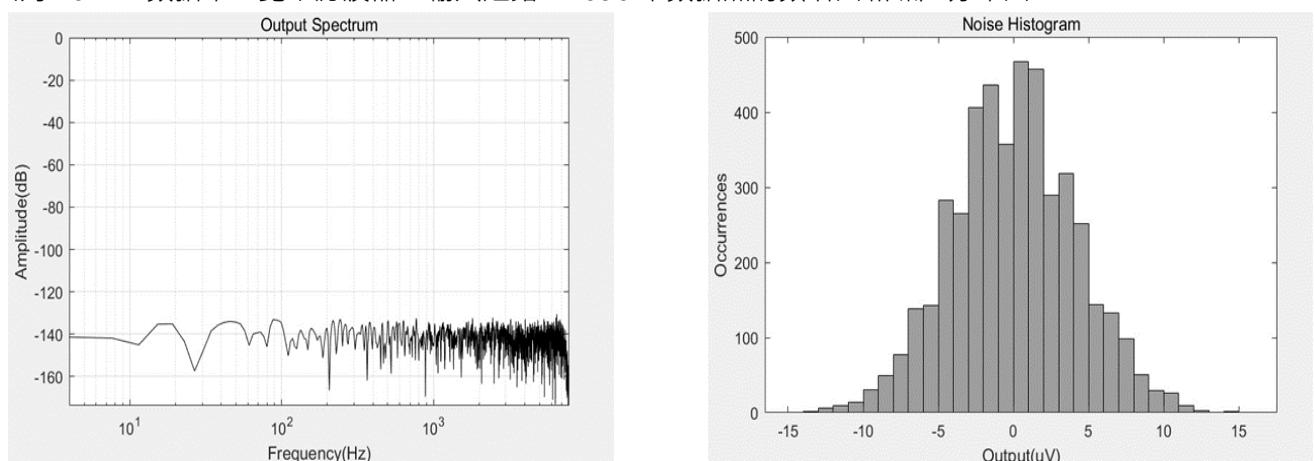

下图为 16KHz 数据率，宽带滤波器，输入短路，4096 个数据点的频谱图和噪声分布图。

下图为 64KHz 数据率 · 宽带滤波器 · 输入短路 · 4096 个数据点的频谱图和噪声分布图。

下图为 256KHz 数据率 · 宽带滤波器 · 输入短路 · 4096 个数据点的频谱图和噪声分布图。

## 7.2 增益和 offset 的温漂

增益温漂测试条件 : 在输入信号上迭加 1V 峰峰值、1KHz 的正弦信号 · AVDD=5V · IOVDD=3.3V · DVDD-1.8V · REFP=2.5V · 采样率 256KHz.4096 个数据点的频谱如下图所示。

### 7.3 共模抑制比 ( CMRR )

测试条件 :在输入信号上迭加 1V 峰峰值 ·1KHz 的正弦信号 AVDD=5V ·IOVDD=3.3V ·DVDD=1.8V ·REFP=2.5V ·采样率 256KHz.4096 个数据点的频谱如下图所示。

## 8 参考应用电路

## 9. PACKAGING 封装

## 10. 参考 DEMO 程序