# 82750LA Technical Specifications

September 1992

Order Number: 241346-001

# 82750LA (KAGA) Keying and Audio Gate Array

| <b>CONTENTS</b> PA                                   | GE   | CONTENTS                                                   | PAGE    |

|------------------------------------------------------|------|------------------------------------------------------------|---------|

| 1.0 PIN DESCRIPTION1-                                | 249  | 3.0 HARDWARE INTERFACE                                     | . 1-266 |

| 1.1 Pinout                                           | 249  | 3.1 DVI Bus Register Access                                | . 1-266 |

| 1.2 Pin Descriptions 1-                              | 253  | 3.2 Audio                                                  |         |

| 1.2.1 KAGA Audio and DVI Bus<br>Signal Definitions1- | 253  | 3.2.1 ADSP Bus Register Access                             | . 1-267 |

| 1.2.2 KAGA Keying/Genlock Signal Definitions1-       | 256  | 3.2.2 Reset and Boot Load 3.2.3 Program Load               |         |

| 2.0 INTERNAL ARCHITECTURE 1-                         | 258  | 3.2.4 VRAM DMA Transfers                                   |         |

| 2.1 Audio1-                                          |      | 3.2.5 Audio Data Capture                                   | . 1-270 |

| 2.1.1 Overview 1-                                    |      | 3.2.6 Audio Data Playback                                  | . 1-270 |

| 2.1.2 Register Configuration 1-                      |      | 3.3 Keying and Genlock                                     | . 1-271 |

| 2.1.3 DMA Registers 1-                               |      | 3.3.1 Video Sync Selection                                 |         |

| 2.1.4 Boot Register 1-                               |      | 3.3.2 Display Processor                                    |         |

| 2.1.5 Message Registers 1-                           | 260  | Synchronization                                            | . 1-271 |

| 2.1.6 Playback and Capture Registers1-               | -260 | 3.3.3 Synchronizing the Display Processor                  | . 1-272 |

| 2.1.7 Command and Status Registers                   |      | 3.3.4 PB and DB Clock Selection                            |         |

| 2.2 Keying and Genlock 1-                            |      | 3.3.5 Video Keying                                         | . 1-272 |

| 2.2.1 Overview 1-                                    |      | 4.0 PROGRAMMING INFORMATION .                              | . 1-273 |

| 2.2.2 Video Sync Muxes 1-                            | -261 | 4.1 Audio                                                  | . 1-273 |

| 2.2.3 Display Processor Vertical Reset Mux1-         | -263 | 4.1.1 Audio Command and Status Register (ACS)              | . 1-273 |

| 2.2.4 Phaselock Loop Components 1-                   | -263 | 4.1.2 Message to DVI Register (MDVI)                       |         |

| 2.2.5 PB and DB Clock Muxes 1-                       | -265 | 4.1.3 Message to DSP Register                              |         |

| 2.2.6 Keying Logic 1-                                | -265 | (MDSP)                                                     |         |

| 2.2.7 Register Configuration 1-                      | -265 | 4.1.4 Sample Rate Command and Status Register (SRCS)       | 1-275   |

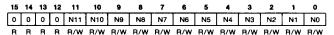

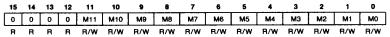

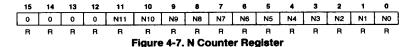

| 2.2.8 Modulus and Counter Registers1-                | -266 | 4.1.5 VRAM Data Registers<br>(VRDAT0,VRDAT1)               |         |

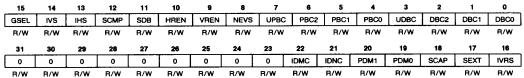

| 2.2.9 Genlock Command and Status Register1-          | -266 | 4.1.6 Capture/Playback Audio<br>Registers (CPAR,CPAL)      |         |

| 2.2.10 Chroma Keying Value Register1-                | -266 | 4.1.7 VRAM Write Address Registers (WVRADD0,               | . 1-2/0 |

| 2.2.11 Keying Mode Select                            |      | WVRADD1)                                                   | . 1-275 |

| Register1-                                           | -266 | 4.1.8 VRAM Read Address<br>Registers (RVRADD0,<br>RVRADD1) | . 1-276 |

| CONTENTS                                            | PAGE  | CONTENTS                                                                | PAGE  |

|-----------------------------------------------------|-------|-------------------------------------------------------------------------|-------|

| 4.1.9 DVI Command and Status Register (DCS)         | -     | 4.2.7 Keying Mode Select (KMSEL)                                        |       |

| 4.2 Keying and Genlock 4.2.1 N Modulus Register     | 1-277 | 4.2.8 Common System Configurations                                      | 1-282 |

| (NMOD)                                              |       | 5.0 ELECTRICAL SPECIFICAT 5.1 DC Characteristics 5.2 AC Characteristics | 1-284 |

| (NCTR) 4.2.4 M Counter Register (MCTR)              |       | 6.0 PACKAGE THERMAL SPECIFICATIONS                                      | 1-294 |

| 4.2.5 Genlock Command and<br>Status Register (GCSR) | 1-278 |                                                                         |       |

| 4.2.6 Chroma Keying Value<br>Register (CKVAL)       | 1-281 |                                                                         |       |

#### INTRODUCTION

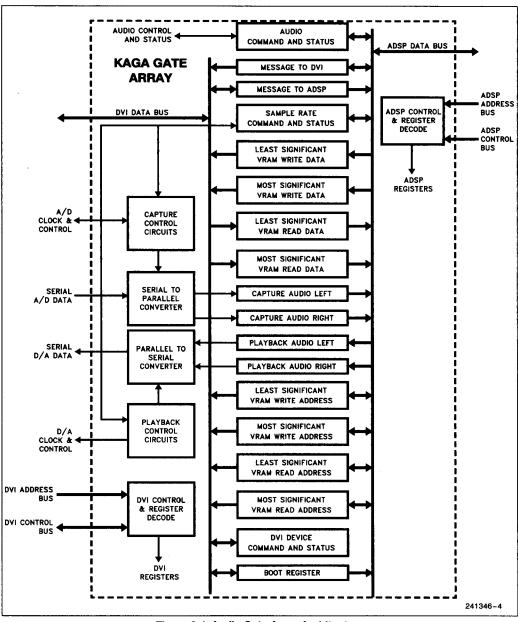

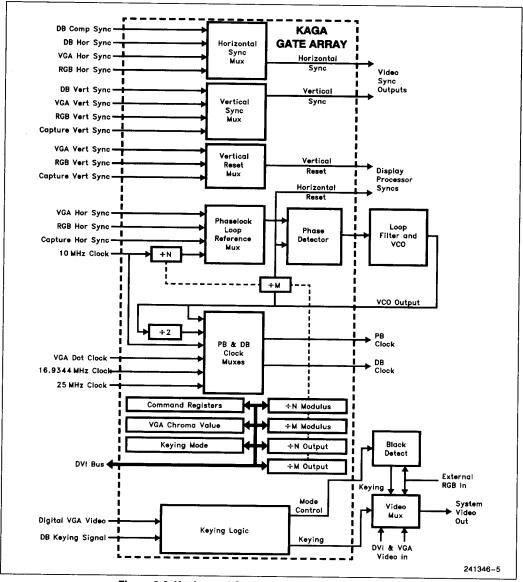

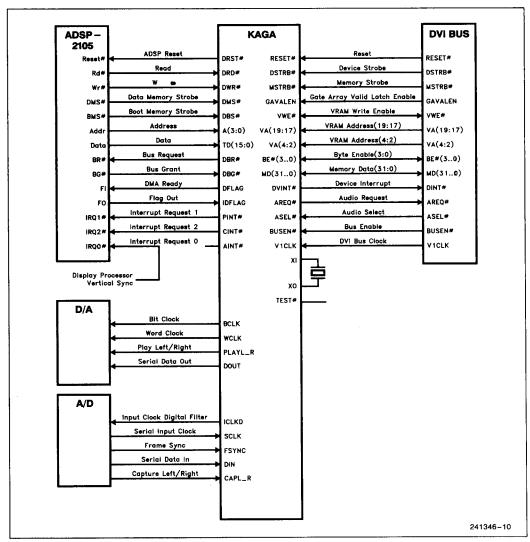

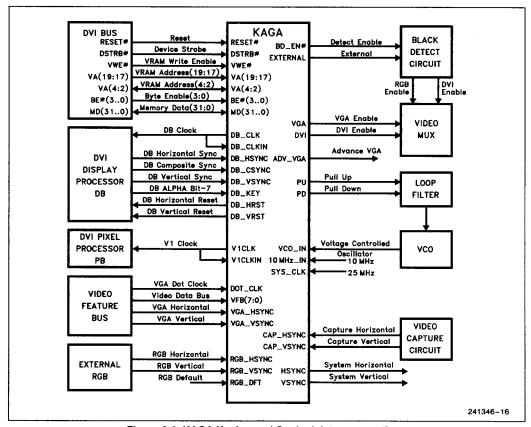

The Keying and Audio Gate Array (KAGA) serves three functions: (1) It is the interface between the Audio Digital Signal Processor (ADSP) and both the DVI Bus and the analog conversion components; (2) it generates keying signals to allow various video sources to be combined; (3) it contains portions of the phaselock loop which both provides video genlock capability and generates clock signals for the entire DVI System.

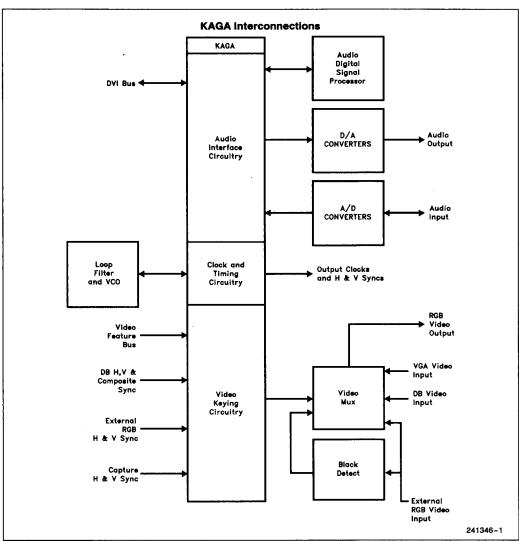

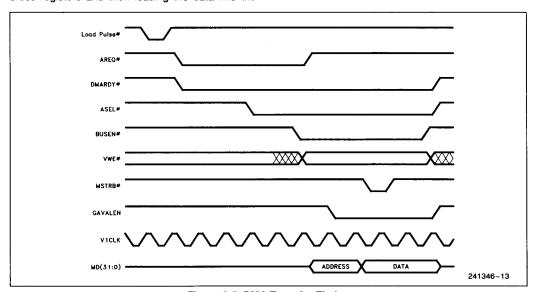

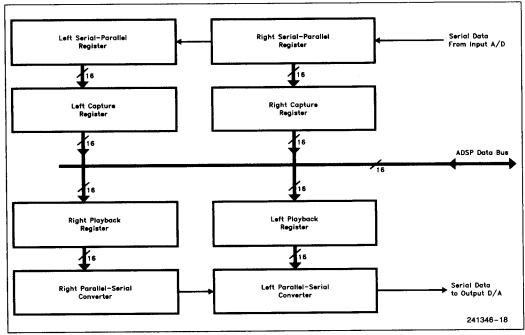

The following figure shows a simplified block diagram of the KAGA gate array interconnections in a typical DVI system. The ADSP outputs stereo digital audio to a dual D/A converter through a set of registers in the gate array. These analog outputs, filtered to a 17 KHz bandwidth, comprise the audio output of the DVI system. Similarly, digital stereo audio is input to the ADSP from a dual A/D converter through a set of registers in the gate array. Additional registers in KAGA provide the mechanism for the ADSP to communicate with DVI Bus components, especially the Host Processor for programming information and VRAM for audio data.

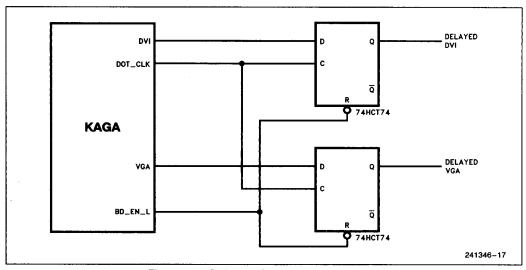

The KAGA chip provides the control signals for analog multiplexing the Intel 82750DB DVI Display Proc-

essor (DB) video with either the host's VGA video or an external source on a pixel-by-pixel basis. The actual video source selection is performed in mux chips capable of instantaneously switching inputs. The control for the keying is generated in KAGA for the VGA video by monitoring the video feature bus and in a black detect circuit for the external RGB video. The keying parameters are determined by registers in the gate array.

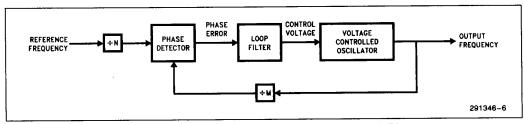

In order for the DB video to be combined with other video sources into a unified video stream, the sources must be synchronized or genlocked; i.e. their horizontal and vertical scanning must be carefully aligned. This is accomplished, in part, by synchronizing the DB horizontal scanning to either the VGA or external RGB horizontal sync using a phaselock loop. The loop is comprised of a phase detector and input counters in the gate array and a loop filter and VCO located off-chip. Together, these components lock the horizontal syncs and provide a pixel clock for the DB video. Alternatively, when genlocking is not required, the phaselock loop can be locked to a 10 MHz crystal to generate the timing for a wide variety of video formats, with pixel rates up to 50 MHz. The selection of clock and sync sources, as well as phaselock loop parameters are determined by registers internal to KAGA.

Manufactured and tested for Intel by Texas Instruments in accordance with Texas Instruments, internal standards.

# 1.0 PIN DESCRIPTION

# 1.1 Pinout

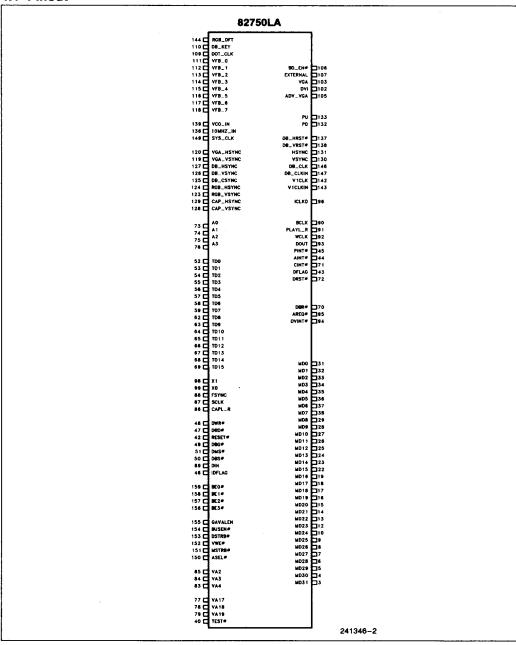

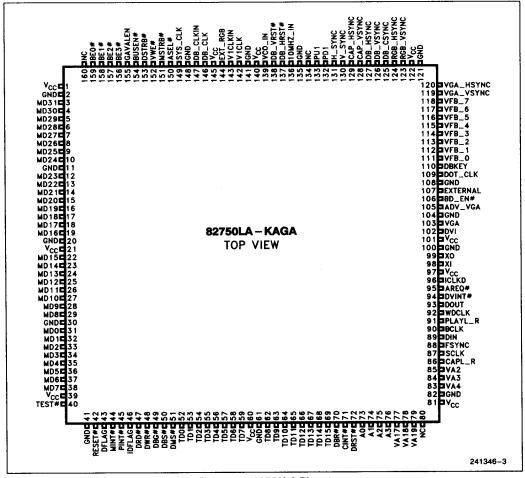

Figure 1-1. 82750LA Pinout

Table 1-1. Pin Cross Reference by Pin Name

| Pin<br>Name | Location |

|-------------|----------|

| 10MHZ_IN    | 136      |

| A0          | 73       |

| A1          | 74       |

| A2          | 75       |

| A3          | 76       |

| ADV_VGA     | 105      |

| AREQ#       | 95       |

| ASEL#       | 150      |

| BCLK        | 90       |

| BD_EN#      | 106      |

| BE0#        | 159      |

| BE1#        | 158      |

| BE2#        | 157      |

| BE3#        | 156      |

| BUSEN#      | 154      |

| CAP HSYNC   | 129      |

| CAP VSYNC   | 128      |

| CAPL R      | 86       |

| CINT#       | 71       |

| DB CLK      | 146      |

| DB CLKIN    | 147      |

| DB CSYNC    | 125      |

| DB HRST#    | 137      |

| DB HSYNC    | 127      |

| DBVRST#     | 138      |

| DB_VSYNC    | 126      |

| DBG#        | 49       |

| DBKEY       | 110      |

| DBR#        | 70       |

| DBS#        | 50       |

| DFLAG       | 43       |

| DIN         | 89       |

| DMS#        | 51       |

| DOT_CLK     | 109      |

| DOUT        | 93       |

| DRD#        | 47       |

| DRS#        | 72       |

| DSTRB#      | 153      |

| DVI         | 102      |

| DVINT#      | 94       |

| DWR #         48           EXT_RGB         144           EXTERNAL         107           FSYNC         88           GAVALEN         155           GND         2           GND         11           GND         20           GND         30           GND         41           GND         61           GND         82           GND         100           GND         104           GND         108           GND         121           GND         135           GND         141           GND         148           HSYNC         131           ICLKD         96           IDFLAG         46           MD0         31           MD1         32           MD2         33           MD3         34           MD4         35           MD5         36           MD6         37           MD7         38           MD9         28           MD10         27           MD11         26 | Pin         | Location     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------|

| EXT_RGB 144  EXTERNAL 107  FSYNC 88  GAVALEN 155  GND 2  GND 11  GND 20  GND 30  GND 41  GND 61  GND 82  GND 100  GND 104  GND 108  GND 121  GND 135  GND 141  GND 135  GND 141  GND 330  GND 30  GND 35  GND 35  GND 35  GND 35  GND 35  GND 31  ICLKD 96  IDFLAG 46  MD0 31  MD1 32  MD2 33  MD3 34  MD4 35  MD5 36  MD6 37  MD7 38  MD6 37  MD7 38  MD8 29  MD9 28  MD10 27  MD11 26                                                                                                                                                                                                                                                                                                                                                                            | Name        | 40           |

| EXTERNAL 107 FSYNC 88 GAVALEN 155 GND 2 GND 11 GND 20 GND 30 GND 41 GND 61 GND 82 GND 100 GND 104 GND 108 GND 121 GND 135 GND 121 GND 135 GND 141 GND 33 MD1 148 HSYNC 131 ICLKD 96 IDFLAG 46 MD0 31 MD1 32 MD2 33 MD3 34 MD4 35 MD5 36 MD6 37 MD7 38 MD8 29 MD9 28 MD10 27 MD11 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |              |

| FSYNC         88           GAVALEN         155           GND         2           GND         11           GND         20           GND         30           GND         41           GND         61           GND         82           GND         100           GND         104           GND         121           GND         141           GND         148           HSYNC         131           ICLKD         96           IDFLAG         46           MD0         31           MD1         32           MD2         33           MD3         34           MD4         35           MD5         36           MD6         37           MD7         38           MD8         29           MD9         28           MD10         27           MD11         26                                                                                                                    |             |              |

| GAVALEN 155 GND 2 GND 11 GND 20 GND 30 GND 41 GND 61 GND 82 GND 100 GND 104 GND 108 GND 121 GND 135 GND 121 GND 135 GND 141 GND 33 GND 33 GND 34 HSYNC 131 ICLKD 96 IDFLAG 46 MD0 31 MD1 32 MD2 33 MD3 34 MD4 35 MD5 36 MD6 37 MD7 38 MD6 37 MD7 38 MD8 29 MD9 28 MD10 27 MD11 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <del></del> |              |

| GND 2 GND 11 GND 20 GND 30 GND 41 GND 61 GND 61 GND 82 GND 100 GND 104 GND 108 GND 121 GND 135 GND 141 GND 135 GND 141 GND 33 GND 31 ICLKD 96 IDFLAG 46 MD0 31 MD1 32 MD2 33 MD3 34 MD4 35 MD5 36 MD6 37 MD7 38 MD6 37 MD7 38 MD8 29 MD9 28 MD10 27 MD11 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             | <del></del>  |

| GND 11 GND 20 GND 30 GND 41 GND 61 GND 82 GND 100 GND 104 GND 108 GND 121 GND 121 GND 135 GND 141 GND 135 GND 141 GND 33 HSYNC 131 ICLKD 96 IDFLAG 46 MD0 31 MD1 32 MD2 33 MD3 34 MD4 35 MD5 36 MD6 37 MD7 38 MD6 37 MD7 38 MD8 29 MD9 28 MD10 27 MD11 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             |              |

| GND 20 GND 30 GND 41 GND 61 GND 82 GND 100 GND 104 GND 108 GND 109 GND 121 GND 121 GND 135 GND 141 GND 148 HSYNC 131 ICLKD 96 IDFLAG 46 MD0 31 MD1 32 MD2 33 MD3 34 MD4 35 MD5 36 MD6 37 MD7 38 MD8 29 MD9 28 MD10 27 MD11 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             |              |

| GND 30 GND 41 GND 61 GND 82 GND 100 GND 104 GND 108 GND 121 GND 135 GND 141 GND 135 GND 141 GND 148 HSYNC 131 ICLKD 96 IDFLAG 46 MD0 31 MD1 32 MD2 33 MD3 34 MD4 35 MD5 36 MD6 37 MD7 38 MD6 37 MD7 38 MD8 29 MD9 28 MD10 27 MD11 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             | 11           |

| GND 41 GND 61 GND 82 GND 100 GND 104 GND 108 GND 121 GND 135 GND 141 GND 148 HSYNC 131 ICLKD 96 IDFLAG 46 MD0 31 MD1 32 MD2 33 MD3 34 MD4 35 MD5 36 MD6 37 MD7 38 MD8 29 MD9 28 MD10 27 MD11 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | GND         | 20           |

| GND 61 GND 82 GND 100 GND 104 GND 108 GND 121 GND 135 GND 141 GND 148 HSYNC 131 ICLKD 96 IDFLAG 46 MD0 31 MD1 32 MD2 33 MD3 34 MD4 35 MD5 36 MD6 37 MD7 38 MD8 29 MD9 28 MD10 27 MD11 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | GND         | 30           |

| GND 82 GND 100 GND 104 GND 108 GND 121 GND 135 GND 141 GND 148 HSYNC 131 ICLKD 96 IDFLAG 46 MD0 31 MD1 32 MD2 33 MD3 34 MD4 35 MD5 36 MD6 37 MD7 38 MD8 29 MD9 28 MD10 27 MD11 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | GND         | 41           |

| GND 100 GND 104 GND 108 GND 108 GND 121 GND 135 GND 141 GND 148 HSYNC 131 ICLKD 96 IDFLAG 46 MD0 31 MD1 32 MD2 33 MD3 34 MD4 35 MD5 36 MD6 37 MD7 38 MD7 38 MD8 29 MD9 28 MD10 27 MD11 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | GND         | 61           |

| GND 104 GND 108 GND 108 GND 121 GND 135 GND 141 GND 148 HSYNC 131 ICLKD 96 IDFLAG 46 MD0 31 MD1 32 MD2 33 MD3 34 MD4 35 MD5 36 MD6 37 MD7 38 MD8 29 MD9 28 MD10 27 MD11 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | GND         | 82           |

| GND 108 GND 121 GND 121 GND 135 GND 141 GND 148 HSYNC 131 ICLKD 96 IDFLAG 46 MD0 31 MD1 32 MD2 33 MD3 34 MD4 35 MD5 36 MD6 37 MD7 38 MD7 38 MD8 29 MD9 28 MD10 27 MD11 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | GND         | 100          |

| GND 121 GND 135 GND 135 GND 141 GND 148 HSYNC 131 ICLKD 96 IDFLAG 46 MD0 31 MD1 32 MD2 33 MD3 34 MD4 35 MD5 36 MD6 37 MD7 38 MD8 29 MD9 28 MD10 27 MD11 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | GND         | 104          |

| GND 135 GND 141 GND 148 HSYNC 131 ICLKD 96 IDFLAG 46 MD0 31 MD1 32 MD2 33 MD3 34 MD4 35 MD5 36 MD6 37 MD7 38 MD8 29 MD9 28 MD10 27 MD11 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | GND         | 108          |

| GND 141 GND 148 HSYNC 131 ICLKD 96 IDFLAG 46 MD0 31 MD1 32 MD2 33 MD3 34 MD4 35 MD5 36 MD6 37 MD7 38 MD8 29 MD9 28 MD10 27 MD11 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | GND         | 121          |

| GND 148 HSYNC 131 ICLKD 96 IDFLAG 46 MD0 31 MD1 32 MD2 33 MD3 34 MD4 35 MD5 36 MD6 37 MD7 38 MD8 29 MD9 28 MD10 27 MD11 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | GND         | 135          |

| HSYNC 131 ICLKD 96 IDFLAG 46 MD0 31 MD1 32 MD2 33 MD3 34 MD4 35 MD5 36 MD6 37 MD7 38 MD8 29 MD9 28 MD10 27 MD11 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | GND         | 141          |

| ICLKD 96 IDFLAG 46 MD0 31 MD1 32 MD2 33 MD3 34 MD4 35 MD5 36 MD6 37 MD7 38 MD8 29 MD9 28 MD10 27 MD11 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | GND         | 148          |

| IDFLAG 46  MD0 31  MD1 32  MD2 33  MD3 34  MD4 35  MD5 36  MD6 37  MD7 38  MD8 29  MD9 28  MD10 27  MD11 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | HSYNC       | 131          |

| MD0 31 MD1 32 MD2 33 MD3 34 MD4 35 MD5 36 MD6 37 MD7 38 MD8 29 MD9 28 MD10 27 MD11 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ICLKD       | 96           |

| MD1 32<br>MD2 33<br>MD3 34<br>MD4 35<br>MD5 36<br>MD6 37<br>MD7 38<br>MD8 29<br>MD9 28<br>MD10 27<br>MD11 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | IDFLAG      | 46           |

| MD2 33<br>MD3 34<br>MD4 35<br>MD5 36<br>MD6 37<br>MD7 38<br>MD8 29<br>MD9 28<br>MD10 27<br>MD11 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | MD0         | 31           |

| MD3 34<br>MD4 35<br>MD5 36<br>MD6 37<br>MD7 38<br>MD8 29<br>MD9 28<br>MD10 27<br>MD11 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MD1         | 32           |

| MD4 35<br>MD5 36<br>MD6 37<br>MD7 38<br>MD8 29<br>MD9 28<br>MD10 27<br>MD11 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MD2         | 33           |

| MD5 36<br>MD6 37<br>MD7 38<br>MD8 29<br>MD9 28<br>MD10 27<br>MD11 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MD3         | 34           |

| MD6 37<br>MD7 38<br>MD8 29<br>MD9 28<br>MD10 27<br>MD11 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | MD4         | 35           |

| MD7 38<br>MD8 29<br>MD9 28<br>MD10 27<br>MD11 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | MD5         | 36           |

| MD8 29<br>MD9 28<br>MD10 27<br>MD11 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | MD6         | 37           |

| MD9 28<br>MD10 27<br>MD11 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | MD7         | 38           |

| MD9 28<br>MD10 27<br>MD11 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | MD8         | 29           |

| MD10 27<br>MD11 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             | <del> </del> |

| MD11 26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             |              |

| 1 1710 12   20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | MD12        | 25           |

| MD13 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |              |

| MD14 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |              |

| MD15 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |              |

| MD16 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             | <del> </del> |

| MD17 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |              |

| Pin       |          |

|-----------|----------|

| Name      | Location |

| MD18      | 17       |

| MD19      | 16       |

| MD20      | 15       |

| MD21      | 14       |

| MD22      | 13       |

| MD23      | 12       |

| MD24      | 10       |

| MD25      | 9        |

| MD26      | 8        |

| MD27      | 7        |

| MD28      | 6        |

| MD29      | 5        |

| MD30      | 4        |

| MD31      | 3        |

| MINT#     | 44       |

| MSTRB#    | 151      |

| NC        | 80       |

| NC        | 134      |

| NC        | 160      |

| PD1       | 132      |

| PINT#     | 45       |

| PLAYL_R   | 91       |

| PU1       | 133      |

| RESET#    | 42       |

| RGB_HSYNC | 124      |

| RGB_VSYNC | 123      |

| SCLK      | 87       |

| SYS_CLK   | 149      |

| TD0       | 52       |

| TD1       | 53       |

| TD2       | 54       |

| TD3       | 55       |

| TD4       | 56       |

| TD5       | 57       |

| TD6       | 58       |

| TD7       | 59       |

| TD8       | 62       |

| TD9       | 63       |

| TD10      | 64       |

| TD11      | 65       |

|           |          |

| Pin<br>Name     | Location |

|-----------------|----------|

| TD12            | 66       |

| TD13            | 67       |

| TD14            | 68       |

| TD15            | 69       |

| TEST#           | 40       |

| V1CLK           | 142      |

| V1CLKIN         | 143      |

| V_SYNC          | 130      |

| VA2             | 85       |

| VA3             | 84       |

| VA4             | 83       |

| VA17            | 77       |

| VA18            | 78       |

| VA19            | 79       |

| V <sub>CC</sub> | 1        |

| V <sub>CC</sub> | 21       |

| V <sub>CC</sub> | 39       |

| V <sub>CC</sub> | 60       |

| V <sub>CC</sub> | 81       |

| V <sub>CC</sub> | 97       |

| V <sub>CC</sub> | 101      |

| V <sub>CC</sub> | 122      |

| V <sub>CC</sub> | 140      |

| V <sub>CC</sub> | 145      |

| VCO_IN          | 139      |

| VFB_0           | 111      |

| VFB1            | 112      |

| VFB2            | 113      |

| VFB_3           | 114      |

| VFB4            | 115      |

| VFB5            | 116      |

| VFB6            | 117      |

| VFB_7           | 118      |

| VGA             | 103      |

| VGA_HSYNC       | 120      |

| VGA_VSYNC       | 119      |

| VWE#            | 152      |

| WDCLK           | 92       |

| ΧI              | 98       |

| хо              | 99       |

Table 1-2. Pin Cross Reference by Pin Number

| Pin<br>Name | Location        |

|-------------|-----------------|

| 1           | Vcc             |

| 2           | GND             |

| 3           | MD31            |

| 4           | MD30            |

| 5           | MD29            |

| 6           | MD28            |

| 7           | MD27            |

| 8           | MD26            |

| 9           | MD25            |

| 10          | MD24            |

| 11          | GND             |

| 12          | MD23            |

| 13          | MD22            |

| 14          | MD21            |

| 15          | MD20            |

| 16          | MD19            |

| 17          | MD18            |

| 18          | MD17            |

| 19          | MD16            |

| 20          | GND             |

| 21          | Vcc             |

| 22          | MD15            |

| 23          | MD14            |

| 24          | MD13            |

| 25          | MD12            |

| 26          | MD11            |

| 27          | MD10            |

| 28          | MD9             |

| 29          | MD8             |

| 30          | GND             |

| 31          | MD0             |

| 32          | MD1             |

| 33          | MD2             |

| 34          | MD3             |

| 35          | MD4             |

| 36          | MD5             |

| 37          | MD6             |

| 38          | MD7             |

| 39          | V <sub>CC</sub> |

| 40          | TEST#           |

| Pin<br>Name | Location        |

|-------------|-----------------|

| 41          | GND             |

| 42          | RESET#          |

| 43          | DFLAG           |

| 44          | MINT#           |

| 45          | PINT#           |

| 46          | IDFLAG          |

| 47          | DRD#            |

| 48          | DWR#            |

| 49          | DBG#            |

| 50          | DBS#            |

| 51          | DMS#            |

| 52          | TD0             |

| 53          | TD1             |

| 54          | TD2             |

| 55          | TD3             |

| 56          | TD4             |

| 57          | TD5             |

| 58          | TD6             |

| 59          | TD7             |

| 60          | V <sub>CC</sub> |

| 61          | GND             |

| 62          | TD8             |

| 63          | TD9             |

| 64          | TD10            |

| 65          | TD11            |

| 66          | TD12            |

| 67          | TD13            |

| 68          | TD14            |

| 69          | TD15            |

| 70          | DBR#            |

| 71          | CINT#           |

| 72          | DRST#           |

| 73          | A0              |

| 74          | A1              |

| 75          | A2              |

| 76          | A3              |

| 77          | VA17            |

| 78          | VA18            |

| 79          | VA19            |

| 80          | NC.             |

| erence by Pin Number |                 |  |

|----------------------|-----------------|--|

| Pin                  | Location        |  |

| Name                 | .,              |  |

| 81                   | V <sub>CC</sub> |  |

| 82                   | GND             |  |

| 83                   | VA4             |  |

| 84                   | VA3             |  |

| 85                   | VA2             |  |

| 86                   | CAPL_R          |  |

| 87                   | SCLK            |  |

| 88                   | FSYNC           |  |

| 89                   | DIN             |  |

| 90                   | BCLK            |  |

| 91                   | PLAYL_R         |  |

| 92                   | WDCLK           |  |

| 93                   | DOUT            |  |

| 94                   | DVINT#          |  |

| 95                   | AREQ#           |  |

| 96                   | ICLKD           |  |

| 97                   | Vcc             |  |

| 98                   | ΧI              |  |

| 99                   | хо              |  |

| 100                  | GND             |  |

| 101                  | Vcc             |  |

| 102                  | DVI             |  |

| 103                  | VGA             |  |

| 104                  | GND             |  |

| 105                  | ADV_VGA         |  |

| 106                  | BD_EN#          |  |

| 107                  | EXTERNAL        |  |

| 108                  | GND             |  |

| 109                  | DOT_CLK         |  |

| 110                  | DBKEY           |  |

| 111                  | VFB0            |  |

| 112                  | VFB1            |  |

| 113                  | VFB_2           |  |

| 114                  | VFB_3           |  |

| 115                  | VFB4            |  |

| 116                  | VFB_5           |  |

| 117                  | VFB6            |  |

| 118                  | VFB_7           |  |

| 119                  | VGA_VSYNC       |  |

| 120                  | VGA_HSYNC       |  |

| Pin<br>Name | Location        |

|-------------|-----------------|

| 121         | GND             |

| 122         | V <sub>CC</sub> |

| 123         | RGB_VSYNC       |

| 124         | RGB_HSYNC       |

| 125         | DB_CSYNC        |

| 126         | DBVSYNC         |

| 127         | DB_HSYNC        |

| 128         | CAP_VSYNC       |

| 129         | CAP_HSYNC       |

| 130         | V_SYNC          |

| 131         | H_SYNC          |

| 132         | PD1             |

| 133         | PU1             |

| 134         | NC              |

| 135         | GND             |

| 136         | 10MHZ_IN        |

| 137         | DB_HRST#        |

| 138         | DB_VRST#        |

| 139         | VCOIN           |

| 140         | V <sub>CC</sub> |

| 141         | GND             |

| 142         | V1CLK           |

| 143         | V1CLKIN         |

| 144         | EXTRGB          |

| 145         | V <sub>CC</sub> |

| 146         | DB_CLK          |

| 147         | DB_CLKIN        |

| 148         | GND             |

| 149         | SYS_CLK         |

| 150         | ASEL#           |

| 151         | MSTRB#          |

| 152         | VWE#            |

| 153         | DSTRB#          |

| 154         | BUSEN#          |

| 155         | GAVALEN         |

| 156         | BE3#            |

| 157         | BE2#            |

| 158         | BE1#            |

| 159         | BE0#            |

| 160         | NC              |

|             |                 |

# 1.2 Pin Descriptions

# 1.2.1 KAGA AUDIO AND DVI BUS SIGNAL DEFINITIONS

| Symbol    | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                         |

|-----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A3-A0     | ı    | A3-A0: DSP address output used in the decode of external data memory and boot memory space.                                                                                                                                                                                                                                                                                               |

| AREQ#     | 0    | <b>AUDIO REQUEST SIGNAL:</b> This signal is asserted indicating that the DSP is requesting control of the DMA Channel for VRAM accesses.                                                                                                                                                                                                                                                  |

| ASEL#     | ı    | <b>AUDIO SELECT SIGNAL:</b> This signal indicates that the Host has acknowledged the audio request.                                                                                                                                                                                                                                                                                       |

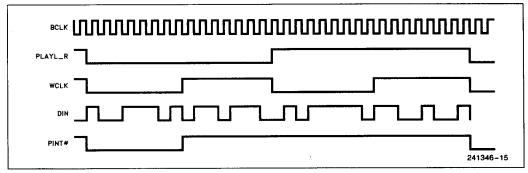

| BCLK      | 0    | <b>DAC BIT CLOCK SIGNAL:</b> The rising edge of this clock will shift the serial data into the internal serial shift register of the DAC.                                                                                                                                                                                                                                                 |

| BE#3-BE#0 | BI   | BYTE ENABLES 3-0: These signals are used by PB and DVI bus devices to indicate which bytes in the 32-bit VRAM word are being accessed. These signals should be driven by the device causing the DVI bus cycle during a VRAM access. These signals are driven by the host interface logic during a host access of registers residing in KAGA.                                              |

| BUSEN#    | 1    | BUS ENABLE SIGNAL: This signal is driven by PB in response to the HREQ# signal. BUSEN# indicates that the DVI bus can now be used by KAGA provided the ASEL# signal is asserted.                                                                                                                                                                                                          |

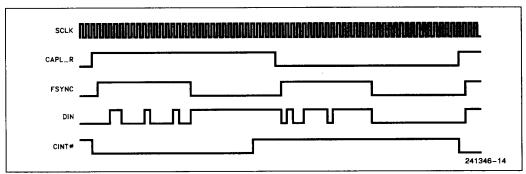

| CAPL_R    | 1    | CAPTURE LEFT/RIGHT CLOCK: This signal is generated in the ADC. KAGA receives this clock from the ADC whose output frequency is at the word rate. When this clock is high, left channel data is output. When this signal is low, right channel data is output.                                                                                                                             |

| CINT#     | 0    | <b>CAPTURE INTERRUPT:</b> Generated internal to KAGA. This signal is connected to the highest priority interrupt on the DSP (IRQ2#). The signal CAPL_R initiates a CINT#. CINT# is negated when either of the audio input registers are read.                                                                                                                                             |

| DBG#      | 1    | <b>BUS GRANT INPUT:</b> This signal originates from the DSP (signal BG $\#$ ). Control of the DSP bus is transferred to the DVI Device when the DSP asserts the BG $\#$ signal.                                                                                                                                                                                                           |

| DBR#      | 0    | BUS REQUEST OUTPUT: This signal is connected to the DSP BR# signal. When the DVI Device requires access to the DSP external bus or if the DVI Device must halt the DSP it will assert DBR#. If the DSP is not performing an external access, then it will respond to the DBR# signal in the same cycle by tri-stating the DSP data and address bus as well as DMS#, DBS#, DRD#, and DWR#. |

| DBS#      | ı    | <b>BOOT MEMORY SELECT:</b> This signal is the DSP BMS# signal. The DSP signal DBS# is used to select the boot memory interface.                                                                                                                                                                                                                                                           |

| DFLAG     | 0    | DSP FLAG: This signal is the DMARDY (DMA Ready) signal generated internal to KAGA. This signal is tied to the asynchronous input FI (Flag In) of the DSP. When DMARDY is asserted (high) the DSP is then able to read or write VRAM.                                                                                                                                                      |

| DIN       | l    | SERIAL DATA INPUT: This is the serial data received from the ADC. Audio data bits are presented MSB first, in 2's complement format.                                                                                                                                                                                                                                                      |

| DVINT#    | 0    | <b>DVI DEVICE INTERRUPT:</b> Generated internal to KAGA. This signal is asserted when the DSP writes to the Message to DVI Device register (MDVI). This signal is <b>negated</b> when the DVI Device reads the most significant byte of the MDVI register.                                                                                                                                |

| DMS#      | ı    | DATA MEMORY SELECT: DSP strobe signal for data memory accesses. When the DMS# signal is asserted this indicates that the address bus is being driven with a data memory address and memory can be selected.                                                                                                                                                                               |

| DOUT      | 0    | DATA OUTPUT: Serial data presented to the playback DAC. The DAC receives this data (with the MSB first) in Binary Two's Complement (BTC) form. The DAC takes this data as input and converts it into analog form.                                                                                                                                                                         |

# 1.2.1 KAGA AUDIO AND DVI BUS SIGNAL DEFINITIONS (Continued)

| Symbol   | Туре | Name and Function                                                                                                                                                                                                                                                                                               |

|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRD#     | ı    | <b>MEMORY READ ENABLE INPUT:</b> This signal is the DSP RD# signal. RD# is a DSP control signal, indicating the direction of the data transfer. When this signal is asserted the operation will be a DSP read of internal registers to KAGA.                                                                    |

| DRST#    | 0    | <b>DSP RESET:</b> DRST# halts DSP execution and returns all registers to a known state. When this bit is negated, the booting sequence takes place.                                                                                                                                                             |

| DWR#     | ı    | <b>MEMORY WRITE ENABLE INPUT:</b> This signal is the DSP WR # signal. WR # is a DSP control signal, indicating the direction of the data transfer. When this signal is asserted the operation will be a DSP write to internal registers of KAGA.                                                                |

| DSTRB#   | ı    | <b>DEVICE STROBE:</b> This signal is used to access one of the eight DVI Devices. This signal is generated whenever a VRAM access falls above the 15M byte boundary.                                                                                                                                            |

| FSYNC    | 1    | FRAME SYNC SIGNAL: This signal is generated internal to the ADC. KAGA receives this clock from the ADC. This is an output clock which goes high coincident with the start of the first data bit (MSB) and falls immediately after the last data bit (LSB).                                                      |

| GAVALEN  | l    | GATE ARRAY VALID ADDRESS LATCH ENABLE: This signal is used to latch the VRAM address from the MD31-MD0) lines. The MD31-MD0) bus is latched at the falling edge of GAVALEN. When GAVALEN and BUSEN# are asserted, the MD31-MD0) bus is used for VRAM address information.                                       |

| ICKLD    | 0    | INPUT CLOCK DIGITAL: This clock is generated in KAGA. This is the source clock for the ADC. This clock runs the digital filter internal to the ADC on the CS2 board. ICLKD must be 384 times the desired sample rate.                                                                                           |

| IDFLAG   | I    | INPUT DSP FLAG: Input signal to KAGA form the DSP. This signal may be set, toggled, or cleared in software to signal events or conditions to the DVI Device.                                                                                                                                                    |

| MD31-MD0 | ВІ   | <b>MEMORY DATA:</b> This bus is the DVI bus data path. MD(0) is the least significant bit. This bus can be used at the start of a DVI bus cycle to temporarily hold the VRAM address until latched by GAVALEN.                                                                                                  |

| MINT#    | 0    | <b>MESSAGE BIT:</b> Generated in KAGA. This signal is asserted when the DVI Device completes a write to the Message to DSP register (MDSP). This signal is negated when the DSP reads the MDSP register.                                                                                                        |

| MSTRB#   | 1    | MEMORY STROBE: This signal is used to latch data during a VRAM access. This signal is generated whenever a VRAM access falls below the 15M byte boundary.                                                                                                                                                       |

| PINT#    | 0    | PLAYBACK INTERRUPT: Generated in KAGA. Interrupt signal to the DSP. This signal is connected to the next highest priority interrupt on the DSP (IRQ1 #). The frequency of PINT # is equivalent to the audio output sample rate. This signal is negated when either of the audio playback registers are written. |

| PLAYL_R  | 0    | PLAYBACK LEFT/RIGHT CLOCK: This signal is the playback left/right selector signal. PLAYL_R has a 50% duty cycle and is equivalent to the playback sample rate. When this signal is high the DOUT data is right channel information.                                                                             |

| RESET#   | I    | KAGA RESET INPUT: This signal when asserted will initialize KAGA internal registers and counters. When asserted, KAGA will place the DSP in a reset state.                                                                                                                                                      |

| SCLK     | l    | SERIAL DATA CLOCK: Capture bit clock generated internal to the ADC. Data is clocked out on the rising edge of this clock. This signal is 64 times the source clock (ICLKD) of the ADC.                                                                                                                          |

| TD15-TD0 | ВІ   | <b>DSP DATA BUS:</b> Data communications for register transfers between KAGA and DSP.                                                                                                                                                                                                                           |

| TEST#    | 1    | TEST PIN: When this signal is asserted the outputs of KAGA are tri-stated.                                                                                                                                                                                                                                      |

| V1CLKIN  | I    | V1 CLOCK: This is the main synchronizing signal for the DVI bus. Although the DVI bus is asynchronous in nature and is meant to be event driven, there are some signals that must be applied to PB synchronously.                                                                                               |

# 1.2.1 KAGA AUDIO AND DVI BUS SIGNAL DEFINITIONS (Continued)

| Symbol    | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

|-----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| VWE#      | BI   | VRAM WRITE ENABLE: This signal is the read/write status line that further defines the bus cycle into a read or write type of cycle. This signal is driven by KAGA when KAGA is causing a DVI bus cycle. VWE # is asserted for a write operation and negated for a read operation. When performing Device Register accesses this signal is driven by the host. |  |  |  |  |  |  |  |

| VA4-VA2   | 1    | VRAM ADDRESSES VA4-VA1: These are the bits that define the offset for a DVI Device register access. The audio portion of KAGA uses only 2 locations (0000b, 0001b).                                                                                                                                                                                           |  |  |  |  |  |  |  |

| VA19-VA17 | l    | VRAM ADDRESSES VA19-VA17: These are the bits that define the DVI Device ID for a DVI Device register access. KAGA has been assigned an ID of 5 (101B).                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| WDCLK     | 0    | WORD CLOCK: This is a playback clock. This clock is generated in KAGA. Clock frequency is 2 times the playback sample rate.                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| ΧI        | l    | CRYSTAL INPUT (16.9344 MHz): Source clock for audio capture and playback clock generation circuitry.                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| XO        | 0    | CLOCK OUTPUT (16.9344 MHz): Oscillator output signal.                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

# 1.2.2 KAGA KEYING/GENLOCK SIGNAL DEFINITIONS

| Symbol    | Туре | Name and Function                                                                                                                                                                                               |

|-----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADV_VGA   | 0    | ADVANCE VGA: Not used in this design. This is a pre-VGA signal.                                                                                                                                                 |

| BD_EN#    | 0    | BLACK DETECT ENABLE: Enable signal for the Black Detect circuitry. Black Detect examines the R G and B external video input and generates video mux control signals when black is detected.                     |

| 10MHZ_IN  | ı    | 10 MHz INPUT CLOCK: The source of this clock is the 10 MHz oscillator output of the DSP chip. This clock can be selected as the source clock for the PB or DB.                                                  |

| SYS_CLK   | I    | 25 MHz INPUT CLOCK: The source of this clock is a 25 MHz oscillator. This clock can be selected as the source clock for the PB or DB.                                                                           |

| DB_CSYNC  | ı    | DB COMPOSITE SYNC INPUT: The source of this signal is the Video Display Processor (DB). This signal contains the vertical serration and equalization information as well as horizontal synchronization pulses.  |

| DOT_CLK   | ١    | VGA DOT CLOCK: Dot frequency originating from the Video Graphics Adaptor (VGA) circuitry.                                                                                                                       |

| DVI       | 0    | <b>DVI VIDEO SELECT:</b> Active high signal. When this signal is asserted the video mux passes the DVI video to the output video amplifiers.                                                                    |

| EXTERNAL  | 0    | <b>EXTERNAL SELECT:</b> Software can force this signal. If this signal is active then the external video (R,G,B) will pass through the video mux on the DS2 board to the video output.                          |

| EXT_RGB   | ı    | <b>EXTERNAL RGB:</b> Status bit which determines the power on default state for video keying operation.                                                                                                         |

| DB_HRST#  | 0    | HORIZONTAL RESET OUTPUT: KAGA generates this signal. Assertion of this signal will reset all of the horizontal timing to the start of the horizontal line.                                                      |

| CAP_HSYNC | ı    | CAPTURE HORIZONTAL SYNC: Horizontal video synchronization signal. The source of this signal is the Video Capture circuitry.                                                                                     |

| VGA_HSYNC | 1    | VGA BUS HORIZONTAL SYNC: Horizontal video synchronization signal. The source of this signal is the VGA circuitry.                                                                                               |

| DB_HSYNC  | 1    | DB HORIZONTAL SYNC: The source of this signal is the Video Display Processor (DB). This is a video synchronization signal which is asserted at the beginning of every line and ends a programmed time later.    |

| RGB_HSYNC | 1    | <b>EXTERNAL HORIZONTAL SYNC:</b> Horizontal video synchronization signal. The source of this signal is the External RGB circuitry.                                                                              |

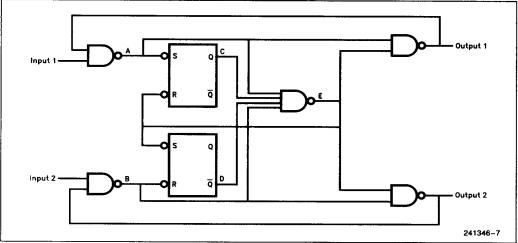

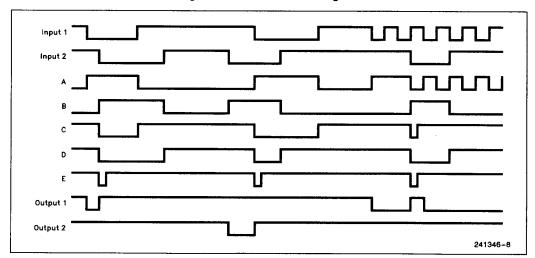

| PD1       | 0    | <b>PUMP DOWN OUTPUT:</b> Phase Detector output. This signal together with the PU1 signal are inputs to the charge pump to the PLL circuit.                                                                      |

| PU1       | 0    | PUMP UP OUTPUT: Phase Detector output. This signal together with the PD1 signal are inputs to the charge pump to the PLL circuit.                                                                               |

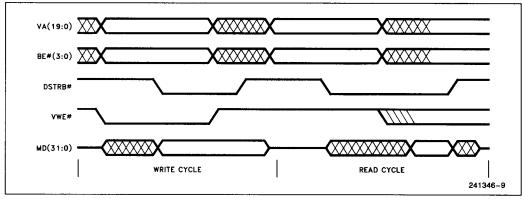

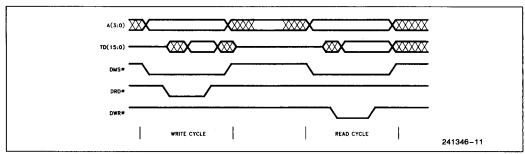

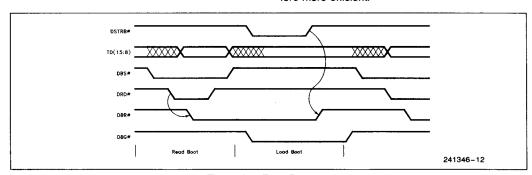

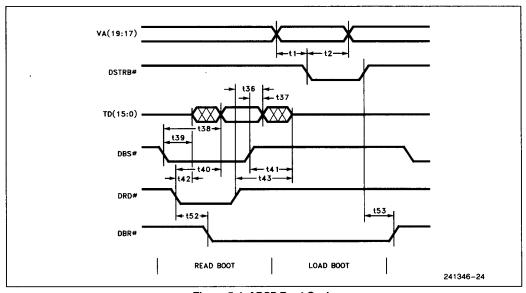

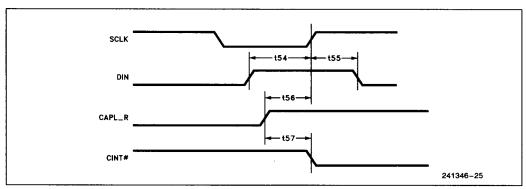

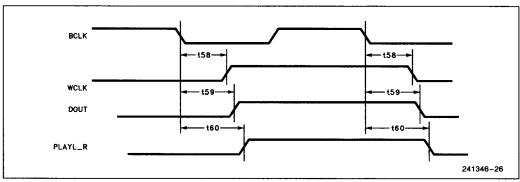

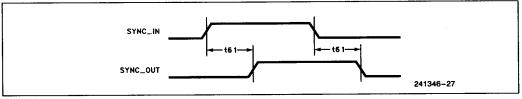

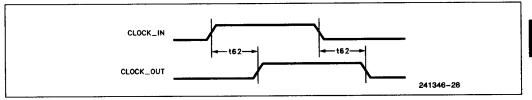

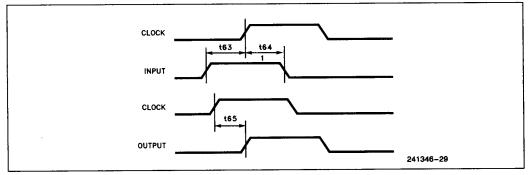

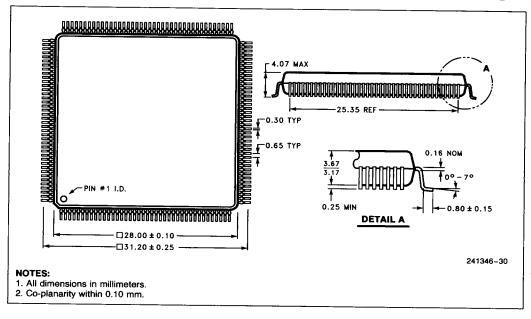

| V1CLK     | 0    | PB CLOCK SOURCE: This signal provides the fundamental timing for the 82750PB.                                                                                                                                   |