DRV8143-Q1 SLVSG63 - JANUARY 2023

# DRV8143-Q1 Automotive Half Bridge Driver with Integrated Current Sense and **Diagnostics**

#### 1 Features

- AEC-Q100 qualified for automotive applications:

- Temperature grade 1: –40°C to +125°C, T<sub>△</sub>

- Functional Safety-Capable

- Documentation available to aid functional safety system design

- 4.5-V to 35-V (40-V abs. max) operating range

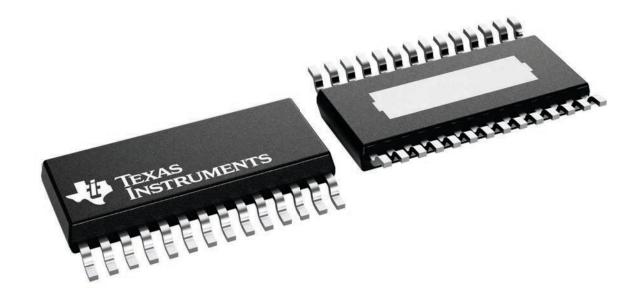

- SPI(S) or HW(H) variant in VQFN-HR package:  $R_{ON\_LS}$  +  $R_{ON\_HS}$ : 42 m $\Omega$

- SPI(P) variant in HVSSOP package: R<sub>ON LS</sub> +  $R_{ON\ HS}$ : 49 m $\Omega$

- $I_{OUT}$  Max = 20 A

- PWM frequency operation up to 125 KHz with automatic dead time assertion

- Configurable slew rate and spread spectrum clocking for low electromagnetic interference (EMI)

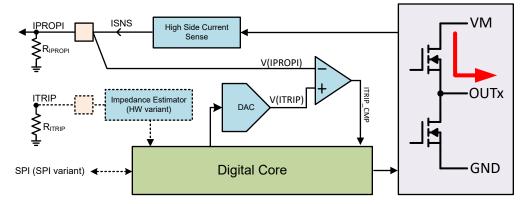

- Integrated current sense (eliminates shunt resistor)

- Proportional load current output on IPROPI pin

- Configurable current regulation

- Protection and diagnostic features with configurable fault reaction (latched or retry)

- Load diagnostics in both the off-state and onstate to detect open load and short circuit

- Voltage monitoring on supply (VM) and charge pump (VCP)

- Over current protection

- Over temperature protection

- Fault indication on nFAULT pin

- Supports 3.3-V, 5-V logic inputs

- Low sleep current 1µA typical at 25°C

- Device family comparison table

## 2 Applications

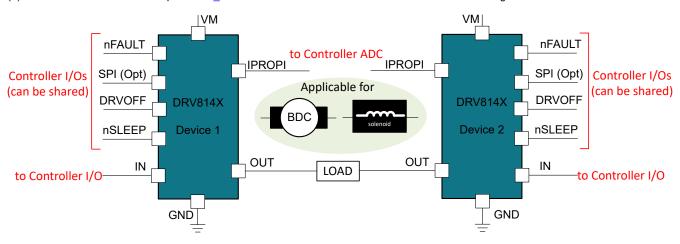

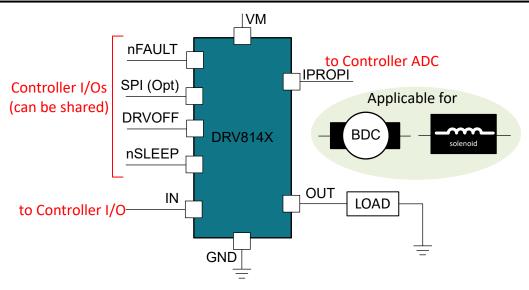

- Automotive brushed DC motors, Solenoids

- Door modules and seat modules

- Body control module (BCM)

- Fuel, water, oil pumps

- On board charger

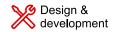

## 3 Description

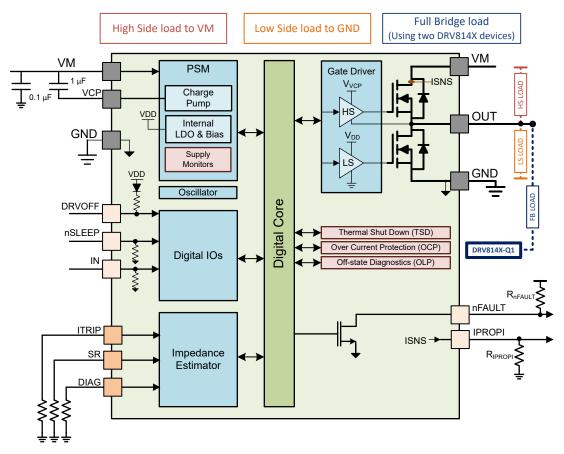

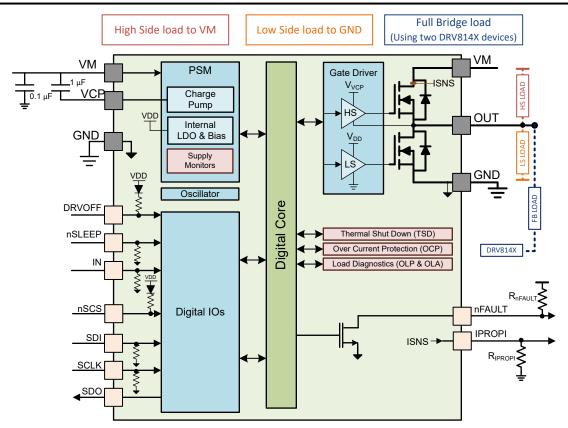

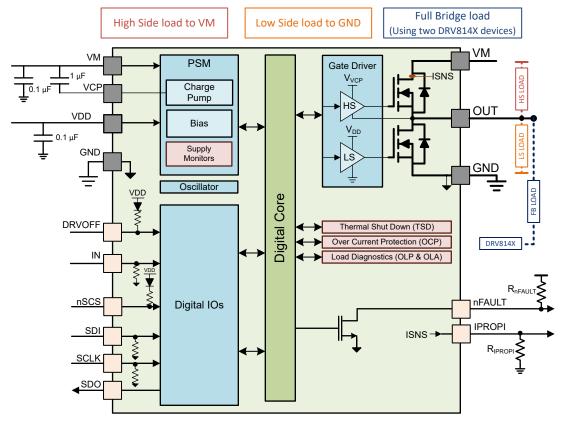

The DRV814x-Q1 family of devices is a fully integrated half-bridge driver intended for a wide range of automotive applications. Designed in a BiCMOS high power process technology node, this monolithic family of devices in a power package offer excellent power handling and thermal capability while providing compact package size, ease of layout, EMI control, accurate current sense, robustness, and diagnostic capability. This family provides an identical pin function with scalable R<sub>ON</sub> (current capability) to support different loads.

The devices integrate a N-channel half-bridge, charge pump regulator, high-side current sensing with regulation, current proportional output, and protection circuitry. A low-power sleep mode is provided to achieve low quiescent current. The devices offer voltage monitoring and load diagnostics as well as protection features against over current and over temperature. Fault conditions are indicated on nFAULT pin. DRV8143 and DRV8145 are available in three variants - hardwired interface: HW (H) and two SPI interface variants: SPI(P) and SPI(S), with SPI (P) for externally supplied logic supply and SPI (S) for internally generated logic supply. DRV8144 is available only in two variants: SPI(S) and HW(H). The SPI interface variants offer more flexibility in device configuration and fault observability.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE      | BODY SIZE (nominal) |

|-------------|--------------|---------------------|

| DRV8143-Q1  | VQFN-HR (14) | 3 mm X 4.5 mm       |

| DRV8143-Q1  | HVSSOP (28)  | 3 mm X 7.3 mm       |

For all available packages, see the orderable addendum at the end of the data sheet

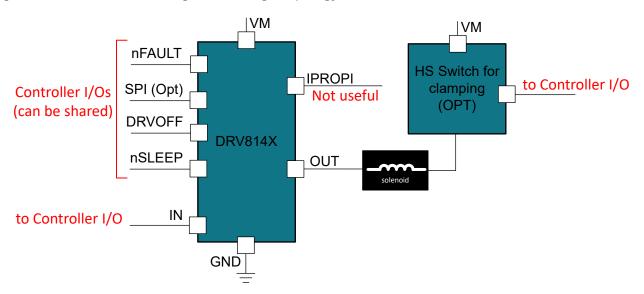

Simplified Schematic

# **Table of Contents**

| 1 Features                           | 8.3 Feature Description                             | 29                |

|--------------------------------------|-----------------------------------------------------|-------------------|

| 2 Applications                       |                                                     |                   |

| 3 Description                        |                                                     | 41                |

| 4 Revision History2                  |                                                     | 45                |

| 5 Device Comparison                  | 9 Application and Implementation                    | 52                |

| 6 Pin Configuration and Functions4   |                                                     |                   |

| 6.1 HW Variant4                      |                                                     |                   |

| 6.2 SPI Variant                      |                                                     |                   |

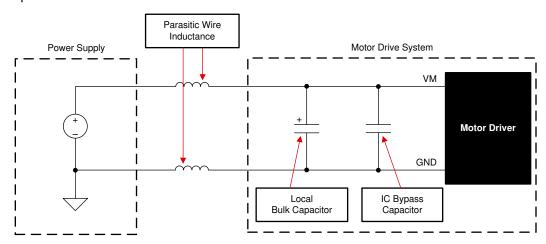

| 7 Specifications                     | 10.1 Bulk Capacitance Sizing                        | 56                |

| 7.1 Absolute Maximum Ratings         | 11 Layout                                           | 57                |

| 7.2 ESD Ratings                      | 11.1 Layout Guidelines                              | 57                |

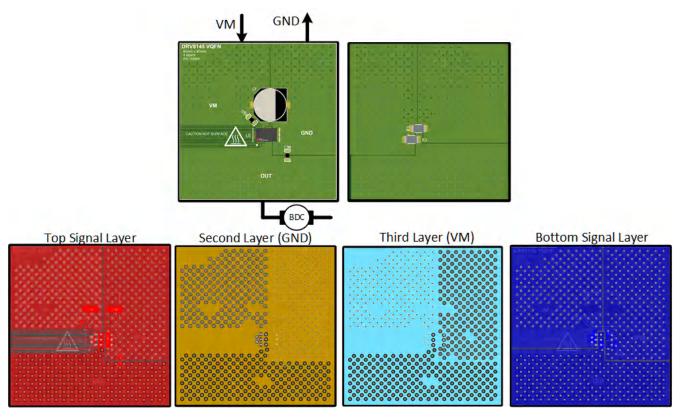

| 7.3 Recommended Operating Conditions | 11.2 Layout Example                                 | 57                |

| 7.4 Thermal Information              | 12 Device and Documentation Support                 | 58                |

| 7.5 Electrical Characteristics       | 12.1 Documentation Support                          | 58                |

| 7.6 SPI Timing Requirements16        | 12.2 Receiving Notification of Documentation Update | s <mark>58</mark> |

| 7.7 Switching Waveforms18            | 12.3 Community Resources                            | 58                |

| 7.8 Typical Characteristics23        | 12.4 Trademarks                                     | 58                |

| 8 Detailed Description26             |                                                     |                   |

| 8.1 Overview                         |                                                     | 58                |

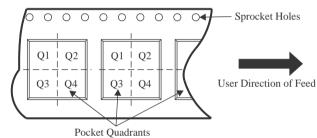

| 8.2 Functional Block Diagram27       | 13.1 Tape and Reel Information                      | 58                |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| DATE         | REVISION NOTES |                 |

|--------------|----------------|-----------------|

| January 2023 | *              | Initial Release |

# **5 Device Comparison**

Table 5-1 summarizes the R<sub>ON</sub> and package differences between devices in the family.

Table 5-1. Device Comparison

| PART NUMBER <sup>(1)</sup> | (LS + HS) R <sub>ON</sub> | I <sub>OUT</sub> MAX | PACKAGE      | BODY SIZE (nominal) | Variants        |

|----------------------------|---------------------------|----------------------|--------------|---------------------|-----------------|

| DRV8143-Q1                 | 42 mΩ                     | 20 A                 | VQFN-HR (14) | 3 mm X 4.5 mm       | HW (H), SPI (S) |

| DRV8143-Q1                 | 49 mΩ                     | 20 A                 | HVSSOP (28)  | 3 mm X 7.3 mm       | SPI (P)         |

| DRV8144-Q1                 | 23.6 mΩ                   | 30 A                 | VQFN-HR (16) | 3 mm X 6 mm         | HW (H), SPI (S) |

| DRV8145-Q1                 | 16 mΩ                     | 46 A                 | VQFN-HR (16) | 3.5 mm X 5.5 mm     | HW (H), SPI (S) |

| DRV8145-Q1                 | 19 mΩ                     | 46 A                 | HTSSOP (28)  | 4.4 mm X 9.7 mm     | SPI (P)         |

<sup>(1)</sup> This is the product datasheet for the DRV8143-Q1. Please reference other device variant data sheets for additional information.

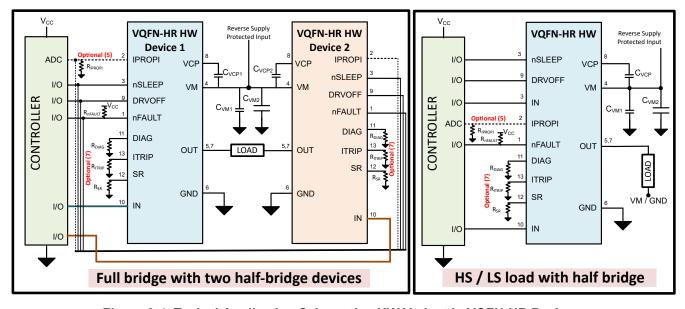

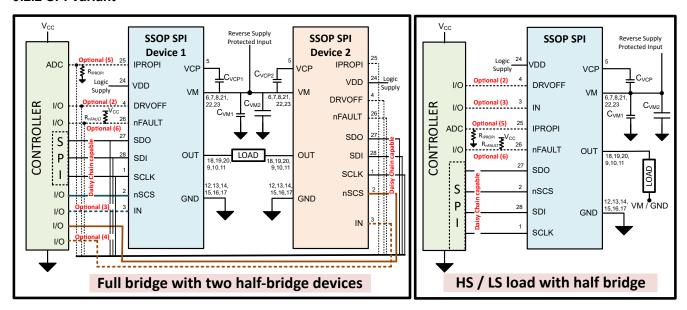

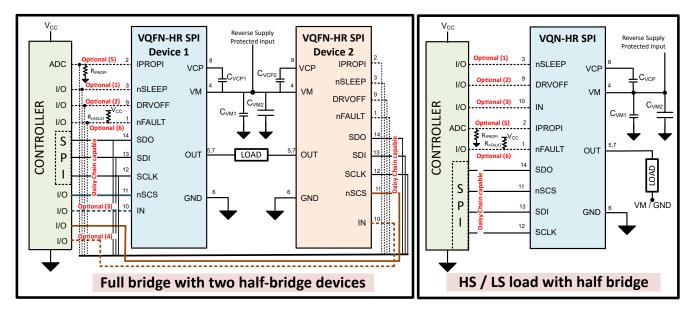

Table 5-2 summarizes the feature differences between the SPI and HW interface variants in the DRV814X-Q1 family. In general, the SPI variant offers more configurability, bridge control options, diagnostic feedback, redundant driver shutoff, improved Pin FMEA and additional features.

In addition, the SPI variant has two options - SPI (S) variant and SPI (P) variant. The SPI (P) variant supports an external, low voltage 5 V supply to the device through the VDD pin for the device logic, whereas in the SPI (S) variant, this supply is internally derived from the VM pin. With this external logic supply, the SPI (P) variant avoids device brown out (reset of device) during VM under voltage transients.

Table 5-2. SPI Variant vs HW Variant Comparison

| FUNCTION                                                                  | HW (H) Variant                                 | SPI (S) Variant                                     | SPI (P) Variant                                      |

|---------------------------------------------------------------------------|------------------------------------------------|-----------------------------------------------------|------------------------------------------------------|

| Bridge control                                                            | Pin only                                       |                                                     | it with pin status indication (Refer<br>Pin control) |

| Sleep function                                                            | Available th                                   | rough nSLEEP pin                                    | Not available                                        |

| External logic supply to the device                                       | Not supported                                  | Not supported                                       | Supported through VDD pin                            |

| Clear fault command                                                       | Reset pulse on nSLEEP pin                      | SPI CLR_FAI                                         | JLT command                                          |

| Slew rate                                                                 | 6 levels                                       | 8 le                                                | vels                                                 |

| Over current protection (OCP)                                             | Fixed at the highest setting                   | 3 choices for thresholds, 4 choices for filter time |                                                      |

| ITRIP regulation                                                          | 5 levels with disable & fixed TOFF time        | 7 levels with disable & indication                  | n, with programmable TOFF time                       |

| Individual fault reaction configuration between retry or latched behavior | Not supported, either all latched or all retry | Supp                                                | ported                                               |

| Detailed fault logging and device status feedback                         | Not supported, nFAULT pin monitoring necessary | Supported, nFAULT p                                 | oin monitoring optional                              |

| VM over voltage                                                           | Fixed                                          | 4 thresho                                           | ld choices                                           |

| On-state (Active) diagnostics                                             | Not supported                                  | Supported for                                       | high-side loads                                      |

| Spread spectrum clocking (SSC)                                            | Not supported                                  | Supp                                                | oorted                                               |

Table 5-3. Differentiating between devices in the family

| Device      | Package Symbolization | DEVICE_ID Register |

|-------------|-----------------------|--------------------|

| DRV8143H-Q1 | 8143H                 | Not applicable     |

| DRV8144H-Q1 | 8144H                 | Not applicable     |

| DRV8145H-Q1 | 8145H                 | Not applicable     |

| DRV8143S-Q1 | 8143S                 | 0 x BA             |

| DRV8144S-Q1 | 8144S                 | 0 x CA             |

| DRV8145S-Q1 | 8145S                 | 0 x DA             |

| DRV8143P-Q1 | 8143P                 | 0 x BE             |

| DRV8145P-Q1 | 8145P                 | 0 x DE             |

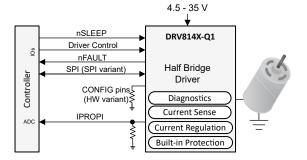

# 6 Pin Configuration and Functions6.1 HW Variant

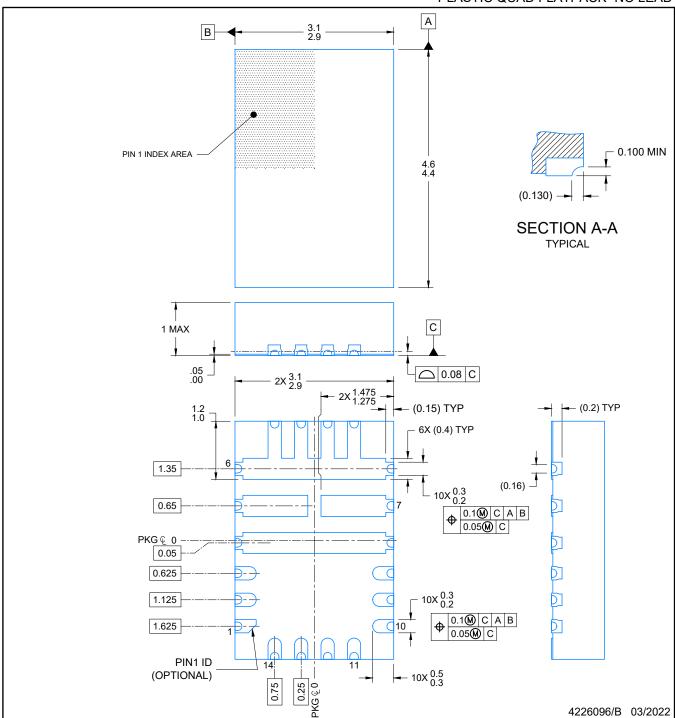

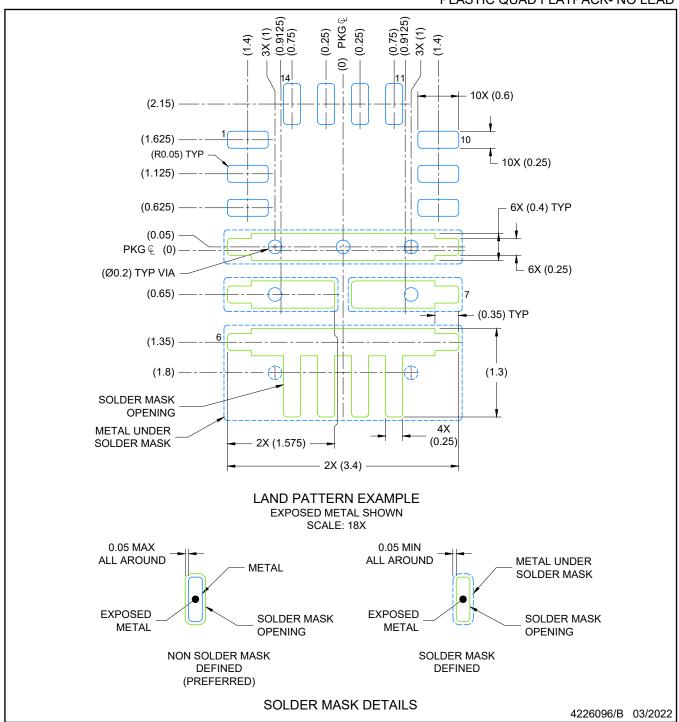

## 6.1.1 VQFN-HR (14) package

Figure 6-1. DRV8143H-Q1 HW variant in VQFN-HR (14) package

Table 6-1. Pin Functions

| Р   | IN     | TYPE (1) | DESCRIPTION                                                                                                                                |

|-----|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME   |          | DESCRIPTION                                                                                                                                |

| 1   | nFAULT | OD       | Fault indication to the controller. For details, refer to nFAULT in the Device Configuration section.                                      |

| 2   | IPROPI | I/O      | Driver load current analog feedback. For details, refer to IPROPI in the Device Configuration section.                                     |

| 3   | nSLEEP | I        | Controller input pin for SLEEP. For details, see the Bridge Control section.                                                               |

| 4   | VM     | Р        | Power supply. This pin is the motor supply voltage. Bypass this pin to GND with a 0.1-μF ceramic capacitor and a bulk capacitor.           |

| 5,7 | OUT    | Р        | Half-bridge output. Connect this pin to the motor or load. Must combine with the other OUT pin to support device current capability.       |

| 6   | GND    | G        | Ground pin                                                                                                                                 |

| 8   | VCP    | Р        | Charge Pump pin for storage cap. Connect a 6.3V, 1µF capacitor to VM supply.                                                               |

| 9   | DRVOFF | I        | Controller input pin for bridge Hi-Z. For details, see the Bridge Control section.                                                         |

| 10  | IN     | I        | Controller input pin for bridge operation. For details, see the Bridge Control section.                                                    |

| 11  | DIAG   | I        | Device configuration pin for load type indication. For details, refer to DIAG in the Device Configuration section                          |

| 12  | SR     | I        | Device configuration pin for Slew Rate control . For details, refer to Slew Rate in the Device Configuration section.                      |

| 13  | ITRIP  | I        | Device configuration pin for ITRIP level for high-side current limiting . For details, refer to ITRIP in the Device Configuration section. |

| P   | IN   | TYPE (1) | DESCRIPTION |

|-----|------|----------|-------------|

| NO. | NAME |          |             |

| 14  | NC   | I        | No connect  |

(1) I = input, O = output, I/O = input/output, G = ground, P = power, OD = open-drain output, PP = push-pull output

## 6.2 SPI Variant

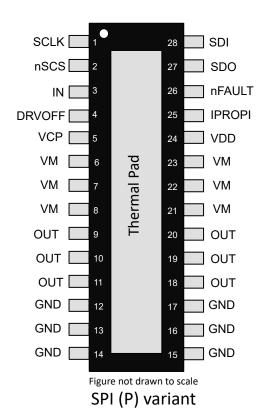

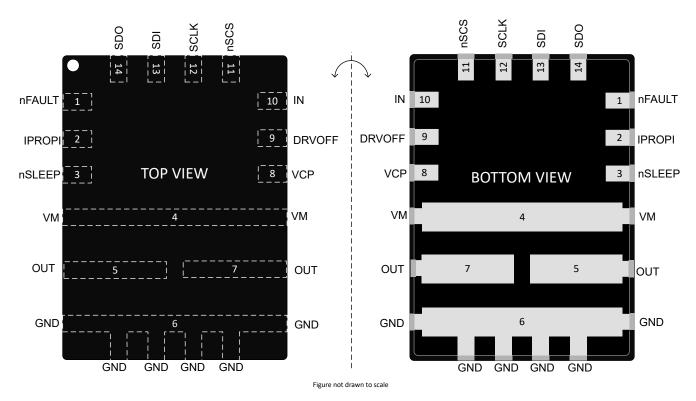

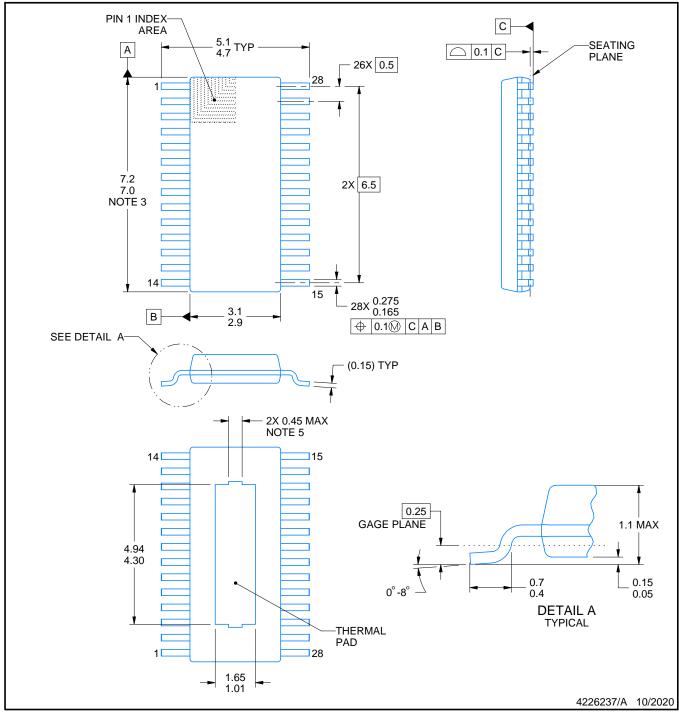

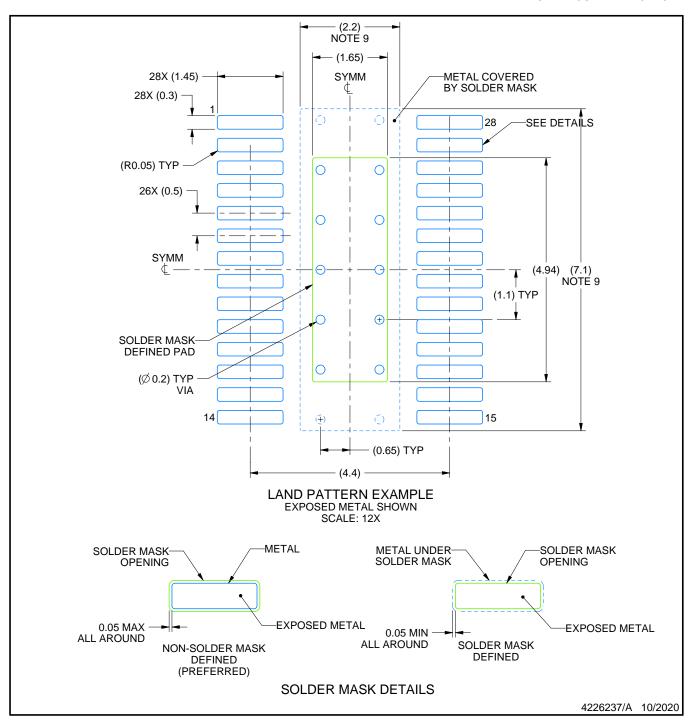

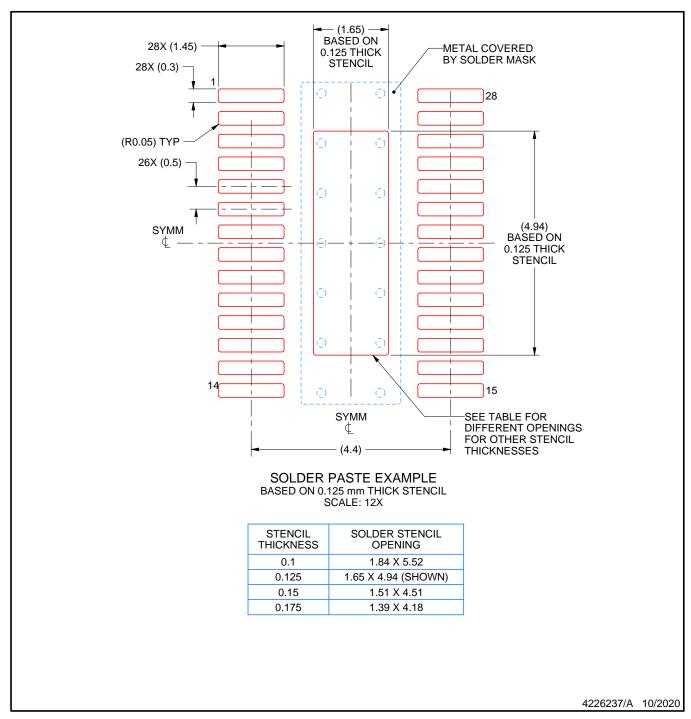

# 6.2.1 HVSSOP (28) package

Figure 6-2. DRV8143P-Q1 SPI(P) variant in HVSSOP (28) package

**Table 6-2. Pin Functions**

| PI                        | IN     | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                            |

|---------------------------|--------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.                       | NAME   |                     | DESCRIPTION                                                                                                                                                                                                            |

| 1                         | SCLK   | ļ                   | SPI - Serial Clock input.                                                                                                                                                                                              |

| 2                         | nSCS   | ļ                   | SPI - Chip Select. An active low on this pin enables the serial interface communication.                                                                                                                               |

| 3                         | IN     | I                   | Controller input pin for bridge operation. For details, see the Bridge Control section.                                                                                                                                |

| 4                         | DRVOFF | Į                   | Controller input pin for bridge Hi-Z. For details, see the Bridge Control section.                                                                                                                                     |

| 5                         | VCP    | Р                   | Charge Pump pin for storage cap. Connect a 6.3V, 1µF capacitor to VM supply.                                                                                                                                           |

| 6, 7, 8, 21,<br>22, 23    | VM     | Р                   | Power supply. This pin is the motor supply voltage. Must combine with the rest of VM pins (6 total) to support device current capability. Bypass this pin to GND with a 0.1-µF ceramic capacitor and a bulk capacitor. |

| 9, 10, 11, 18,<br>19, 20  | OUT    | Р                   | Half-bridge output. Connect this pin to the motor or load. Must combine with the rest of OUT pins (6 total) to support device current capability.                                                                      |

| 12, 13, 14,<br>15, 16, 17 | GND    | G                   | Ground pin. Must combine with the rest of GND pins (6 total) to support device current capability.                                                                                                                     |

| 24                        | VDD    | Р                   | Logic power supply to the device.                                                                                                                                                                                      |

## **Table 6-2. Pin Functions (continued)**

| P   | IN     | TYPE(1) | DESCRIPTION                                                                                            |

|-----|--------|---------|--------------------------------------------------------------------------------------------------------|

| NO. | NAME   | IIFE\/  | DESCRIPTION                                                                                            |

| 25  | IPROPI | I/O     | Driver load current analog feedback. For details, refer to IPROPI in the Device Configuration section. |

| 26  | nFAULT | OD      | Fault indication to the controller. For details, refer to nFAULT in the Device Configuration section.  |

| 27  | SDO    | PP      | SPI - Serial Data Output. Data is updated at the rising edge of SCLK.                                  |

| 28  | SDI    | I       | SPI - Serial Data Input. Data is captured at the falling edge of SCLK.                                 |

(1) I = input, O = output, I/O = input/output, G = ground, P = power, OD = open-drain output, PP = push-pull output

## 6.2.2 VQFN-HR (14) package

Figure 6-3. DRV8143S-Q1 SPI(S) variant in VQFN-HR (14) package

Table 6-3. Pin Functions

| P   | IN     | TYPE (1) | DESCRIPTION                                                                                                                          |

|-----|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME   | IIFE ( / | DESCRIPTION                                                                                                                          |

| 1   | nFAULT | OD       | Fault indication to the controller. For details, refer to nFAULT in the Device Configuration section.                                |

| 2   | IPROPI | I/O      | Driver load current analog feedback. For details, refer to IPROPI in the Device Configuration section.                               |

| 3   | nSLEEP | ļ        | Controller input pin for SLEEP. For details, see the Bridge Control section.                                                         |

| 4   | VM     | Р        | Power supply. This pin is the motor supply voltage. Bypass this pin to GND with a 0.1-μF ceramic capacitor and a bulk capacitor.     |

| 5,7 | OUT    | Р        | Half-bridge output. Connect this pin to the motor or load. Must combine with the other OUT pin to support device current capability. |

| 6   | GND    | G        | Ground pin                                                                                                                           |

| 8   | VCP    | Р        | Charge Pump pin for storage cap. Connect a 6.3V, 1µF capacitor to VM supply.                                                         |

# Table 6-3. Pin Functions (continued)

| P   | IN     | TYPE (1) | DESCRIPTION                                                                                          |

|-----|--------|----------|------------------------------------------------------------------------------------------------------|

| NO. | NAME   | I TPE (7 | DESCRIPTION                                                                                          |

| 9   | DRVOFF | I        | Controller input pin for bridge Hi-Z. For details, see the Bridge Control section.                   |

| 10  | IN     | I        | Controller input pin for bridge operation. For details, see the Bridge Control section.              |

| 11  | nSCS   | ļ        | SPI - Chip Select. An active low on this pin enables the serial interface communication.             |

| 12  | SCLK   | ļ        | SPI - Serial Clock input.                                                                            |

| 13  | SDI    | I        | SPI - Serial Data Input. Data is captured at the falling edge of SCLK. Also VIO logic level for SDO. |

| 14  | SDO    | PP       | SPI - Serial Data Output. Data is updated at the rising edge of SCLK.                                |

<sup>(1)</sup> I = input, O = output, I/O = input/output, G = ground, P = power, OD = open-drain output, PP = push-pull output

# 7 Specifications

# 7.1 Absolute Maximum Ratings

Over operating temperature range (unless otherwise noted)(1)

|                                                        |                      | MIN                   | MAX                    | UNIT |

|--------------------------------------------------------|----------------------|-----------------------|------------------------|------|

| Power supply pin voltage                               | VM                   | -0.3 <sup>(3)</sup>   | 40                     | V    |

| Power supply transient voltage ramp                    | VM                   |                       | 2                      | V/µs |

| Charge pump pin voltage                                | VCP                  | V <sub>VM</sub> – 0.3 | V <sub>VM</sub> + 7    | V    |

| Output pin voltage                                     | OUT                  | -0.9                  | V <sub>VM</sub> + 0.9  | V    |

| Output pin current                                     | OUT                  | Internally            | limited <sup>(2)</sup> | Α    |

| Driver disable pin voltage                             | DRVOFF               | -0.3                  | 40                     | V    |

| Logic I/O voltage                                      | IN, nFAULT           | -0.3                  | 5.75                   | V    |

| HW variant - Configuration pins voltage                | ITRIP, SR, DIAG      | -0.3                  | 5.75                   | V    |

| Analog feedback pin voltage                            | IPROPI               | -0.3                  | 5.75                   | V    |

| Sleep pin voltage (Not applicable for SPI (P) variant) | nSLEEP               | -0.3                  | 40                     | V    |

| SPI I/O voltage - SPI variant                          | SDI, SDO, nSCS, SCLK | -0.3                  | 5.75                   | V    |

| SPI (P) variant - Logic supply                         | VDD                  | -0.3                  | 5.75                   | V    |

| SPI (P) variant - Logic supply transient voltage ramp  | VDD                  |                       | 5                      | V/µs |

| Ambient temperature, T <sub>A</sub>                    |                      | -40                   | 125                    | °C   |

| Junction temperature, T <sub>J</sub>                   |                      | -40                   | 150                    | °C   |

| Storage temperature, T <sub>stg</sub>                  |                      | -65                   | 150                    | °C   |

- (1) Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) Limited by the over current and over temperature protection functions of the device

- (3) With external component support, short duration violation of this limit can be tolerated during ISO 7637 transient pulse testing

## 7.2 ESD Ratings

|                    |           |                                                         |                | VALUE | UNIT     |

|--------------------|-----------|---------------------------------------------------------|----------------|-------|----------|

|                    |           | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup> | VM, OUT, GND   | ±4000 |          |

| Hectrostatic       |           | HBM ESD Classification Level 2                          | All other pins | ±2000 |          |

| V <sub>(ESD)</sub> | discharge | Charged device model (CDM), per AEC Q100-011            | Corner pins    | ±750  | <b>v</b> |

|                    |           |                                                         | Other pins     | ±500  |          |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

# 7.3 Recommended Operating Conditions

over operating temperature range (unless otherwise noted)

|                      |                                        |                            | MIN      | MAX                       | UNIT |

|----------------------|----------------------------------------|----------------------------|----------|---------------------------|------|

| V <sub>VM</sub>      | Power supply voltage                   | VM                         | 4.5      | 35 <sup>(1)</sup>         | V    |

| $V_{VDD}$            | SPI (P) variant - Logic supply voltage | VDD                        | 4.5      | 5.5                       | V    |

| V <sub>VCP</sub>     | Charge pump pin voltage                | VCP                        | $V_{VM}$ | V <sub>VM</sub> +5.5      | V    |

| V <sub>LOGIC</sub>   | Logic pin voltage                      | IN, nSLEEP, DRVOFF, nFAULT | 0        | 5.5                       | V    |

| f <sub>PWM</sub>     | PWM frequency                          | IN                         | 0        | 125                       | KHz  |

| V <sub>CONFIG</sub>  | HW variant - Configuration pin voltage | ITRIP, SR, DIAG            | 0        | 5.5                       | V    |

| V <sub>IPROPI</sub>  | Analog feedback voltage                | IPROPI                     | 0        | 5.5                       | V    |

| V <sub>SPI_IOS</sub> | SPI (S) variant - SPI pin voltage      | SDI, SDO, nSCS, SCLK       | 0        | V <sub>nSLEEP</sub> + 0.5 | V    |

| _                    | SPI (P) variant - SPI pin voltage      | SDI, SDO, nSCS, SCLK       | 0        | V <sub>VDD</sub> + 0.5    | V    |

| T <sub>A</sub>       | Operating ambient temperature          |                            | -40      | 125                       | °C   |

| TJ                   | Operating junction temperature         |                            | -40      | 150                       | °C   |

<sup>(1)</sup> The over current protection function does not support short on OUT to VM or GND above 28 V for short inductance < 1  $\mu$ H.

#### 7.4 Thermal Information

Refer Transient thermal impedance table for application related use case.

|                       | THERMAL METRIC(1)                            | HVSSOP package | VQFN-HR package | UNIT |

|-----------------------|----------------------------------------------|----------------|-----------------|------|

| R <sub>0JA</sub>      | Junction-to-ambient thermal resistance       | 31.0           | 48.4            | °C/W |

| R <sub>θJC(top)</sub> | Junction-to-case(top) thermal resistance     | 29.1           | 22.3            | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 9.3            | 8.1             | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 1.4            | 0.5             | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 9.3            | 7.9             | °C/W |

| R <sub>θJC(bot)</sub> | Junction-to-case(bottom) thermal resistance  | 1.3            | N/A             | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 7.5 Electrical Characteristics

4.5 V (falling) ≤  $V_{VM}$  ≤ 35 V, -40°C ≤  $T_J$  ≤ 150°C (unless otherwise noted) For SPI (P) variant only: 4.5 V ≤  $V_{VDD}$  ≤ 5.5 V (unless otherwise noted)

## 7.5.1 Power Supply & Initialization

Refer wake up transient waveforms

|                     | PARAMETER                                 | TEST CONDITIONS                                                                              | MIN | TYP | MAX | UNIT |

|---------------------|-------------------------------------------|----------------------------------------------------------------------------------------------|-----|-----|-----|------|

| V <sub>VM_REV</sub> | Supply pin voltage during reverse current | I <sub>VM</sub> = - 5 A, device in unpowered state                                           |     | 1.4 |     | V    |

| have                | VM current in SLEEP state                 | $V_{VM}$ = 13.5 V, $V_{nSLEEP}$ = 0 V or $V_{VDD}$ < $POR_{VDD\_FALL}$ , $T_A$ = 25°C        |     | 1   |     | μА   |

| I <sub>VMQ</sub>    |                                           | $V_{VM}$ = 13.5 V, $V_{nSLEEP}$ = 0 V or $V_{VDD}$ < POR <sub>VDD_FALL</sub> , $T_A$ = 125°C |     |     | 5.8 | μА   |

| I <sub>VMS</sub>    | VM current in STANDBY state               | V <sub>VM</sub> = 13.5 V                                                                     |     | 3   | 5   | mA   |

| I <sub>VDD</sub>    | VDD current in ACTIVE state               | SPI (P) variant                                                                              |     |     | 10  | mA   |

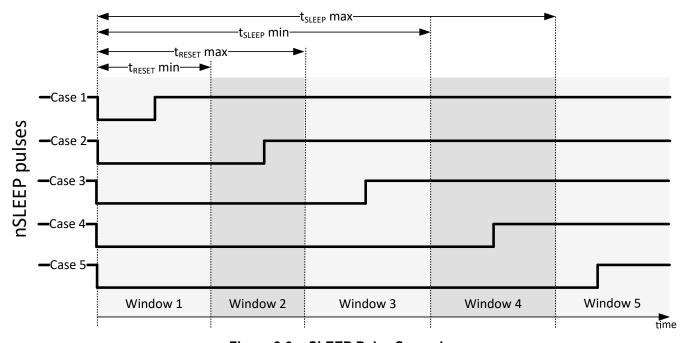

| t <sub>RESET</sub>  | RESET pulse filter time                   | Reset signal on nSLEEP pin for HW (H) variant                                                | 5   |     | 20  | μs   |

| t <sub>SLEEP</sub>  | SLEEP command filter time                 | Sleep signal on nSLEEP pin for HW (H) variant                                                | 40  |     | 120 | μs   |

|                        | PARAMETER                                                                                                    | TEST CONDITIONS                                                                                                                      | MIN | TYP                | MAX | UNIT |

|------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----|--------------------|-----|------|

| t <sub>SLEEP_SPI</sub> | SLEEP command filter time                                                                                    | Sleep signal on nSLEEP pin for SPI (S) variant                                                                                       | 5   |                    | 20  | μs   |

| t <sub>WAKEUP</sub>    | Wake-up command filter time                                                                                  | Wake-up signal on nSLEEP pin for HW (H) and SPI (S) variants                                                                         |     | 10                 |     | μs   |

| t <sub>СОМ</sub>       | Time for communication to be available after wake-up or power-up through VM or VDD supply pin                | Wake-up signal on nSLEEP pin or power cycle - V <sub>VM</sub> > VM <sub>POR_RISE</sub> or V <sub>VDD</sub> > VDD <sub>POR_RISE</sub> |     |                    | 400 | μs   |

| t <sub>READY</sub>     | Time for driver ready to be driven after wake-up through nSLEEP pin or power-up through VM or VDD supply pin | Wake-up signal on nSLEEP pin or power cycle - $V_{VM} > VM_{POR\_RISE}$ or $V_{VDD} > VDD_{POR\_RISE}$ , 1 $\mu F$ cap on VCP pin    |     |                    | 3.5 | ms   |

| V <sub>VCP</sub>       | Charge pump regulator voltage                                                                                | V <sub>VM</sub> > 7 V                                                                                                                |     | V <sub>VM</sub> +5 |     | V    |

| f <sub>VCP</sub>       | Average Charge pump switching frequency                                                                      |                                                                                                                                      |     | 20                 |     | MHz  |

# 7.5.2 Logic I/Os

|                         | PARAMETER                                                              | TEST CONDITIONS             | MIN  | TYP | MAX  | UNIT |

|-------------------------|------------------------------------------------------------------------|-----------------------------|------|-----|------|------|

| V <sub>IL_nSLEEP</sub>  | Input logic low voltage                                                | nSLEEP pin                  |      |     | 0.65 | V    |

| V <sub>IH_nSLEEP</sub>  | Input logic high voltage                                               | nSLEEP pin                  | 1.55 |     |      | V    |

| V <sub>IHYS_nSLEE</sub> | Input hysteresis                                                       | nSLEEP pin                  |      | 200 |      | mV   |

| V <sub>IL</sub>         | Input logic low voltage                                                | DRVOFF, IN pins             |      |     | 0.7  | V    |

| V <sub>IH</sub>         | Input logic high voltage                                               | DRVOFF, IN pins             | 1.5  |     |      | V    |

| V <sub>IHYS</sub>       | Input hysteresis                                                       | DRVOFF, IN pins             |      | 100 |      | mV   |

| R <sub>PD_nSLEEP</sub>  | Internal pull-down resistance on nSLEEP to GND                         | Measured at min VIL level   | 100  |     | 400  | ΚΩ   |

| R <sub>PU</sub>         | Internal pull-up resistance to VDD (reverse current blocked) on DRVOFF | Measured at min VIH level   | 200  |     | 550  | ΚΩ   |

| R <sub>PD</sub>         | Internal pull-down resistance to GND on IN                             | Measured at max VIL level   | 200  |     | 500  | ΚΩ   |

| I <sub>nFAULT_PD</sub>  | Sink current to GND on nFAULT pin when asserted low                    | V <sub>nFAULT</sub> = 0.3 V | 5    |     |      | mA   |

# 7.5.3 SPI I/Os

|                      | PARAMETER                                                            | TEST CONDITIONS                                                            | MIN | TYP | MAX | UNIT |

|----------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------|-----|-----|-----|------|

| R <sub>PU_nSCS</sub> | Internal pull-up resistance to VDD (reverse current blocked) on nSCS | Measured at min VIH level                                                  | 200 |     | 500 | ΚΩ   |

| R <sub>PD_SPI</sub>  | Internal pull-down resistance to GND on SDI, SCLK                    | Measured at max VIL level                                                  | 150 |     | 500 | ΚΩ   |

| V <sub>IL</sub>      | Input logic low voltage                                              | SDI, SCLK, nSCS pins                                                       |     |     | 0.7 | V    |

| V <sub>IH</sub>      | Input logic high voltage                                             | SDI, SCLK, nSCS pins                                                       | 1.5 |     |     | V    |

| V <sub>IHYS</sub>    | Input hysteresis                                                     | SDI, SCLK, nSCS pins                                                       |     | 100 |     | mV   |

| V <sub>OL_SDO</sub>  | Output logic low voltage                                             | 0.5 mA sink into SDO                                                       |     |     | 0.4 | V    |

|                      | Output logic high voltage for SPI (S)                                | 0.5 mA source from SDO, V <sub>nSLEEP</sub> = 5 V, V <sub>VM</sub> > 7 V   | 4.1 |     |     | V    |

| V <sub>OH_SDO</sub>  | variant                                                              | 0.5 mA source from SDO, $V_{\text{nSLEEP}}$ = 3.3 V, $V_{\text{VM}}$ > 5 V | 2.7 |     |     | V    |

|                      | Output logic high voltage for SPI (P) variant                        | 0.5 mA source from SDO, V <sub>VDD</sub> = 5 V                             | 4.5 |     |     | V    |

|            | PARAMETER                               | TEST CONDITIONS                                                          | MIN | TYP | MAX | UNIT |

|------------|-----------------------------------------|--------------------------------------------------------------------------|-----|-----|-----|------|

| V          | Output logic high voltage at no load on | No current from SDO, $V_{nSLEEP} = 5 \text{ V}$ , $V_{VM} > 7 \text{ V}$ |     |     | 5.5 | V    |

| VOH_SDO_NL | SDO, valid only for SPI (S) variant     | No current from SDO, $V_{\text{nSLEEP}}$ = 3.3 V, $V_{\text{VM}}$ > 5 V  |     |     | 3.8 | V    |

# 7.5.4 Configuration Pins - HW Variant Only

|                      | PARAMETER    | TEST CONDITIONS                   | MIN  | TYP | MAX  | UNIT |

|----------------------|--------------|-----------------------------------|------|-----|------|------|

|                      | 6 lev        | el setting for ITRIP, SR and DIAG |      |     |      |      |

| R <sub>LVL1OF6</sub> | Level 1 of 6 | Connect to GND                    |      |     | 10   | Ω    |

| R <sub>LVL2OF6</sub> | Level 2 of 6 | +/- 10% resistor to GND           | 7.4  | 8.2 | 9    | ΚΩ   |

| R <sub>LVL3OF6</sub> | Level 3 of 6 | +/- 10% resistor to GND           | 19.8 | 22  | 24.2 | ΚΩ   |

| R <sub>LVL4OF6</sub> | Level 4 of 6 | +/- 10% resistor to GND           | 42.3 | 47  | 51.7 | ΚΩ   |

| R <sub>LVL5OF6</sub> | Level 5 of 6 | +/- 10% resistor to GND           | 90   | 100 | 110  | ΚΩ   |

| R <sub>LVL6OF6</sub> | Level 6 of 6 | Hi-Z (no connect)                 | 250  |     |      | ΚΩ   |

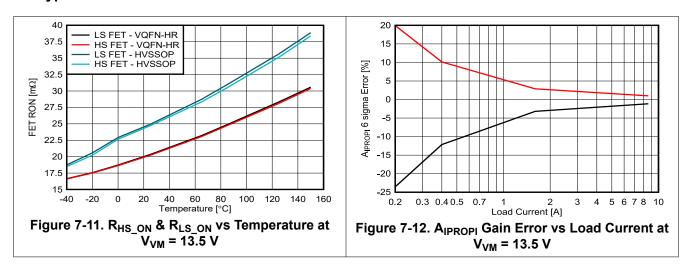

#### 7.5.5 Power FET Parameters

Measured at  $V_{VM}$  = 13.5 V

|                    | PARAMETER                                                                       | TEST CONDITIONS                                | MIN | TYP  | MAX  | UNIT |

|--------------------|---------------------------------------------------------------------------------|------------------------------------------------|-----|------|------|------|

|                    | High-side FET on resistance, HVSSOP                                             | I <sub>OUT</sub> = 6 A, T <sub>J</sub> = 25°C  |     | 24.5 |      | mΩ   |

| Ь                  | package                                                                         | I <sub>OUT</sub> = 6 A, T <sub>J</sub> = 150°C |     |      | 46.6 | mΩ   |

| R <sub>HS_ON</sub> | High-side FET on resistance, VQFN-HR                                            | I <sub>OUT</sub> = 6 A, T <sub>J</sub> = 25°C  |     | 21   |      | mΩ   |

|                    | package                                                                         | I <sub>OUT</sub> = 6 A, T <sub>J</sub> = 150°C |     |      | 39.9 | mΩ   |

|                    | Low-side FET on resistance, HVSSOP                                              | I <sub>OUT</sub> = 6 A, T <sub>J</sub> = 25°C  |     | 24.5 |      | mΩ   |

| D                  | package                                                                         | I <sub>OUT</sub> = 6 A, T <sub>J</sub> = 150°C |     |      | 46.6 | mΩ   |

| R <sub>LS_ON</sub> | Low-side FET on resistance, VQFN-HR                                             | I <sub>OUT</sub> = 6 A, T <sub>J</sub> = 25°C  |     | 21   |      | mΩ   |

|                    | package                                                                         | I <sub>OUT</sub> = 6 A, T <sub>J</sub> = 150°C |     |      | 39.9 | mΩ   |

| V <sub>SD</sub>    | Low-side & High-side FET source-drain voltage when body diode is forward biased | I <sub>OUT</sub> = +/- 6 A(both directions)    | 0.4 | 0.9  | 1.5  | V    |

| R <sub>Hi-Z</sub>  | OUT resistance to GND in SLEEP or STANDBY state                                 | V <sub>OUTx</sub> = V <sub>VM</sub> = 13.5 V   | 1.4 |      | 64   | ΚΩ   |

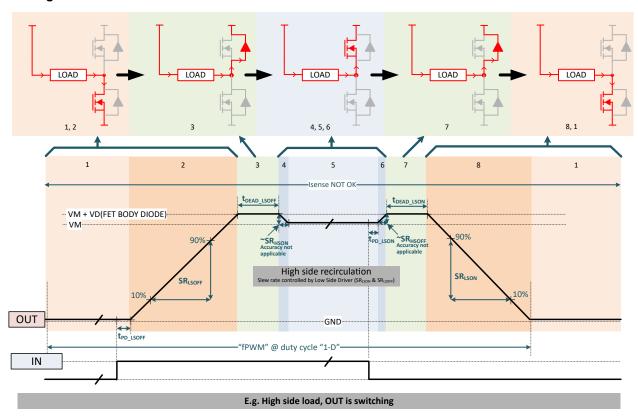

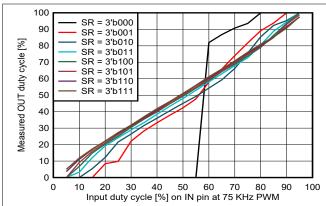

# 7.5.6 Switching Parameters with High-Side Recirculation

Load = 1.5mH / 4.7 Ohm,  $V_{VM}$  = 13.5 V, refer high-side recirculation waveform

|                     | PARAMETER                           | TEST CONDITIONS        | MIN | TYP  | MAX | UNIT |

|---------------------|-------------------------------------|------------------------|-----|------|-----|------|

|                     |                                     | SR = 3'b000 or LVL2    |     | 1.7  |     | V/µs |

|                     |                                     | SR = 3'b001 (SPI only) |     | 4.8  |     | V/µs |

|                     |                                     | SR = 3'b010 (SPI only) |     | 8.1  |     | V/µs |

| CD.                 | Output voltage rise time, 10% - 90% | SR = 3'b011 or LVL3    |     | 14   |     | V/µs |

| SR <sub>LSOFF</sub> |                                     | SR = 3'b100 or LVL4    |     | 19.9 |     | V/µs |

|                     |                                     | SR = 3'b101 or LVL1    |     | 25.7 |     | V/µs |

|                     |                                     | SR = 3'b110 or LVL6    |     | 36.4 |     | V/µs |

|                     |                                     | SR = 3'b111 or LVL5    |     | 45.8 |     | V/µs |

|                         | PARAMETER                                       | TEST CONDITIONS                     | MIN | TYP  | MAX | UNIT |

|-------------------------|-------------------------------------------------|-------------------------------------|-----|------|-----|------|

|                         |                                                 | SR = 3'b000 or LVL2                 |     | 1.2  |     | μs   |

|                         |                                                 | SR = 3'b001 (SPI only)              |     | 0.9  |     | μs   |

|                         | Propagation time during output voltage rise     | SR = 3'b010 (SPI only)              |     | 0.8  |     | μs   |

| t <sub>PD_LSOFF</sub>   |                                                 | SR = 3'b011 or LVL3                 |     | 0.7  |     | μs   |

|                         |                                                 | SR = 3'b100 & 3'b101 or LVL4 & LVL1 |     | 0.5  |     | μs   |

|                         |                                                 | SR = 3'b110 & 3'b111 or LVL6 & LVL5 |     | 0.4  |     | μs   |

| t <sub>DEAD_LSOFF</sub> | Dead time during output voltage rise            | All SRs                             |     | 0.9  |     | μs   |

|                         |                                                 | SR = 3'b000 or LVL2                 |     | 1.7  |     | V/µs |

|                         |                                                 | SR = 3'b001 (SPI only)              |     | 4.8  |     | V/µs |

|                         | Output voltage fall time, 90% - 10%             | SR = 3'b010 (SPI only)              |     | 8.1  |     | V/µs |

| CD                      |                                                 | SR = 3'b011 or LVL3                 |     | 14   |     | V/µs |

| SR <sub>LSON</sub>      |                                                 | SR = 3'b100 or LVL4                 |     | 19.9 |     | V/µs |

|                         |                                                 | SR = 3'b101 or LVL1                 |     | 25.7 |     | V/µs |

|                         |                                                 | SR = 3'b110 or LVL6                 |     | 36.4 |     | V/µs |

|                         |                                                 | SR = 3'b111 or LVL5                 |     | 45.8 |     | V/µs |

|                         |                                                 | SR = 3'b000 or LVL2                 |     | 1.5  |     | μs   |

|                         |                                                 | SR = 3'b001 (SPI only)              |     | 0.9  |     | μs   |

|                         |                                                 | SR = 3'b010 (SPI only)              |     | 0.6  |     | μs   |

| t <sub>PD_LSON</sub>    | Propagation time during output voltage fall     | SR = 3'b011 or LVL3                 |     | 0.5  |     | μs   |

|                         | Tun                                             | SR = 3'b100 or LVL4                 |     | 0.4  |     | μs   |

|                         |                                                 | SR = 3'b101 or LVL1                 |     | 0.35 |     | μs   |

|                         |                                                 | SR = 3'b110 & 3'b111 or LVL6 & LVL5 |     | 0.3  |     | μs   |

|                         |                                                 | SR = 3'b000 or LVL2                 |     | 2.2  |     | μs   |

| t <sub>DEAD_</sub> LSON |                                                 | SR = 3'b001 (SPI only)              |     | 1    |     | μs   |

|                         | Dead time during output voltage fall            | SR = 3'b010 (SPI only)              |     | 1    |     | μs   |

|                         |                                                 | SR = 3'b011 or LVL3                 |     | 0.7  |     | μs   |

|                         |                                                 | All other SRs                       |     | 0.6  |     | μs   |

| Match <sub>SRLS</sub>   | Output voltage rise and fall slew rate matching | All SRs                             | -20 |      | +20 | %    |

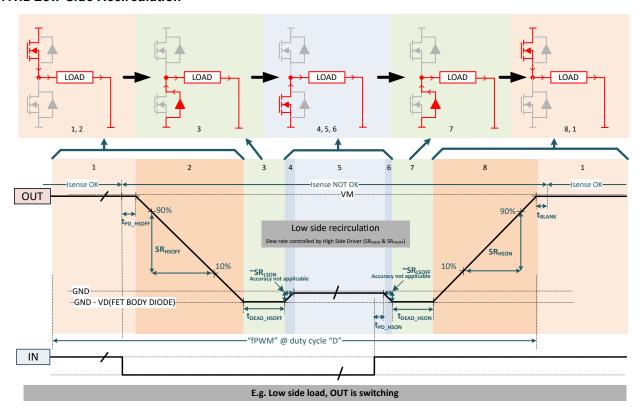

# 7.5.7 Switching Parameters with Low-Side Recirculation

Load = 1.5 mH / 4.7 Ohm,  $V_{VM}$  = 13.5 V, refer low-side recirculation waveform

|                         | PARAMETER                                    | TEST CONDITIONS                  | MIN | TYP  | MAX | UNIT |

|-------------------------|----------------------------------------------|----------------------------------|-----|------|-----|------|

|                         |                                              | SR = 3'b000 or LVL2              |     | 1.8  |     | V/µs |

|                         |                                              | SR = 3'b001 (SPI only)           |     | 5.7  |     | V/µs |

|                         |                                              | SR = 3'b010 (SPI only)           |     | 3.1  |     | V/µs |

| CD                      | Output valtage ries times 400/ 000/          | SR = 3'b011 or LVL3              |     | 8.7  |     | V/µs |

| SR <sub>HSON</sub>      | Output voltage rise time, 10% - 90%          | SR = 3'b100 or LVL4              |     | 14.4 |     | V/µs |

|                         |                                              | SR = 3'b101 or LVL1              |     | 20.1 |     | V/µs |

|                         |                                              | SR = 3'b110 or LVL6              |     | 30.7 |     | V/µs |

|                         |                                              | SR = 3'b111 or LVL5              |     | 40.3 |     | V/µs |

|                         |                                              | SR = 3'b000 or LVL2              |     | 3.2  |     | μs   |

| t <sub>PD_HSON</sub>    |                                              | SR = 3'b001 (SPI only)           |     | 1.7  |     | μs   |

|                         | Propagation time during output voltage rise  | SR = 3'b010 (SPI only)           |     | 1.2  |     | μs   |

|                         |                                              | SR = 3'b011 or LVL3              |     | 1    |     | μs   |

|                         |                                              | All other SRs                    |     | 0.9  |     | μs   |

|                         |                                              | SR = 3'b000 or LVL2              |     | 2.4  |     | μs   |

| _                       | Dood time during a system to the manifest    | SR = 3'b001 (SPI only)           |     | 5.1  |     | μs   |

| t <sub>DEAD_HSON</sub>  | Dead time during output voltage rise         | SR = 3'b010 (SPI only)           |     | 1.2  |     | μs   |

|                         |                                              | All other SRs                    |     | 0.5  |     | μs   |

|                         |                                              | SR = 3'b000 or LVL2              |     | 2.5  |     | V/µs |

|                         |                                              | SR = 3'b001 (SPI only)           |     | 5.7  |     | V/µs |

|                         |                                              | SR = 3'b010 (SPI only)           |     | 8.6  |     | V/µs |

| CD                      | Outrout valte as fall times 000/ 400/        | SR = 3'b011 or LVL3              |     | 14.1 |     | V/µs |

| SR <sub>HSOFF</sub>     | Output voltage fall time, 90% - 10%          | SR = 3'b100 or LVL4              |     | 19.7 |     | V/µs |

|                         |                                              | SR = 3'b101 or LVL1              |     | 25.1 |     | V/µs |

|                         |                                              | SR = 3'b110 or LVL6              |     | 35   |     | V/µs |

|                         |                                              | SR = 3'b111 or LVL5              |     | 43.6 |     | V/µs |

| t <sub>PD_HSOFF</sub>   | Propagation time during output voltage fall  | All SRs                          |     | 0.25 |     | μs   |

| t <sub>DEAD_HSOFF</sub> | Dead time during output voltage fall         | All SRs                          |     | 0.3  |     | μs   |

|                         | Current regulation blanking time after       | SR = 3'b000 or LVL2              |     | 10.8 |     | μs   |

| t <sub>BLANK</sub>      | OUT slewing for current sense output to      | SR = 3'b001 or 3'b010 (SPI only) |     | 3.5  |     | μs   |

|                         | settle (Valid for only for LS recirculation) | All other SRs                    |     | 2.5  |     | μs   |

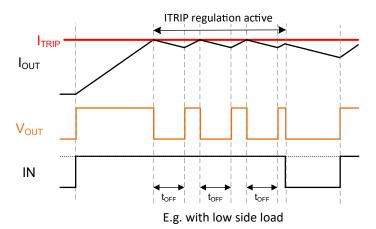

# 7.5.8 IPROPI & ITRIP Regulation

|                          | PARAMETER                                                                       | TEST CONDITIONS                        | MIN  | TYP  | MAX  | UNIT |

|--------------------------|---------------------------------------------------------------------------------|----------------------------------------|------|------|------|------|

| ^                        | Current scaling factor, HVSSOP package                                          |                                        |      | 3040 |      | A/A  |

| A <sub>IPROPI</sub>      | Current scaling factor, VQFN-HR package                                         |                                        |      | 3050 |      | A/A  |

|                          | Current scaling factor                                                          | 1.6 A < I <sub>OUT</sub> < 8.6 A       | -5   |      | +5   | %    |

| A <sub>I_ERR</sub>       |                                                                                 | 0.4 A < I <sub>OUT</sub> ≤ 1.6 A       | -20  |      | +20  | %    |

|                          |                                                                                 | 0.2 A < I <sub>OUT</sub> ≤ 0.4 A       | -50  |      | +50  | %    |

| Offset <sub>IPROPI</sub> | Offset current on IPROPI at no load current                                     | I <sub>OUT</sub> = 0 A                 |      |      | 15   | μA   |

| BW <sub>IPROPI</sub>     | Bandwidth of the IPROPI internal sense circuit                                  | No external capacitor on IPROPI.       | 400  |      |      | KHz  |

| V <sub>IPROPI_LIM</sub>  | Internal clamping voltage on IPROPI                                             |                                        | 4.5  |      | 5.5  | V    |

|                          |                                                                                 | ITRIP = 3'b001 or LVL2                 | 1.06 | 1.18 | 1.3  | V    |

|                          |                                                                                 | ITRIP = 3'b010 (SPI only)              | 1.27 | 1.41 | 1.55 | V    |

|                          |                                                                                 | ITRIP = 3'b011 (SPI only)              | 1.49 | 1.65 | 1.82 | V    |

| V <sub>ITRIP_LVL</sub>   | Voltage limit on V <sub>IPROPI</sub> to trigger TOFF cycle for ITRIP regulation | ITRIP = 3'b100 or LVL3                 | 1.78 | 1.98 | 2.18 | V    |

|                          | oyolo lo iii logalaacii                                                         | ITRIP = 3'b101 or LVL4                 | 2.08 | 2.31 | 2.54 | V    |

|                          |                                                                                 | ITRIP = 3'b110 or LVL5                 | 2.38 | 2.64 | 2.9  | V    |

|                          |                                                                                 | ITRIP = 3'b111 or LVL6                 | 2.67 | 2.97 | 3.27 | V    |

|                          |                                                                                 | TOFF = 2'b00 (SPI only)                | 16   | 20   | 25   | μs   |

| t <sub>OFF</sub>         | ITRIP regulation - off time                                                     | TOFF = 2'b01 (SPI). Only choice for HW | 24   | 30   | 36   | μs   |

|                          |                                                                                 | TOFF = 2'b10 (SPI only)                | 33   | 40   | 48   | μs   |

|                          |                                                                                 | TOFF = 2'b11 (SPI only)                | 41   | 50   | 61   | μs   |

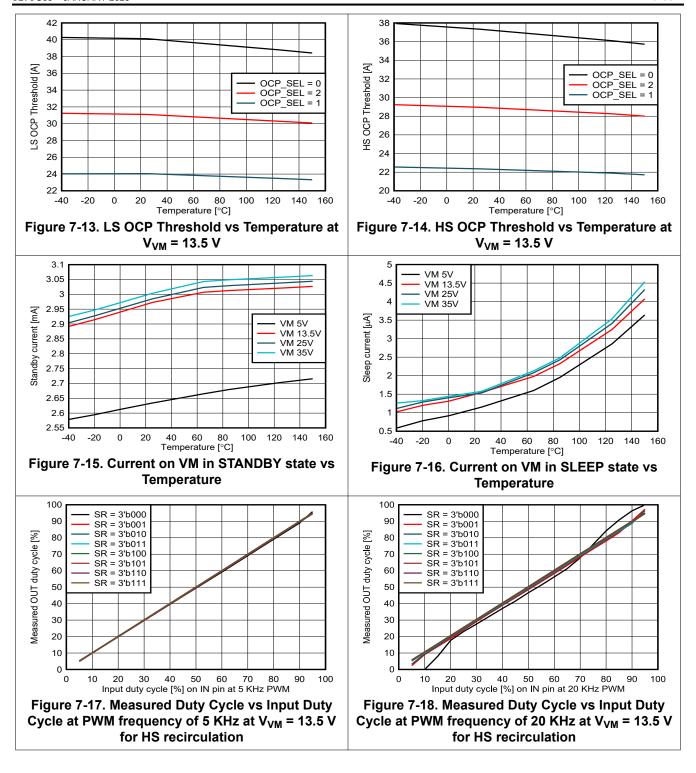

# 7.5.9 Over Current Protection (OCP)

|                     | PARAMETER                                | TEST CONDITIONS                            | MIN  | TYP | MAX | UNIT |

|---------------------|------------------------------------------|--------------------------------------------|------|-----|-----|------|

|                     | Over current protection threshold on the | OCP_SEL = 2'b00 (SPI), Only choice for HW  | 24   |     | 48  | Α    |

| I <sub>OCP_HS</sub> | high side                                | OCP_SEL = 2'b10 (SPI only)                 | 18   |     | 36  | Α    |

|                     |                                          | OCP_SEL = 2'b01 (SPI only)                 | 12   |     | 28  | Α    |

|                     | Over current protection threshold on the | OCP_SEL = 2'b00 (SPI), Only choice for HW  | 24   |     | 48  | Α    |

| I <sub>OCP_LS</sub> | low side                                 | OCP_SEL = 2'b10 (SPI only)                 | 18   |     | 36  | Α    |

|                     |                                          | OCP_SEL = 2'b01 (SPI only)                 | 12   |     | 28  | Α    |

|                     | Over current protection deglitch time    | TOCP_SEL = 2'b00 (SPI), Only choice for HW | 4.5  | 6   | 7.3 | μs   |

| t <sub>OCP</sub>    | Over current protection deglitch time    | TOCP_SEL = 2'b01 (SPI only)                | 2.2  | 3   | 4.1 | μs   |

| 23.                 | Over current protection deglitch time    | TOCP_SEL = 2'b10 (SPI only)                | 1.1  | 1.5 | 2.3 | μs   |

|                     | Over current protection deglitch time    | TOCP_SEL = 2'b11 (SPI only)                | 0.15 | 0.2 | 0.4 | μs   |

# 7.5.10 Over Temperature Protection (TSD)

| PARAMETER        |                                | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|------------------|--------------------------------|-----------------|-----|-----|-----|------|

| T <sub>TSD</sub> | Thermal shutdown temperature   |                 | 155 | 170 | 185 | °C   |

| T <sub>HYS</sub> | Thermal shutdown hysteresis    |                 |     | 30  |     | °C   |

| t <sub>TSD</sub> | Thermal shutdown deglitch time |                 | 10  | 12  | 19  | μs   |

Submit Document Feedback

# 7.5.11 Voltage Monitoring

|                             | PARAMETER                                         | TEST CONDITIONS                                   | MIN  | TYP                  | MAX | UNIT |

|-----------------------------|---------------------------------------------------|---------------------------------------------------|------|----------------------|-----|------|

|                             |                                                   | VMOV_SEL = 2'b00 (SPI), Only choice in HW variant | 33.6 |                      | 37  | V    |

| $V_{VMOV}$                  | VM over voltage threshold while rising            | VMOV_SEL = 2'b01 (SPI only)                       | 28   |                      | 31  | V    |

|                             |                                                   | VMOV_SEL = 2'b10 (SPI only)                       | 18   |                      | 21  | V    |

| V <sub>VMOV_HYS</sub>       | VM over voltage hysteresis                        |                                                   |      | 0.6                  |     | V    |

| t <sub>VMOV</sub>           | VM over voltage deglitch time                     |                                                   | 10   | 12                   | 19  | μs   |

| $V_{VMUV}$                  | VM under voltage threshold while falling          |                                                   | 4.2  |                      | 4.5 | V    |

| V <sub>VMUV_HYS</sub>       | VM under voltage hysteresis                       |                                                   |      | 200                  |     | mV   |

| t <sub>VMUV</sub>           | VM under voltage deglitch time                    |                                                   | 8    | 12                   | 19  | μs   |

| VM <sub>POR_FALL</sub>      | VM voltage at which device goes into POR          | Applicable for HW & SPI (S) variant               |      |                      | 3.6 | V    |

| VM <sub>POR_RISE</sub>      | VM voltage at which device comes out of POR       | Applicable for HW & SPI (S) variant               |      |                      | 3.9 | V    |

| VDD <sub>POR_FAL</sub><br>L | VDD voltage at which device goes into POR         | Applicable for SPI (P) variant                    |      |                      | 3.5 | V    |

| VDD <sub>POR_RIS</sub>      | VDD voltage at which device comes out of POR      | Applicable for SPI (P) variant                    |      |                      | 3.8 | V    |

| V <sub>CPUV</sub>           | Charge pump under-voltage threshold while falling |                                                   |      | V <sub>VM</sub> +2.5 |     | V    |

| t <sub>CPUV</sub>           | Charge pump deglitch time                         |                                                   | 10   | 12                   | 19  | μs   |

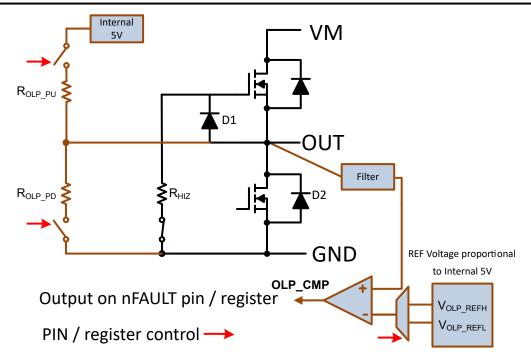

## 7.5.12 Load Monitoring

|                       | PARAMETER                                                                       | TEST CONDITIONS                                    | MIN | TYP  | MAX | UNIT |

|-----------------------|---------------------------------------------------------------------------------|----------------------------------------------------|-----|------|-----|------|

|                       |                                                                                 | Off-state diagnostics (OLP)                        |     |      |     |      |

| R <sub>S_GND</sub>    | Resistance on OUT to GND that will be detected as short                         |                                                    |     |      | 1   | ΚΩ   |

| R <sub>S_VM</sub>     | Resistance on OUT to VM that will be detected as short                          |                                                    |     |      | 1   | ΚΩ   |

| R <sub>OPEN_LS</sub>  | Resistance on OUT to GND that will be detected as open                          | Valid for low-side load                            | 2   |      |     | ΚΩ   |

| R <sub>OPEN_HS</sub>  | Resistance on OUT to VM that will be detected as open                           | Valid for high-side load, V <sub>VM</sub> = 13.5 V | 10  |      |     | ΚΩ   |

| V <sub>OLP_REFH</sub> | OLP Comparator Reference High                                                   |                                                    |     | 2.65 |     | V    |

| V <sub>OLP_REFL</sub> | OLP Comparator Reference Low                                                    |                                                    |     | 2    |     | V    |

| R <sub>OLP_PU</sub>   | Internal pull-up resistance on OUT to VDD during OLP                            | V <sub>OUTx</sub> = V <sub>OLP_REFH</sub> + 0.1V   |     | 1    |     | ΚΩ   |

| R <sub>OLP_PD</sub>   | Internal pull-down resistance on OUT to GND during OLP                          | V <sub>OUTx</sub> = V <sub>OLP_REFL</sub> - 0.1V   |     | 1    |     | ΚΩ   |

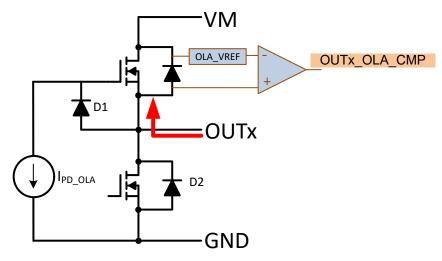

|                       | SPI varia                                                                       | nnt only - On-state diagnostics (OLA)              |     |      |     |      |

| I <sub>PD_OLA</sub>   | Internal sink current on OUT to GND during dead-time in high-side recirculation |                                                    | 0.1 |      | 10  | mA   |

| V <sub>OLA_REF</sub>  | Comparator Reference with respect to VM used for OLA                            |                                                    |     | 0.25 |     | V    |

# 7.5.13 Fault Retry Setting

Refer to retry setting waveform

|             | PARAMETER                   | TEST CONDITIONS             | MIN | TYP | MAX | UNIT |

|-------------|-----------------------------|-----------------------------|-----|-----|-----|------|

| $t_{RETRY}$ | Automatic driver retry time | Fault reaction set to RETRY | 4.1 | 5   | 6.1 | ms   |

| PARAMETER              |                                                                     | TEST CONDITIONS             | MIN | TYP | MAX | UNIT |

|------------------------|---------------------------------------------------------------------|-----------------------------|-----|-----|-----|------|

| t <sub>CLEAR</sub>     | Fault free operation time to auto-clear from over current event     | Fault reaction set to RETRY | 85  |     | 200 | μs   |

| t <sub>CLEAR_TSD</sub> | Fault free operation time to auto-clear from over temperature event | Fault reaction set to RETRY | 4.2 |     | 6.7 | ms   |

## 7.5.14 Transient Thermal Impedance & Current Capability

Information based on thermal simulations

Table 7-1. Transient Thermal Impedance (R<sub>0JA</sub>) and Current Capability - half-bridge

|                          |             |                                        | D Г°  | СЛАД(1) |                            |         |       | Currer | nt [A] <sup>(2)</sup>   |        |     |

|--------------------------|-------------|----------------------------------------|-------|---------|----------------------------|---------|-------|--------|-------------------------|--------|-----|

| PART NUMBER   PACKA   GE |             | R <sub>θJA</sub> [°C/W] <sup>(1)</sup> |       |         | without PWM <sup>(3)</sup> |         |       |        | with PWM <sup>(4)</sup> |        |     |

|                          |             | 0.1 sec                                | 1 sec | 10 sec  | DC                         | 0.1 sec | 1 sec | 10 sec | DC                      | 10 sec | DC  |

| DRV8143-Q1               | VQFN-<br>HR | 6.6                                    | 12.4  | 16.9    | 33.4                       | 15.7    | 11.5  | 9.8    | 7.0                     | 8.0    | 5.3 |

| DRV8143-Q1               | HVSSOP      | 5.0                                    | 9.8   | 14.7    | 31.7                       | 16.7    | 11.9  | 9.7    | 6.6                     | 8.2    | 5.2 |

- (1) Based on thermal simulations using 40 mm x 40 mm x 1.6 mm 4 layer PCB 2 oz Cu on top and bottom layers, 1 oz Cu on internal planes with 0.3 mm thermal via drill diameter, 0.025 mm Cu plating, 1 minimum mm via pitch.

- (2) Estimated transient current capability at 85 °C ambient temperature for junction temperature rise up to 150°C

- (3) Only conduction losses (I<sup>2</sup>R) considered

- Switching loss roughly estimated by the following equation:

$$P_{SW} = V_{VM} \times I_{Load} \times f_{PWM} \times V_{VM}/SR, \text{ where } V_{VM} = 13.5 \text{ V}, f_{PWM} = 20 \text{ KHz}, SR = 23 \text{ V/}\mu\text{s}$$

(1)

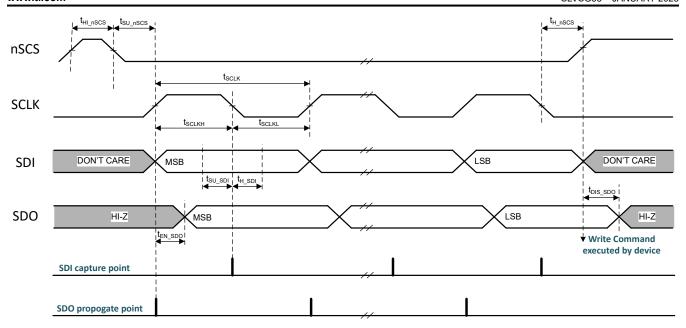

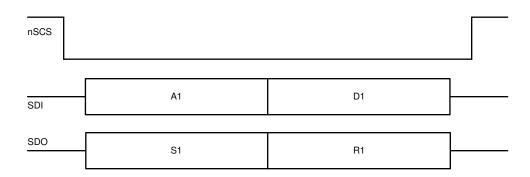

# 7.6 SPI Timing Requirements

|                      |                                       | MIN | TYP | MAX | UNIT |

|----------------------|---------------------------------------|-----|-----|-----|------|

| t <sub>SCLK</sub>    | SCLK minimum period <sup>(1)</sup>    | 100 |     |     | ns   |

| t <sub>SCLKH</sub>   | SCLK minimum high time                | 50  |     |     | ns   |

| t <sub>SCLKL</sub>   | SCLK minimum low time                 | 50  |     |     | ns   |

| t <sub>HI_nSCS</sub> | nSCS minimum high time                | 300 |     |     | ns   |

| t <sub>SU_nSCS</sub> | nSCS input setup time                 | 25  |     |     | ns   |

| t <sub>H_nSCS</sub>  | nSCS input hold time                  | 25  |     |     | ns   |

| t <sub>SU_SDI</sub>  | SDI input data setup time             | 25  |     |     | ns   |

| t <sub>H_SDI</sub>   | SDI input data hold time              | 25  |     |     | ns   |

| t <sub>EN_SDO</sub>  | SDO enable delay time <sup>(1)</sup>  |     |     | 35  | ns   |

| t <sub>DIS_SDO</sub> | SDO disable delay time <sup>(1)</sup> |     |     | 100 | ns   |

(1) SPI (S) variant: SDO delay times are valid only with SDO external load of 5 pF. With a 20 pF load on SDO, there is an additional delay on SDO, which results in a 25% increase in SCLK minimum time, limiting the SCLK to a maximum of 8 MHz. There is NO such limitation for the SPI (P) variant.

Submit Document Feedback

Figure 7-1. SPI Peripheral-Mode Timing Definition

# 7.7 Switching Waveforms

This section illustrates the switching transients for an inductive load due to external PWM or internal ITRIP regulation.

# 7.7.1.1 High-Side Recirculation

Figure 7-2. Output Switching Transients with High-Side Recirculation

#### 7.7.1.2 Low-Side Recirculation

Figure 7-3. Output Switching Transients with Low-Side Recirculation

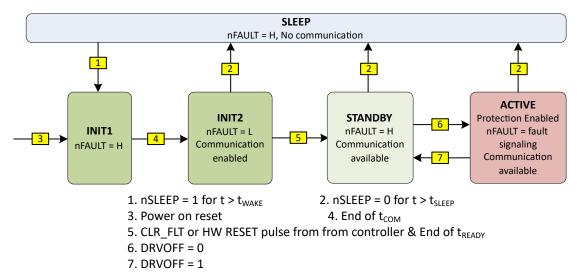

## 7.7.2 Wake-up Transients

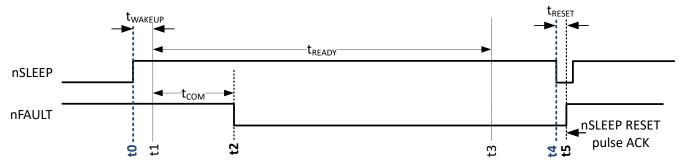

#### 7.7.2.1 HW Variant

Figure 7-4. Wake-up from SLEEP State to STANDBY State Transition for HW Variant

Hand shake between controller and device during wake-up as follows:

- t0: Controller nSLEEP asserted high to initiate device wake-up

- t1: Device internal state Wake-up command registered by device (end of Sleep state)

- t2: Device nFAULT asserted low to acknowledge wake-up and indicate device ready for communication

- t3: Device internal state Initialization complete

- t4 (any time after t2): Controller Issue nSLEEP reset pulse to acknowledge device wake-up

- t5: Device nFAULT de-asserted as an acknowledgment of nSLEEP reset pulse. Device in STANDBY state

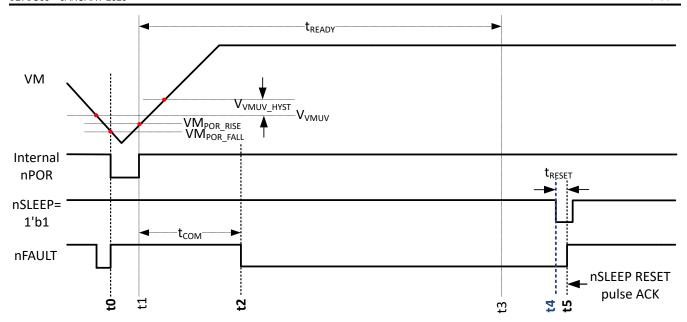

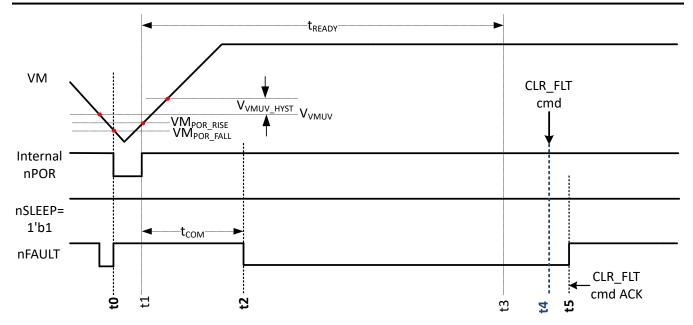

Figure 7-5. Power-up to STANDBY State Transition for HW Variant

Hand shake between controller and device during power-up as follows:

- t0: Device internal state POR asserted based on under voltage of internal LDO (VM dependent)

- t1: Device internal state POR de-asserted based on recovery of internal LDO voltage

- t2: Device nFAULT asserted low to acknowledge wake-up and indicate device ready for communication

- t3: Device internal state Initialization complete

- t4 (any time after t2): Controller Issue nSLEEP reset pulse to acknowledge device power-up

- t5: Device nFAULT de-asserted as an acknowledgment of nSLEEP reset pulse. Device in STANDBY state

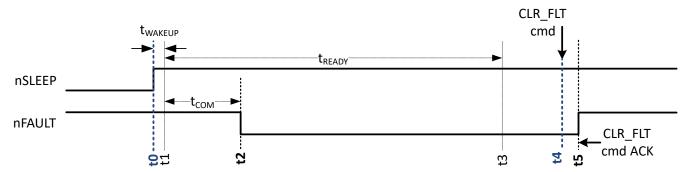

#### 7.7.2.2 SPI Variant

Figure 7-6. Wake-up from SLEEP State to STANDBY State Transition for SPI (S) Variant

Hand shake between controller and device during a wake-up transient as follows:

- t0: Controller nSLEEP asserted high to initiate device wake-up

- t1: Device internal state Wake-up command registered by device (end of Sleep state)

- t2: Device nFAULT asserted low to acknowledge wake-up and indicate device ready for communication

- t3: Device internal state Initialization complete

- t4 (Any time after t2): Controller Issue CLR FLT command through SPI to acknowledge device wake-up

- t5: Device nFAULT de-asserted as an acknowledgment of nSLEEP reset pulse. Device in STANDBY state

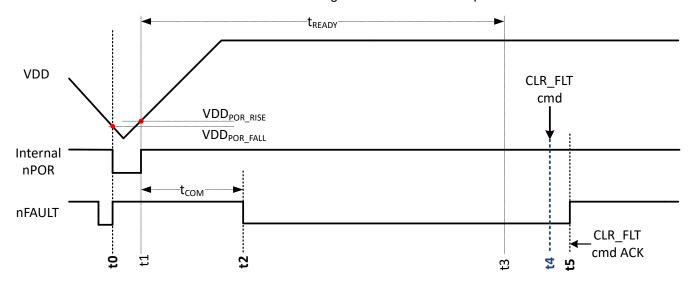

Figure 7-7. Power-up to STANDBY State Transition for SPI (S) Variant

Hand shake between controller and device during power-up as follows:

- t0: Device internal state POR asserted based on under voltage of internal LDO (VM dependent)

- t1: Device internal state POR de-asserted based on recovery of internal LDO voltage

- t2: Device nFAULT asserted low to acknowledge wake-up and indicate device ready for communication

- t3: Device internal state Initialization complete

- t4 (Any time after t2): Controller Issue CLR\_FLT command through SPI to acknowledge device power-up

- t5: Device nFAULT de-asserted as an acknowledgment of nSLEEP reset pulse. Device in STANDBY state

Figure 7-8. Power-up to STANDBY State Transition for SPI (P) Variant

Hand shake between controller and device during power-up as follows:

- t0: Device internal state POR asserted based on under voltage on VDD (external supply)

- t1: Device internal state POR de-asserted based on recovery of voltage on VDD (external supply)

- t2: Device nFAULT asserted low to acknowledge wake-up and indicate device ready for communication

- t3: Device internal state Initialization complete

- t4 (Any time after t2): Controller Issue CLR FLT command through SPI to acknowledge device power-up

- t5: Device nFAULT de-asserted as an acknowledgment of nSLEEP reset pulse. Device in STANDBY state

#### 7.7.3 Fault Reaction Transients

#### 7.7.3.1 Retry setting

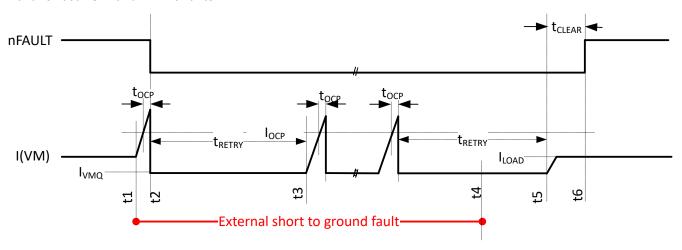

Valid for both SPI and HW variants

Figure 7-9. Fault reaction with RETRY setting (shown for OCP occurrence on high-side when OUT is shorted to ground)

Short occurrence and recovery scenario with RETRY setting:

- t1: An external short occurs.

- t2: OCP (Over Current Protection) fault confirmed after t<sub>OCP</sub>, output disabled, nFAULT asserted low to indicate fault.

- t3: Device automatically attempts retry (auto retry) after t<sub>RETRY</sub>. Each time output is briefly turned on to confirm short occurrence and then immediately disabled after t<sub>OCP</sub>. nFAULT remains asserted low through out. Cycle repeats till driver is disabled by the user or external short is removed, as illustrated further. Note that, in case of a TSD (Thermal Shut Down) event, automatic retry time depends on the cool off based on thermal hysteresis.

- t4: The external short is removed.

- t5: Device attempts auto retry. But this time, no fault occurs and device continues to keep the output enabled.

- t6: After a fault free operation for a period of t<sub>CLEAR</sub> is confirmed, nFAULT is de-asserted.

- SPI variant only Fault status remains latched till a CLR\_FLT command is issued.

Note that, in the event of an output short to ground causing the high-side OCP fault detection, IPROPI pin will continue to be pulled up to  $V_{IPROPI\_LIM}$  voltage to indicate this type of short, while the output is disabled. This is especially useful for the HW (H) variant to differentiate the indication of a short to ground fault from the other faults.

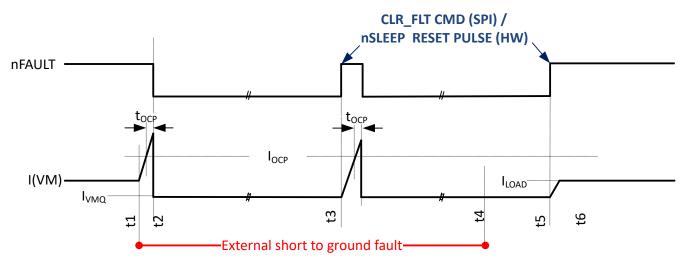

#### 7.7.3.2 Latch setting

Valid for both SPI and HW variants

Figure 7-10. Fault reaction with Latch setting (shown for OCP occurrence on high-side when OUT is shorted to ground)

Short occurrence and recovery scenario with LATCH setting:

- t1: An external short occurs.

- t2: OCP (Over Current Protection) fault confirmed after t<sub>OCP</sub>, output disabled, nFAULT asserted low to indicate fault.

- t3: A CLR FLT command (SPI variant) or nSLEEP RESET Pulse (HW variant) issued by controller. nFAULT is de-asserted and output is enabled. OCP fault is detected again and output is disabled with nFAULT asserted low.

- t4: The external short is removed.

- t5: A CLR FLT command (SPI variant) or nSLEEP RESET Pulse (HW variant) issued by controller. nFAULT is de-asserted and output is enabled. Normal operation resumes.

- SPI variant only Fault status remains latched till a CLR FLT command is issued.

Note that, in the event of an output short to ground causing the high-side OCP fault detection, IPROPI pin will continue to be pulled up to V<sub>IPROPI LIM</sub> voltage to indicate this type of short, while the output is disabled. This is especially useful for the HW (H) variant to differentiate the indication of a short to ground fault from the other

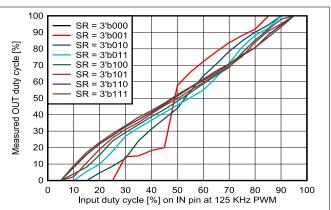

## 7.8 Typical Characteristics

Figure 7-19. Measured Duty Cycle vs Input Duty Cycle at PWM frequency of 75 KHz at  $V_{VM}$  = 13.5 V for HS recirculation

Figure 7-20. Measured Duty Cycle vs Input Duty Cycle at PWM frequency of 125 KHz at  $V_{VM}$  = 13.5 V for HS recirculation

# 8 Detailed Description

#### 8.1 Overview

The DRV814x-Q1 family of devices are brushed DC motor drivers that operate from 4.5 to 35-V supporting a wide range of output load currents for various types of motors and loads. The devices integrate a charge pump regulator to support efficient high-side N-channel MOSFETs with 100% duty cycle operation. The devices operate from a single power supply input (VM) which can be directly connected to a battery or DC voltage supply. The devices also provide a low power mode to minimize current draw during system inactivity.

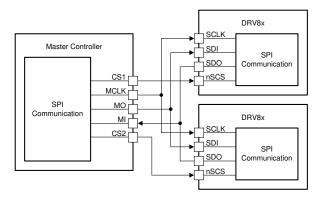

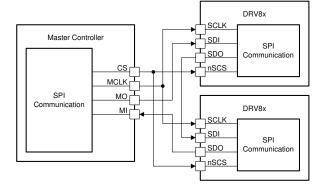

The devices are available in two interface variants -

- 1. HW variant Hardwired interface variant is available for easy device configuration. Due to the limited number of available pins in the device, this variant offers fewer configuration and fault reporting capability compared to the SPI variant.

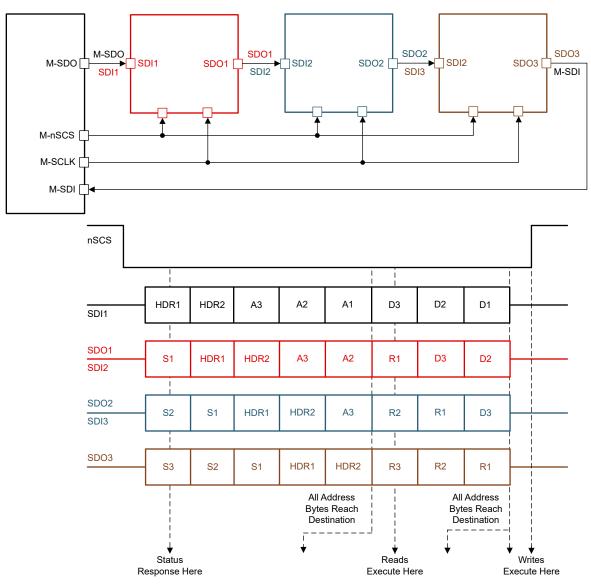

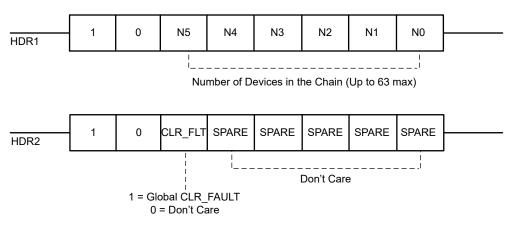

- 2. SPI variant A standard 4-wire serial peripheral interface (SPI) with daisy chain capability allows flexible device configuration and detailed fault reporting to an external controller. The feature differences of the SPI and HW variants can be found in the device comparison section. The SPI interface is available in two device variant choices, as stated below: