# 82586 IEEE 802.3 ETHERNET LAN COPROCESSOR

- Performs Complete CSMA/CD Medium Access Control Functions Independently of CPU

- High-Level Command Interface

- Supports Established and Emerging LAN Standards

- IEEE 802.3/Ethernet (10BASE5)

- IEEE 802.3/Cheapernet (10BASE2)

- IEEE 802.3/StarLAN (1BASE5)

- Proposed 10BASE-T

- -- Proposed 10BASE-F

- Proprietary CSMA/CD Networks up to 10 Mb/s

- On-Chip Memory Management

- Automatic Buffer Chaining

- Buffer Reclaim After Receipt of Bad Frames

- Save Bad Frames, Optionally

- Interfaces to 8-Bit and 16-Bit Microprocessors

- 48-Pin DIP and 68-Pin PLCC

(see "Intel Packaging" Document, Order Number: 231369)

- Supports Minimum Component Systems

- Shared Bus Configuration

- Interface to 80186 and 80188 Microprocessors Without Glue

- **■** Supports High-Performance Systems

- Bus Master, with On-Chip DMA

- --- 5-MB/s Bus Bandwidth

- Compatible with Dual-Port Memory

- Back-to-Back Frame Reception at 10 Mb/s

- Network Management

- CRC Error Tally

- Alignment Error Tally

- Location of Cable Faults

- Self-Test Diagnostics

- Internal Loopback

- External Loopback

- Internal Register Dump

- Backoff Timer Check

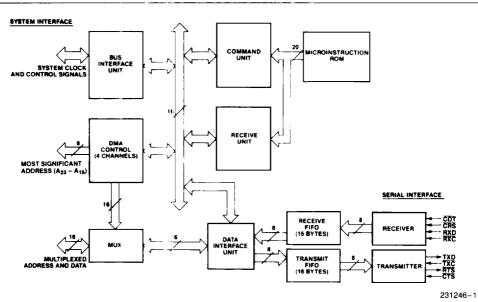

Figure 1. 82586 Functional Block Diagram

<sup>\*</sup>IBM is a trademark of International Business Machines Corporation.

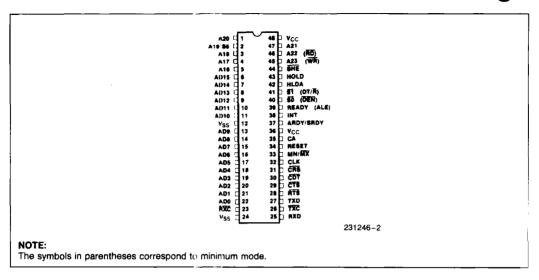

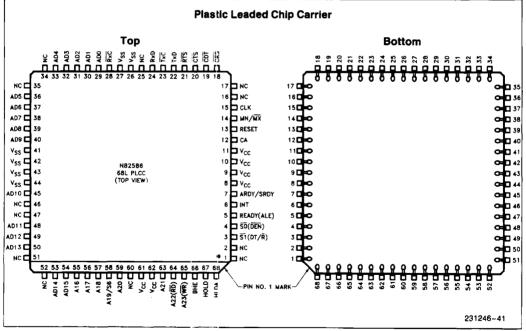

Figure 2. 82586 Pinout Diagrams

The 82586 is an intelligent, high-performance Local Area Network coprocessor, implementing the CSMA/CD access method (Carrier Sense Multiple Access with Collision Detection). It performs all time-critical functions independently of the host processor, which maximizes performance and network efficiency.

The 82586 performs the full set of IEEE 802.3 CSMA/CD Medium Access Control and channel interface functions including: framing, preamble generation and stripping, source address generation, destination address checking, CRC generation and checking, short frame detection. Any data rate up to 10 Mb/s can be used.

The 82586 features a powerful host system interface. It automatically manages memory structures with command chaining and bidirectional data chaining. An on-chip DMA controller manages four channels transparently to the user. Buffers containing errored or collided frames can be automatically recovered. The 82586 can be configured for 8-bit or 16-bit data path, with maximum burst transfer rate of 2 or 4 MB/s respectively. Memory address space is 16 megabytes maximum.

The 82586 provides two independent 16-byte FIFOs, one for receiving and one for transmitting. The threshold for block transfer to/from memory is programmable, enabling the user to optimize bus overhead for a given worst case bus latency.

The 82586 provides a rich set of diagnostic and network management functions including: internal and external loopbacks, exception condition tallies, channel activity indicators, optional capture of all frames regardless of destination address, optional capture of errored or collided frames, and time domain reflectometry for locating faults in the cable.

The 82586 can be used in either baseband or broadband networks. It can be configured for maximum network efficiency (minimum contention overhead) for any length network operating at any data rate up to 10 Mb/s. The controller supports address field lengths of 1, 2, 3, 4, 5, or 6 bytes. It can be configured for either the IEEE 802.3/Ethernet or HDLC method of frame delineation. Both 16-bit and 32-bit CRCs are supported.

The 82586 is fabricated in Intel's reliable HMOS II 5-V technology and is available in a 48-pin DIP or 68-pin PLCC package.

Table 1. 82586 Pin Description

| Symbol                            | 48 Pin DIP<br>Pin No. | 68 Pin PLCC<br>Pin No.    | Type<br>Level | Name and Function                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------------------|-----------------------|---------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub> , V <sub>CC</sub> | 48, 36                | 8, 9, 10, 1°,<br>61, 62   |               | System Power: + 5V Power Supply.                                                                                                                                                                                                                                                                                                                                  |

| V <sub>SS</sub> , V <sub>SS</sub> | 12, 24                | 26, 27, 41,<br>42, 43, 44 | 100           | System Ground.                                                                                                                                                                                                                                                                                                                                                    |

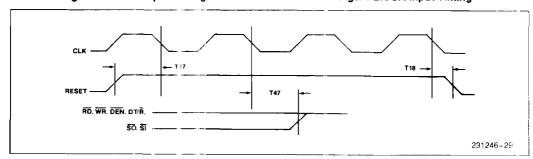

| RESET                             | 34                    | 13                        | I<br>TTL      | RESET is an active HIGH internally synchronized signal, causing the 82586 to terminate present activity immediately. The signal must be HIGH for at least four clock cycles. The 82586 will execute RESET within ten system clock cycles starting from RESET HIGH. When RESET returns LOW, the 82586 waits for the first CA to begin the initialization sequence. |

| TxD                               | 27                    | 22                        | 0<br>TTL      | Transmitted Serial Data output signal. This signal is HIGH when not transmitting.                                                                                                                                                                                                                                                                                 |

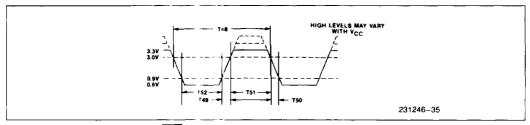

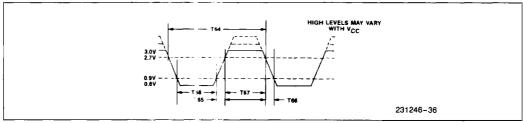

| TxC                               | 26                    | 23                        | *             | Transmit Data Clock. This signal provides timing information to the internal serial logic, depending upon the mode of data transfer. For NRZ mode of operation, data is transferred to the TxD pin on the HIGH to LOW clock transition.                                                                                                                           |

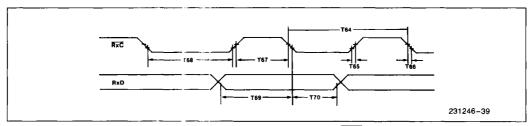

| RxD                               | 25                    | 24                        | TTL           | Received Data Input Signal.                                                                                                                                                                                                                                                                                                                                       |

| RxC                               | 23                    | 28                        | i<br>*        | Received Data Clock. This signal provides timing information to the internal shifting logic depending upon the mode of data transfer. For NRZ data, the state of the RxD pin is sampled on the HIGH to LOW clock transition.                                                                                                                                      |

<sup>\*</sup>See D.C. Characteristics.

Table 1, 82586 Pin Description (Continued)

| Table 1. 82586 Pin Description (Continued) |                       |                                                |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------|-----------------------|------------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                                     | 48 Pin DIP<br>Pin No. | 68 Pin PLCC<br>Pin No.                         | Type<br>Level | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

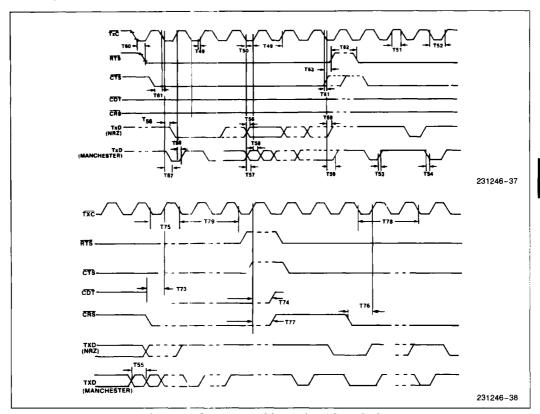

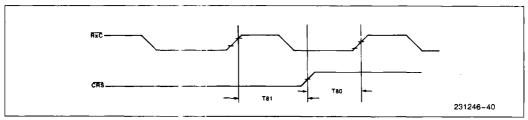

| RTS                                        | 28                    | 21                                             | 0<br>TTL      | Request To Send signal. When LOW, notifies an external interface that the 82586 has data to transmit. It is forced HIGH after a Reset and while the Transmit Serial Unit is not sending data.                                                                                                                                                                                                                                                                           |

| CTS                                        | 29                    | 20                                             | I<br>TTL      | Active LOW Clear To Send input enables the 82586 transmitter to actually send data. It is normally used as an interface handshake to RTS. This signal going inactive stops transmission. It is internally synchronized. If CTS goes inactive, meeting the setup time to TxC negative edge, transmission is stopped and RTS goes inactive within, at most, two TxC cycles.                                                                                               |

| CRS                                        | 31                    | 18                                             | I<br>TTL      | Active LOW Carrier Sense input used to notify the 82586 that there is traffic on the serial link. It is used only if the 82586 is configured for external Carrier Sense. When so configured, external circuitry is required for detecting serial link traffic. It is internally synchronized. To be accepted, the signal must stay active for at least two serial clock cycles.                                                                                         |

| CDT                                        | 30                    | 19                                             | TTL           | Active LOW Collision Detect input is used to notify the 82586 that a collision has occurred. It is used only if the 82586 is configured for external Collision Detect. External circuitry is required for detecting the collision. It is internally synchronized. To be accepted, the signal must stay active for at least two serial clock cycles. During transmission, the 82586 is able to recognize a collision one bit time after preamble transmission has begun. |

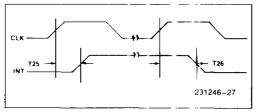

| INT                                        | 38                    | 6                                              | ()<br>  T L   | Active HIGH Interrupt request signal.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

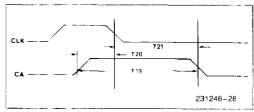

| CLK                                        | 32                    | 15                                             | MOS           | The system clock input from the 80186 or another symmetrical clock generator.                                                                                                                                                                                                                                                                                                                                                                                           |

| MN/MX                                      | 33                    | 14                                             | TTL           | When HIGH, MN/MX selects RD, WR, ALE DEN, DT/R (Minimum Mode). When LOW, MN/MX selects A22, A23, READY, S0, S1 (Maximum Mode). Note: This pin should be static during 82586 operation.                                                                                                                                                                                                                                                                                  |

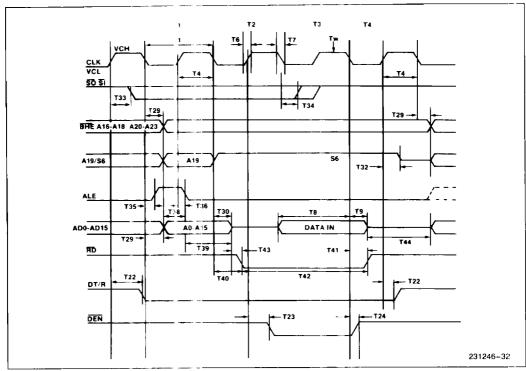

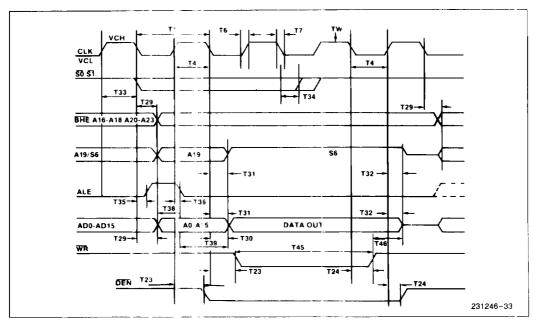

| AD0-AD15                                   | 6–11,<br>13–22        | 29-33, 36-<br>40, 45, 48,<br>49, 50, 53,<br>54 | I/O<br>TTL    | These lines form the time multiplexed memory address (t1) and data (t2, t3, tW, t4) bus. When operating with an 8-bit bus, the high byte will output the address only during T1. AD0-AD15 are floated after a RESET or when the bus is not acquired.                                                                                                                                                                                                                    |

| A16-A18<br>A20-A23                         | 1, 3-5<br>45-47       | 55-57, 59,<br>63-65                            | O<br>TTL      | These lines constitute 7 out of 8 most significant address bits for memory operation. They switch during t1 and stay valid during the entire memory cycle. The lines are floated after RESET or when the bus is not acquired. Address lines A22 and A23 are not available for use in minimum mode.                                                                                                                                                                      |

| A19/S6                                     | 2                     | 58                                             | O<br>TTL      | During t1 it forms line 19 of the memory address. During t2 through t4 it is used as a status indicating that this is a Master peripheral cycle, and is HIGH. Its timing is identical to that of AD0-AD15 during write operation.                                                                                                                                                                                                                                       |

Table 1. 82586 Pin Description (Continued)

| Symbol    | 48 Pin DIP<br>Pin No. | 68 Pin PLCC<br>Pin No. | Type<br>Level | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------|-----------------------|------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

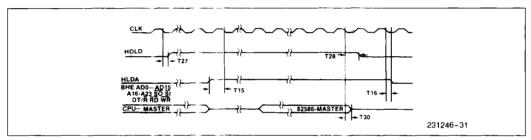

| HOLD      | 43                    | 67                     | O<br>TTL      | HOLD is an active HIGH signal used by the 82586 to request local bus mastership at the end of the current CPU bus transfer cycle, or at the end of the current DMA burst transfer cycle. In normal operation, HOLD goes inactive before HLDA. The 82586 can be forced off the bus by HLDA going inactive. In this case, HOLD goes inactive within four clock cycles in word mode and eight clock cycles in byte mode.                                                                                                                                                                               |

| HLDA      | 42                    | 68                     | I<br>TTL      | HLDA is an active HIGH Hold Acknowledge signal indicating that the CPU has received the HOLD request and that bus control has been relinquished to the 82586. It is internally synchronized. After HOLD is detected as LOW, the processor drives HLDA LOW. Note, CONNECTING V <sub>CC</sub> TO HLDA IS NOT ALLOWED because it will cause a deadlock. Users wanting to give permanent bus access to the 82586 should connect HLDA with HOLD.                                                                                                                                                         |

| CA        | 35                    | 12                     | i<br>TTL      | The CA pin is a Channel Attention input used by the CPU to initiate the 82586 execution of memory resident Command Blocks. The CA signal is synchronized internally. The signal must be HIGH for at least one system clock period. It is latched internally on HIGH to LOW edge and then detected by the 82586.                                                                                                                                                                                                                                                                                     |

| BHE       | 44                    | 66                     | 0<br>TTL      | The Bus High Enable signal (BHE) is used to enable data onto the most significant half of the data bus. Its timing is identical to that of A16–A23. With a 16-bit bus it is LOW and with an 8-bit bus it is HIGH. Note: after RESET, the 82586 is configured to 8-bit bus.                                                                                                                                                                                                                                                                                                                          |

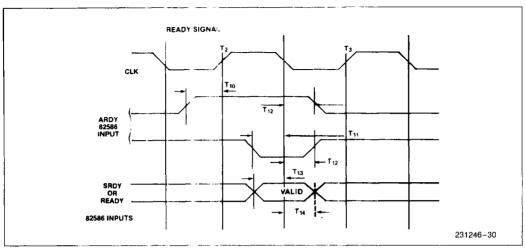

| READY     | 39                    | 5                      | I<br>TTL      | This active HIGH signal is the acknowledgement from the addressed memory that the transfer cycle can be completed. While LOW, it causes wait states to be inserted. This signal must be externally synchronized with the system clock. The Ready signal internal to the 82586 is a logical OR between READY and SRDY/ARDY.                                                                                                                                                                                                                                                                          |

| ARDY/SRDY | 37                    | 7                      | I<br>TTL      | This active HIGH signal performs the same function as READY. If it is programmed at configure time to SRDY, it is identical to READY. If it is programmed to ARDY, the positive edge of the Ready signal is internally synchronized. Note, the negative edge must still meet setup and hold time specifications, when in ARDY mode. The ARDY signal must be active for at least one system clock HIGH period for proper strobing. The Ready signal internal to the 82586 is a logical OR between READY (in Maximum Mode only) and SRDY/ARDY. Note that following RESET, this pin assumes ARDY mode. |

Table 1. 82586 Pin Description (Continued)

| Symbol | 48 Pin DIP<br>Pin No. | 68 Pin PLCC<br>Pin No. | Type<br>Level | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------|-----------------------|------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S0, S1 | 40,41                 | 4, 3                   | O<br>TTL      | Maximum mode only. These status pins define the type of DMA transfer during the current memory cycle. They are encoded as follows:  \$\overline{S1}\$ \$\overline{S0}\$  0                                                                                                                                                                                                                                                            |

| RD     | 46                    | 64                     | O<br>TTL      | Used in minimum mode only. The read strobe indicates that the 82586 is performing a memory read cycle. RD is active LOW during t2, t3 and tW of any read cycle. This signal is pulled HIGH and floated after a RESET and when the bus is not acquired.                                                                                                                                                                                |

| WR     | 45                    | 65                     | O<br>TTL      | Used in minimum mode only. The write strobe indicates that the 82586 is performing a write memory cycle. WR is active LOW during t2, t3 and tW of any write cycle. It is pulled HIGH and floats after RESET and when the bus is not acquired.                                                                                                                                                                                         |

| ALE    | 39                    | 5                      | O<br>TTL      | Used in minimum mode only. Address Latch Enable is provided by the 82586 to latch the address into the 8282/8283 address latch. It is a HIGH pulse, during t1 ('clock low') of any bus cycle. Note that ALE is never floated.                                                                                                                                                                                                         |

| DEN    | 40                    | 4                      | O<br>TTL      | Used in minimum mode only. Data ENable is provided as output enable for the 8286/8287 transceivers in a standalone (no 8288) system. DEN is active LOW during each memory access. For a read cycle, it is active from the middle of t2 until the beginning of t4. For a write cycle, it is active from the beginning of t2 until the middle of t4. It is pulled HIGH and floats after a system RESET or when the bus is not acquired. |

| DT/R   | 41                    | 3                      | C<br>TTL      | Used in minimum mode only. DT/R is used in non-8288 systems using an 8286/8287 data bus transceiver. It controls the direction of data flow through the Transceiver. Logically, DT/R is equivalent to \$\overline{ST}\$. It becomes valid in the t4 preceding a bus cycle and remains valid until the final t4 of the cycle. This signal is pulled HIGH and floated after a RESET or when the bus is not acquired.                    |

#### NOTE:

<sup>\*8288</sup> does not support 10 MHz operation.

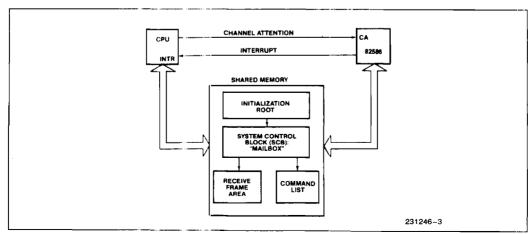

#### 82586/HOST CPU INTERACTION

Communication between the 82586 and the host is carried out via shared memory. The 82586's on-chip DMA capability allows autonomous transfer of data blocks (buffers, frames) and relieves the CPU of byte transfer overhead. The 82586 s optimized to interface the iAPX 186, but due to the small number of hardware signals between the 82586 and the CPU, the 82586 can operate easily with other processors. The 82586/host interaction is explained separately in terms of the logical interface and the hardware bus interface.

The 82586 consists of two independent units: Command Unit (CU) and Receive Unit (RU). The CU executes commands from shared memory. The RU handles all activities related to frame reception. The CU and RU enable the 82586 to engage in the two types of activities simultaneously: the CU may be fetching and executing commands out of memory, and the RU may be storing received frames in memory. CPU intervention is only required after the CU executes a sequence of commands or the RU stores a sequence of frames.

The only hardware signals that connect the CPU and the 82586 are INTERRUPT and CHANNEL ATTENTION (see Figure 3). Interrupt is used by the 82586 to draw the CPU's attention to a change in the contents of the SCB. Channel Attention is used by the CPU to draw the 82586's attention.

# 82586 SYSTEM MEMORY STRUCTURE

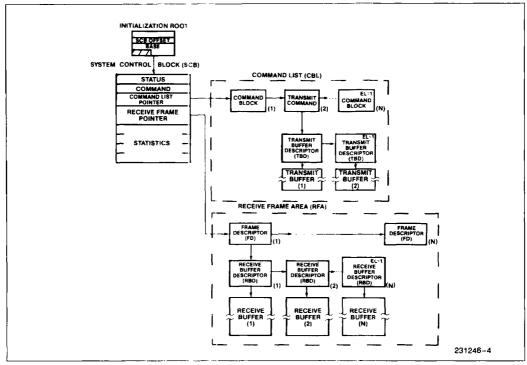

The Shared Memory structure consists of four parts: Initialization Root, System Control Block (SCB),

Command List, and Receive Frame Area (RFA) (see Figure 4).

The Initialization Root is at a predetermined location in the memory space, (0FFFFF6H), known to both the host CPU and the 82586. The root is accessed at initialization and points to the System Control Block.

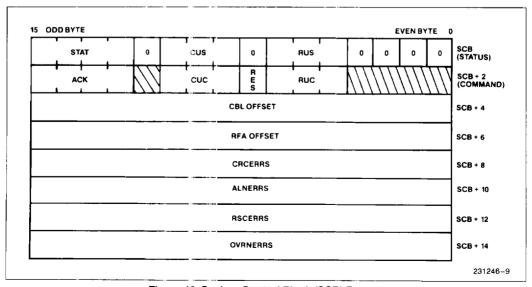

The System Control Block (SCB) functions as a bidirectional mail drop between the host CPU, CU and RU. It is the central element through which the CPU and the 82586 exchange control and status information. The SCB consists of two parts, the first of which entails instructions from the CPU to the 82586. These include: control of the CU and RU (START, ABORT, SUSPEND, RESUME), a pointer to the list of commands for the CU, a pointer to the receive frame area, and a set of Interrupt acknowledge bits. The second entails status information keyed by the 82586 to the CPU, including: state of the CU and RU (e.g. IDLE, ACTIVE READY, SUS-PENDED, NO RECEIVE RESOURCES), interrupts bits (command completed, frame received, CU not ready, RU not ready), and statistics (see Figure 4).

The Command List serves as a program for the CU. Individual commands are placed in memory units called a Command Block, or CB. CB's contain command specific parameters and command specific statuses. Specifically, these high level commands are called Action Commands (e.g. Transmit, Configure).

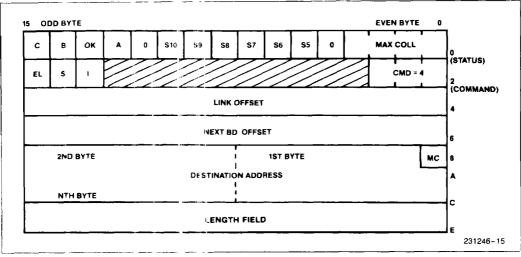

A specific command, Transmit, causes transmission of a frame by the 82586. The Transmit command block includes Destination Address, Length Field, and a pointer to a list of linked buffers that holds the frame to be constructed from several buffers scattered in memory. The Command Unit performs with-

Figure 3, 82586/Host CPU Interaction

Figure 4, 82586 Shared Memory Structure

out the CPU intervention, the DMA of each buffer and the prefetching of references to new buffers in parallel. The CPU is notified only after successful transmission or retransmission.

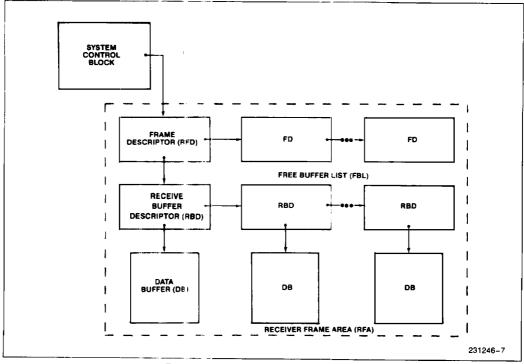

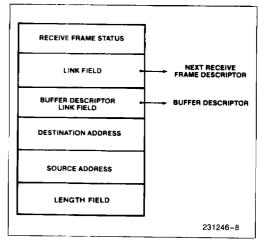

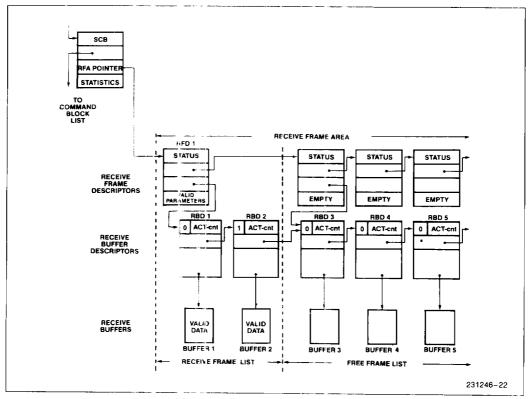

The Receive Frame Area is a list of Free Frame Descriptors (Descriptors not yet used) and a list of buffers prepared by the user. It is conceptually distinct from the Command List. Frames arrive without being solicited by the 82586. The 82586 must be prepared to receive them even if it is engaged in other activities and to store them in the Free Frame Area. The Receive Unit fills the buffers upon frame reception and reformats the Free Buffer List into received frame structures. The frame structure is virtually identical to the format of the frame to be transmitted. The first frame descriptor is referenced by SCB. A Frame Descriptor and the associated Buffer Descriptor wasted upon receiving a Bad Frame (CRC or Alignment errored, Receive DMA overrun errored, or Collision fragmented frame) are automatically reclaimed and returned to the Free Buffe. List, unless the chip is configured to Save Bad Frames

Receive buffer chaining (i.e. storing incoming frames in a linked list of buffers) improves memory utilization significantly. Without buffer chaining, the user must allocate consecutive blocks of the maximum frame size (1518 bytes in Ethernet) for each frame. Taking into account that a typical frame size may be about 100 bytes, this practice is very inefficient. With buffer chaining, the user can allocate small buffers and the 82586 uses only as many as needed.

In the past, the drawback of buffer chaining was the CPU processing overhead and the time involved in the buffer switching (especially at 10 Mb/s). The 82586 overcomes this drawback by performing buffer management on its own for both transmission and reception (completely transparent to the user).

The 82586 has a 22-bit memory address range in minimum mode and 24-bit memory address range in maximum mode. All memory structures, the System Control Block, Command List, Receive Descriptor List, and all buffer descriptors must reside within one 64K-byte memory segment. The Data Buffers can be located anywhere in the memory space.

#### TRANSMITTING FRAMES

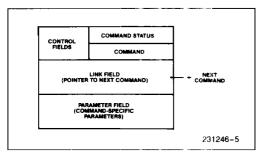

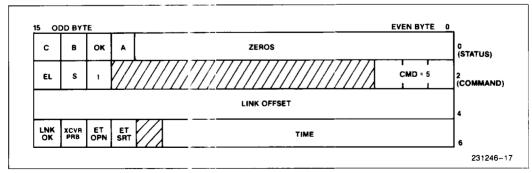

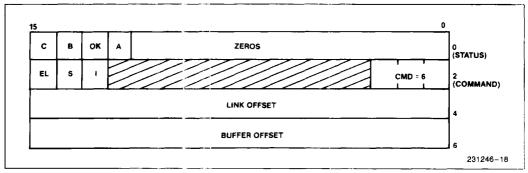

The 82586 executes high level action commands from the Command List in external memory. Action commands are fetched and executed in parallel with the host CPU's operation, thereby significantly improving system performance. The general action commands format is shown in Figure 5.

Figure 5. Action Command Format

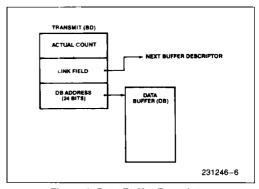

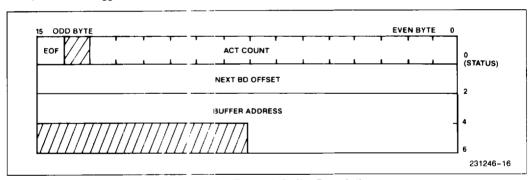

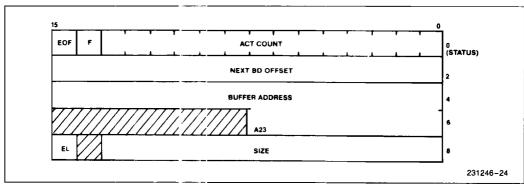

Message transmission is accomplished by using the Transmit command. A single Transmit command contains, as part of the command-specific parameters, the destination address and length field for the transmitted frame along with a pointer to a buffer area in memory containing the data portion of the frame. (See Figure 15.) The data field is contained in a memory data structure consisting of a Buffer Descriptor (BD) and Data Buffer (or a linked list of buffer descriptors and buffers) as shown in Figure 6. The BD contains a Link Field which points to the next BD on the list and a 24-bit address pointing to the Data Buffer itself. The length of the Data Buffer is specified by the Actual Count field of the BD.

Using the BD's and Data Buffers, multiple Data Buffers can be 'chained' together. Thus, a frame with a long Data Field can be transmitted using multiple (shorter) Data buffers chained together. This chaining technique allows the system designer to develop efficient buffer management policies.

The 82586 automatically generates the preamble (alternating 1's and 0's) and start frame delimiter, fetches the destination address and length field from the Transmit command, inserts its unique address as the source address, fetches the data field from

Figure 6. Data Buffer Descriptor and Data Buffer Structure

buffers pointed to by the Transmit command, and computes and appends the CRC at the end of the frame. See Figure 7.

The 82586 can be configured to generate either the Ethernet or HDLC start and end frame delimiters. In the Ethernet mode, the start frame delimiter is 10101011 and the end frame delimiter indicated by the lack of a signal after transmitting the last bit of the frame check sequence field. When in the HDLC mode, the 82586 will generate the 011111110 'flag' for the start and end frame delimiters and perform the standard 'bit stuffing/stripping'. In addition, the 82586 will optionally pad frames that are shorter than the specified minimum frame length by appending the appropriate number of flags to the end of the frame.

In the event of a collision (or collisions), the 82586 manages the entire jam, random wait and retry process, reinitializing DMA pointers without CPU intervention. Multiple frames can be sent by linking the appropriate number of Transmit commands together. This is particularly useful when transmitting a message that is larger than the maximum frame size (1518 bytes for Ethernet).

#### RECEIVING FRAMES

In order to minimize CPU overhead, the 82586 is designed to receive frames without CPU supervision. The host CPU first sets aside an adequate

| PREAMBLE | START<br>FRAME<br>DELIMITER | DEST<br>ADDR | SOURCE<br>ADDR | LENGTH<br>FIELD | DATA<br>FIELD | FRAME<br>CHECK<br>SEQUENCE | END<br>FRAME<br>DELIMITER |

|----------|-----------------------------|--------------|----------------|-----------------|---------------|----------------------------|---------------------------|

|----------|-----------------------------|--------------|----------------|-----------------|---------------|----------------------------|---------------------------|

Figure 7. Frame Format

Figure 8. Receive Frame Area Diagram

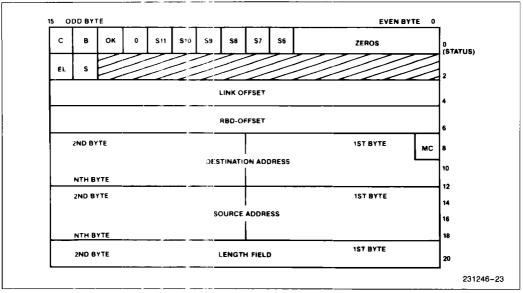

amount of receive buffer space and then enables the 82586's Receive Unit. Once enabled, the RU 'watches' for any of its frames which it automatically stores in the Receive Frame Area (RFA). The RFA consists of a Receive Descriptor List (RDL) and a list of free buffers called the Free Buffer List (FBL) as shown in Figure 8. The individual Receive Frame Descriptors that make up the RDL are used by the 82586 to store the destination and source address, length field and status of each frame that is received. (Figure 9.)

The 82586, once enabled, checks each passing frame for an address match. The 82586 will recognize its own unique address, one or more multicast addresses or the broadcast address. If a match occurs, it stores the destination and source address and length field in the next available RFD. It then begins filling the next free Data Buffer on the FBL (which is pointed to by the current FIFD) with the data portion of the incoming frame. As one DB is filled, the 82586 automatically fetches the next DB on the FBL until the entire frame is received. This buffer chaining technique is particularly memory efficient because it allows the system designer to set aside buffers that fit a frame size that may be much shorter than the maximum allowable frame

Figure 9. Receive Frame Descriptor

Once the entire frame is received without error, the 82586 performs the following housekeeping tasks:

Updates the Actual Count field of the last Buffer Descriptor used to hold the frame just received with the number of bytes stored in its associated Data Buffer.

- Fetches the address of the next free Receive Frame Descriptor.

- Writes the address of the next free Buffer Descriptor into the next free Receive Frame Descriptor.

- Posts a 'Frame Received' interrupt status bit in the SCB.

- Interrupts the CPU.

In the event of a frame error, such as a CRC error, the 82586 automatically reinitializes its DMA pointers and reclaims any data buffers containing the bad frame. As long as Receive Frame Descriptors and data buffers are available, the 82586 will continue to receive frames without further CPU help

# 82586 NETWORK MANAGEMENT AND DIAGNOSTIC FUNCTIONS

The behavior of data communication betworks is typically very complex due to their distributed and asynchronous nature. It is particularly difficult to pinpoint a failure when it occurs. The \$2586 was designed in anticipation of these problems and includes a set of features for improving reliability and testability.

The 82586 reports on the following events after each frame transmitted:

- Transmission successful

- Transmission unsuccessful; lost Carrier Sense.

- Transmission unsuccessful: lost Clear to-Send.

- Transmission unsuccessful: DMA underrun because the system bus did not keep ip with the transmission.

- Transmission unsuccessful; number of collisions exceeded the maximum allowed.

The 82586 checks each incoming frame and reports on the following errors, (if configured to "Save Bad Frame"):

- · CRC error: incorrect CRC in a well aligned frame.

- Alignment error: incorrect CRC is a misaligned frame.

- Frame too short: the frame is shorter than the configured value for minimum frame length.

- Overrun: the frame was not completely placed in memory because the system bus old not keep up with incoming data.

- Out of buffers: no memory resources to store the frame, so part of the frame was descarded.

# NETWORK PLANNING AND MAINTENANCE

To perform proper planning, operation, and maintenance of a communication network, the network management entity must accumulate information on network behavior. The 82586 provides a rich set of network-wide diagnostics that can serve as the basis for a network management entity.

Network Activity information is provided in the status of each frame transmitted. The activity indicators are:

- Number of collisions: number of collisions the 82586 experienced in attempting to transmit this frame.

- Deferred transmission: indicates if the 82586 had to defer to traffic on the link during the first transmission attempt.

Statistics registers are updated after each received frame that passes the address filtering, and is longer than the Minimum Frame Length configuration parameter.

- CRC errors: number of frames that experienced a CRC error and were properly aligned.

- Alignment errors: number of frames that experienced a CRC error and were misaligned.

- No-resources: number of correct frames lost due to lack of memory resources.

- Overrun errors: number of frame sequences lost due to DMA overrun.

The 82586 can be configured to Promiscuous Mode. In this mode it captures all frames transmitted on the Network without checking the Destination Address. This is useful in implementing a monitoring station to capture all frames for analysis.

The 82586 is capable of determining if there is a short or open circuit anywhere in the Network using the built in Time Domain Reflectometer (TDR) mechanism

#### STATION DIAGNOSTICS

The chip can be configured to External Loopback The transmitter to receiver interconnection can be placed anywhere between the 82586 and the link to locate faults, for example: the 82586 output pins, the Serial Interface Unit, the Transceiver cable, or in the Transceiver

The 82586 has a mechanism recognizing the transceiver 'heart beat' signal for verifying the correct operation of the Transceiver's collision detection circuitry.

#### 82586 SELF TESTING

The 82586 can be configured to Internal Loopback. It disconnects itself from the Serial Interface Unit, and any frame transmitted is received immediately. The 82586 connects the Transmit Data to the Receive Data signal and the Transmit Clock to the Receive Clock.

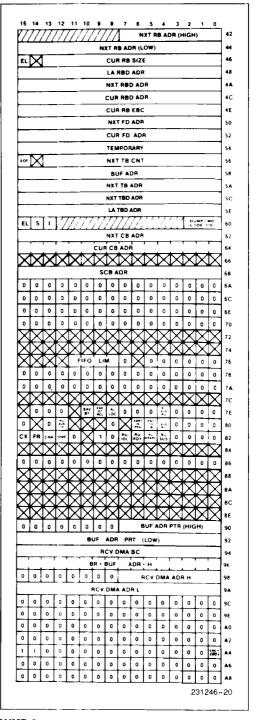

The Dump Command causes the chip to write over 100 bytes of its internal registers to memory.

The Diagnose command checks the exponential Backoff random number generator internal to the 82586

#### **CONTROLLING THE 82586**

The CPU controls operation of the 82586's Command Unit (CU) and Receive Unit (RU) of the 82586 via the System Control Block.

### THE COMMAND UNIT (CU)

The Command Unit is the logical unit that executes Action Commands from a list of commands very similar to a CPU program. A Command Block (CB) is associated with each Action Command.

The CU can be modeled as a logical machine that takes, at any given time, one of the following states:

- IDLE—CU is not executing a command and is not associated with a CB on the list. This is the initial state.

- SUSPENDED—CU is not executing a command but (different from IDLE) is associated with a CB on the list.

- ACTIVE—CU is currently executing an Action Command, and points to its CB.

The CPU may affect the CU operation in two ways: issuing a CU control Command or setting bits in the COMMAND word of the Action Command.

# THE RECEIVE UNIT (RU)

The Receive Unit is the logical unit that receives frames and stores them in memory.

The RU is modeled as a logical machine that takes, at any given time, one of the following states:

- IDLE—RU has no memory resources and is discarding incoming frames. This is the initial RU state.

- NO-RESOURCES—RU has no memory resources and is discarding incoming frames. This state differs from the IDLE state in that RU accumulates statistics on the number of frames it had to discard.

- SUSPENDED—RU has free memory resources to store incoming frames but discard them anyway.

Figure 10. System Control Block (SCB) Format

READY—RU has free memory resources and stores incoming frames.

The CPU may affect RU operation in three ways: issuing an RU Control Command, setting bits in Frame Descriptor, FD, COMMAND word of the frame currently being received, or setting EL bit of Buffer Descriptor, BD, of the buffer currently being filled.

#### SYSTEM CONTROL BLOCK (SCB)

The System Control Block is the communication mail-box between the 82586 and the host CPU. The SCB format is shown in Figure 10.

The host CPU issues Control Commands to the 82586 via the SCB. These commands may appear at any time during routine operation, as determined by the host CPU. After the requirec Control Command is setup, the CPU sends a CA signal to the 82586.

SCB is also used by the 82586 to return status information to the host CPU. After inserting the required status bits into SCB, the 82586 issues an Interrupt to the CPU.

The format is as follows:

**STATUS word:** Indicates the status of the 82586. This word is modified only by the 82586. Defined bits are:

| aio. |             |                                                                            |

|------|-------------|----------------------------------------------------------------------------|

| CX   | (Bit 15)    | A command in the CBL having its 'I' (interrupt) bit set has been executed. |

| FR   | (Bit 14)    | A frame has been received.                                                 |

| CNR  | (Bit 13)    | The Commar d Unit left the Active state.                                   |

| RNR  | (Bit 12)    | The Receive Unit left the                                                  |

|      | `           | Ready state.                                                               |

| CUS  | (Bits 8-10) | <ul> <li>(3 bits) this field contains</li> </ul>                           |

|      |             | the status of the Command Unit.                                            |

|      |             | Valid values are:                                                          |

|      |             |                                                                            |

|      |             |                                                                            |

|      |             | 1 — Suspendec                                                              |

|      |             | 2 — Active                                                                 |

|      |             | 3-7 — Not lised                                                            |

| RUS  | (Bits 4—6)  | <ul> <li>(3 bits) this field contains</li> </ul>                           |

|      |             | the status of the Receive                                                  |

| l    |             | Unit. Valid values are:                                                    |

|      |             | 0 — Idle                                                                   |

| J    |             | 1 — Suspended                                                              |

| 1    |             | 2 — No Resources                                                           |

|      |             | 3 — Not Used                                                               |

|      |             | 4 — Reacy                                                                  |

|      |             | 5-7 — Not Used                                                             |

|      |             |                                                                            |

**COMMAND word:** Specifies the action to be performed as a result of the CA. This word is set by the CPU and cleared by the 82586. Defined bits are:

| ACK-CX  | (Bit 15)          | Acknowledges the                                                                                                                                                                  |

|---------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACK-FR  | (Bit 14)          | <ul> <li>command executed event.</li> <li>Acknowledges the frame received event.</li> </ul>                                                                                       |

| ACK-CNA | (Bit 13)          | Acknowledes that the<br>Command Unit became not                                                                                                                                   |

| ACK-RNR | (Bit 12)          | ready.  • Acknowledges that the Receive Unit became not                                                                                                                           |

| cuc     | (Bits 8-10)       | ready.  • (3 bits) this field contains the command to the                                                                                                                         |

|         | 0                 | Command Unit.  NOP (doesn't affect current state of the unit).                                                                                                                    |

|         | 1                 | Start execution of the first command on the CBL. If a                                                                                                                             |

|         | 2                 | command is in execution, then complete it before starting the new CBL. The beginning of the CBL is in CBL OFFSET.  Resume the operation of the command unit by executing the next |

|         | 3                 | command. This operation assumes that the command unit has been previously suspended.  Suspend execution of commands on CBL after current command is                               |

|         | 4                 | Abort execution of                                                                                                                                                                |

| RUC     | 5-7<br>(Bits 4-6) | commands immediately.  Reserved, illegal for use.  (3 bits) This field contains the command to the receive unit. Valid values                                                     |

|         | 0                 | are: • NCP (does not alter current                                                                                                                                                |

|         | 1                 | state of unit).  Start reception of frames. If a frame is being received, then complete reception before starting. The beginning of the RFA is                                    |

|         | 2                 | contained in the RFA OFFSET.  Resume frame receiving (only when in suspended                                                                                                      |

|         | 3                 | state.)  • Suspend frame receiving. If a frame is being received, then complete its recention.                                                                                    |

|         | 4                 | then complete its reception before suspending.  • Abort receiver operation immediately.                                                                                           |

| RESET   | 5–7<br>(Bit 7)    | Reserved, illegal for use.     Reset chip (logically the same as hardware RESET).                                                                                                 |

#### **CBL-OFFSET:**

Gives the 16-bit offset address of the first command (Action Command) in the command list to be executed following CU-START. Thus, the 82586 reads this word only if the CUC field contained a CU-START Control Command.

#### RFA-OFFSET:

Points to the first Receive Frame Descriptor in the Receive Frame Area.

#### CRCERRS:

CRC Errors - contains the numbe of properly aligned frames received with a CRC error

#### ALNERRS:

Alignment Errors - contains the number of misaligned frames received with a CRC error.

#### **RSCERRS:**

Resource Errors - records the number of correct incoming frames discarded due to lack of memory resources (buffer space or received frame descriptors).

#### **OVRNERRS:**

Overrun Errors - counts the number of received frame sequences lost because the memory bus was not available in time to transfer them.

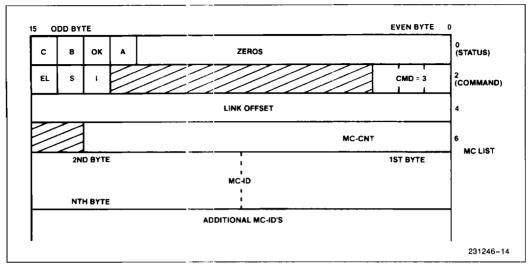

### **ACTION COMMANDS**

The 82586 executes a 'program' that s made up of action commands in the Command Lis. As shown in

Figure 5, each command contains the command field, status and control fields, link to the next action command in the CL, and any command-specific parameters. This command format is called the Command Block.

The 82586 has a repertoire of 8 commands:

NOP Setup Individual Address Configure Setup Multicast Address Transmit TDR Diagnose Dump

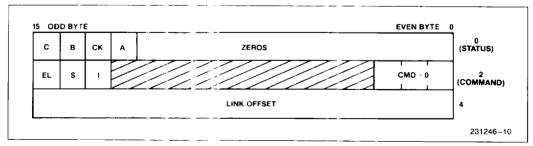

#### NOP

This command results in no action by the 82586, except as performed in normal command processing. It is present to aid in Command List manipulation.

NOP command includes the following fields:

#### STATUS word (written by 82586):

| С  | (Bit 15) | Command Completed                          |

|----|----------|--------------------------------------------|

| В  | (Bit 14) | <ul> <li>Busy Executing Command</li> </ul> |

| OK | (Eit 13) | <ul> <li>Error Free Completion</li> </ul>  |

#### **COMMAND** word:

| EL  | (Bit 15)   | End of Command List                            |

|-----|------------|------------------------------------------------|

| S   | (Bit 14)   | Suspend After Completion                       |

| 1   | (Bit 13)   | <ul> <li>Interrupt After Completion</li> </ul> |

| CMD | (Bits 0-2) | • NOP = 0                                      |

LINK OFFSET: Address of next Command Block

Figure 11. The NOP Command Block

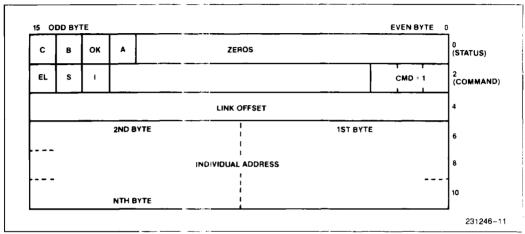

#### IA-SETUP

This command loads the 82586 with the Individual Address. This address is used by the 82586 for rec-

ognition of Destination Address during reception and insertion of Source Address during transmission.

The IA-SETUP command includes the following fields:

Figure 12. The IA-SETUP Command Block

#### STATUS word (written by 82586).

| C<br>B | (Bit 15)<br>(Bit 14) | Command Completed     Busy Executing Command |

|--------|----------------------|----------------------------------------------|

| OK     | (Bit 13)             | Error Free Completion                        |

| Α      | (Bit 12)             | Command Aborted                              |

#### **COMMAND** word:

| EL  | (Bit 15)   | End of Command List        |

|-----|------------|----------------------------|

| S   | (Bit 14)   | Suspend After Completion   |

| 1   | (Bit 13)   | Interrupt Afte: Completion |

| CMD | (Bits 0-2) | • IA-SETUP = 1             |

LINK OFFSET: Address of next Command Block

**INDIVIDUAL ADDRESS:** Individual Address parameter

The least significant bit of the Individual Address parameter must be zero for IEEE 802.3/Ethernet. However, no enforcement of 0 is provided by the 82586. Thus, an Individual Address with least significant bit 1, is possible.

#### **CONFIGURE**

The CONFIGURE command is used o update the 82586 operating parameters.

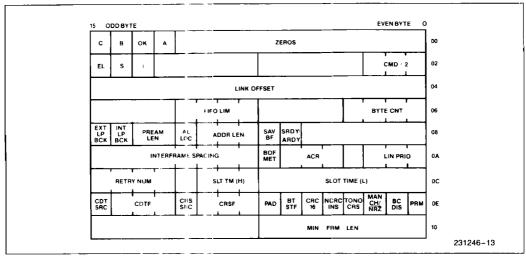

The CONFIGURE command includes the following fields:

#### STATUS word (written by 82586):

|    |          | •                                          |

|----|----------|--------------------------------------------|

| С  | (Bit 15) | Command Completed                          |

| В  | (Bit 14) | <ul> <li>Busy Executing Command</li> </ul> |

| OK | (Bit 13) | <ul> <li>Error Free Completion</li> </ul>  |

| Α  | (Bit 12) | <ul> <li>Command Aborted</li> </ul>        |

#### COMMAND word:

| EL<br>S  | (Bit 15)<br>(Bit 14)   | End of Command List     Suspend After Completion                   |

|----------|------------------------|--------------------------------------------------------------------|

| I<br>CMD | (Bit 13)<br>(Bits 0-2) | <ul><li>Interrupt After Completion</li><li>Configure = 2</li></ul> |

LINK OFFSET: Address of next Command Block

### Byte 6-7:

| BYTE CNT (Bits 0-3) | Byte Count, Number of<br>bytes including this one,<br>holding the parameters to<br>be configured. A number<br>smaller than 4 is<br>interpreted as 4. A<br>number greater than 12 is<br>interpreted as 12. |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

Figure 13. The CONFIGURE Command Block

| FIFO-LIM               | (Bits 8-11)  | Value of FIF()     Threshold.                                                  |                        | 1                    | Address and Length<br>Fields are part of the                                                   |

|------------------------|--------------|--------------------------------------------------------------------------------|------------------------|----------------------|------------------------------------------------------------------------------------------------|

| Byte 8-9:<br>SRDY/ARDY | (Bit 6)<br>0 | • SRDY/ARDY pin                                                                |                        |                      | Transmit/Receive data<br>buffers, including<br>Source Address (which<br>is not inserted by the |

|                        | 1            | operates as ARDY (internal synchronization).  • SRDY/ARDY pin operates as SRDY | PREAM-<br>LEN          | (Bits<br>12-13)      | 82586).  • Preamble Length including Beginning of Frame indicator:  00 - 2 bytes               |

| SAV-BF                 | (Bit 7)      | (external synchronization).                                                    |                        |                      | 01 - 4 bytes<br>10 - 8 bytes<br>11 - 16 bytes                                                  |

|                        | 0            | Received bad     frames are not saved     in memory.                           | INT-LPBCK<br>EXT-LPBCK | (Bit 14)<br>(Bit 15) | <ul> <li>Internal Loopback</li> <li>External Loopback</li> <li>NOTE: Bits 14 and 15</li> </ul> |

|                        | 1            | Received bad<br>frames are saved in                                            |                        |                      | configured to 1, cause<br>Internal Loopback.                                                   |

| ADD-LEN                | (Bits 8-10)  | memory.  Number of address                                                     | Byte 10-11:            |                      |                                                                                                |

|                        | (2 5         | byes. NOTE: 7 is                                                               | LIN-PRIO               | (Bits 0-2)           | Linear Priority                                                                                |

interpreted as 0.

Address and Length Fields separated from data and associated with Transmit Command Block or Receive Frame Descriptor.

For transmitted Frame, Source Address is inserted by the 82586.

| LIN-PRIO | (Bits 0-2) | Linear Priority                                                                                           |

|----------|------------|-----------------------------------------------------------------------------------------------------------|

| ACR      | (Bits 4-6) | <ul> <li>Accelerated Contention<br/>Resolution (Exponential<br/>Priority)</li> </ul>                      |

| BOF-MET  | (Bit 7)    | <ul> <li>Exponential Backoff<br/>Method</li> <li>IEEE 802.3/Ethernet</li> <li>Alternate Method</li> </ul> |

AL-LOC

(Bit 11)

| INTER   | (Bits 8-15) | Number indicating |

|---------|-------------|-------------------|

| FRAME   |             | the Interframe    |

| SPACING |             | Spacing in TxC    |

|         |             | period units.     |

#### Byte 12-13:

| SLOT-<br>TIME (L) | (Bits 0-7)      | <ul> <li>Slot Time Number,<br/>Low Byte</li> </ul>                               |

|-------------------|-----------------|----------------------------------------------------------------------------------|

| SLT-TM (H)        | (Bits 8-10)     | <ul> <li>Slot Time Number,<br/>High Bits</li> </ul>                              |

| RETRY-<br>NUM     | (Bits<br>12-15) | <ul> <li>Maximum Number of<br/>Transmission Retries<br/>on Collisions</li> </ul> |

## Byte 14-15:

| Dyic 14 10. |            |                               |

|-------------|------------|-------------------------------|

| PRM         | (Bit 0)    | Promiscuous Mode              |

| BC-DIS      | (Bit 1)    | Broadcast Disable             |

| MANCH/      | (Bit 2)    | Manchester or NRZ             |

| NRZ         | , ,        | Encoding/Decoding             |

|             | lo         | • NRZ                         |

|             | 1          | Manchester                    |

| TONO-CRS    | (Bit 3)    | Transmit on No                |

|             | , ,        | Carrier Sense                 |

|             | 0          | Cease Transmission            |

|             |            | if CRS Goes Inactive          |

|             |            | During Frame                  |

|             |            | Transmission                  |

|             | 1          | Continue                      |

|             |            | Transmission Even if          |

|             |            | no Carrier Sense              |

| NCRC-INS    | (Bit 4)    | No CRC Insertion              |

| CRC-16      | (Bit 5)    | CRC Type:                     |

|             | 0          | 32 bit Autodin II CRC         |

|             |            | Polynomial                    |

|             | 1          | 16 bit CCITT CRC              |

|             |            | Polynomial                    |

| BT-STF      | (Bit 6)    | Bitstuffing:                  |

|             | 0          | End of Carrier Mode           |

|             |            | (Ethernet)                    |

|             | 1          | HDLC like Bitstuffing         |

| DAD         | (D:+ 7)    | Mode                          |

| PAD         | (Bit 7)    | Padding     No Padding        |

|             | 0          | No Padding                    |

|             | 1          | Perform Padding by            |

|             |            | Transmitting Flags            |

|             |            | for Remainder of<br>Slot Time |

| CRSF        | (Bits 8-9) | Carrier Sense Filter          |

| Onor        | (101120-9) | in Bit Times                  |

| CRS-SRC     | (Bit 11)   | Carrier Sense                 |

| 3.10 3.10   | \          | Source                        |

| 1           | o          | External                      |

|             | 1          | Internal                      |

|             |            |                               |

| CDTF    | (Bits<br>12-14 | Collision Detect     Filter in Bit Times        |

|---------|----------------|-------------------------------------------------|

| CDT-SRC | (Bit 15)       | <ul> <li>Collision Detect<br/>Source</li> </ul> |

|         | 0              | <ul> <li>External</li> </ul>                    |

|         | 1              | <ul><li>Internal</li></ul>                      |

#### Byte 16:

| MIN-FRM- | (Bits 0-7) | Minimum Number of |  |

|----------|------------|-------------------|--|

|          |            | Bytes in a Frame  |  |

# **CONFIGURATION DEFAULTS**

The default values of the configuration parameters are compatible with the IEEE 802.3/Ethernet Standards. RESET configures the 82586 according to the defaults shown in Table 2.

Table 2, 82586 Default Values

| Preamble Length (Bytes)         =         8           Address Length (Bytes)         =         6           Broadcast Disable         =         0           CRC-16/CRC-32         =         0           No CRC Insertion         =         0           Bitstuffing/EOC         =         0           Padding         =         0           Min-Frame-Length (Bytes)         =         64           Interframe Spacing (Bits)         =         96           Slot Time (Bits)         =         95           Slot Time (Bits)         =         96           Slot Time (Bits)         =         0           Cacelerated Contention Resolution         =         0           CRS Filter         =         0 | Table 2, 62366 Default val        | ues |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----|-----|

| Broadcast Disable         =         0           CRC-16/CRC-32         =         0           No CRC Insertion         =         0           Bitstuffing/EOC         =         0           Padding         =         0           Min-Frame-Length (Bytes)         =         64           Interframe Spacing (Bits)         =         96           Slot Time (Bits)         =         512           Number of Retries         =         15           Linear Priority         =         0           Accelerated Contention Resolution         =         0           Exponential Backoff Method         =         0           Manchester/NRZ         =         0           Internal CRS         =         0           CRS Filter         =         0           Internal CDT         =         0           CDT Filter         =         0           Transmit On No CRS         =         0           FIFO THRESHOLD         =         8           SRDY/ARDY         =         0           Save Bad Frame         =         0           Address/Length Location         =         0           INT Loop          | Preamble Length (Bytes)           | =   | 8   |

| CRC-16/CRC-32         =         0           No CRC Insertion         =         0           Bitstuffing/EOC         =         0           Padding         =         0           Min-Frame-Length (Bytes)         =         64           Interframe Spacing (Bits)         =         96           Slot Time (Bits)         =         512           Number of Retries         =         15           Linear Priority         =         0           Accelerated Contention Resolution         =         0           Exponential Backoff Method         =         0           Manchester/NRZ         =         0           Internal CRS         =         0           CRS Filter         =         0           Internal CDT         =         0           CDT Filter         =         0           Transmit On No CRS         =         0           FIFO THRESHOLD         =         8           SRDY/ARDY         =         0           Save Bad Frame         =         0           Address/Length Location         =         0           INT Loopback         =         0                                  | Address Length (Bytes)            | =   | 6   |

| No CRC Insertion         =         0           Bitstuffing/EOC         =         0           Padding         =         0           Min-Frame-Length (Bytes)         =         64           Interframe Spacing (Bits)         =         96           Slot Time (Bits)         =         512           Number of Retries         =         15           Linear Priority         =         0           Accelerated Contention Resolution         =         0           Exponential Backoff Method         =         0           Manchester/NRZ         =         0           Internal CRS         =         0           CRS Filter         =         0           Internal CDT         =         0           CDT Filter         =         0           Transmit On No CRS         =         0           FIFO THRESHOLD         =         8           SRDY/ARDY         =         0           Save Bad Frame         =         0           Address/Length Location         =         0           INT Loopback         =         0                                                                              | Broadcast Disable                 | =   | 0   |

| Bitstuffing/EOC         =         0           Padding         =         0           Min-Frame-Length (Bytes)         =         64           Interframe Spacing (Bits)         =         96           Slot Time (Bits)         =         512           Number of Retries         =         15           Linear Priority         =         0           Accelerated Contention Resolution         =         0           Exponential Backoff Method         =         0           Manchester/NRZ         =         0           Internal CRS         =         0           CRS Filter         =         0           Internal CDT         =         0           CDT Filter         =         0           Transmit On No CRS         =         0           FIFO THRESHOLD         =         8           SRDY/ARDY         =         0           Save Bad Frame         =         0           Address/Length Location         =         0           INT Loopback         =         0                                                                                                                             | CRC-16/CRC-32                     | =   | 0   |

| Padding         =         0           Min-Frame-Length (Bytes)         =         64           Interframe Spacing (Bits)         =         96           Slot Time (Bits)         =         512           Number of Retries         =         15           Linear Priority         =         0           Accelerated Contention Resolution         =         0           Exponential Backoff Method         =         0           Manchester/NRZ         =         0           Internal CRS         =         0           CRS Filter         =         0           Internal CDT         =         0           CDT Filter         =         0           Transmit On No CRS         =         0           FIFO THRESHOLD         =         8           SRDY/ARDY         =         0           Save Bad Frame         =         0           Address/Length Location         =         0           INT Loopback         =         0           EXT Loopback         =         0                                                                                                                                | No CRC Insertion                  | =   | 0   |

| Min-Frame-Length (Bytes)       =       64         Interframe Spacing (Bits)       =       96         Slot Time (Bits)       =       512         Number of Retries       =       15         Linear Priority       =       0         Accelerated Contention Resolution       =       0         Exponential Backoff Method       =       0         Manchester/NRZ       =       0         Internal CRS       =       0         CRS Filter       =       0         Internal CDT       =       0         CDT Filter       =       0         Transmit On No CRS       =       0         FIFO THRESHOLD       =       8         SRDY/ARDY       =       0         Save Bad Frame       =       0         Address/Length Location       =       0         INT Loopback       =       0         EXT Loopback       =       0                                                                                                                                                                                                                                                                                      | Bitstuffing/EOC                   | =   | 0   |

| Interframe Spacing (Bits)         =         96           Slot Time (Bits)         =         512           Number of Retries         =         15           Linear Priority         =         0           Accelerated Contention Resolution         =         0           Exponential Backoff Method         =         0           Manchester/NRZ         =         0           Internal CRS         =         0           CRS Filter         =         0           Internal CDT         =         0           CDT Filter         =         0           Transmit On No CRS         =         0           FIFO THRESHOLD         =         8           SRDY/ARDY         =         0           Save Bad Frame         =         0           Address/Length Location         =         0           INT Loopback         =         0           EXT Loopback         =         0                                                                                                                                                                                                                              | Padding                           | =   | 0   |

| Slot Time (Bits)       =       512         Number of Retries       =       15         Linear Priority       =       0         Accelerated Contention Resolution       =       0         Exponential Backoff Method       =       0         Manchester/NRZ       =       0         Internal CRS       =       0         CRS Filter       =       0         Internal CDT       =       0         CDT Filter       =       0         Transmit On No CRS       =       0         FIFO THRESHOLD       =       8         SRDY/ARDY       =       0         Save Bad Frame       =       0         Address/Length Location       =       0         INT Loopback       =       0         EXT Loopback       =       0                                                                                                                                                                                                                                                                                                                                                                                           | Min-Frame-Length (Bytes)          | =   | 64  |

| Number of Retries         =         15           Linear Priority         =         0           Accelerated Contention Resolution         =         0           Exponential Backoff Method         =         0           Manchester/NRZ         =         0           Internal CRS         =         0           CRS Filter         =         0           Internal CDT         =         0           CDT Filter         =         0           Transmit On No CRS         =         0           FIFO THRESHOLD         =         8           SRDY/ARDY         =         0           Save Bad Frame         =         0           Address/Length Location         =         0           INT Loopback         =         0           EXT Loopback         =         0                                                                                                                                                                                                                                                                                                                                        | Interframe Spacing (Bits)         | ==  | 96  |

| Linear Priority         =         0           Accelerated Contention Resolution         =         0           Exponential Backoff Method         =         0           Manchester/NRZ         =         0           Internal CRS         =         0           CRS Filter         =         0           Internal CDT         =         0           CDT Filter         =         0           Transmit On No CRS         =         0           FIFO THRESHOLD         =         8           SRDY/ARDY         =         0           Save Bad Frame         =         0           Address/Length Location         =         0           INT Loopback         =         0           EXT Loopback         =         0                                                                                                                                                                                                                                                                                                                                                                                         | Slot Time (Bits)                  | =   | 512 |

| Accelerated Contention Resolution         =         0           Exponential Backoff Method         =         0           Manchester/NRZ         =         0           Internal CRS         =         0           CRS Filter         =         0           Internal CDT         =         0           CDT Filter         =         0           Transmit On No CRS         =         0           FIFO THRESHOLD         =         8           SRDY/ARDY         =         0           Save Bad Frame         =         0           Address/Length Location         =         0           INT Loopback         =         0           EXT Loopback         =         0                                                                                                                                                                                                                                                                                                                                                                                                                                       | Number of Retries                 | =   | 15  |

| Exponential Backoff Method         =         0           Manchester/NRZ         =         0           Internal CRS         =         0           CRS Filter         =         0           Internal CDT         =         0           CDT Filter         =         0           Transmit On No CRS         =         0           FIFO THRESHOLD         =         8           SRDY/ARDY         =         0           Save Bad Frame         =         0           Address/Length Location         =         0           INT Loopback         =         0           EXT Loopback         =         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Linear Priority                   | =   | 0   |

| Manchester/NRZ         =         0           Internal CRS         =         0           CRS Filter         =         0           Internal CDT         =         0           CDT Filter         =         0           Transmit On No CRS         =         0           FIFO THRESHOLD         =         8           SRDY/ARDY         =         0           Save Bad Frame         =         0           Address/Length Location         =         0           INT Loopback         =         0           EXT Loopback         =         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Accelerated Contention Resolution | =   | 0   |