# Am2930

Program Control Unit

# DISTINCTIVE CHARACTERISTICS

- Powerful, 4-bit slice address controller for memories Useful with both main memory and microprogram mem-

- Expandable to generate any address length

- **Executes 32 instructions** Capable of executing branch and subroutine call and return

- Twelve different relative address instructions Including JUMP-TO-SUBROUTINE relative and RE-TURN-FROM-SUBROUTINE relative

- Built-in condition code input Sixteen instructions are dependent on external condition control

- Seventeen-level push/pop stack On-chip storage of subroutine return addresses nested up to 17 levels deep

- Separate incrementer for program counter A relative address may be computed and PC may be incremented by one on a single cycle

# **GENERAL DESCRIPTION**

The Am2930 is a four-bit wide Program Control Unit intended to perform machine level addressing functions, although the device can also be used as a microprogram sequencer. Four Am2930's may be interconnected to generate a 16-bit address (64K words). The Am2930 contains a program counter, a subroutine stack, an auxiliary register, and a full adder for computing relative addresses.

The Am2930 performs five types of instructions. These are: 1) Unconditional Fetch; 2) Conditional Jump; 3) Conditional Jump-to-Subroutine; 4) Conditional Return-from-Subroutine; and 5) Miscellaneous Instructions.

There are four sources of data for the adder which generates the Address outputs (Y0-Y3). These are: 1) the Program Counter (PC); 2) the Stack (S); 3) the auxiliary Register (R); and 4) the Direct inputs (D). Under control of the instruction inputs (I<sub>0</sub>-I<sub>4</sub>), the multiplexers at the adder inputs allow various combinations of these terms to be generated at the three-state Y address outputs. The instruction lines also control the updating of the program counter and the auxiliary register. A condition code input is provided for conditional instructions.

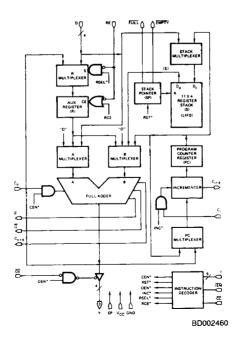

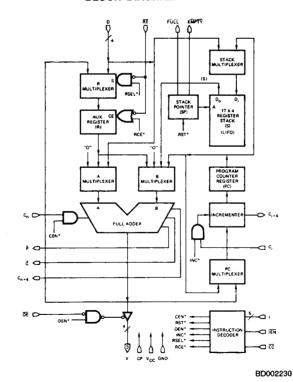

# **BLOCK DIAGRAM**

03642B

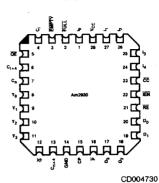

# CONNECTION DIAGRAM TOD View

Chip-Pak<sup>TM</sup> L-28-1

\*F-28 pin configuration identical to D-28. Note: Pin 1 is marked for orientation

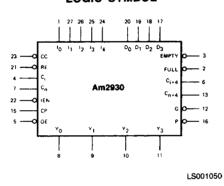

# LOGIC SYMBOL

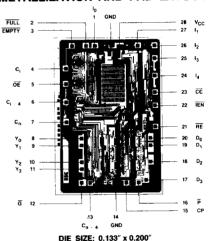

# METALLIZATION AND PAD LAYOUT

Pad numbers correspond to DIP pinout

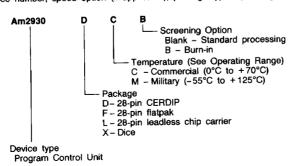

# **ORDERING INFORMATION**

AMD products are available in several packages and operating ranges. The order number is formed by a combination of the following: Device number, speed option (if applicable), package type, operating range and screening option (if desired).

| Valid Combinations |                                          |  |  |  |  |

|--------------------|------------------------------------------|--|--|--|--|

| Am2930             | DC, DCB, DMB<br>FMB<br>LC, LMB<br>XC, XM |  |  |  |  |

#### Valid Combinations

Consult the AMD sales office in your area to determine if a device is currently available in the combination you wish.

# PIN DESCRIPTION

| Pin No. | Name             | 1/0 | Description                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 10-4             |     | The five Instruction control lines to the Am2930, used to establish data paths and enable internal registers.                                                                                                                                                                                                                                                                                              |

| 22      | ĪĒŇ              |     | The instruction Enable Input, used to enable and disable internal registers. When IEN is LOW, all internal registers are under control of the Instruction inputs. When IEN is HIGH, all internal registers except R are inhibited from changing state. R is controlled by the RE input. The IEN input does not affect the combinatorial data paths and the outputs established by the IEnstruction inputs. |

| 23      | CC C             | ı   | The Condition Code input determines whether or not a conditional instruction (Instructions 16-31) is performed. If $\overline{CC}$ is LOW, the conditional instruction is executed. If $\overline{CC}$ is HIGH, Fetch PC (Instruction 1) is executed. The $\overline{CC}$ input may be either HIGH or LOW for unconditional instructions (Instructions 0-15).                                              |

| 21      | RE               | ı   | The Register Enable input for the Auxiliary Register (R). A LOW on RE causes the Auxiliary Register (R) to be loaded from the D inputs unless Instruction 8 or 9 is being executed and IEN is LOW.                                                                                                                                                                                                         |

| 7       | Cn               | ł   | The carry-in to the Full Adder.                                                                                                                                                                                                                                                                                                                                                                            |

| 13      | Cn + 4           | 0   | The carry-out of the Full Adder.                                                                                                                                                                                                                                                                                                                                                                           |

| 16,12   | P, G             | 0   | The carry generate and propagate outputs of the Full Adder.                                                                                                                                                                                                                                                                                                                                                |

| 4       | Ci               | 1   | The carry-in to the program counter incrementer.                                                                                                                                                                                                                                                                                                                                                           |

| 6       | Ci + 4           | 0   | The carry-out of the program counter incrementer.                                                                                                                                                                                                                                                                                                                                                          |

|         | Y <sub>0-3</sub> | 0   | The four address outputs of the Am2930. These are three-state output lines. When enabled, they display the outputs of the Full Adder.                                                                                                                                                                                                                                                                      |

| 5       | OE               | ï   | Output Enable. When $\overline{OE}$ is HIGH, the Y outputs are OFF (high-impedance); when $\overline{OE}$ is LOW, the Y outputs are active (HIGH or LOW).                                                                                                                                                                                                                                                  |

| •       | D <sub>0-3</sub> | 1   | The four Direct inputs which are used as inputs to the Auxiliary Register, the RAM, and the Full Adder, under instruction control.                                                                                                                                                                                                                                                                         |

| 3       | Empty            | - 0 | The Empty output is LOW when the Stack is empty.                                                                                                                                                                                                                                                                                                                                                           |

| 2       | Full             | 0   | The Full output is LOW when the LiFO stack is full - during and after the 17th push operation.                                                                                                                                                                                                                                                                                                             |

| 15      | СР               | 1   | The clock input to the Am2930. All internal registers (R, SP, PC) and the RAM are updated on the LOW-to-HIGH transition of the clock input.                                                                                                                                                                                                                                                                |

# **BLOCK DIAGRAM**

\*INTERNAL

# ARCHITECTURE OF THE Am2930

The Am2930 is a bipolar Program Control Unit intended for use in high-speed microprocessor applications. The device is a cascadable, four-bit slice such that three devices allow addressing of up to 4K words of memory and four devices allow addressing of up to 64K words of memory.

As shown in the Block Diagram, the device consists of the following:

- 1. A full adder with input multiplexers

- 2. A Program Counter Register with an incrementer and an input multiplexer

- A 17 x 4 Last-In, First-Out (LIFO) stack consisting of an input multiplexer, a 17 x 4 RAM, and a Stack Pointer

- 4. An auxiliary register with an input multiplexer

- 5. An instruction decoder

- 6. Four 3-state output buffers on the address outputs

The following paragraphs describe each of these blocks in detail.

#### Full Adder

The Full Adder is a binary device with full lookahead carry logic for high-speed addition and provision is made for further lookahead by including both carry propagate ( $\overline{P}$ ) and carry generate ( $\overline{G}$ ) outputs. In slower systems, the carry output ( $C_n+4$ ) can be connected to the next higher  $C_n$  to provide ripple block arithmetic. The carry input to the adder ( $C_n$ ) is internally inhibited during those instructions which do not require an addition to be performed. For these instructions, the data is passed directly through the adder, independent of the state of  $C_n$ .

The multiplexers at the A and B inputs of the adder are controlled by the Instruction decoder which selects the appropriate adder inputs for the selected instruction.

#### **Program Counter**

The program counter consists of a register preceded by an incrementer. The Program Counter Register (PC) is a four-bit, edge-triggered, D-type register which is loaded from the incrementer output on the LOW-to-HIGH transition of the clock input (CP) at the end of every instruction.

The incrementer utilizes full lookahead logic for high speed. For cascading devices, the carry output of the incrementer (Ci + 4) is connected to the incrementer carry input (Ci) of the next higher device. The output of the incrementer, which is loaded into the PC, is equal to the incrementer input plus Ci. Therefore, it is possible to control the entire cascaded incrementer from the Ci input of the least significant device; a LOW on the Ci input of the least significant device will simply pass the data from the multiplexer output to the inputs of PC; a HIGH will cause the outputs of the multiplexer to be incremented before they are loaded into PC. During three instructions (unconditional Hold and conditional Hold and Suspend when the CC input is LOW), the Ci input is internally inhibited; therefore, data is passed from the multiplexer output to the PC without incrementing. The multiplexer selects the input to the incrementer from either PC or the output of the Full Adder, depending upon the instruction being executed. During the Jump, Jump-to-Subroutine, and Return instructions, the multiplexer chooses the Full Adder outputs as the input to the incrementer if the CC input is LOW. The Full Adder output is also selected for the Reset instruction. For all other instructions, the PC is selected as the input to the incrementer.

#### 17 x 4 LIFO Stack

The 17 x 4 LIFO stack consists of a multiplexer, a 17 x 4 RAM, and a Stack Pointer (SP) which address the words in the RAM.

The SP always points to the last word written into the RAM (Top of the Stack). The Top of the Stack (S) is available at the output of the RAM.

Data is pushed onto the Top of the Stack from either D or PC. It is written into memory location SP+1. The SP is incremented on the LOW-to-HIGH clock transition at the end of the cycle so that it still points to the last data written into the RAM.

For a Pop operation, the contents of the RAM are not changed, but the SP is decremented at the end of the cycle so that it then points to the new Top of the Stack.

The SP is an up/down counter which changes state on the LOW-to-HIGH transition of the Clock input. It is internally prevented from incrementing when the stack is full and from decrementing when the Stack is empty. When the Stack is full, the RAM write circuitry is also inhibited.

The active LOW Empty output (EMPTY) is LOW when the stack is empty (after the Reset instruction and after the last word has been Popped from the stack); the active LOW Full output (FULL) is LOW either when the stack is full or when the current instruction being executed will fill the stack (during and after the 17th Push).

#### Auxiliary Register (R)

The Auxiliary Register (R) can be loaded from either the Direct inputs (D) or the output of the Full Adder. It is loaded on the LOW-to-HIGH transition of the clock input (CP) if the Register Enable input (RE) is LOW or if the Instruction inputs call for it to be loaded. When RE is LOW, R is loaded from the D inputs unless the Instruction dictates that R be loaded from the output of the Full Adder.

#### Instruction Decoder

The Instruction Decoder generates the signals necessary to establish the data paths and to enable the loading of the PC, R, SP, and RAM.

For unconditional instructions, the  $\overline{CC}$  input is not utilized; it may be either HIGH or LOW. For conditional instructions, if  $\overline{CC}$  is LOW, the condition is met and the conditional operation is performed; if  $\overline{CC}$  is HIGH, a Fetch PC is performed.

## **Output Buffers**

The Address outputs (Y<sub>0</sub>–Y<sub>3</sub>) are three-state drivers which may be disabled either under Instruction control or by a HIGH on the Output Enable input (OE). Disabling the Y outputs does not affect the execution of instructions inside the Am2930.

#### Instruction Enable

When HIGH, the Instruction Enable input (IEN) forces PC and SP into the hold mode and disables the write circuitry to the RAM. The auxiliary register (R) is under control of the RE input when IEN is HIGH, independent of the state of the Instruction inputs. The IEN input does not affect the combinatorial data paths or Y outputs in the Am2930. The data paths are selected by the Instruction and CC inputs and are not affected by IEN.

# Am2930 INSTRUCTION SET

The Am2930 Instruction set can be divided into five types of instructions. These are:

- Unconditional Fetches

- Conditional Jumps

- Conditional Jumps-to-Subroutine

- Conditional Returns-from-Subroutine

- Miscellaneous Instructions

The following paragraphs describe each of these types in detail.

## **Unconditional Fetches**

As can be seen from Table 1, there are nine unconditional Fetch instructions (Instructions 1–9). Under control of the Instruction inputs, the desired value is placed at the Y outputs. For all Fetch instructions, PC is incremented if C<sub>1</sub> of the least significant device is HIGH. For Instructions 1 through 7, the auxiliary register is under control of the RE input. For Instructions 8 and 9, R is loaded with PC and R + D, respectively. The RAM and Stack Pointer are not changed during a Fetch instruction.

#### **Conditional Jumps**

There are six conditional Jump instructions (Instructions 16 through 21). Under control of the Instruction inputs, the desired value is placed at the Y outputs. Additionally, the value is incremented if  $C_i$  of the least significant device is HIGH and loaded into PC. During these instructions,  $R_i$  is controlled by  $R_i$ . The RAM and Stack Pointer are not changed during these instructions. The above operations are performed if the  $C_i$  input is LOW; if  $C_i$  is HIGH, a Fetch PC operation is performed.

#### Conditional Jumps-to-Subroutine

There are six conditional Jump-to-Subroutine instructions (Instructions 22 through 27). Under control of the Instruction inputs, the desired value is placed on the Y outputs. On the rising edge of the clock the value is incremented\* and loaded into PC; PC is loaded into the RAM at location SP + 1, and SP is incremented.

As with Conditional Jump Instructions, R is controlled by  $\overline{\text{RE}}$  and whether the Jump-to-Subroutine or Fetch PC is performed depends upon the state of the  $\overline{\text{CC}}$  input.

## Conditional Returns-from-Subroutine

There are two conditional Return-from-Subroutine instructions (Instructions 28 and 29). Under control of the instruction inputs, either S or S + D is placed at the Y outputs. Additionally, the selected value is incremented\* and loaded into PC and SP is decremented at the end of the cycle (on the rising edge of the clock).

\*If Ci of the least significant device is HIGH.

As with the Condition Jump and Jump-to-Subroutine Instructions, R is controlled by  $\overline{\text{RE}}$  and whether the Return-from-Subroutine or Fetch PC is performed depends upon the state of the  $\overline{\text{CC}}$  input.

#### Miscellaneous Instructions

Each of the nine miscellaneous instructions is described individually.

#### Reset (Instruction 0)

The Reset instruction forces the Y outputs to zero, loads either zero or one into PC, depending upon the  $C_i$  input of the least significant device, and resets SP. The RAM is unchanged and R is controlled by  $\overline{\text{RE}}$ .

#### Load R (Instruction 10)

This instruction loads the data on the D inputs into R. PC is either incremented or held depending upon  $C_i$  of the least significant device. The SP and RAM are not changed.

#### Push PC (Instruction 11)

This instruction is the same as Fetch PC except that PC is loaded into RAM and SP is incremented at the end of the cycle; i.e., the current PC is Pushed onto the stack.

#### Push D (Instruction 12)

This instruction is the same as Fetch PC except that D is loaded into the RAM and SP is incremented at the end of the cycle; i.e., external data is Pushed onto the stack.

## Pop S (Instruction 13)

This instruction places the Top of the Stack (S) at the Y outputs and decrements SP at the end of the cycle. The PC is incremented if the  $C_i$  input of the least significant device is HIGH. R is controlled by  $\overline{\text{RE}}$ .

#### Pop PC (Instruction 14)

This instruction is the same as Fetch PC except SP is decremented at the end of the cycle, causing the data at the top of the stack to be lost.

#### Hold (Instruction 15)

This instruction places PC at the Y outputs and inhibits any change in PC, SP, and RAM. R is controlled by  $\overline{\text{RE}}$ .

#### Conditional Hold (Instruction 30)

This instruction is the same as Hold except  $\overline{CC}$  must be LOW. If  $\overline{CC}$  is HIGH, the Fetch PC instruction is performed.

#### Suspend (Instruction 31)

The Suspend instruction is the same as the Conditional Hold instruction except the Y outputs are forced into the high-impedance state if  $\overline{CC}$  is LOW.

TABLE I - Am2930 INSTRUCTION SET

|               |                       |                       |        |                  | İ                                                 | Next State (after CP) (Note 3)                                                       |        |      |                 |          |

|---------------|-----------------------|-----------------------|--------|------------------|---------------------------------------------------|--------------------------------------------------------------------------------------|--------|------|-----------------|----------|

|               |                       | !                     |        |                  |                                                   |                                                                                      | R      |      |                 |          |

| Mne-<br>monic | Instruction<br>Number | l4 l3 l2 l1 l0        | CC IEN | Instruction      | Y <sub>0</sub> -Y <sub>3</sub>                    | PC                                                                                   | RE = L | RE≖H | RAM             | SP       |

|               |                       | $x \times x \times x$ | хн     |                  | Note 1                                            | -                                                                                    | D      | -    | -               | -        |

| PRST          | .0                    | LLLLL                 |        | RESET            | ··o··                                             | "0" + Ci                                                                             | D      | -    | -               | Reset    |

| FPC           | 1                     | LLLLH                 | X L    | FETCH PC         | PC                                                | PC + Ci                                                                              | D      | - 1  | -               | -        |

| FR            | 2                     | LLLHL                 |        | FETCH R          | B                                                 | PC + Ci                                                                              | D      | -    | - 1             | _        |

| FD            | 3                     | LLLHH                 |        | FETCH D          | D                                                 | PC + Ci                                                                              | D<br>D | ~    |                 | _        |

| FRD           | 4                     | LLHLL                 |        | FETCH R + D      | P+D+Cn                                            | PC + Ci                                                                              | D I    | - 1  | _               |          |

| FPD           | 5                     | LLHLH                 |        | FETCH PC + D     | PC + D + Cn                                       | PC + Ci<br>PC + Ci                                                                   | ا ط    |      | _               | - 1      |

| FPR           | 5<br>6<br>7           | LLHHL                 |        | FETCH PC + R     | PC + R + C <sub>n</sub><br>S + D + C <sub>n</sub> | PC + Ci                                                                              | Ď      | _    | _ '             | - i      |

| FSD           | 7                     | LLHHH                 |        | FETCH S + D      | PC PC                                             | PC + C                                                                               | PC     | PC   | _               | -        |

| FPLR          | 8 9                   | LHLLL                 |        | FETCH PC - R     | R + D + Cn                                        | PC + Ci                                                                              | R+D+Cn |      | _               | -        |

| FRDR          | 9                     | LHLLH                 |        | LOAD R           | PC                                                | PC + Ci                                                                              | D 0    | D    | _               | -        |

| PLDR          | 10                    | LHLHL                 |        | PUSH PC          | PC                                                | PC + C                                                                               | Ď      | _    |                 | SP + 1   |

| PSHP          | 11                    |                       |        | PUSH D           | PC                                                | PC + C                                                                               | D      | -    | D → Loc SP + 1  | SP + 1   |

| PSHD          | 12<br>13              | 1:44:4                |        | POP S            | s                                                 | PC+Ci                                                                                | D      | -    | -               | SP-1     |

| POPS          | 14                    | LHHHL                 |        | POP PC           | PC                                                | PC + Ci                                                                              | D      | -    | -               | SP-1     |

| PHLD          | 15                    | LHHHH                 |        | HOLD             | PC                                                | - '                                                                                  | D      | -    | -               | -        |

| PALLO         | '5                    | I                     | /· -   |                  |                                                   |                                                                                      | i      |      |                 |          |

|               | 16-31                 | нхххх                 | H L    | FAIL COND'L      | PC                                                | PC + Ci                                                                              | D      | -    | -               | -        |

| ì             | ,,,,,                 |                       |        | TEST (FETCH PC)  |                                                   |                                                                                      |        |      |                 |          |

| JMPR          | 16                    | HLLLL                 | L L    | JUMP R           | R                                                 | R + C <sub>i</sub>                                                                   | D      | _    | -               | -        |

| JMPD          | 17                    | HLLLH                 | LL     | JUMP D           | D                                                 | D+Ci                                                                                 | D      | _    | _               | -        |

| JMPZ          | 18                    | HLLHL                 |        | JUMP "O"         | "O"                                               | "O" + C <sub>i</sub>                                                                 | D<br>D | -    | i -             | 1 - 1    |

| JPRD          | 19                    | HLLHH                 |        | JUMP R + D       | R + D + C <sub>n</sub>                            | R+D+Cn+Ci                                                                            | D D    |      |                 | _        |

| JPPD          | 20                    | HLHLL                 |        | JUMP PC + D      |                                                   | PC + D + C <sub>n</sub> + C <sub>i</sub><br>PC + R + C <sub>n</sub> + C <sub>i</sub> | l b    | _    |                 | _        |

| JPPR          | 21                    | HLHLH                 |        | JUMP PC + R      | R                                                 | R+Ci                                                                                 | Ď      | _    | PC→Loc SP + 1   | SP + 1   |

| JSBR          | 22                    | HLHHL                 |        | JSB R            | D D                                               | D+C                                                                                  | lő     | _    | PC→Loc SP + 1   | SP + 1   |

| JSBD          | 23                    | HIHHH                 |        | JSB D<br>JSB "O" | O                                                 | "O" + C <sub>1</sub>                                                                 | D<br>D | -    |                 | SP + 1   |

| JSBZ          | 24                    | HHLLL                 |        | JSB R + D        | R+D+Cn                                            | R + D + Cn + Ci                                                                      | Ď      | -    | PC → Loc SP + 1 | SP + 1   |

| JSRD          | 25                    | HHLLH                 |        | JSB PC + D       | PC + D + C                                        | PC + D + Cn + Ci                                                                     | l D    | -    | PC → Loc SP + 1 | SP + 3   |

| JSPD          | 26                    | HHLHH                 |        | JSB PC + R       | PC + R + Cn                                       | PC + R + Cn + Ci                                                                     | D      | i -  | PC → Loc SP + 1 | SP + 1   |

| JSPR          | 27<br>28              | HHHLL                 |        | RETURN S         | s                                                 | S+Ci"                                                                                | D      | l –  | -               | SP-1     |

| RTS           |                       | НННЕН                 |        | RETURN S + D     | S+D+Cn                                            | S + D + Cn + Ci                                                                      | D      | -    | -               | SP-1     |

| RTSD          |                       | H H H H L             |        | HOLD             | PC                                                | - " '                                                                                | D      | -    | -               | -        |

| PSUS          |                       | Паннай                |        | SUSPEND          | Z (Note 2)                                        | -                                                                                    | D      |      |                 | <u> </u> |

| 7303          |                       | 1                     |        | <u> </u>         |                                                   |                                                                                      |        |      | Otracta Tara    |          |

PC - Program Counter R - Auxiliary Register

SP - Stack Pointer D - Direct Inputs

S - Stack Top

Notes: 1. When IEN is HIGH, the Y0-Y3 outputs contain the same data as when IEN is LOW, as determined by I0-I4 and CC.

2. Z = High impedance state (outputs "OFF").

3. - = No change.

## **APPLICATIONS**

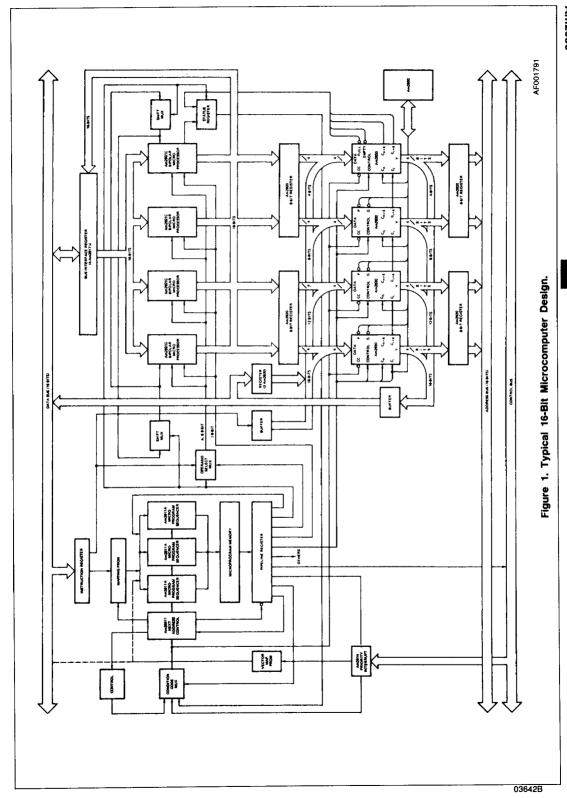

The Am2930 is shown in a typical 16-bit, 2900 Microcomputer design in Figure 1.

The Direct inputs (D) of the Am2930 are derived from one of three sources: the Instruction Register, the Data Bus via a 16bit register (two Am2920 8-bit Registers), and the output of the Am2901's via a 16-bit register.

The Address outputs (Y) of the Am2930 are loaded into a 16bit Memory Address Register (MAR). Although the MAR is shown as part of the CPU, in some applications it may be part of the memory.

An Am2902 High-Speed Lookahead Carry Generator is utilized to provide high-speed relative and indexed addressing. In slower systems, the Cn+4 output can be wired to the next higher Cn input to provide ripple block arithmetic.

The Condition Code input (CC) is derived from the same condition code multiplexer which generates the condition code input for the microprogram sequencer.

The control inputs of the Am2930 (I<sub>0-4</sub>,  $\overline{\text{IEN}}$ ,  $\overline{\text{RE}}$ ,  $\overline{\text{OE}}$ , and C<sub>i</sub> and Cn of the least significant device) are shown originating at the Pipeline Register. Although it is not shown in Figure 1, it is possible to share the Pipeline Register outputs which go to these pins with another device. This can be accomplished if both the Am2930 and the other device do not operate on the same microcycle. Forcing the IEN input HIGH inhibits any changes in the Am2930 internal registers, independent of the state of these seven inputs. This allows the Am2930 to be placed in a hold mode while the other device is using the same Pipeline Register outputs as control signals.

5-251

# **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature65°C to +150°C              |

|------------------------------------------------|

| (Ambient) Temperature Under Bias55°C to +125°C |

| Supply Voltage to Ground Potential             |

| Continuous0.5V to +7.0V                        |

| DC Voltage Applied to Outputs For              |

| High Output State0.5V to +V <sub>CC</sub> max  |

| DC Input Voltage0.5V to +5.5V                  |

| DC Output Current, Into Outputs 30mA           |

| DC Input Current30mA to +5.0mA                 |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

## **OPERATING RANGES**

| Commercial (C) Devices Temperature | 0°C to +70°C<br>+4.75V to +5.25V                                                |

|------------------------------------|---------------------------------------------------------------------------------|

| Supply Voltage                     | -55°C to +125°C<br>+4.5V to +5.5V<br>a limits over which the function-<br>leed. |

DC CHARACTERISTICS over operating range unless otherwise specified

| Parameters                              | ers Description Test Conditions (Note 2) |                                                                                |                                                                                             |                                 | Note 2)                           | Min | Typ<br>(Note 1) | Max   | Units    |  |

|-----------------------------------------|------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------|-----------------------------------|-----|-----------------|-------|----------|--|

| Voн                                     | Output HiGH Voltage                      | V <sub>CC</sub> = MIN,<br>V <sub>IN</sub> = V <sub>IL</sub> or V <sub>IH</sub> | Y <sub>D</sub> , Y <sub>1</sub> , Y <sub>2</sub><br>G, C <sub>n+4</sub><br>C <sub>i+4</sub> | Y <sub>2</sub> , Y <sub>3</sub> |                                   | 2.4 |                 |       | Volts    |  |

| ·on                                     |                                          | AIM - AIT OL AIM                                                               | P. FULL.                                                                                    |                                 | I <sub>OH</sub> = -1.2mA          | 2.4 |                 |       |          |  |

|                                         |                                          |                                                                                |                                                                                             |                                 | I <sub>OL</sub> = 20mA<br>(COM'L) |     |                 | 0.5   |          |  |

|                                         |                                          |                                                                                | Y <sub>0</sub> , Y <sub>1</sub> , Y                                                         | 2, Y3                           | I <sub>OL</sub> = 16mA (MIL)      |     |                 | 0.5   | l        |  |

| V <sub>OL</sub>                         | Output LOW Voltage                       | V <sub>CC</sub> = MIN<br>V <sub>IN</sub> = V <sub>IL</sub> or V <sub>IH</sub>  | G, Cn + 4                                                                                   | C <sub>i + 4</sub>              | I <sub>OL</sub> = 16mA            |     |                 | 0.5   | Volts    |  |

| 01                                      |                                          |                                                                                | P, FULL<br>EMPTY                                                                            |                                 | I <sub>OL</sub> = 12mA            |     |                 | 0.5   |          |  |

| ViH                                     | Input HIGH Level (Note 4)                |                                                                                |                                                                                             |                                 |                                   | 2.0 |                 |       | Volts    |  |

| VIL                                     | Input LOW Level (Note 4)                 |                                                                                |                                                                                             |                                 |                                   |     |                 | 0.8   | Volts    |  |

| VI                                      | Input Clamp Voltage                      | V <sub>CC</sub> = MIN, I <sub>IN</sub> = -18mA                                 |                                                                                             |                                 |                                   |     |                 | -1.5  | Volts    |  |

| • • • • • • • • • • • • • • • • • • • • | Input LOW Current                        | D <sub>0-3</sub>                                                               |                                                                                             |                                 |                                   |     |                 | 360   |          |  |

|                                         |                                          | V <sub>CC</sub> = MAX, V <sub>IN</sub> = 0.5V                                  |                                                                                             | 10-4,<br>CP, C                  | RE, IEN,<br>DE                    |     |                 | 702   |          |  |

| I <sub>IL</sub>                         |                                          |                                                                                |                                                                                             | CC                              |                                   |     |                 | 657   | 31<br>25 |  |

|                                         |                                          |                                                                                |                                                                                             | Ci                              |                                   |     |                 | -2.31 |          |  |

|                                         |                                          |                                                                                |                                                                                             | Cn                              |                                   |     |                 | -3.25 |          |  |

|                                         |                                          |                                                                                |                                                                                             | D <sub>0-3</sub>                |                                   |     |                 | 20    | 0        |  |

|                                         |                                          |                                                                                |                                                                                             | I <sub>0-4</sub> ,<br>CP, 0     | RE, IEN,<br>DE                    |     |                 | 40    | 40 μA    |  |

| liн                                     | Input HIGH Current                       | V <sub>CC</sub> = MAX, V <sub>IN</sub>                                         | = 2.7V                                                                                      | CC                              |                                   |     |                 | 50    | ] ‴      |  |

|                                         |                                          | C <sub>i</sub>                                                                 |                                                                                             | Ci                              |                                   |     |                 | 90    |          |  |

|                                         | •                                        |                                                                                |                                                                                             |                                 |                                   |     | 250             |       |          |  |

| l <sub>i</sub>                          | Input HIGH Current                       | V <sub>CC</sub> = MAX, V <sub>IN</sub>                                         | = 5.5V                                                                                      |                                 |                                   |     |                 | 1.0   | m/       |  |

| Isc                                     | Output Short Circuit<br>Current (Note 3) | V <sub>CC</sub> = MAX                                                          |                                                                                             |                                 |                                   | -30 |                 | -85   | m/       |  |

| lozi                                    | , , , , , , , , , , , , , , , , , , ,    | Voc = MAY                                                                      |                                                                                             |                                 | T = 0.5V                          |     |                 | -50   | _ μ      |  |

| lozh                                    | Output OFF Current                       | $\frac{V_{CC}}{OE} = MAX,$<br>OE = 2.4V                                        | Y <sub>0-3</sub>                                                                            | Vou                             | T = 2.4V                          |     |                 | 50    | <u>μ</u> |  |

| ·02n                                    |                                          |                                                                                |                                                                                             |                                 | -55 to +125°C                     |     | 1               | 239   | 4        |  |

|                                         |                                          |                                                                                |                                                                                             | T <sub>C</sub> =                | + 125°C                           | ļ   | <u> </u>        | 170   | mA.      |  |

| 1cc                                     | Power Supply Current (Note 5)            | V <sub>CC</sub> = MAX                                                          |                                                                                             |                                 | 0 to 70°C                         |     |                 | 220   | - '''′   |  |

|                                         |                                          | 1                                                                              |                                                                                             | TA=                             | 70°C                              |     |                 | 185   |          |  |

1. Typical limits are at V<sub>CC</sub> = 5.0V, 25°C ambient and maximum loading.

2. For conditions shown as MIN or MAX, use the appropriate value specified under Operating Ranges for the applicable device type.

3. Not more than one output should be shorted at a time. Duration of the short circuit test should not exceed one second.

4. These input levels provide no guaranteed noise immunity and should only be tested in a static-, noise-free environment.

5. Minimum loc is at maximum temporature.

5. Minimum ICC is at maximum temperature.

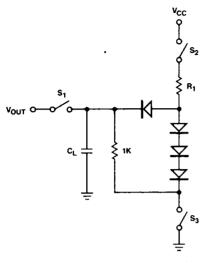

# SWITCHING TEST CIRCUIT

## A. THREE STATE OUTPUTS

## **B. NORMAL OUTPUTS**

TCR01350

$$R_1 = \frac{5.0 - V_{BE} - V_{OL}}{I_{OL} + V_{OL}/1K}$$

$$R_2 = \frac{2.4V}{I_{OH}}$$

$$R_1 = \frac{5.0 - V_{BE} - V_{OL}}{I_{OL} + V_{OL}/R_2}$$

Notes: 1.  $C_L = 50pF$  includes scope probe, wiring and stray capacitances without device in test fixture.

2.  $S_1$ ,  $S_2$ ,  $S_3$  are closed during function tests and all AC tests except output enable tests.

S<sub>1</sub> and S<sub>3</sub> are closed while S<sub>2</sub> is open for tp<sub>ZH</sub> test.

S<sub>1</sub> and S<sub>2</sub> are closed while S<sub>3</sub> is open for tp<sub>ZL</sub> test.

4. C<sub>1</sub> - 5.0pF for output disable tests.

## **TEST OUTPUT LOADS FOR Am2930**

| Pin#<br>(DIP) | Pin Label          | Test<br>Circuit | R <sub>1</sub> | R <sub>2</sub> |

|---------------|--------------------|-----------------|----------------|----------------|

| 2             | FULL               | В               | 300            | 2K             |

| 3             | EMPTY              | В               | 300            | 2K             |

| 6             | C <sub>i + 4</sub> | В               | 240            | 1.5K           |

| B-11          | Y <sub>0-3</sub>   | Α               | 240            | 1K             |

| 12            | G                  | В               | 240            | 1.5K           |

| 13            | C <sub>n + 4</sub> | В               | 240            | 1.5K           |

| 16            | P                  | В               | 300            | 2K             |

For additional information on testing, see section "Guidelines on Testing Am2900 Family Devices."

# **Am2930 SWITCHING CHARACTERISTICS**

Tables A, B, C and D define the timing characteristics of the Am2930. Measurements are made at 1.5V with  $V_{\rm IL}$  = 0V and  $V_{\rm IH}$  = 3.0V. For three-state disable tests,  $C_{\rm L}$  = 5.0pF and measurement is to 0.5V change on output voltage level.

# I. GUARANTEED PERFORMANCE OVER COMMERCIAL OPERATING RANGE

$V_{CC} = 4.75$  to 5.25V,  $T_A = 0$  to 70°C

# TABLE IA Clock Characteristics.

| Minimum | Clock | LOW  | Time | 31ns |

|---------|-------|------|------|------|

| Minimum | Clock | HIGH | Time | 33ns |

# All in ns. C<sub>L</sub> = 5.0pF for output disable tests.

| From                           | То | Enable | Disable |

|--------------------------------|----|--------|---------|

| ŌĒ                             | Υ  | 27     | 26      |

| CC<br>(Note 1)                 | Υ  | 55     | 37      |

| l <sub>4 = 0</sub><br>(Note 1) | Υ  | 80     | 55      |

TABLE IB

Output Enable/Disable Times.

Note 1: "Suspend" instruction.

# TABLE IC Combinational Propagation Delays. All in ns. Outputs fully loaded. $C_L = 50 pF$ .

|               |             | To Output |                    |                                          |                                          |      |       |  |  |  |  |

|---------------|-------------|-----------|--------------------|------------------------------------------|------------------------------------------|------|-------|--|--|--|--|

| From<br>Input | Υ           | G, P      | C <sub>n + 4</sub> | C <sub>1 + 4</sub><br>1 <sub>4</sub> = L | C <sub>i + 4</sub><br>I <sub>4</sub> = H | Full | Empty |  |  |  |  |

| 14-0          | 81          | 67        | 77                 | 80                                       | 91                                       | 69   |       |  |  |  |  |

| CC            | <b>.</b> 63 | 45        | 55                 | _                                        | 72                                       | 42   |       |  |  |  |  |

| Cn            | 32          | -         | 25                 | -                                        | 45                                       | -    |       |  |  |  |  |

| Ci            | _           | -         | -                  | 22                                       | 22                                       | -    |       |  |  |  |  |

| CP            | 69          | 53        | 61                 | 43                                       | 78                                       | 55   | 55    |  |  |  |  |

| D             | 49          | 33        | 40                 | -                                        | 59                                       |      |       |  |  |  |  |

| ĪĒÑ           | -           | _         |                    | _                                        | _                                        | 40   |       |  |  |  |  |

# TABLE ID Set-up and Hold Times. All in ns. All relative to clock LOW-to-HIGH transition.

|                                               | CP:            |              |

|-----------------------------------------------|----------------|--------------|

| Input                                         | Set-up<br>Time | Hold<br>Time |

| 14-0                                          | 114            | 0            |

| CC                                            | 75             | 0            |

| ĪĒN                                           | 55             | 0            |

| Cn                                            | 43             | 0            |

| Ci                                            | 32             | 5            |

| D (RE = L<br>I <sub>4-0</sub> = 0-8 or 10-15) | 25             | 2            |

| RE                                            | 24             | 4            |

# II. GUARANTEED PERFORMANCE OVER MILITARY OPERATING RANGE

$V_{CC} = 4.5$  to 5.5V,  $T_{C} = -55$  to  $+125^{\circ}C$

# TABLE IIA Clock Characteristics.

| Minimum | Clock | LOW  | Time | 35ns |

|---------|-------|------|------|------|

| Minimum | Clock | HIGH | Time | 35ns |

# TABLE IIC Combinational Propagation Delays. All in ns. Outputs fully loaded. C<sub>L</sub> = 50pF.

|               |    | To Output |                    |                                          |                                          |      |       |

|---------------|----|-----------|--------------------|------------------------------------------|------------------------------------------|------|-------|

| From<br>Input | γ  | G, P      | C <sub>n + 4</sub> | C <sub>i + 4</sub><br>I <sub>4</sub> = L | C <sub>I + 4</sub><br>I <sub>4</sub> = H | Full | Empty |

| 14-0          | 88 | 74        | 82                 | 87                                       | 97                                       | 78   | -     |

| CC            | 68 | 52        | 60                 | -                                        | 78                                       | 47   | _     |

| Cn            | 37 | _         | 30                 | _                                        | 46                                       | -    | -     |

| Ci            |    | -         | _                  | 23                                       | 23                                       |      | -     |

| СР            | 74 | 58        | 66                 | 48                                       | 84                                       | 60   | 60    |

| D             | 55 | 38        | 45                 | _                                        | 65                                       | _    |       |

| ĪĒÑ           | -  | -         | -                  | -                                        |                                          | 45   | _     |

# TABLE IIB Output Enable/Disable Times.

All in ns.  $C_1 = 5.0 pF$  for output disable tests.

| From                           | To | Enable | Disable |

|--------------------------------|----|--------|---------|

| ŌĒ                             | Υ  | 32     | 31      |

| CC<br>(Note 1)                 | Y  | 60     | 42      |

| l <sub>4 - 0</sub><br>(Note 1) | Υ  | 85     | 60      |

Note 1: "Suspend" instruction.

# TABLE IID Setup and Hold Times. All in ns. All relative to clock LOW-to-HIGH transition.

|                                               | CP:            |              |

|-----------------------------------------------|----------------|--------------|

| Input                                         | Set-up<br>Time | Hold<br>Time |

| 14-0                                          | 124            | 0            |

| CC                                            | 80             | 0            |

| ĪĒN                                           | 69             | 0            |

| Cn                                            | 52             | 0            |

| Ci                                            | 37             | 5            |

| D (RE = L<br>I <sub>4-0</sub> = 0-8 or 10-15) | 30             | 2            |

| D (All other conditions)                      | 72             | 2            |

| RE                                            | 29             | 4            |

## **Notes on Testing**

Incoming test procedures on this device should be carefully planned, taking into account the high complexity and power levels of the part. The following notes may be useful:

- Insure the part is adequately decoupled at the test head.

Large changes in V<sub>CC</sub> current when the device switches may cause erroneous function failures due to V<sub>CC</sub> changes.

- 2. Do not leave inputs floating during any tests, as they may start to oscillate at high frequency.

- Do not attempt to perform threshold tests at high speed.

Following an input transition, ground current may change by as much as 400mA in 5-8ns. Inductance in the ground

cable may allow the ground pin at the device to rise by 100s of millivolts momentarily.

- 4. Use extreme care in defining input levels for AC tests. Many inputs may be changed at once, so there will be significant noise at the device pins and they may not actually reach  $V_{IL}$  or  $V_{IH}$  until the noise has settled. AMD recommends using  $V_{IL} \leqslant 0V$  and  $V_{IH} \geqslant 3.0V$  for AC tests.

- To simplify failure analysis, programs should be designed to perform DC, Function, and AC tests as three distinct groups of tests.

- To assist in testing, AMD offers complete documentation on our test procedures and, in most cases, can provide Fairchild Sentry programs, under license.

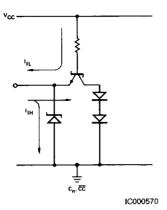

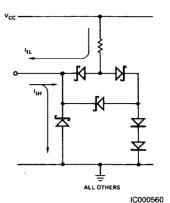

# INPUT/OUTPUT CURRENT INTERFACE CONDITIONS Driven Inputs

Note: C<sub>i</sub> input is connected to both configurations in parallel.

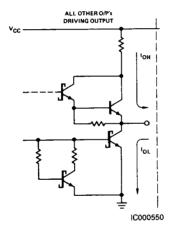

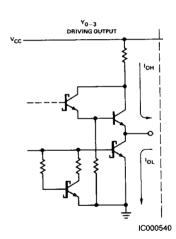

# **Driving Outputs**

Note: Actual current flow direction shown.

# **RELATED PRODUCTS**

| Part No. | Description                   |

|----------|-------------------------------|

| Am2902A  | Carry Look-Ahead Generator    |

| Am2904   | Status and Shift Control Unit |

| Am2920   | 8-Bit Register                |

| Am2922   | Condition Code MUX            |

For applications information, see Chapter V of Bit Slice Microprocessor Design, Mick & Brick, McGraw Hill Publications.