# Highly Integrated Photo Flash Charger and IGBT Driver

# **DESCRIPTION**

The MP3360 is a fast, highly efficient and precision high voltage photo-flash charger for camera phone xenon flash.

The MP3360 has programmable peak currents of 1.5A/1.4A/1.3A/1.2A/1.1A/1.0A/0.9A/0.8A /0.75A/0.7A/0.65A/0.6A/0.55A/0.5A/0.45A/0.4A. A 60V,  $0.5\Omega$  internal power switch lowers transformer turns ratio and switching losses associated with the primary leakage inductance and winding capacitance. Integrated secondary feedback resistors provide +/-2.5% output voltage charge accuracy. MP3360 also has an integrated IGBT driver with a regulated 2.7V gate voltage.

MP3360 is available in the 10-pin, 2X2 flip chip package.

# **FEATURES**

- Integrated 60V, 0.5Ω Power Switch

- Single wire digital interface for current limit programming.

- 2.5% Charge Accuracy

- <1uA Shutdown Current</li>

- Integrated IGBT Driver with Regulated Gate Voltage

# **APPLICATIONS**

- Mobile Phones with Xeon Flash

- Digital Still Cameras

- Optical Film Cameras

- PDAs with Xeon Flash

"MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

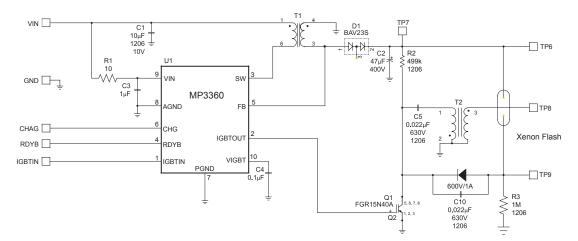

# TYPICAL APPLICATION

# ORDERING INFORMATION

| Part Number* | Package              | Top Marking | Free Air Temperature (T <sub>A</sub> ) |

|--------------|----------------------|-------------|----------------------------------------|

| MP3360       | 10-pin, 2x2 Flip QFN | 4KY         | -40°C to +85°C                         |

For Tape & Reel, add suffix –Z (e.g. MP3360DG–Z); For RoHS Compliant Packaging, add suffix –LF(e.g. MP3360DG–LF–Z)

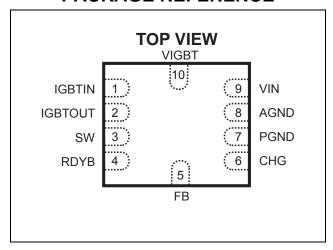

### PACKAGE REFERENCE

# **ABSOLUTE MAXIMUM RATINGS (1)**

| V <sub>IN</sub> to GNDCHG, IGBTIN, IGBTOUT, VIGB |                                        |

|--------------------------------------------------|----------------------------------------|

| RDYB to AGND                                     | 0.3Vto 6V                              |

| FB to AGND                                       | 60V to 350V                            |

| SW to AGND                                       | 0.3V to 60V                            |

| PGND to AGND                                     | 0.3V to +0.3V                          |

| 2X2, 10 pin Flip Chip Thermal R                  | esistance                              |

| <b>Operating Temperature Ranges</b>              |                                        |

|                                                  | -20°C to +85°C                         |

| Storage Temperature                              | ·55°C to +150°C                        |

| Junction Temperature                             | +150°C                                 |

| Continuous Power Dissipation (                   | Γ <sub>A</sub> = +25°C) <sup>(2)</sup> |

|                                                  | 1.6W                                   |

| Lead Temperature (Solder)                        | +260°C                                 |

| Recommended Operating Conditions (3)    |                         |                         |       |

|-----------------------------------------|-------------------------|-------------------------|-------|

| Supply Voltage V <sub>IN</sub>          | -                       | 2.5V                    | to 6V |

| Operating Junct. Temp (T <sub>J</sub> ) | 40°                     | C to +                  | 125°C |

| Thermal Resistance (4)                  | $oldsymbol{	heta}_{JA}$ | $oldsymbol{	heta}_{JC}$ |       |

| 2x2 Flip Chip                           | 80                      | 16                      | .°C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-to-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) = ( $T_J$  (MAX)- $T_A$ )/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

$V_{IN} = V$  (CHG) = 3.6V,  $T_A = +25$ °C, unless otherwise noted.

| Parameter                              | Conditions                                               | Min | Тур | Max | Unit |

|----------------------------------------|----------------------------------------------------------|-----|-----|-----|------|

| Photoflash Capacitor Charger           |                                                          |     |     |     |      |

| V <sub>IN</sub> Voltage Range          |                                                          | 2.5 |     | 6   | V    |

| V <sub>IN</sub> UVLO                   | Rising edge, hysteresis = 200mV typical                  |     |     | 2.5 | V    |

| V <sub>IN</sub> Quiescent Current      | V(CHG)=High, V(SW) = 0                                   |     | 1   | 2   | mA   |

| V <sub>IN</sub> Quiescent Current      | V(CHG)=High, V(FB) = 325V                                |     |     | 150 | μΑ   |

| Shutdown Current from V <sub>IN</sub>  | V(CHG)=Low, V <sub>IN</sub> =3.6V                        |     |     | 1   | μΑ   |

| V <sub>SW</sub> Leakage Current        | V <sub>IN</sub> =3.6V, V <sub>SW</sub> =60V, in Shutdown |     |     | 1   | μΑ   |

| SW ON Resistance between SW and GND    | Switch turn-on                                           |     | 0.5 |     | Ω    |

| Pull-down Resistance of CHG pin        | V(CHG)=3.6V                                              |     | 100 |     | kΩ   |

| IPEAK1                                 | Program for Highest Current Limit                        | 1.3 | 1.5 | 1.7 | Α    |

| IPEAK2                                 | Program for Lowest Current Limit                         |     | 0.4 | 0.6 | Α    |

| Charge completion detect voltage at FB |                                                          | 290 | 298 | 308 | ٧    |

| FB Resistance                          | V(FB)=30V                                                |     | 303 |     | kΩ   |

| DCM Comparator threshold               |                                                          |     | 5   |     | V    |

| RDYB Leakage Current                   | V(RDYB)=3.6V                                             |     |     | 0.1 | μΑ   |

| RDYB Output Low Voltage                | ISINK= 2mA                                               |     | 0.2 |     | V    |

| MAX TON                                | Maximum TON time                                         |     | 70  | 120 | μS   |

| Thermal Shutdown                       | Rising edge, hysteresis = 15°C                           |     | 150 |     | °C   |

| Charge Input High Voltage              |                                                          | 2.4 |     |     | V    |

| Charge Input Low Voltage               |                                                          |     |     | 0.6 | V    |

| t <sub>HI</sub>                        |                                                          | 0.1 |     |     | μS   |

| $t_LO$                                 |                                                          | 0.1 |     |     | μS   |

| t <sub>EN delay</sub>                  |                                                          | 30  |     |     | μS   |

| t <sub>PW</sub>                        | Vin=2.7V-5.5V                                            |     |     | 60  | μS   |

# **PIN FUNCTIONS**

| Pin | Name    | Function                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | IGBTIN  | Logic Input Pin for IGBT Drive.                                                                                                                                                                                                                                                                                                                                                                                          |

| 2   | IGBTOUT | Output Drive for IGBT Gate. Connect this pin to the gate of the IGBT.                                                                                                                                                                                                                                                                                                                                                    |

| 3   | SW      | Switch Pin. This is the drain of the internal power switch.                                                                                                                                                                                                                                                                                                                                                              |

| 4   | RDYB    | Open-Drain Power-Ready Output. RDYB becomes low when the output voltage is reached.                                                                                                                                                                                                                                                                                                                                      |

| 5   | FB      | Feedback Pin. Its trip voltage is 298V                                                                                                                                                                                                                                                                                                                                                                                   |

| 6   | CHG     | Charge Enable Pin. A low to high transition on this pin puts the part into power delivery mode. Once the target voltage is reached, the part will stop charging the output. Toggle this pin will start charging again. Bring this pin low will terminate the power delivery and put the part in shutdown. This pin can be also used to program the peak current regulation. See the description for current programming. |

| 7   | PGND    | Power Ground                                                                                                                                                                                                                                                                                                                                                                                                             |

| 8   | AGND    | Analog ground. Tie it directly to local ground plane.                                                                                                                                                                                                                                                                                                                                                                    |

| 9   | VIN     | Input Supply Pin. Connect it to system supply voltage. Bypass VIN to GND with a 0.1uF or greater ceramic capacitor.                                                                                                                                                                                                                                                                                                      |

| 10  | VIGBT   | 2.7V LDO output. VIGBT is the supply voltage for IGBT gate driver. Bypass VIGBT with 0.1uF cap to GND.                                                                                                                                                                                                                                                                                                                   |

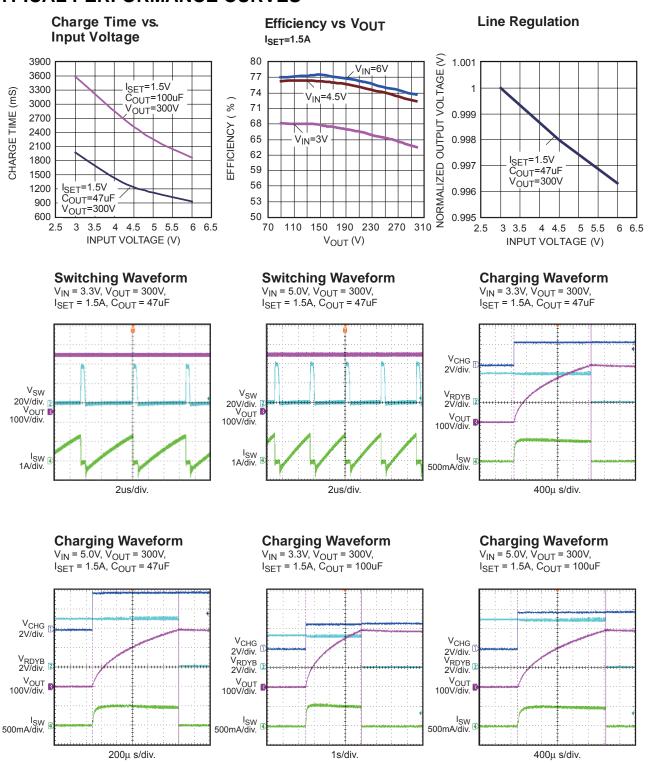

# TYPICAL PERFORMANCE CURVES

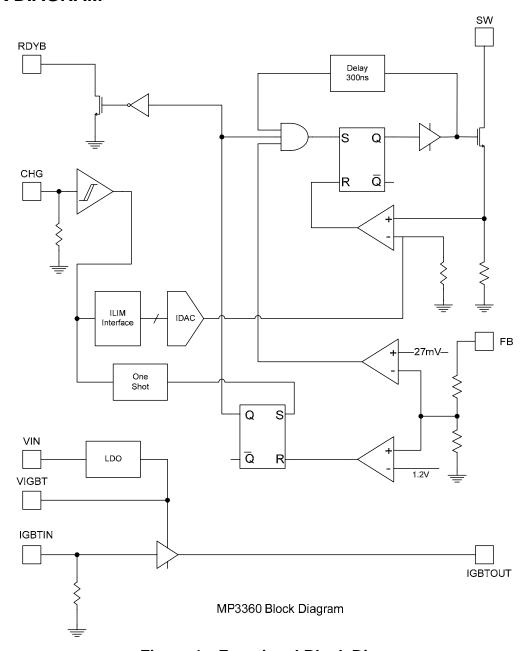

# **BLOCK DIAGRAM**

Figure 1—Functional Block Diagram

#### **OPERATION**

The MP3360 controlled flyback charger operates in critical conduction mode with peak current set by the CHG pin. The output voltage is divided down through internal 300: 1 resistive divider from the positive terminal of the transformer secondary (FB pin) and compares it with the internal 1.2V reference. The low to high transition of the CHG pin will enable the flyback converter to switch.

A constant T<sub>OFF</sub> of 20µs is used when the output voltage is below 20V to avoid inrush The boundary mode operation will follow to minimize charge time when the output voltage is above 20V. A minimum T<sub>OFF</sub> of 200ns serves as blanking for turn off transition. The circuit will stop switching and RDYB will be pulled low once the flash capacitor is charged to 300V, a value set by the internal 300:1 R divider and 1.2V reference. VIGBT will be regulated to 2.7V. When the charge is full. then part will shut down its internal circuitry with less than 1uA drawn from V<sub>IN</sub>. Toggling the CHG pin will restart charge cycle. Bringing the CHG pin low terminates the power delivery and put the part in shutdown. A maximum T<sub>ON</sub> timer prevents pulling current from a depleted battery. If the ON time exceeds maximum T<sub>ON</sub>, the switch is forced OFF regardless of the IPEAK detection.

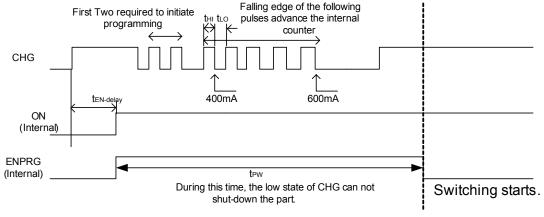

#### CURRENT LIMIT PROGRAMMING

The current limit can be programmed using the CHG pin. After asserting the CHG, it should be held high for at least 30us. After that, it takes two pulses to enter the programming mode. In the programming mode, each pulse advances the internal counter to the next higher current limit by 50mA until 750mA is reached and by 100mA increments beyond 750mA. The first pulse is for 400mA current limit. The next pulse will set the current limit to 450mA, etc. This programming should be done within 60us. Otherwise, the programming pulses will be ignored after the programming window expires. When you have advanced to the desired current limit setting, the high state should be held to make the part switch with the set current limit. To set the current limit to 1.5A (highest possible), the previous procedure is not necessary. Asserting and holding high the CHG pin will make the part switches with a 1.5A current limit. See the following timing diagram for detailed timing information.

ILIM Programming Timing Diagram (600mA Current Limit)

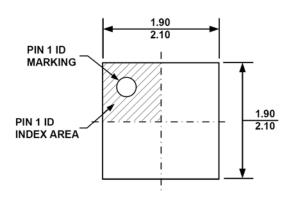

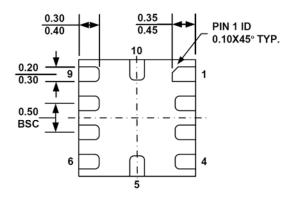

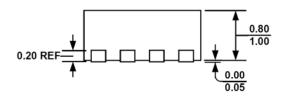

# **PACKAGE INFORMATION**

# **QFN10 (2mm x 2mm)**

**TOP VIEW**

**BOTTOM VIEW**

**SIDE VIEW**

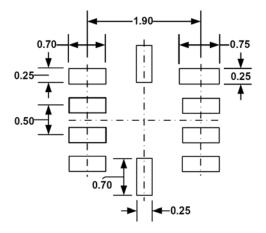

RECOMMENDED LAND PATTERN

#### NOTE:

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) EXPOSED PADDLE SIZE DOES NOT INCLUDE MOLD FLASH.

- 3) LEAD COPLANARITY SHALL BE 0.10 MILLIMETER MAX.

- 4) JEDEC REFERENCE IS MO-220, VARIATION VCCD.

- 5) DRAWING IS NOT TO SCALE.

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.