## CLM1100

### 多通道工业以太网从站控制器

#### 产品参数

- 工作范围

- 内部 LDO 提供逻辑内核/PLL 电源 (5V/3.3V 到 1.8V)

- 选择外部电源供电给内部 LDO 提供逻辑内核/PLL 电源。

- 以太网端口数量 : 2-4 端口 ( 每个可配置成 LVDS 接口或者 MII 接口 )

- FMMUs 数量 : 8

- 同步管理 SM ( SyncManager ) 数量 : 8

- RAM 容量 : 8 Kbyte

- 集成分布时钟 DC ( Distributed Clock ) : 有 , 64 bit

- 过程数据接口 PDI ( Process Data Interface ) :

- 32Bit 的数字量 I/O 信号接口(单向的/双向的)

- SPI 从站接口

- 8/16 同步/异步微处理器接口

- I/O : 3.3V

- 封装 : CLM1100 BGA128 (10×10 mm<sup>2</sup>)

- 其他 : 内部 1GHz PLL

#### 介绍

本芯片为实现工业以太网协议的从站控制器芯片。

工业以太网是一种实时工业以太网协议，它充分利用了以太网的全双工特性。使用主从模式介质访问控制 (MAC)，主站发送以太网帧给各从站，从站从数据帧中抽取数据或将数据插入数据帧。主站使用标准的以太网接口卡，从站使用专门的工业以太网从站控制器，即可使用本芯片。

本芯片在从站系统中主要负责处理工业以太网数据帧，并使用双端口存储区实现工业以太网主站与从站本地应用的数据交换。各个从站工业以太网从站控制器按照各自在环路上的物理位置顺序移位读写数据帧。在报文经过从站时，工业以太网从站控制器从报文中提取发送给自己的输出命令数据并将其存储到内部存储区，输入数据从内部存储区又被写到相应的子报文中。数据的提取和插入都是由工业以太网从站控制器完成。

## 描述

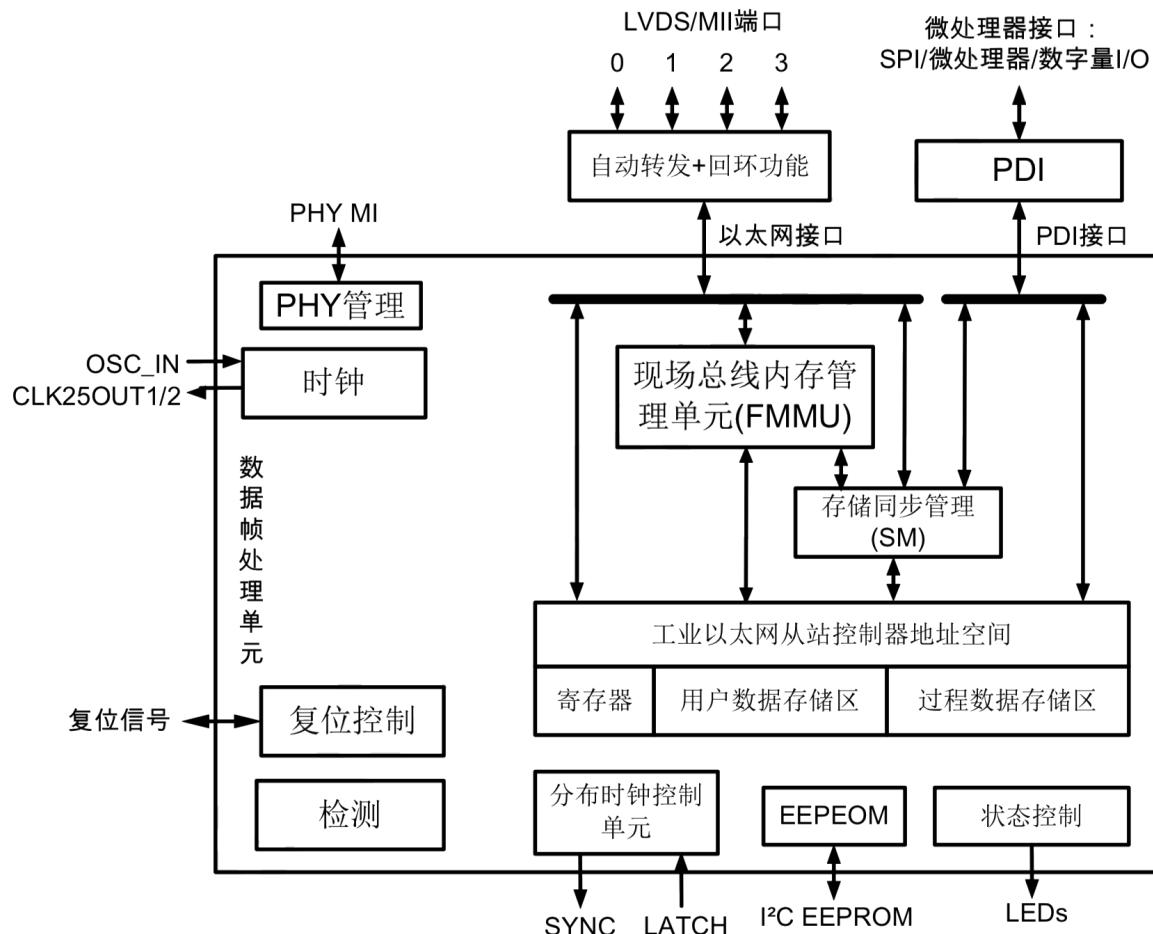

### 芯片模块框图

本芯片为工业以太网从站控制芯片，是实现工业以太网数据链路层协议的专用集成电路芯片。它处理工业以太网数据帧，并为从站控制装置提供数据接口。结构如下图：

图 2-1 结构框图

本芯片具有 4 个数据收发端口、8 个 FMMU 单元、8 个 SM 通道、4KB 控制寄存器、8KB 过程数据存储器、支持 64 位分布时钟功能。它可以直接作为 32 位数字量输入/输出站点，或由外部微处理器控制，组成复杂的从站设备。

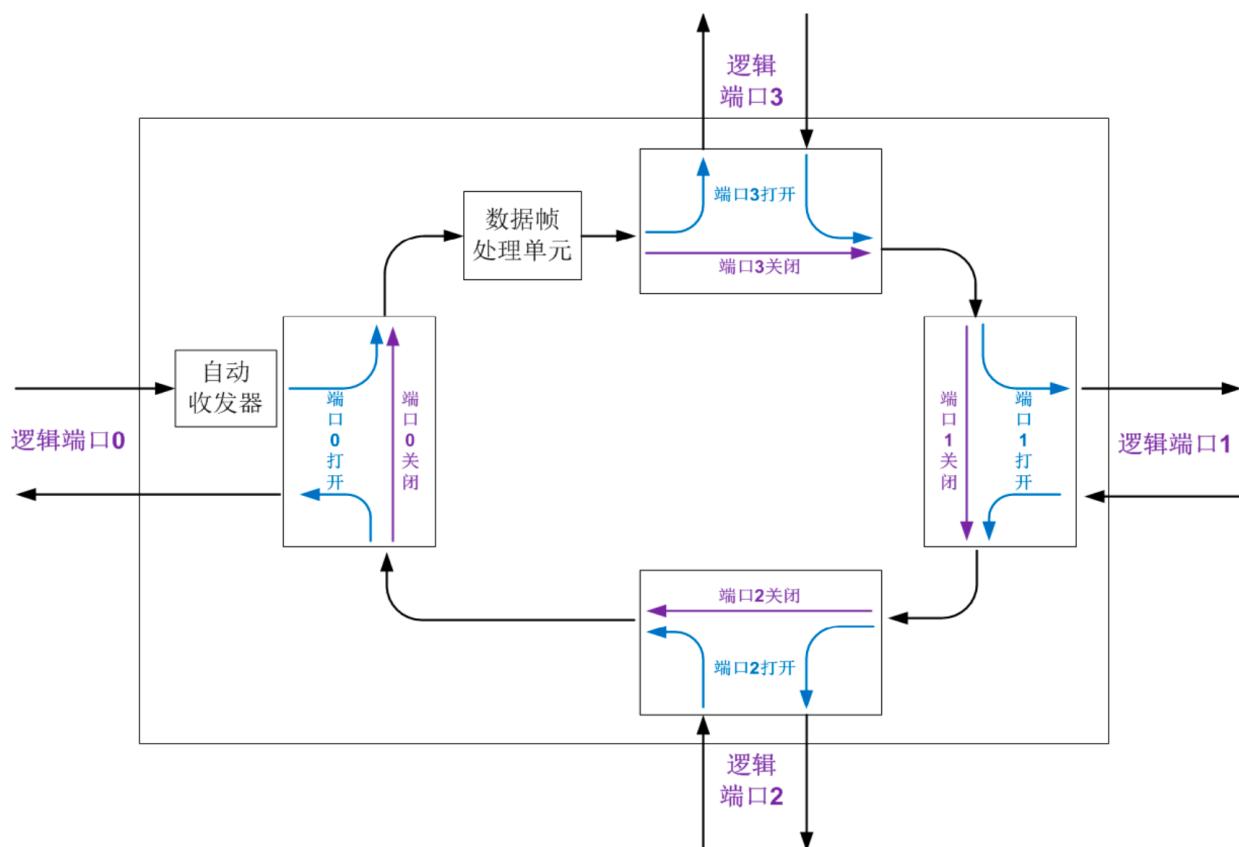

## 数据帧处理顺序

本芯片的数据帧处理顺序由 LVDS/MII 端口数量和芯片模式决定:

| LVDS/MII 端口数量 | 数据帧处理顺序                                                                                                   |

|---------------|-----------------------------------------------------------------------------------------------------------|

| 2             | 0 → 工业以太网数据帧处理单元 → 1 / 1 → 0                                                                              |

| 3             | 0 → 工业以太网数据帧处理单元 → 1 / 1 → 2 / 2 → 0 (逻辑端口 0,1, 2)或<br>0 → 工业以太网数据帧处理单元 → 3 / 3 → 1 / 1 → 0 (逻辑端口 0,1, 3) |

| 4             | 0 → 工业以太网数据帧处理单元 → 3 / 3 → 1 / 1 → 2 / 2 → 0                                                              |

表格 2-1 数据帧处理顺序

图 2-2 以太网从站控制内部数据帧传输顺序

## 模块概述

### 物理通信接口：

本芯片有 4 个物理通信端口，分别命名为端口 0 到端口 3，每个端口都可以配置为 MII 接口或LVDS 接口两种形式。

MII 接口：使用此接口时，需要外接以太网物理层 PHY 芯片。

LVDS 接口：使用低压差分信号，最远传输距离为 10 米。

### PDI 接口：

支持直接 IO 信号接口、SPI 接口、并行/串行微处理器接口。

### 以太网从站控制器数据帧处理单元：

每个以太网从站控制器可以最多支持 4 个数据收发端口，每个端口都可以处在打开或闭合状态。如果端口打开，则可以向其他以太网从站控制器发送数据帧或从其他以太网从站控制器接收数据帧。一个闭合的端口不会与其他以太网从站控制器交换数据帧，它在内部将数据帧转发到下一个逻辑端口，直到数据帧到达一个打开的端口。

### 存储同步管理

以太网从站控制器使用了存储同步管理通道 SM ( SyncManager ) 来保证主站与本地应用数据交换的一致性和安全性，并在数据状态改变时产生中断来通知双方。

### 现场总线内存管理单元 ( FMMU )

FMMU 将从站本地物理存储地址映射到网段内逻辑地址。实现从站在 4GB (  $2^{32}$  ) 地址空间的逻辑寻址，报文内的 32 位地址区作为整体的数据逻辑寻址的地址。

### 分布时钟

分布时钟 ( DC , Distributed Clock ) 可以使所有工业以太网设备使用相同的系统时间，从而控制设备任务的同步执行。从站设备可以根据同步的系统时间产生同步信号，用于中断控制或触发数据量输入输出。

## 引脚分配

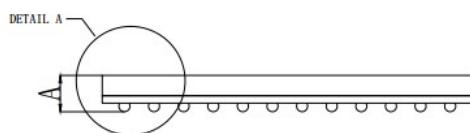

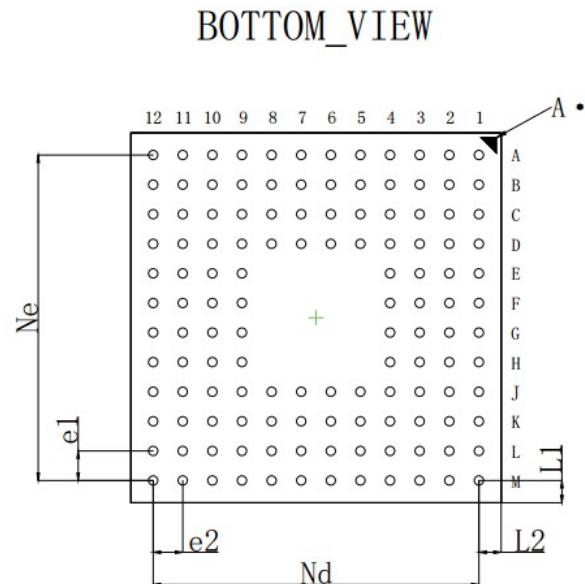

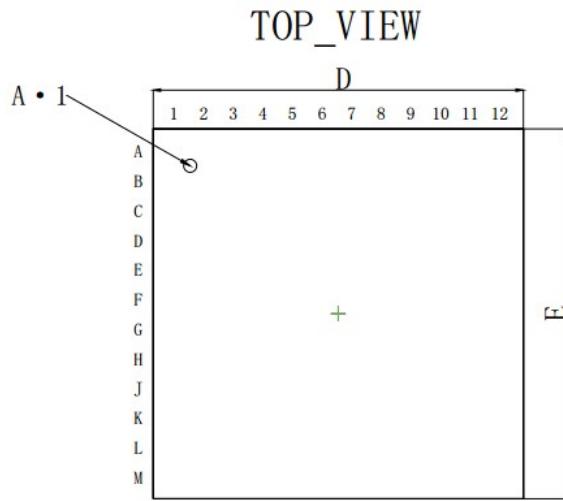

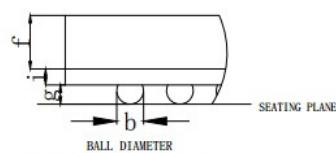

### BGA128 封装

#### 引脚排布

CLM1100 采用了 BGA128 封装。BGA128 封装引脚分布如图 3-1 所示，引脚名称如表 3-1 所示，共有 128 个引脚。

|    |    |    |    |    |    |    |    |    |     |     |     |

|----|----|----|----|----|----|----|----|----|-----|-----|-----|

| A1 | A2 | A3 | A4 | A5 | A6 | A7 | A8 | A9 | A10 | A11 | A12 |

| B1 | B2 | B3 | B4 | B5 | B6 | B7 | B8 | B9 | B10 | B11 | B12 |

| C1 | C2 | C3 | C4 | C5 | C6 | C7 | C8 | C9 | C10 | C11 | C12 |

| D1 | D2 | D3 | D4 | D5 | D6 | D7 | D8 | D9 | D10 | D11 | D12 |

| E1 | E2 | E3 | E4 |    |    |    |    | E9 | E10 | E11 | E12 |

| F1 | F2 | F3 | F4 |    |    |    |    | F9 | F10 | F11 | F12 |

| G1 | G2 | G3 | G4 |    |    |    |    | G9 | G10 | G11 | G12 |

| H1 | H2 | H3 | H4 |    |    |    |    | H9 | H10 | H11 | H12 |

| J1 | J2 | J3 | J4 | J5 | J6 | J7 | J8 | J9 | J10 | J11 | J12 |

| K1 | K2 | K3 | K4 | K5 | K6 | K7 | K8 | K9 | K10 | K11 | K12 |

| L1 | L2 | L3 | L4 | L5 | L6 | L7 | L8 | L9 | L10 | L11 | L12 |

| M1 | M2 | M3 | M4 | M5 | M6 | M7 | M8 | M9 | M10 | M11 | M12 |

图 3-1 BGA128 封装引脚分布

## 引脚名称

| 引脚  | 引脚名称                           | 方向     | 引脚  | 引脚名称                         | 方向    |

|-----|--------------------------------|--------|-----|------------------------------|-------|

| A1  | PDI[27]/RX_DV(3)/LVDS(3)-RX-   | BD/LI- | G1  | PDI[35]/RX_ERR(2)            | BD    |

| A2  | PDI[26]/TX_ENA(3)/LVDS(3)-TX+  | BD/LO+ | G2  | PDI[36]/RX_CLK(2)            | BD    |

| A3  | PDI[24]/TX_D(3)[1]/LVDS(3)-TX- | BD/LO- | G3  | Res. [1]                     | I     |

| A4  | PDI[22]/TX_D(3)[3]             | BD     | G4  | Res. [2]                     | I     |

| A5  | PDI[20]/RX_D(3)[3]             | BD     | G9  | GNDPLL                       |       |

| A6  | PDI[18]/RX_D(3)[0]             | BD     | G10 | Vcc PLL                      |       |

| A7  | PDI[16]/RX_ERR(3)              | BD     | G11 | EEPROM_CLK                   | BD    |

| A8  | PDI[14]                        | BD     | G12 | OSC_IN                       | I     |

| A9  | PDI[12]                        | BD     | H1  | RX_DV(2)/LVDS(2)-RX-         | I/LI- |

| A10 | PDI[10]                        | BD     | H2  | PDI[37]/RX_D(2)[0]           | BD    |

| A11 | PDI[8]                         | BD     | H3  | TESTMODE                     | I     |

| A12 | PDI[6]                         | BD     | H4  | GNDI/O (T1)                  |       |

| B1  | PDI[29]/RX_D(3)[1]/LVDS(3)-RX+ | BD/LI+ | H9  | Vcc I/O (T3)                 |       |

| B2  | PDI[28]/PERR(3)/TRANS(3)       | BD     | H10 | Res. [5]                     | I     |

| B3  | PDI[25]/TX_D(3)[0]             | BD     | H11 | RUN/EEPROM_SIZE              | BD    |

| B4  | PDI[23]/TX_D(3)[2]             | BD     | H12 | RESET                        | BD    |

| B5  | PDI[21]/LINK_MII(3)            | BD     | J1  | RX_D(2)[1]/LVDS(2)-RX+       | I/LI+ |

| B6  | PDI[19]/RX_D(3)[2]             | BD     | J2  | PDI[38]/RX_D(2)[2]           | BD    |

| B7  | PDI[17]/RX_CLK(3)              | BD     | J3  | Vcc I/O                      |       |

| B8  | PDI[15]                        | BD     | J4  | GNDI/O                       |       |

| B9  | PDI[13]                        | BD     | J5  | GNDI/O                       |       |

| B10 | PDI[9]                         | BD     | J6  | GNDCore                      |       |

| B11 | PDI[7]/CPU_CLK                 | BD     | J7  | GNDCore                      |       |

| B12 | PDI[4]                         | BD     | J8  | GNDI/O                       |       |

| C1  | PDI[31]/CLK25OUT2              | BD     | J9  | GNDI/O                       |       |

| C2  | PDI[30]/LINKACT(3)/P_CONF(3)   | BD     | J10 | Vcc I/O                      |       |

| C3  | PERR(2)/TRANS(2)/PHYAD_OFF     | BD     | J11 | PERR(0)/TRANS(0)/CLK_MODE[0] | BD    |

| C4  | RBIAS                          |        | J12 | LINKACT(0)/P_CONF[0]         | BD    |

| C5  | Vcc I/O                        |        | K1  | PDI[39]/RX_D(2)[3]           | BD    |

| C6  | VCC Core                       |        | K2  | PERR(1)/TRANS(1)/CLK_MODE(1) | BD    |

| C7  | VCC Core                       |        | K3  | LINK_MII(1)                  | I     |

| C8  | Res. [4]                       | I      | K4  | RX_CLK(1)                    | I     |

| C9  | PDI[11]                        | BD     | K5  | VCC I/O                      |       |

| C10 | PDI[5]                         | BD     | K6  | Vcc Core                     |       |

| C11 | PDI[3]                         | BD     | K7  | Vcc Core                     |       |

| C12 | PDI[2]                         | BD     | K8  | VCC I/O                      |       |

| D1  | PDI[32]/TX_D(2)[3]             | BD     | K9  | GNDI/O (T2)                  |       |

| D2  | PDI[33]/TX_D(2)[2]             | BD     | K10 | RX_D(0)[0]                   | I     |

| D3  | Vcc I/O                        |        | K11 | MI_CLK/LINKPOL               |       |

| D4  | GNDI/O                         |        | K12 | MI_DATA                      | BD    |

|     |                                     |        |     |                           |        |

|-----|-------------------------------------|--------|-----|---------------------------|--------|

| D5  | GND <sub>I/O</sub>                  |        | L1  | LINKACT(1)/P_CONF(1)      | BD     |

| D6  | GND <sub>Core</sub>                 |        | L2  | TX_D(1)[2]/P_MODE[0]      | BD     |

| D7  | GND <sub>Core</sub>                 |        | L3  | TX_D(1)[0]/TRANS_MODE_ENA | BD     |

| D8  | Res. [7]                            | I      | L4  | RX_D(1)[0]                | I      |

| D9  | GND <sub>I/O</sub>                  |        | L5  | RX_D(1)[2]                | I      |

| D10 | Vcc I/O                             |        | L6  | RX_ERR(1)                 | I      |

| D11 | PDI[1]                              | BD     | L7  | TX_D(0)[2]/C25_SHI[0]     | BD     |

| D12 | PDI[0]                              | BD     | L8  | TX_D(0)[0]/C25_ENA        | BD     |

| E1  | TX_D(2)[1]/LVDS(2)-TX-              | O/LO-  | L9  | LINK_MII(0)               | I      |

| E2  | PDI[34]/TX_D(2)[0]/CTRL_STATUS_MOVE | BD     | L10 | RX_CLK(0)                 | I      |

| E3  | LINKACT(2)/P_CONF[2]                | BD     | L11 | RX_D(0)[2]                | I      |

| E4  | Res. [0]                            | I      | L12 | RX_D(0)[3]                | I      |

| E9  | Vcc I/O                             |        | M1  | TX_D(1)[3]/P_MODE[1]      | BD     |

| E10 | Res. [3]                            | I      | M2  | TX_D(1)[1]/LVDS(1)-TX-    | O/LO-  |

| E11 | SYNC/LATCH[0]                       | BD     | M3  | TX_ENA(1)/LVDS(1)-TX+     | BD/LO+ |

| E12 | SYNC/LATCH[1]                       | BD     | M4  | RX_DV(1)/LVDS(1)-RX-      | I/LI+  |

| F1  | TX_ENA(2)/LVDS(2)-TX+               | BD/LO+ | M5  | RX_D(1)[1]/LVDS(1)-RX+    | I/LI+  |

| F2  | LINK_MII(2)/CLK25OUT1               | BD     | M6  | RX_D(1)[3]                | I      |

| F3  | Vcc I/O (T0)                        |        | M7  | TX_D(0)[3]/C25_SHI[1]     | BD     |

| F4  | Res. [6]                            | I      | M8  | TX_D(0)[1]/LVDS(0)-TX-    | O/LO-  |

| F9  | GND <sub>I/O</sub>                  |        | M9  | TX_ENA(0)/LVDS(0)-TX+     | BD/LO+ |

| F10 | Vcc I/O                             |        | M10 | RX_ERR(0)                 | I      |

| F11 | EEPROM_DATA                         | BD     | M11 | RX_DV(0)/LVDS(0)-RX-      | I/LI-  |

| F12 | OSC_OUT                             | O      | M12 | RX_D(0)[1]/LVDS(0)-RX+    | I/LI+  |

表格 3-1 BGA128 封装引脚名称

需要注意的是，CLM1100 在芯片使用时不要直接将这些引脚随意的接到电源地，应该按照下表中的方式连接，这些引脚如下：

| 位置  | 封装名称                    | 正常使用时处理方式     |

|-----|-------------------------|---------------|

| K9  | GND <sub>I/O</sub> (T2) | 接地或悬空         |

| H9  | VCC I/O(T3)             | 接 VCC I/O 或悬空 |

| E10 | Reserve[3]              | 接地或悬空(建议悬空)   |

| C8  | Reserve[4]              | 接地或悬空         |

| D8  | Reserve[7]              | 接地或悬空         |

| E4  | Reserve[0]              | 接地或悬空         |

| F3  | VCC I/O(T0)             | 接 VCC I/O 或悬空 |

| H4  | GND <sub>I/O</sub> (T1) | 接地或悬空         |

| G3  | Reserve[1]              | 接地或悬空(建议接地)   |

表格 3-2 BGA128 封装保留引脚

## 引脚功能及连接要求

| 信号                  | 类型     | 方向   | 功能描述                                    |

|---------------------|--------|------|-----------------------------------------|

| C25_ENA             | 配置     | I    | CLK25OUT2 使能: 使能 CLK25OUT2 输出           |

| C25_SHI[1:0]        | 配置     | I    | TX 信号 (发送信号) 相位偏移: MII TX 信号的转移/相位偏移    |

| CLK_MODE[1:0]       | 配置     | I    | CPU_CLK 配置                              |

| CLK25OUT1/CLK25OUT2 | MII    | O    | 工业以太网 PHY 的 25MHz 时钟源                   |

| CPU_CLK             | PDI    | O    | 微控制器的时钟信号                               |

| CTRL_STATUS_MOVE    | 配置     | I    | 转移数字 I/O 控制/状态信号到最后一个可用 PDI 字节          |

| LVDS(3:0)-RX-       | LVDS   | LI-  | 低电压差分接收信号负极                             |

| LVDS (3:0)-RX+      | LVDS   | LI+  | 低电压差分接收信号正极                             |

| LVDS (3:0)-TX-      | LVDS   | LO-  | 低电压差分发送信号负极                             |

| LVDS (3:0)-TX+      | LVDS   | LO+  | 低电压差分发送信号正极                             |

| EEPROM_CLK          | EEPROM | BD   | EEPROM 接口集成电路总线 (I <sup>2</sup> C) 通信时钟 |

| EEPROM_DATA         | EEPROM | BD   | EEPROM 接口 I <sup>2</sup> C 通信数据         |

| EEPROM_SIZE         | 配置     | I    | EEPROM 存储大小配置                           |

| PERR(3:0)           | LED    | O    | 端口接收错误指示灯(LED)输出 (用于测试)                 |

| GND <sub>Core</sub> | 电源     |      | 逻辑内核地                                   |

| GND <sub>I/O</sub>  | 电源     |      | I/O 地                                   |

| GND <sub>PLL</sub>  | 电源     |      | PLL 锁相环地                                |

| LINK_MII(3:0)       | MII    | I    | PHY 信号表示链接                              |

| LINKACT(3:0)        | LED    | O    | 链接/活动指示灯 (LED) 输出                       |

| LINKPOL             | 配置     | I    | LINK_MII(3:0)连接有效极性配置                   |

| MI_CLK              | MII    | O    | PHY 管理接口时钟                              |

| MI_DATA             | MII    | BD   | PHY 管理接口数据                              |

| OSC_IN              | Clock  | I    | 时钟源 (晶体/振荡器)                            |

| OSC_OUT             | Clock  | O    | 时钟源 (晶体)                                |

| P_CONF(3:0)         | 配置     | I    | 逻辑端口的物理层                                |

| P_MODE[1:0]         | 配置     | I    | 物理端口和相应的逻辑端口数量                          |

| PDI[39:0]           | PDI    | BD   | PDI 信号, 取决于 EEPROM 内容                   |

| PHYAD_OFF           | 配置     | I    | 工业以太网 PHY 地址偏移                          |

| RBIAS               | LVDS   | LVDS | 用于低电压差分发送信号 (LVDS-TX) 电流调节的偏压电阻         |

| Res. [7:0]          | 保留     | I    | 保留管脚                                    |

| RESET               | 通用     | BD   | 集电极开路内部复位输出信号/外部复位控制信号输入                |

| RUN                 | LED    | O    | 应用层状态寄存器控制的运行指示灯                        |

| RX_CLK(3:0)         | MII    | I    | MII 接收时钟                                |

| RX_D(3:0)[3:0]      | MII    | I    | MII 接收数据                                |

| RX_DV(3:0)          | MII    | I    | MII 接收数据有效信号                            |

| RX_ERR(3:0)         | MII    | I    | MII 接收错误                                |

| SYNC/LATCH[1:0]     | DC     | I/O  | 分布式时钟同步信号输出或者自锁信号输入                     |

| TESTMODE            | 通用     | I    | 用于测试的保留管脚, 连接到地                         |

| TRANS(3:0)          | MII    | I    | MII 接口共享: 共享接口使能                        |

| TRANS_MODE_ENA      | 配置     | I    | 使能 MII 接口共享(与 TRANS(3:0) 信号)            |

| TX_D(3:0)[3:0]      | MII    | O    | MII 发送数据                                |

| TX_ENA(3:0)         | MII    | O    | MII 发送使能                                |

| VCC Core            | 电源     |      | 逻辑内核电源                                  |

| VCC I/O             | 电源     |      | I/O 信号电源                                |

| VCC PLL             | 电源     |      | PLL 锁相环电源                               |

表格 3-3 信号概述

| PDI        | 信号            | 方向     | 描述                      |

|------------|---------------|--------|-------------------------|

| 数字量 I/O 接口 | EEPROM_LOADED | O      | PDI 激活, EEPROM 数据正确加载   |

|            | I/O[31:0]     | I/O/BD | 输入/输出或者双向数据             |

|            | LATCH_IN      | I      | 外部数据锁存信号                |

|            | OE_CONF       | I      | 输出使能配置                  |

|            | OE_EXT        | I      | 输出使能                    |

|            | OUTVALID      | O      | 输出数据有效/输出事件             |

|            | SOF           | O      | 帧起始                     |

|            | WD_TRIG       | O      | 看门狗触发                   |

| SPI 从站接口   | EEPROM_LOADED | O      | PDI 激活, EEPROM 数据正确加载   |

|            | SPI_CLK       | I      | SPI 时钟                  |

|            | SPI_DI        | I      | SPI 数据 MOSI             |

|            | SPI_DO        | O      | SPI 数据 MISO             |

|            | SPI_IRQ       | O      | SPI 中断                  |

|            | SPI_SEL       | I      | SPI 片选                  |

| 异步微处理器接口   | CS            | I      | 片选                      |

|            | BHE           | I      | 字节高位使能 (只用于 16 位微控制器接口) |

|            | RD            | I      | 读命令                     |

|            | WR            | I      | 写命令                     |

|            | BUSY          | O      | 工业以太网设备忙碌               |

|            | IRQ           | O      | 中断                      |

|            | EEPROM_LOADED | O      | PDI 激活, EEPROM 数据正确加载   |

|            | DATA[7:0]     | BD     | 8 位微控制器接口数据总线           |

|            | ADR[15:0]     | I      | 地址总线                    |

|            | DATA[15:0]    | BD     | 16 位微控制器接口数据总线          |

| 同步微处理器接口   | ADR[15:0]     | I      | 地址总线                    |

|            | BHE           | I      | 字节高位使能                  |

|            | CPU_CLK_IN    | I      | 微控制器接口时钟                |

|            | CS            | I      | 片选                      |

|            | DATA[15:0]    | BD     | 16 位微控制器接口数据总线          |

|            | DATA[7:0]     | BD     | 8 位微控制器接口数据总线           |

|            | EEPROM_LOADED | O      | PDI 激活, EEPROM 数据正确加载   |

|            | IRQ           | O      | 中断                      |

|            | RD/nWR        | I      | 读/写访问                   |

|            | TA            | O      | 传输确认                    |

|            | TS            | I      | 传输开始                    |

表格 3-4 PDI 信号概述

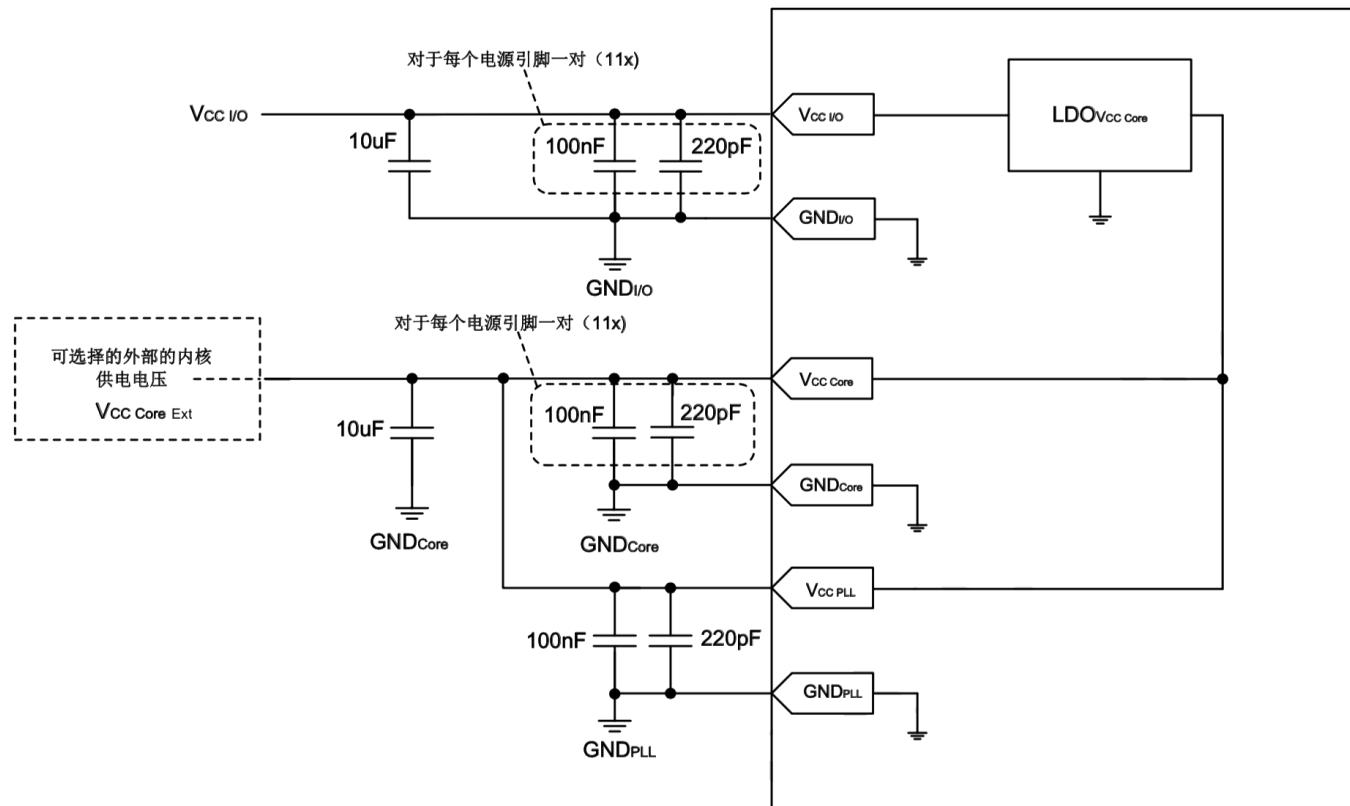

## 电源

CLM1100 支持不同的电源和 I/O 电平选择，它可以是 3.3V ( 也可选用 5V，但是实际应用中不建议选用 )，也支持选择单电源供电或者双电源供电。

V<sub>CC</sub> I/O 的电压值直接决定所有 I/O 信号的电平，，它可以使用 3.3V 或 5V 供电。使用 3.3V 时，

I/O 信号电平即为 3.3V，不允许使用 5V 输入。使用 5V 供电时，I/O 信号电平即为 5V。

CLM1100 逻辑内核要求 1.8V 供电。V<sub>CC</sub> Core/V<sub>CC</sub> PLL 可通过内部 LDO ( Low Dropout Regulator，低压线性稳压器 ) 产生，也可由外部提供。内部 LDO 使用 V<sub>CC</sub> I/O 作为电源。V<sub>CC</sub> Core 总等于 V<sub>CC</sub> PLL。内部 LDO 不能被关闭，但是如果外部供电电压高于内部 LDO 输出时，LDO 停止供电，因此 V<sub>CC</sub> Core/V<sub>CC</sub> PLL 使用外部供电时，供电电压至少要高于内部 LDO 电压输出 0.1V，以使内部 LDO 停止输出。

使用内部 LDO 会增加功耗，同时值得注意的是，I/O 信号选用 5V 供电时的功耗大于 I/O 信号选用 3.3V 供电时的功耗。所以建议选用 3.3V 的 I/O 信号电压和内部 LDO 为 V<sub>CC</sub> Core/V<sub>CC</sub> PLL 供电。。

每个电源引脚都要连接稳压电容。

| V <sub>CC</sub> I/O | V <sub>CC</sub> Core/V <sub>CC</sub> PLL | 输入信号   | 输出信号   | 解释          |

|---------------------|------------------------------------------|--------|--------|-------------|

| 3.3V                | 内部 LDO (1.8V)                            | 仅 3.3V | 仅 3.3V | 单电源供电, 低功耗  |

| 为了将来的兼容性不建议选用:      |                                          |        |        |             |

| 3.3V                | 外部电压 1.8V                                | 仅 3.3V | 仅 3.3V | 双电源供电, 最低功耗 |

| 5V                  | 内部 LDO(1.8V)                             | 仅 5V   | 仅 5V   | 单电源供电, 最高功耗 |

| 5V                  | 外部电压 1.8V                                | 仅 5V   | 仅 5V   | 双电源供电, 高功耗  |

表格 3-5 供电电压选择

## 信号电源

根据需要的接口电压，VCC I/O 电源管脚可以使用 3.3V 或者 5V 供电（不推荐使用 5V）。使用 3.3V 供电时，I/O 信号电平即为 3.3V，不允许使用 5V 输入。使用 5V 供电时，I/O 信号电平即为 5V。所有的电源引脚 VCC I/O/GND I/O 之间必须并联稳压电容。

| 引脚     | 引脚名称         |

|--------|--------------|

| BGA128 |              |

| C5     | VCC I/O      |

| D5     | GND I/O      |

| D3     | VCC I/O      |

| D4     | GND I/O      |

| J3     | VCC I/O      |

| J4     | GND I/O      |

| K5     | VCC I/O      |

| J5     | GND I/O      |

| K8     | VCC I/O      |

| J8     | GND I/O      |

| J10    | VCC I/O      |

| J9     | GND I/O      |

| F10    | VCC I/O*     |

| F9     | GND I/O*     |

| D10    | VCC I/O      |

| D9     | GND I/O      |

| E9     | VCC I/O*     |

| H4     | GND I/O (T1) |

| F3     | VCC I/O (T0) |

| K9     | GND I/O (T2) |

| H9     | VCC I/O (T3) |

表格 3-6 I/O 电源供电引脚

注意：I/O 电源管脚中标有 T0-T3 的引脚，是用于 CLM1100 进入测试模式的引脚，应用中为了将来芯片的兼容性，它们必须被连接到表中提供的电压。

## 逻辑内核电源

下表为 CLM1100 的内核电源引脚 VCC Core。CLM1100 的逻辑内核要求 1.8V 供电，该供电电压既可以由内部 LDO 产生，也可以由外部提供。内部 LDO 使用 VCC I/O 作为电源供电。这两种情况下，电源引脚 VCC Core/GNDCore 之间必须并联稳压电容。

| 引脚     | 引脚名称     |

|--------|----------|

| BGA128 |          |

| C7     | VCC Core |

| D7     | GNDCore  |

| C6     | VCC Core |

| D6     | GNDCore  |

| K6     | VCC Core |

| J6     | GNDCore  |

| K7     | VCC Core |

| J7     | GNDCore  |

表格 3-7 逻辑内核电源供电引脚

## PLL 电源

PLL ( Phase Lock Loop, 锁相回路 ) 电源引脚 VCC PLL 如下表所示。PLL 电源供电电压 1.8V，该供电电压既可以由内部 LDO 产生，也可以由外部提供。内部 LDO 使用 VCC I/O 作为电源供电。这两种情况下，电源引脚 VCC PLL/GNDPLL 之间必须并联稳压电容。

| 引脚     | 引脚名称    |

|--------|---------|

| BGA128 |         |

| G10    | VCC PLL |

| G9     | GNDPLL  |

表格 3-8 PLL 电源供电引脚

## 举例电源引脚连接原理图

图 3-2 CLM1100 电源供电

稳压电容建议：对于每个电源引脚并联 100nF 和 220pF 陶瓷电容到地，另外 VCC I/O 和 VCC Core/VCC PLL 并联 10uF 电容到地，总共需要 2 个 10uF 电容。

将 GNDPLL, GNDcore, GNDI/O 引脚连接到一个电位 GND。

如果 VCC Core/VCC PLL 的实际电压高于各自名义上的内部 LDO 的输出电压时，内部 LDO 将会自我失效。

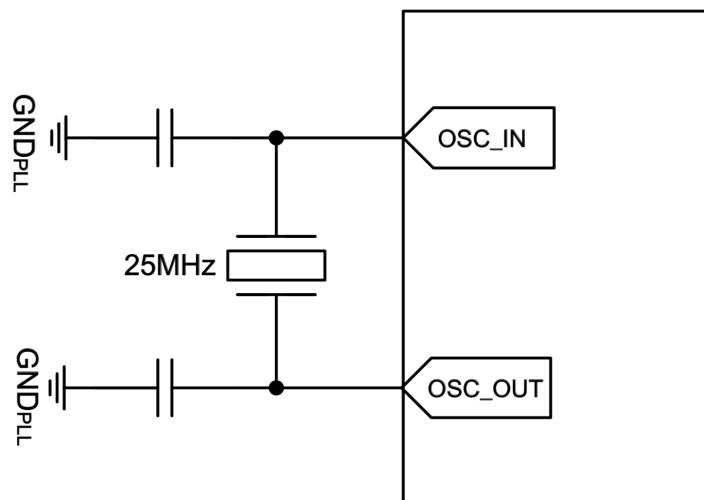

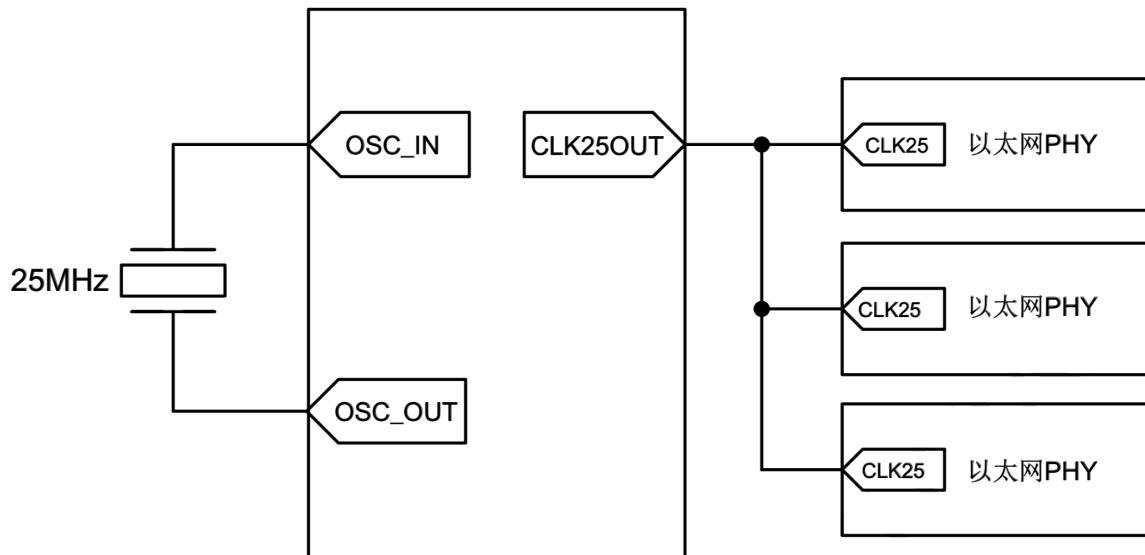

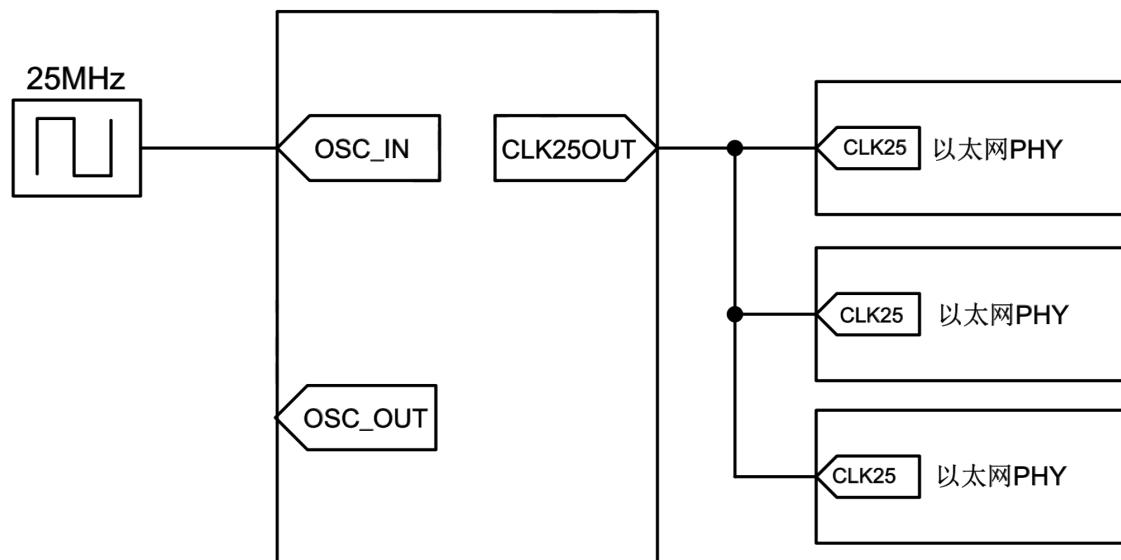

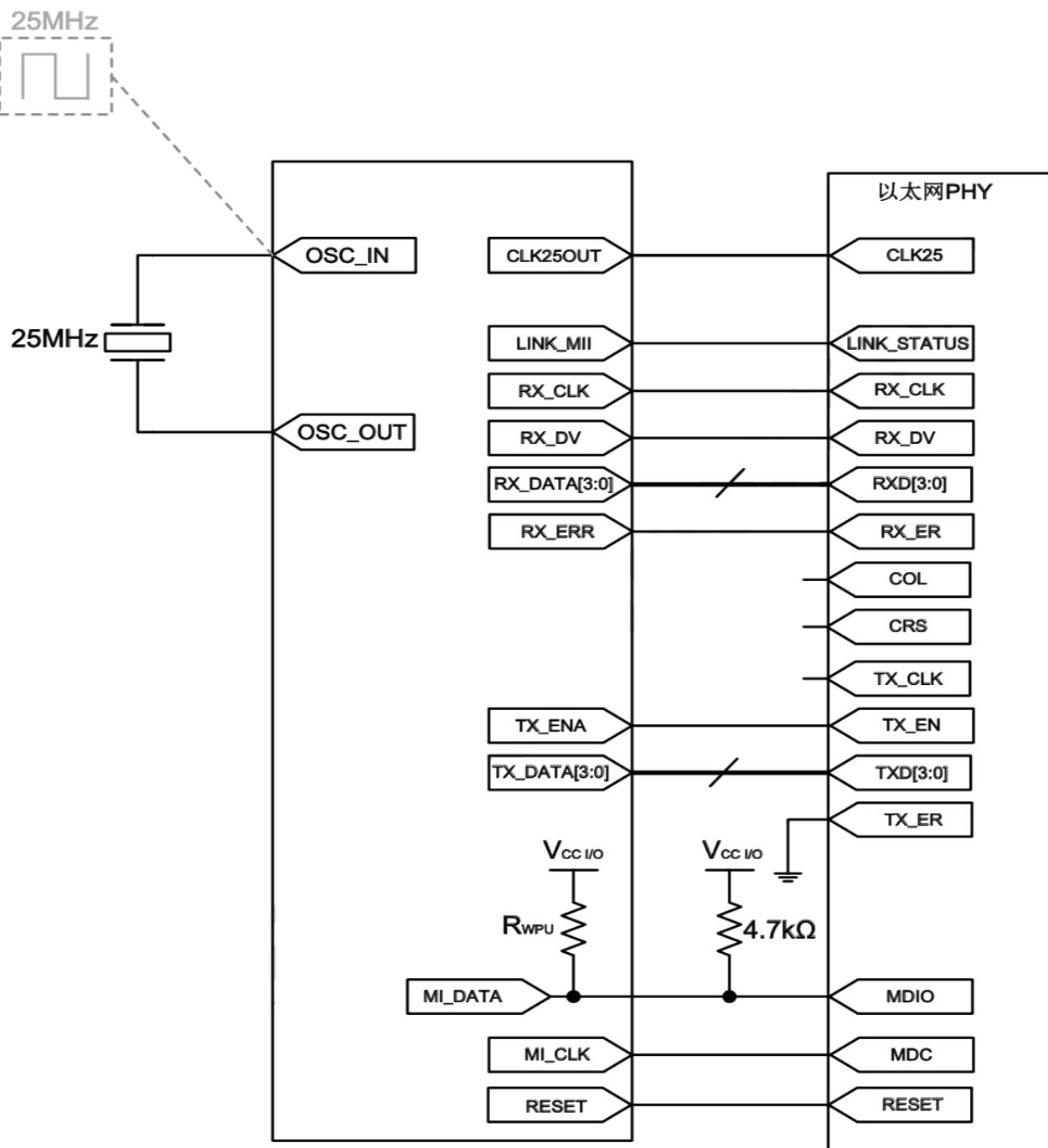

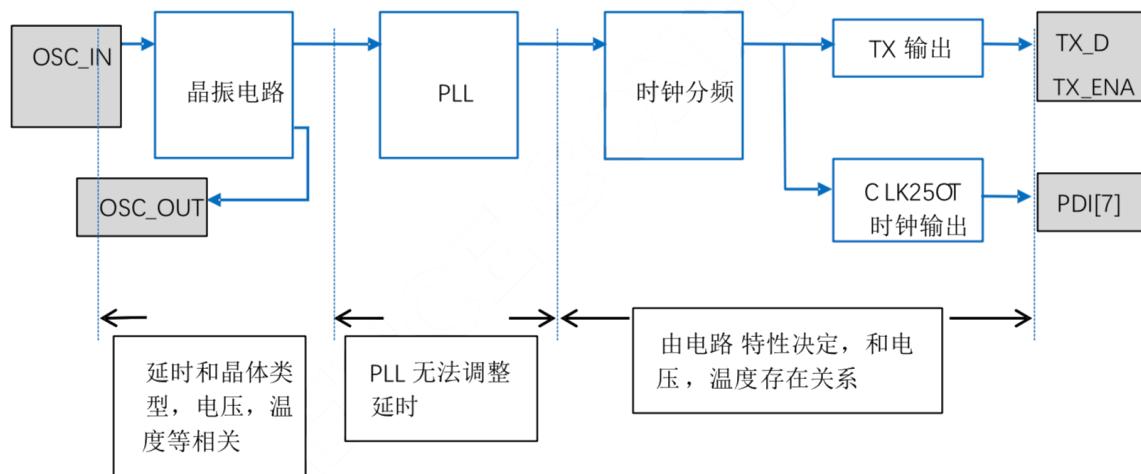

## 时钟

引脚 OSC\_IN 作为时钟源输入，外接 25MHz 的晶体或者振荡器。当 CLM1100 的时钟由振荡器提供时，以太网 PHY 芯片的时钟需由 CLM1100 输出时钟提供，具体使用方法参考引脚配置章节。25MHz 的时钟源要求精度为 25ppm 以上。

引脚 OSC\_OUT 外部晶体。当 OSC\_IN 接入振荡器时，该引脚悬空。

| 引脚      |    | 信号      |    | 信号描述 | 内部上拉/下拉电阻 |

|---------|----|---------|----|------|-----------|

| 名称      | 方向 | 信号      | 方向 |      |           |

| OSC_IN  | I  | OSC_IN  | I  |      |           |

| OSC_OUT | O  | OSC_OUT | O  |      |           |

表格 3-9 时钟引脚

## 举例时钟供应原理图

时钟源的布局对于系统的 EMC/EMI 有最大的影响。虽然一个 25MHz 时钟频率不要求大量的设计工作，但是以下规则有助于改善系统功能。

- ◆ 时钟源尽可能靠近以太网从站控制器布置；

- ◆ 在这个区域的地层应该无缝；

- ◆ 电源对时钟源和以太网从站控制器时钟呈现低阻抗；

- ◆ 应该使用时钟元器件推荐的电容值；

- ◆ 时钟源和以太网从站控制器时钟输入之间的电容量应该相同，具体数值取决于线路板的几何特性；

- ◆ CLM1100 的时钟源的精度为 25ppm 以上。

图 3-3 CLM1100 石英晶体时钟源的连接

注意：负载电容的值取决于晶体的负载电容，以太网从站控制器的引脚电容  $C_{os}$ ，以及板子设计（电容典型值为 12pF，此时  $CL=10pF$ ）。

图 3-4 CLM1100 和以太网从站 PHY 使用石英晶体时的连接

图 3-5 CLM1100 和以太网从站 PHY 使用振荡器时的连接

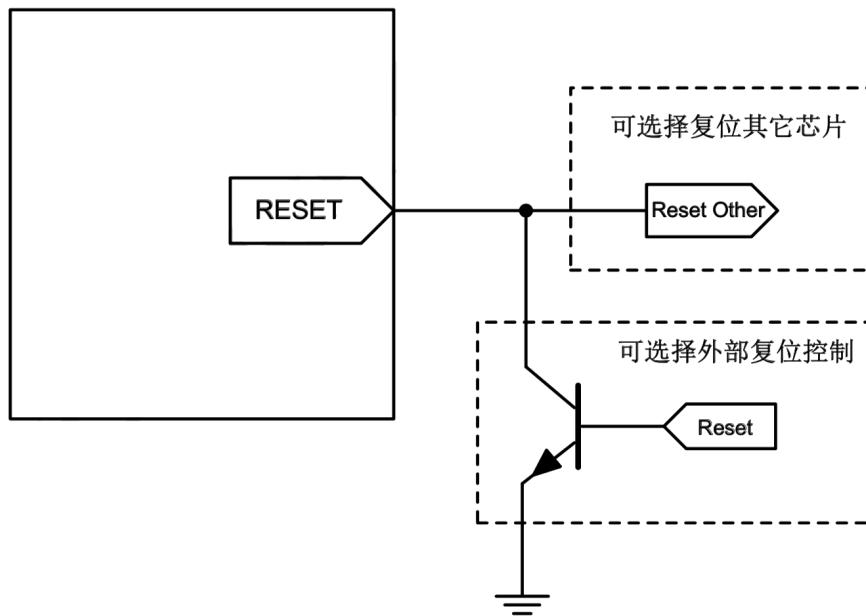

## 复位引脚

管脚 RESET 是集电极开路输入/输出信号（低电平有效），表示 CLM1100 的复位状态，以下三种情况可以引起 CLM1100 内部复位：

1. 在上电之后进入复位状态；

2. 供电电压过低；

3. 由写复位寄存器 0x0040 触发一次复位。

内部复位时，RESET 信号可以用于复位其它外围芯片，例如以太网 PHY 芯片。

| 引脚    |    | 信号    |    | 信号描述 | 内部上拉/下拉电阻 |

|-------|----|-------|----|------|-----------|

| 名称    | 方向 | 信号    | 方向 |      |           |

| RESET | BD | RESET | BD |      | 3.3 kΩ PU |

表格 3-10 复位引脚

## 举例复位引脚原理图

RESET 信号由外部设备拉低时，CLM1100 也进入复位状态，RESET 引脚连接如下图。

图 3-6 RESET 引脚连接图

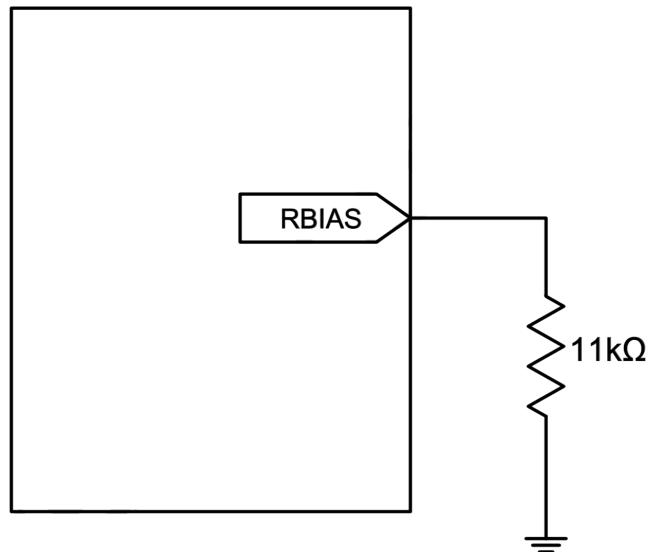

## RBIAS 引脚

CLM1100 的 RBIAS 引脚用于连接对 LVDS-TX 信号进行电流调节的偏压电阻，该引脚连接  $11\text{k}\Omega$  电阻到地。

| 引脚    |    | 信号    |    | 信号描述 | 内部上拉/下拉电阻 |

|-------|----|-------|----|------|-----------|

| 名称    | 方向 | 信号    | 方向 |      |           |

| RBIAS |    | RBIAS |    |      |           |

表格 3-11 RBIAS 引脚

注意：如果仅仅 MII 接口被使用（没有 LVDS 接口使用），RBIAS 电阻选取  $10\text{-}15\text{k}\Omega$ 。

## 举例 RBIAS 电阻原理图

LVDS 的 RBIAS 电阻值为  $\text{RBIAS}=11\text{k}\Omega$ 。

图 3-7 LVDS 偏压电阻

## 配置信号引脚

配置信号引脚在上电时通过外接上拉或下拉电阻来配置 CLM1100。上电时，配置信号引脚作为输入由 CLM1100 锁存配置信号信息。上电之后，这些引脚都有分配的操作功能，必要时引脚信号方向也可以改变。RESET 信号指示上电配置完成。若没有未重新上电，在随后的复位阶段，CLM1100 不会再锁存配置信号信息，配置引脚一直作为状态输出。

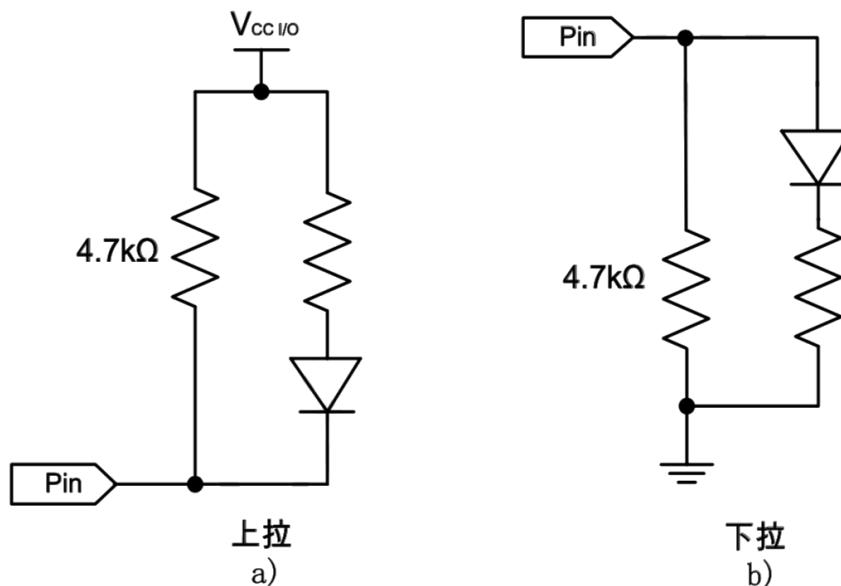

外接下拉电阻时，配置信号为 0；使用上拉电阻时，配置信号为 1。一些配置信号引脚也可以外接 LED 作为状态输出引脚，LED 的极性取决于需要配置的值。

## 举例配置信号输入/指示灯输出引脚原理图

如果配置信号为 1，需要外接上拉电阻，引脚输出为 0（低）时 LED 导通。如果配置信号为 0，则需外接下拉电阻，引脚输出为 1（高）时 LED 导通。如下图所示。

图 3-8 输入/LED 输出引脚双功能配置连接

a) 配置信号=1      b) 配置信号=0

## 端口模式

端口模式 ( Port Mode ) 用于配置物理端口和相应逻辑端口的数量。信息如下表所示

| 描述   | 配置信号      | 引脚名称                 | 寄存器       | P_MODE[1:0]值                                                                                              |

|------|-----------|----------------------|-----------|-----------------------------------------------------------------------------------------------------------|

| 端口模式 | P_MODE[0] | TX_D(1)[2]/P_MODE[0] | 0x0E00[0] | 00 = 2 端口(逻辑端口 0 和 1)<br>01 = 3 端口(逻辑端口 0,1 和 2)<br>10 = 3 端口(逻辑端口 0,1 和3)<br>11 = 4 端口(逻辑端口 0, 1, 2 和 3) |

|      | P_MODE[1] | TX_D(1)[3]/P_MODE[1] | 0x0E00[1] |                                                                                                           |

表格 3-12 端口模式

注意：物理端口是用于分组 CLM1100 接口引脚的，为用户外观上看到的芯片引脚名称。而任何主站/从站软件和寄存器设定是基于逻辑端口，只有配置后才能确定，但是逻辑端口之间的信号流向是固定的。每个逻辑端口映射到一个物理端口。每个端口都可以配置为 MII 接口或者 LVDS 接口两种形式。

如果同时配置了 MII 接口和 LVDS 接口，则 MII 接口总是优先占据更低位的物理端口，然后才是给 LVDS 接口分配物理端口。只要有 MII 接口被配置，最低位的 MII 接口总是被连接到物理端口 0，接下来高一位的 MII 接口连接到物理端口 1，依次分配。如果配置了 LVDS 接口，给 MII 接口分配完物理端口以后，开始分配最低位的 LVDS 接口到物理端口。如果没有配置 MII 接口，则最低位的 LVDS 接口连接到物理端口 0。

如果仅配置了 LVDS 接口或者 MII 接口，即当 P\_MODE[1:0]=00, 01 或 11 时，物理端口编码和逻辑端口编码相同。

## 端口配置

P\_CONF[3:0]决定了物理层配置 (MII 接口或者 LVDS 接口)。 P\_CONF[0] 决定了逻辑端口 0 的物理层, P\_CONF[1] 决定了逻辑端口 1 , P\_CONF[2] 决定了下一个可用的逻辑端口的物理层(P\_MODE[1:0]=10 时为端口 3, 否则为端口 2), 以及 P\_CONF[3] 决定了逻辑端口 3。如果没有物理端口被使用, 那么相应的 P\_CONF 配置信号也不会使用。

| 描述   | 配置信号      | 引脚名称                         | 寄存器       | 值                   |

|------|-----------|------------------------------|-----------|---------------------|

| 端口配置 | P_CONF[0] | LINKACT(0)/P_CONF[0]         | 0x0E00[2] | 0 = LVDS<br>1 = MII |

|      | P_CONF[1] | LINKACT(1)/P_CONF(1)         | 0x0E00[3] |                     |

|      | P_CONF[2] | LINKACT(2)/P_CONF[2]         | 0x0E00[4] |                     |

|      | P_CONF[3] | PDI[30]/LINKACT(3)/P_CONF(3) | 0x0E00[5] |                     |

表格 3-13 端口配置

## 端口配置

配置 2 端口时，逻辑端口 0 和逻辑端口 1 被使用。根据端口配置，端口信号可用物理端口 0 和物理端口 1。此时，P\_MODE[1:0]必须设为 00。P\_CONF[1:0] 决定了逻辑端口 1 和逻辑端口 0 的物理层配置。此时，P\_CONF[3:2] 未使用, P\_CONF[2]不应该悬空，建议连接到 GND。如果应用允许，对 P\_CONF[3]引脚下拉，即为表中标符 “-” 。2 端口的配置情况如下表所示。

| 逻辑端口    |         | 物理端口    |         | P_CONF [3:0] |

|---------|---------|---------|---------|--------------|

| 1       | 0       | 1       | 0       |              |

| LVDS(1) | LVDS(0) | LVDS(1) | LVDS(0) | -000         |

| LVDS(1) | MII(0)  | LVDS(1) | MII(0)  | -001         |

| MII(1)  | LVDS(0) | LVDS(0) | MII(1)  | -010         |

| MII(1)  | MII(0)  | MII(1)  | MII(0)  | -011         |

表格 3-14 2 端口配置(P\_MODE[1:0]=00)

## 端口配置

配置 3 端口时,逻辑端口 0, 1 , 2 (P\_MODE[1:0]=01) 或者逻辑端口 0, 1 3 (P\_MODE[1:0]=10)被使用。根据端口配置，端口信号可用物理端口 0,1,2。根据 P\_MODE 的设定值， P\_CONF[2:0] 决定了逻辑端口 2,1,0 或者逻辑端口 3,1,0 的物理层 ( P\_CONF[2]用于逻辑端口 2 或者逻辑端口 3 的配置 )。如果应用允许，对 P\_CONF[3]引脚下拉，即为表中标符 “-” 。3 端口的配置情况如下表所示。

| 逻辑端口    |         |         | 物理端口    |         |         | P_CONF [3:0] |

|---------|---------|---------|---------|---------|---------|--------------|

| 2       | 1       | 0       | 2       | 1       | 0       |              |

| LVDS(2) | LVDS(1) | LVDS(0) | LVDS(2) | LVDS(1) | LVDS(0) | -000         |

| LVDS(2) | LVDS(1) | MII(0)  | LVDS(2) | LVDS(1) | MII(0)  | -001         |

| LVDS(2) | MII(1)  | LVDS(0) | LVDS(2) | LVDS(0) | MII(1)  | -010         |

| LVDS(2) | MII(1)  | MII(0)  | LVDS(2) | MII(1)  | MII(0)  | -011         |

| MII(2)  | LVDS(1) | LVDS(0) | LVDS(1) | LVDS(0) | MII(2)  | -100         |

| MII(2)  | LVDS(1) | MII(0)  | LVDS(1) | MII(2)  | MII(0)  | -101         |

| MII(2)  | MII(1)  | LVDS(0) | LVDS(0) | MII(2)  | MII(1)  | -110         |

| MII(2)  | MII(1)  | MII(0)  | MII(2)  | MII(1)  | MII(0)  | -111         |

表格 3-15 3 端口配置(端口 0 , 端口 1 , 端口 2 , P\_MODE[1:0]=01)

| 逻辑端口    |         |         | 物理端口    |         |         | P_CONF [3:0] |

|---------|---------|---------|---------|---------|---------|--------------|

| 3       | 1       | 0       | 2       | 1       | 0       |              |

| LVDS(3) | LVDS(1) | LVDS(0) | LVDS(3) | LVDS(1) | LVDS(0) | -000         |

| LVDS(3) | LVDS(1) | MII(0)  | LVDS(3) | LVDS(1) | MII(0)  | -001         |

| LVDS(3) | MII(1)  | LVDS(0) | LVDS(3) | LVDS(0) | MII(1)  | -010         |

| LVDS(3) | MII(1)  | MII(0)  | LVDS(3) | MII(1)  | MII(0)  | -011         |

| MII(3)  | LVDS(1) | LVDS(0) | LVDS(1) | LVDS(0) | MII(3)  | -100         |

| MII(3)  | LVDS(1) | MII(0)  | LVDS(1) | MII(3)  | MII(0)  | -101         |

| MII(3)  | MII(1)  | LVDS(0) | LVDS(0) | MII(3)  | MII(1)  | -110         |

| MII(3)  | MII(1)  | MII(0)  | MII(2)  | MII(3)  | MII(0)  | -111         |

表格 3-16 3 端口配置(端口 0 , 端口 1 , 端口 3 , P\_MODE[1:0]=10)

## 端口配置

配置4端口时，逻辑端口0，1，2，3均被使用。根据端口配置，端口信号可用物理端口0到3。P\_MODE[1:0]设置为11。P\_CONF[3:0]决定了逻辑端口0到逻辑端口3的物理层。4端口的配置情况如下表所示。

| 逻辑端口    |         |         |         | 物理端口    |         |         |         | P_CONF<br>[3:0] |

|---------|---------|---------|---------|---------|---------|---------|---------|-----------------|

| 3       | 2       | 1       | 0       | 3       | 2       | 1       | 0       |                 |

| LVDS(3) | LVDS(2) | LVDS(1) | LVDS(0) | LVDS(3) | LVDS(2) | LVDS(1) | LVDS(0) | 0000            |

| LVDS(3) | LVDS(2) | LVDS(1) | MII(0)  | LVDS(3) | LVDS(2) | LVDS(1) | MII(0)  | 0001            |

| LVDS(3) | LVDS(2) | MII(1)  | LVDS(0) | LVDS(3) | LVDS(2) | LVDS(0) | MII(1)  | 0010            |

| LVDS(3) | LVDS(2) | MII(1)  | MII(0)  | LVDS(3) | LVDS(2) | MII(1)  | MII(0)  | 0011            |

| LVDS(3) | MII(2)  | LVDS(1) | LVDS(0) | LVDS(3) | LVDS(1) | LVDS(0) | MII(2)  | 0100            |

| LVDS(3) | MII(2)  | LVDS(1) | MII(0)  | LVDS(3) | LVDS(1) | MII(2)  | MII(0)  | 0101            |

| LVDS(3) | MII(2)  | MII(1)  | LVDS(0) | LVDS(3) | LVDS(0) | MII(2)  | MII(1)  | 0110            |

| LVDS(3) | MII(2)  | MII(1)  | MII(0)  | LVDS(3) | MII(2)  | MII(1)  | MII(0)  | 0111            |

| MII(3)  | LVDS(2) | LVDS(1) | LVDS(0) | LVDS(2) | LVDS(1) | LVDS(0) | MII(3)  | 1000            |

| MII(3)  | LVDS(2) | LVDS(1) | MII(0)  | LVDS(2) | LVDS(1) | MII(3)  | MII(0)  | 1001            |

| MII(3)  | LVDS(2) | MII(1)  | LVDS(0) | LVDS(2) | LVDS(0) | MII(3)  | MII(1)  | 1010            |

| MII(3)  | LVDS(2) | MII(1)  | MII(0)  | LVDS(2) | MII(3)  | MII(1)  | MII(0)  | 1011            |

| MII(3)  | MII(2)  | LVDS(1) | LVDS(0) | LVDS(1) | LVDS(0) | MII(3)  | MII(2)  | 1100            |

| MII(3)  | MII(2)  | LVDS(1) | MII(0)  | LVDS(1) | MII(3)  | MII(2)  | MII(0)  | 1101            |

| MII(3)  | MII(2)  | MII(1)  | LVDS(0) | LVDS(0) | MII(3)  | MII(2)  | MII(1)  | 1110            |

| MII(3)  | MII(2)  | MII(1)  | MII(0)  | MII(3)  | MII(2)  | MII(1)  | MII(0)  | 1111            |

表格 3-17 4 端口配置(P\_MODE[1:0]=11)

## CPU\_CLK 模式

CLK\_MODE 可用于提供一个时钟信号给外部微处理器。如果 CLK\_MODE 不是 00, CPU\_CLK 将使用 PDI[7], 此时这个引脚不再用于任何 PDI 信号。对于微处理器的 PDI, PDI[7] 为 ADR[15] , 当 CPU\_CLK 被选择时 , 其被视为 0。CPU\_CLK 配置模式如下表所示。

| 描述         | 配置信号        | 引脚名称                         | 寄存器       | CLK_MODE[1:0]值                                                                                                                               |

|------------|-------------|------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| CPU_CLK 模式 | CLK_MODE[0] | PERR(0)/TRANS(0)/CLK_MODE[0] | 0x0E00[6] | 00 = off, PDI[7]/CPU_CLK 适用于 PDI<br>01 = 25 MHz 时钟输出在 PDI[7]/CPU_CLK<br>10 = 20 MHz 时钟输出在 PDI[7]/CPU_CLK<br>11 = 10 MHz 时钟输出在 PDI[7]/CPU_CLK |

|            | CLK_MODE[1] | PERR(1)/TRANS(1)/CLK_MODE(1) | 0x0E00[7] |                                                                                                                                              |

表格 3-18 CPU\_CLK 模式

## TX 相位移动

MII 接口的 TX 信号(TX\_ENA, TX\_D[3:0])的相位移动(0/10/20/30ns) 通过 C25\_SHI[x] 信号获得。为了使能后期调整 , 建议通过硬件选择能够支持所有的 C25\_SHI[1:0]配置。TX 相位移动情况如下表所示。

| 描述      | 配置信号       | 管脚名称                  | 寄存器       | C25_SHI[1:0]值                                                                                   |

|---------|------------|-----------------------|-----------|-------------------------------------------------------------------------------------------------|

| TX 相位偏移 | C25_SHI[0] | TX_D(0)[2]/C25_SHI[0] | 0x0E01[0] | 00 = MII TX 信号无延迟<br>01 = MII TX 信号延迟 10 ns<br>10 = MII TX 信号延迟 20 ns<br>11 = MII TX 信号延迟 30 ns |

|         | C25_SHI[1] | TX_D(0)[3]/C25_SHI[1] | 0x0E01[1] |                                                                                                 |

表格 3-19 TX 相位偏移

## CLK25OUT2 使能

工业以太网PHY 可以通过CLM1100 的PDI[31]/CLK25OUT2 管脚获取一个 25MHz 的时钟。这仅和配置了 3 个 MII 接口时相关。当少于 3 个 MII 接口使用时, 因为 LINK\_MII(2) 未使用 , 引脚 LINK\_MII(2)/CLK25OUT1 总是作为 CLK25OUT1 输出 25MH 时钟。当使用 4 个MII 端口时 , 无论 CLK25OUT2 是否使能 , PDI[31]/CLK25OUT2 引脚都作为 CLK25OUT2 输出 25MHz 时钟。CLK25OUT2 使能如下表所示。

| 描述           | 配置信号    | 引脚名称               | 寄存器       | C25_ENA 值                                                                  |

|--------------|---------|--------------------|-----------|----------------------------------------------------------------------------|

| CLK25OUT2 使能 | C25_ENA | TX_D(0)[0]/C25_ENA | 0x0E01[2] | 0 = 失能, PDI[31]/CLK25OUT2 适用于 PDI<br>1 = 使能, PDI[31]/CLK25OUT2 输出 25MHz 时钟 |

表格 3-20 CLK25OUT2 使能

## 透明模式使能

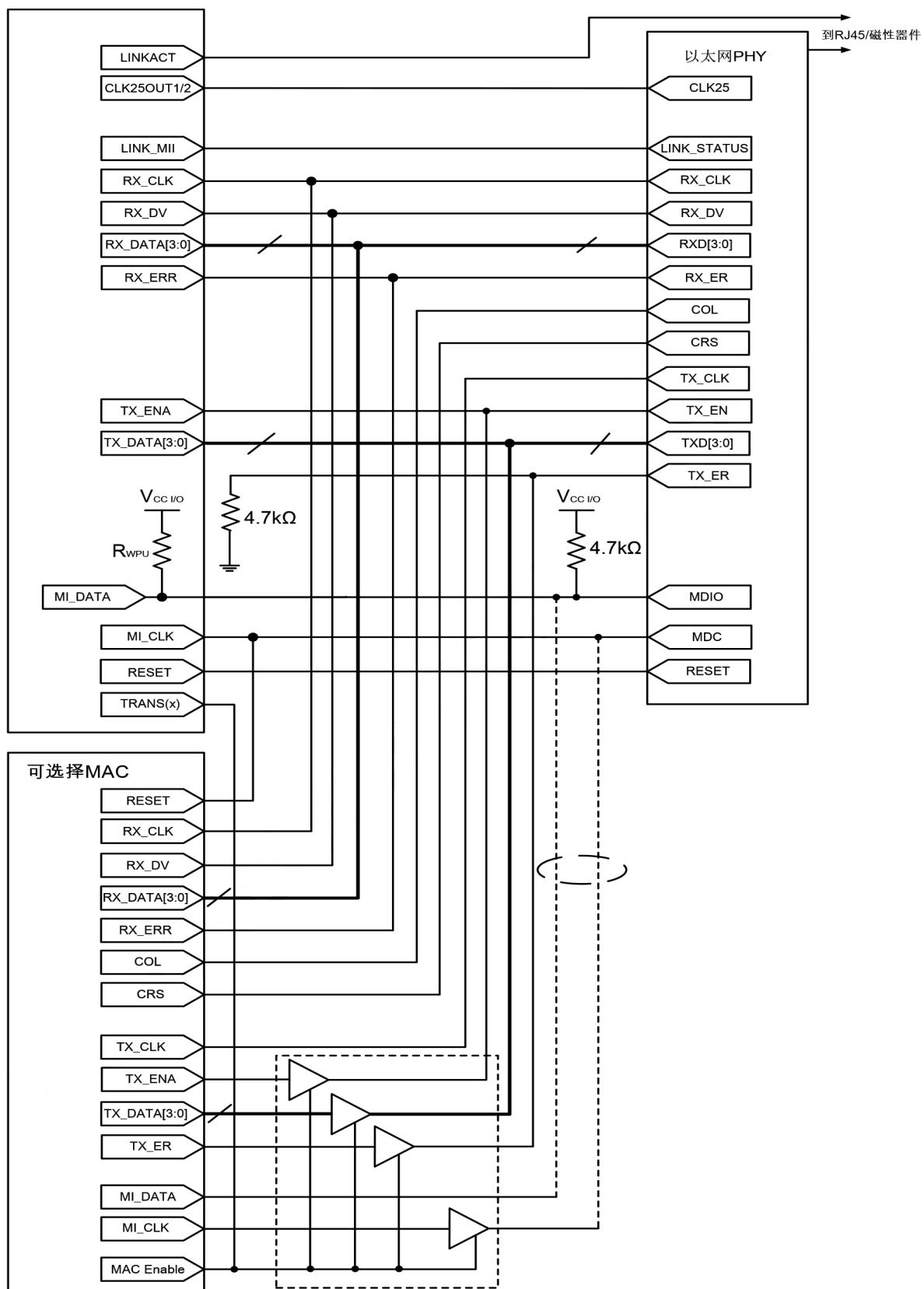

CLM1100 有能力在每一个端口上同其它 MAC 分享 MII 接口。通常情况下，透明模式失能，CLM1100 有专门分配 MII 接口给 PHY 芯片。当透明模式使能以后，MII 接口既可以由CLM1100 分配也可以由其它 MAC 分配，例如微处理器和集成 MAC。在处理同时网络信息流量时，不应该重新分配。

透明模式主要影响 PERR(x)/TRANS(x)引脚信号。如果透明模式使能，PERR(x)/TRANS(x)引脚作为 TRANS(x)信号使用 (低电平有效)，能够控制每个端口的透明状态，此透明模式下，PERR(x)是不可用的。

TRANS(x) 信号仅影响同一个端口的 TX\_ENA(x)/TX\_D(x) 以及 MI\_CLK/MI\_DATA 。连接CLM1100 和其它 MAC 的 RX\_CLK(x), RX\_DV(x),RX\_D(x),RX\_ERR(x)。

如果 TRANS(x)是高电平，每个 MII 接口和往常一样，CLM1100 控制 MII 接口。如果 TRANS ( x ) 为低电平，端口成为透明的 ( 或者单独的 )，比如此时CLM1100 不再驱动TX\_ENA(x)/TX\_D(x)活动，因此，其它 MAC 能够驱动这些信号。

LINKACT ( x ) 引脚外接 LED 一直被 CLM1100 驱动，因为它通过取样 RX\_DV(x) 和TX\_ENA(x) ( 在透明模式下，它们作为输入使用 ) 用于活动性检测。

只要至少一个 MII 接口不是透明模式，CLM1100 都由 MII 管理接口管理控制。透明模式开启时，CLM1100 的 PHY 管理接口能够凭借 PDI 接口获取，所以微处理器可以使用管理接口。当所有的 MII 接口均为透明模式，CLM1100 会放开 MI\_CLK 和 MI\_DATA 驱动，此时它们能够被其它 MAC 驱动。透明模式使能如下表所示。

| 描述     | 配置信号           | 引脚名称                      | 寄存器       | TRANS_MODE_ENA 值                                                             |

|--------|----------------|---------------------------|-----------|------------------------------------------------------------------------------|

| 透明模式使能 | TRANS_MODE_ENA | TX_D(1)[0]/TRANS_MODE_ENA | 0x0E01[3] | 0 =常规模式/透明模式失能，CLM1100 使用专有地<br>PHY<br>1 =使能透明模式，CLM1100 能够同其它<br>MAC 共享 PHY |

表格 3-21 透明模式使能

注意：使能透明模式配置时，会失能极性配置为高电平有效。

## 举例透明模式应用原理图

图 3-9 透明模式

## 数字控制/状态转移

接口信号中除 I/O[31:0]以外的信号称为控制/状态信号，分配在引脚 PDI[39:32]。如果从站使用了两个以上的物理通信端口，PDI[39:32]不能用作 PDI 信号，即控制/状态信号无效。此时，可以通过配置引脚 CTRL\_STATUS\_MOVE 将 PDI[23:16]或者 PDI[15:8]分配为控制/状态信号。

数字控制/状态转移配置情况如下表所示。

| 描述        | 配置信号             | 引脚名称                                    | 寄存器       | CTRL_STATUS_MOVE 值                                                                                                                                         |

|-----------|------------------|-----------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 数字控制/状态移动 | CTRL_STATUS_MOVE | PDI[34]/TX_D(2)[0]/<br>CTRL_STATUS_MOVE | 0x0E01[4] | 0 = I/O 无控制状态引脚转移:如果少于 3 个<br>MII 接口被使用，它们用于 PDI[39:32]，否则<br>不可使用。<br>1 = I/O 控制状态引脚转移：将 PDI[23:16]或<br>者 PDI[15:8]分配为控制/状态信号。I/O 控制/<br>状态信号在任何配置中都是可用的。 |

表格 3-22 数字控制/状态转移

## PHY 地址偏移

CLM1100 支持两种 ( 0 或 16 ) PHY 地址偏移配置。

PHY 地址偏移如下表所示：

| 描述       | 配置信号      | 引脚名称                        | 寄存器       | PHYAD_OFF 值                       |

|----------|-----------|-----------------------------|-----------|-----------------------------------|

| PHY 地址偏移 | PHYAD_OFF | PERR(2)/TRANS(2)/ PHYAD_OFF | 0x0E01[5] | 0 = PHY 地址偏移 0<br>1 = PHY 地址偏移 16 |

表格 3-23 PHY 地址偏移

## 链接有效信号极性

以太网物理层 ( PHY ) 芯片通过断言LINK\_MII(x)发信号 100 Mbit/s 全双工链接给CLM1100。LINKPOL 可以用于选择链接有效信号极性。链接极性配置如下表所示。

| 描述       | 配置信号    | 管脚名称           | 寄存器       | LINKPOL 值                                    |

|----------|---------|----------------|-----------|----------------------------------------------|

| 链接有效信号极性 | LINKPOL | MI_CLK/LINKPOL | 0x0E01[6] | 0 = LINK_MII(x)低电平有效<br>1 = LINK_MII(x)高电平有效 |

表格 3-24 链接有效信号极性

注意：使能透明模式配置时，会失能极性配置为高电平有效。

## SII EEPROM 内存大小

EEPROM\_SIZE 决定了 EEPROM 的内存大小(和 I<sup>2</sup>C 地址字节数目)。在 EEPROM 存取加载开始时，EEPROM\_SIZE 取样。EEPROM\_SIZE 配置如下表所示：

| 描述        | 配置信号        | 引脚名称            | 寄存器       | EEPROM_SIZE 值                                                               |

|-----------|-------------|-----------------|-----------|-----------------------------------------------------------------------------|

| EEPROM 容量 | EEPROM_SIZE | RUN/EEPROM_SIZE | 0x0502[7] | 0 = 单字节地址 (1 Kbit 到 16 Kbit EEPROM)<br>1 = 2 双字节地址(32 Kbit 到 4 Mbit EEPROM) |

表格 3-25 SII EEPROM\_SIZE

## 保留配置引脚

当 4 个端口被使用时，保留配置管脚拉低，否则悬空。如下表所示：

| 描述 | 配置信号     | 引脚名称                     | 寄存器       | RESERVED 值 |

|----|----------|--------------------------|-----------|------------|

| 保留 | RESERVED | PDI[28]/PERR(3)/TRANS(3) | 0x0E01[7] | 0 到 4 端口配置 |

表格 3-26 保留引脚

## SII EEPROM 接口

EEPROM\_CLK 为 EEPROM I<sup>2</sup>C 通信时钟信号 ( 集电极开路输出 ) 。

EEPROM\_DATA 为 EEPROM I<sup>2</sup>C 通信数据信号 ( 集电极开路输出 ) 。

| 引脚          |    | 信号          |    | 信号描述 | 内部上拉/下拉电阻 |

|-------------|----|-------------|----|------|-----------|

| 名称          | 方向 | 信号          | 方向 |      |           |

| EEPROM_CLK  | BD | EEPROM_CLK  | BD |      | 3.3 kΩ PU |

| EEPROM_DATA | BD | EEPROM_DATA | BD |      | 3.3 kΩ PU |

表格 3-27 SII EEPROM 接口

## MII 管理引脚

MII 管理接口信号仅用于至少一个 MII 接口被配置时。

MI\_CLK/LINKPOL 引脚在上电时作为 LINKPOL 信号配置，此后作为 PHY 管理接口时钟

MI\_CLK 信号。MI\_CLK 为轨到轨 ( rail-to-rail ) 驱动，空闲时为高电平。

MI\_DATA 为 PHY 管理接口数据，应该连接外部上拉电阻，推荐阻值 4.7 kΩ。

| 引脚             |    | 没有 MII 接口使用 |    | MII 接口使用 |    | 配置信号    | 内部上拉/下拉电阻 |

|----------------|----|-------------|----|----------|----|---------|-----------|

| 名称             | 方向 | 信号          | 方向 | 信号       | 方向 |         |           |

| MI_CLK/LINKPOL | BD |             | BD | MI_CLK   | O  | LINKPOL | WPD       |

| MI_DATA        | BD |             | BD | MI_DATA  | BD |         | WPD       |

表格 3-28 MII 管理引脚

## 分布时钟同步/自锁引脚

SYNC/LATCH[x] 为分布式时钟同步信号 ( Distributed Clocks SyncSignal ) 输出或者自锁信号

( LatchSignal ) 输入，这取决于 SII EEPROM 配置。EEPROM 加载前，SYNC/LATCH 信号都会处于高阻态不会被驱动。

| 引脚            |    | 信号               |     | 信号描述 | 内部上拉/下拉电阻 |

|---------------|----|------------------|-----|------|-----------|

| 名称            | 方向 | 信号               | 方向  |      |           |

| SYNC/LATCH[0] | BD | SYNC[0]/LATCH[0] | O/I |      |           |

| SYNC/LATCH[1] | BD | SYNC[1]/LATCH[1] | O/I |      |           |

表格 3-29 分布时钟同步/自锁引脚

## LED 信号

所有的配置信号引脚也可作为状态输出引脚而外接 LED。LED 的极性取决于需要配置的值：如果配置信号为 1，需要外接上拉电阻，引脚输出为 0 (低) 时发光二极管 (LED) 导通；如果配置信号为 0，引脚需要外接下拉电阻，引脚输出为 1 (高) 时发光二极管 (LED) 导通。

| 引脚              |    | 信号  |     | 配置信号        | 内部上拉/下拉电阻 |

|-----------------|----|-----|-----|-------------|-----------|

| 名称              | 方向 | 信号  | 方向  |             |           |

| RUN/EEPROM_SIZE | BD | RUN | O/I | EEPROM_SIZE |           |

表格 3-30 LED 引脚

注意: LINKACT(x) 和 PERR(x)/TRANS(x)的引脚在物理端口章节有描述。

RUN/EEPROM\_SIZE 引脚中 RUN 信号为运行指示灯信号。在 EEPROM 存取加载开始时，SII EEPROM 内存大小配置 (1 Kbit-16 Kbit 或者 32 KBit-4 Mbit) 进行取样。否则引脚就会输出 RUN 状态信号，此时外接 LED 为运行指示灯。如果引脚配置拉低，则引脚输出高电平有效，如果引脚配置拉高，则引脚输出低电平有效。

LINKACT(x)引脚为物理端口 x 的输出数据状态信号，此引脚外接指示灯 (LED)，来表示相应端口的线路是否连接或者活动的状态 (指示灯灭表示没有连接，指示灯亮表示有连接但没有数据传输活动，指示灯闪烁表示连接且有数据传输活动)。如果引脚拉低，则引脚 LINKACT(x)输出高电平有效，如果管脚拉高，则引脚 LINKACT(x)输出低电平有效。

PERR(x)/TRANS(x)引脚用于物理端口 x 配置为 LVDS 接口或者 TRANS\_MODE\_ENA=0 时的MII 接口发生错误时的输出状态信号，此时外接指示灯 (LED) 表示相应故障状态指示灯。当TRANS\_MODE\_ENA=1，PERR(x)/TRANS(x)引脚作为 TRANS (x) 信号用于作为 MII 接口的物理端口 x, 此时端口 x 进入独立透明操作，PERR (x) 此时不可用。如果引脚拉低，则引脚 PERR(x)输出高电平有效，如果引脚拉高，则引脚 PERR(x)输出低电平有效。

注意：PERR(x)引脚的外接 LED 信号并不是以太网指示说明的部分。这些指示灯是为了测试和排除故障。一旦芯片物理层发生接收故障，这些 PERR(x)引脚的外接LED 就会闪烁。不能混淆 PERR(x) LED 和应用层故障指示灯 (ERR LED)，ERR LED 不是被以太网从站控制器决定的，而是由微控制器控制的。

## 物理端口和PDI 引脚

CLM1100 有 4 个物理端口，分别命名为端口 0~端口 3。端口 0 和端口 1 不作为 PDI 引脚的接口使用，端口 2 和端口 3 与 PDI[39:16]有重叠部分，可进行引脚复用以获得芯片规模和功能的最佳组合，但是因此也限制了选用 PDI 的数量。

CLM1100 有 40 个 PDI 引脚 ( PDI[39:0] )。将其分为 4 组: PDI[15:0] (PDI 字节 0 和 PDI 字节1), PDI[16:23] (PDI 字节 2), PDI[24:31] (PDI 字节 3), 以及 PDI[32:39] (PDI 字节 4)。

物理端口和 PDI 引脚分配排列如下表所示。

| PDI 配置<br>端口使用配置                        | 异步微处理器        | 同步微处理器        | SPI               | 数 量 I/O CTLR_STATUS_MOVE= |                   |

|-----------------------------------------|---------------|---------------|-------------------|---------------------------|-------------------|

|                                         |               |               |                   | 0                         | 1                 |

| 2 个端口 (0 或 1) 或者 3 个端口，并且至少 1 个 LVDS 接口 | 8 Bit 或 16Bit | 8 Bit 或 16Bit | SPI +32 Bit GPI/O | 32Bit I/O+控制/状态信号         |                   |

| 3 个端口，都使用 MII 接口                        | 8Bit          | 8Bit          | SPI+24 Bit GPI/O  | 32Bit I/O                 | 24Bit I/O+控制/状态信号 |

| 4 个端口，至少 2 个使用 LVDS 接口                  | 不可用           | 不可用           | SPI+16Bit GPI/O   | 24Bit I/O +控制/状态信号        |                   |

| 4 个端口，其中 3 个 MII 接口，1 个 LVDS 接口         | 不可用           | 不可用           | SPI+16Bit GPI/O   | 24 Bit I/O                | 16Bit I/O+控制/状态信号 |

| 4 个端口，都是 MII 接口                         | 不可用           | 不可用           | SPI+8Bit GPI/O    | 16Bit I/O                 | 8Bit I/O+控制/状态信号  |

表格 3-31 PDI 类型和通信端口的组合配置

## MII 信号

下表描述了 CLM1100 所使用的 MII 接口信号。

| 信号           | 方向 | 描述                 |

|--------------|----|--------------------|

| LINK_MII(x)  | I  | 100Mbit/s 的全双工连接状态 |

| RX_CLK(x)    | I  | 接收时钟               |

| RX_DV(x)     | I  | 接收数据有效             |

| RX_D(x)[3:0] | I  | 接收数据               |

| RX_ERR(x)    | I  | 接收出错               |

| TX_ENA(x)    | O  | 发送使能               |

| TX_D(x)[3:0] | O  | 发送数据               |

表格 3-32 MII 信号

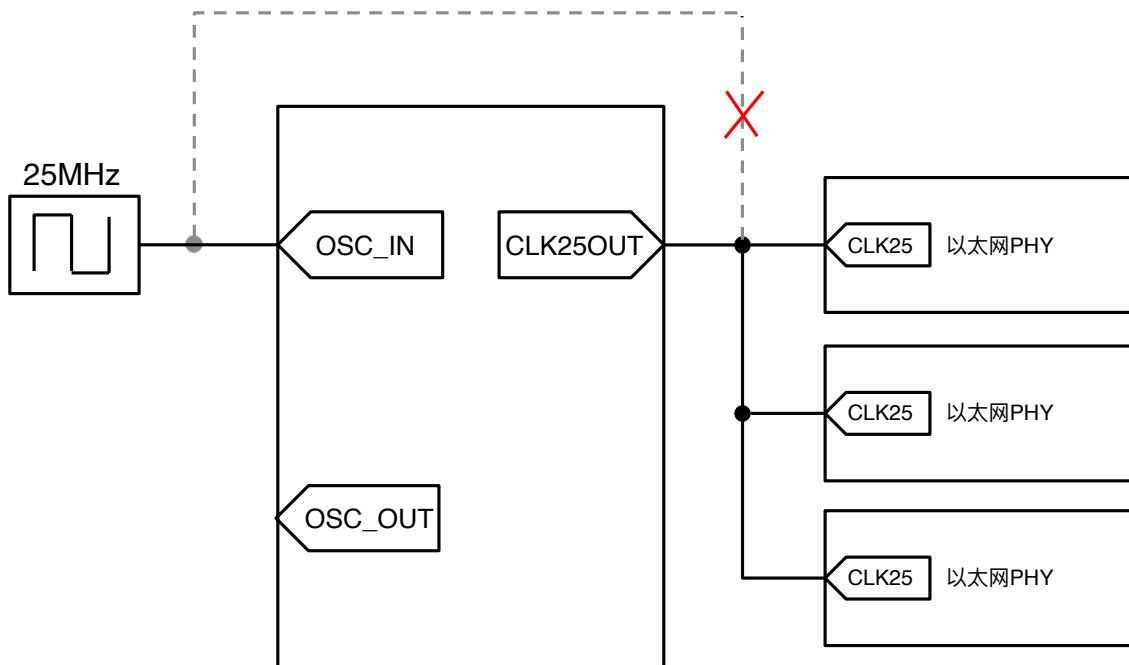

## CLK25OUT1/2 信号

当 CLM1100 采用外接晶体获取 25MHz 时钟时，其需要通过 CLK25OUT 为以太网 PHY 芯片提供一个 25MHz 的时钟源。如果 CLM1100 使用 25MHz 振荡器输入，PHY 芯片必须采用 CLK25OUT 输出作为时钟源，而不能和 CLM1100 采用同一振荡器输入。根据引脚配置和 C25\_ENA, CLK25OUT 可由 CLK25OUT1 或者 CLK25OUT2 提供，具体情况如下表所示。

| 配置      | C25_ENA=0                                                                               | C25_ENA=1                                             |

|---------|-----------------------------------------------------------------------------------------|-------------------------------------------------------|

| 0-2xMII | LINK_MII(2)/CLK25OUT1 提供 CLK25OUT 输出<br>(如果 4 端口被使用, PDI[31]/CLK25OUT2 也提供 CLK25OUT 输出) | LINK_MII(2)/CLK25OUT1 和 PDI[31]/CLK25OUT2 提供 CLK25OUT |

| 3xMII   | CLK25OUT 不可用                                                                            | PDI[31]/CLK25OUT2 提供 CLK25OUT                         |

| 4xMII   |                                                                                         | PDI[31]/CLK25OUT2 提供 CLK25OUT                         |

表格 3-33 CLK25OUT1/2 信号输出

注意：为了减少驱动负载，没有使用的 CLK25OUT 引脚悬空

## 举例 MII 连接原理图

要特别注意 TX Shift , LINK\_POL 以及 PHY 地址的配置。

图 3-10 PHY 连接

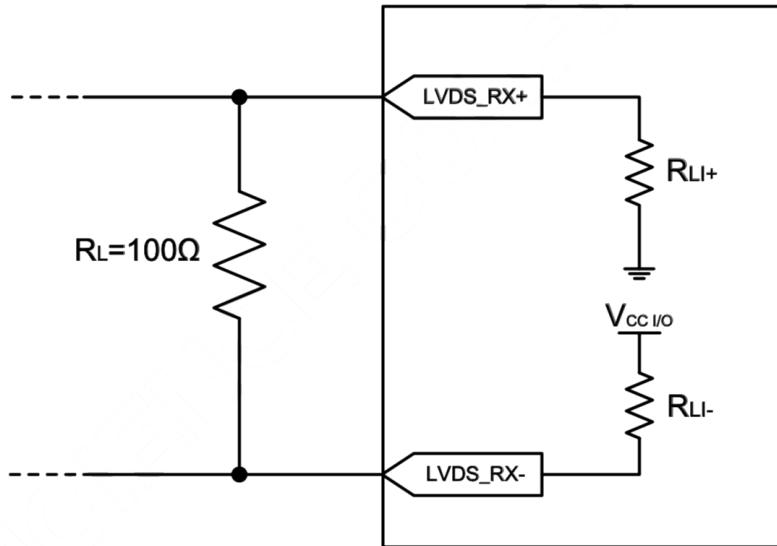

## LVDS 信号

CLM1100 的 LVDS 端口具有开路故障安全。LVDS 可以满足快速以太网 100Mbit/s 数据传输的波特率。具体信号描述如下表所示。

| 信号                      | 方向 | 描述                                                                                                        |

|-------------------------|----|-----------------------------------------------------------------------------------------------------------|

| LVDS(x)-RX+ LVDS(x)-RX- | I  | LVDS 接口接收信号。即使端口未配置成 LVDS 接口, LVDS (x) -RX+ 包含了一个内部下拉电阻 $R_{L1+}$ , LVDS (x) -RX- 包含了一个内部上拉电阻 $R_{L1-}$ 。 |

| LVDS(x)-TX+ LVDS(x)-TX- | O  | LVDS 接口发送信号                                                                                               |

| RBIAS                   |    | 用于对 LVDS-TX 信号进行电流调节的偏压电阻                                                                                 |

表格 3-34 LVDS 信号

## 举例 LVDS 端口连接原理图

每对 LVDS 线对只需要跨接一个  $100\Omega$  的负载电阻  $R_L$ 。仅在 LVDS 端口需要, 且靠近 LVDS\_RX 放置。

图 3-11 LVDS 端口接收端

## PDI 引脚

PDI[x]信号的功能取决于存储在器件 SII EEPROM 中的配置。EEPROM 加载前，PDI 信号都会处于高阻态不会被驱动。数字量输出尤其需要注意这点。没有 PDI 被配置，则 PDI 信号都会处于高阻态不会被驱动，PDI 控制寄存器 0x0140=0x00。

CLM1100 可通过引脚 PDI[7]/CPU\_CLK 提供给微处理器一个时钟信号。CPU\_CLK 的输出由 CLK\_MODE 配置决定。当 CPU\_CLK 使能时，则 PDI7 不能作为 PDI 使用，比如此时微处理器的 PDI 不能使用 ADR[15](内部将 ADR[15]处理成 0)，数字量 I/O 也不能使用 I/O[7]。

## 物理端口 0

下表为物理端口 0 的引脚。这些引脚能够被配置为 MII 接口或者 LVDS 接口使用。端口 0 和 PDI引脚无关。

| 引脚                           |        | MII              |     | LVDS        |     | 配置信号        | 内部上拉/下拉电阻 |

|------------------------------|--------|------------------|-----|-------------|-----|-------------|-----------|

| 名称                           | 方向     | 信号               | 方向  | 信号          | 方向  |             |           |

| TX_ENA(0)/LVDS(0)-TX+        | BD/LO+ | TX_ENA(0)        | O/I | LVDS(0)-TX+ | LO+ |             |           |

| TX_D(0)[0]/C25_ENA           | BD     | TX_D(0)[0]       | O   |             |     | C25_ENA     |           |

| TX_D(0)[1]/LVDS(0)-TX-       | O/LO-  | TX_D(0)[1]       | O   | LVDS(0)-TX- | LO- |             |           |

| TX_D(0)[2]/C25_SHI[0]        | BD     | TX_D(0)[2]       | O   |             |     | C25_SHI[0]  |           |

| TX_D(0)[3]/C25_SHI[1]        | BD     | TX_D(0)[3]       | O   |             |     | C25_SHI[1]  |           |

| RX_D(0)[0]                   | I      | RX_D(0)[0]       | I   |             | UI  |             |           |

| RX_D(0)[1]/LVDS(0)-RX+       | I/LI+  | RX_D(0)[1]       | I   | LVDS(0)-RX+ | LI+ |             | 27 kΩ PU  |

| RX_D(0)[2]                   | I      | RX_D(0)[2]       | I   |             | UI  |             |           |

| RX_D(0)[3]                   | I      | RX_D(0)[3]       | I   |             | UI  |             |           |

| RX_DV(0)/LVDS(0)-RX-         | I/LI-  | RX_DV(0)         | I   | LVDS(0)-RX- | LI- |             | 27 kΩ PU  |

| RX_ERR(0)                    |        | RX_ERR(0)        | I   |             | UI  |             |           |

| RX_CLK(0)                    | I      | RX_CLK(0)        | I   |             | UI  |             |           |

| LINK_MII(0)                  | I      | LINK_MII(0)      | I   |             | UI  |             |           |

| PERR(0)/TRANS(0)/CLK_MODE[0] | BD     | PERR(0)/TRANS(0) | O/I | PERR(0)     | O   | CLK_MODE[0] |           |

| LINKACT(0)/P_CONF[0]         | BD     | LINKACT(0)       | O   | LINKACT(0)  | O   | P_CONF[0]   |           |

表格 3-35 物理端口 0

## 物理端口 1

下表展示了物理端口 1 的引脚。这些引脚能够被配置为 MII 接口或者 LVDS 接口使用。端口1的引脚与PDI 引脚无关。

| 引脚                           |        | MII              |     | LVDS        |     | 配置信号           | 内部上拉/下拉电阻 |

|------------------------------|--------|------------------|-----|-------------|-----|----------------|-----------|

| 名称                           | 方向     | 信号               | 方向  | 信号          | 方向  |                |           |

| TX_ENA(1)/LVDS(1)-TX+        | BD/LO+ | TX_ENA(1)        | O/I | LVDS(1)-TX+ | LO+ |                |           |

| TX_D(1)[0]/TRANS-MODEENA     | BD     | TX_D(1)[0]       | O   |             |     | TRANS_MODE_ENA |           |

| TX_D(1)[1]/LVDS(1)-TX        | O/LO-  | TX_D(1)[1]       | O   | LVDS(1)-TX- | LO- |                |           |

| TX_D(1)[2]/P_MODE[0]         | BD     | TX_D(1)[2]       | O   |             |     | P_MODE[0]      |           |

| TX_D(1)[3]/P_MODE[1]         | BD     | TX_D(1)[3]       | O   |             |     | P_MODE[1]      |           |

| RX_D(1)[0]                   | I      | RX_D(1)[0]       | I   |             | UI  |                |           |

| RX_D(1)[1]/LVDS(1)-RX+       | I/LI+  | RX_D(1)[1]       | I   | LVDS(1)-RX+ | LI+ |                | 27 kΩ PD  |

| RX_D(1)[2]                   | I      | RX_D(1)[2]       | I   |             | UI  |                |           |

| RX_D(1)[3]                   | I      | RX_D(1)[3]       | I   |             | UI  |                |           |

| RX_DV(1)/LVDS(1)-RX-         | I/LI-  | RX_DV(1)         | I   | LVDS(1)-RX- | LI- |                | 27 kΩ PU  |

| RX_ERR(1)                    | I      | RX_ERR(1)        | I   |             | UI  |                |           |

| RX_CLK(1)                    | I      | RX_CLK(1)        | I   |             | UI  |                |           |

| LINK_MII(1)                  | I      | LINK_MII(1)      | I   |             | UI  |                |           |

| PERR(1)/TRANS(1)/CLK_MODE(1) | BD     | PERR(1)/TRANS(1) | O/I | PERR(1)     | O   | CLK_MODE[1]    |           |

| LINKACT(1)/P_CONF(1)         | BD     | LINKACT(1)       | O   | LINKACT(1)  | O   | P_CONF[1]      |           |

表格 3-36 物理端口 1

## 物理端口 2/ PDI Byte4

下表为物理端口 2 的引脚或者作为 PDI Byte4 (PDI[39:32])。这些引脚能够被配置为 MII 接口或者 LVDS 接口使用。

|            | 引脚                                  |    | PDI     |    | MII        |    | LVDS    |    | 配置信号             | 内部上拉/下拉电阻 |

|------------|-------------------------------------|----|---------|----|------------|----|---------|----|------------------|-----------|

|            | 名称                                  | 方向 | 信号      | 方向 | 信号         | 方向 | 信号      | 方向 |                  |           |

| PDI Byte 4 | PDI[32]/TX_D(2)[3]                  | BD | PDI[32] | BD | TX_D(2)[3] | O  | PDI[32] | BD |                  |           |

|            | PDI[33]/TX_D(2)[2]                  | BD | PDI[33] | BD | TX_D(2)[2] | O  | PDI[33] | BD |                  |           |

|            | PDI[34]/TX_D(2)[0]/CTRL_STATUS_MOVE | BD | PDI[34] | BD | TX_D(2)[0] | O  | PDI[34] | BD | CTRL_STATUS_MOVE |           |

|            | PDI[35]/RX_ERR(2)                   | BD | PDI[35] | BD | RX_ERR(2)  | I  | PDI[35] | BD |                  |           |

|            | PDI[36]/RX_CLK(2)                   | BD | PDI[36] | BD | RX_CLK(2)  | I  | PDI[36] | BD |                  |           |

|            | PDI[37]/RX_D(2)[0]                  | BD | PDI[37] | BD | RX_D(2)[0] | I  | PDI[37] | BD |                  |           |

|            | PDI[38]/RX_D(2)[2]                  | BD | PDI[38] | BD | RX_D(2)[2] | I  | PDI[38] | BD |                  |           |

|            | PDI[39]/RX_D(2)[3]                  | BD | PDI[39] | BD | RX_D(2)[3] | I  | PDI[39] | BD |                  |           |

表格 3-37 物理端口 2/PDI Byte4

| 引脚                         |        | 仅 2 端口    |      | MII              |     | LVDS        |     | 配置信号      | 内部上拉/下拉电阻 |

|----------------------------|--------|-----------|------|------------------|-----|-------------|-----|-----------|-----------|

| 名称                         | 方向     | 信号        | 方向   | 信号               | 方向  | 信号          | 方向  |           |           |

| TX_ENA(2/LVDS(2)-TX+       | BD/LO+ |           | UI   | TX_ENA(2)        | O/I | LVDS(2)-TX+ | LO+ |           |           |

| TX_D(2)[1]/LVDS(2)-TX-     | O/LO   |           | n.c. | TX_D(2)[1]       | O   | LVDS(2)-TX- | LO- |           |           |

| RX_DV(2)/LVDS(2)-RX-       | I/LI-  |           | UI   | RX_DV(2)         | I   | LVDS(2)-RX- | LI- |           | 27 kΩ PU  |

| RX_D(2)[1]/LVDS(2)-RX+     | I/LI+  |           | UI   | RX_D(2)[1]       | I   | LVDS(2)-RX+ | LI+ |           | 27 kΩ PD  |

| PERR(2)/TRANS(2)/PHYAD_OFF | BD     |           | O    | PERR(2)/TRANS(2) | O/I | PERR(2)     | O   | PHYAD_OFF |           |

| LINKACT(2)/P_CONF[2]       | BD     |           | O    | LINKACT(2)       | O   | LINKACT(2)  | O   | P_CONF[2] |           |

| LINK_MII(2)/CLK25OUT1      | BD     | CLK25OUT1 | O    | LINK_MII(2)      | I   | CLK25OUT1   | O   |           |           |

表格 3-38 物理端口 2

## 物理端口 3 / PDI Byte2 和 Byte3

下表为物理端口 3 的引脚或者 PDI 字节 2/3 (PDI[23:16], PDI[31 : [17])。这些引脚能够被配置为MII 接口或者 LVDS 接口使用。

|            | 引脚                             |         | PDI               |    | MII              |     | LVDS        |     | 配置信号      | 内部上拉/下拉电阻 |

|------------|--------------------------------|---------|-------------------|----|------------------|-----|-------------|-----|-----------|-----------|

|            | 名称                             | 方向      | 信号                | 方向 | 信号               | 方向  | 信号          | 方向  |           |           |

| PDI Byte 2 | PDI[16]/RX_ERR(3)              | BD      | PDI[16]           | BD | RX_ERR(3)        | I   | PDI[16]     | BD  |           |           |

|            | PDI[17]/RX_CLK(3)              | BD      | PDI[17]           | BD | RX_CLK(3)        | I   | PDI[17]     | BD  |           |           |

|            | PDI[18]/RX_D(3)[0]             | BD      | PDI[18]           | BD | RX_D(3)[0]       | I   | PDI[18]     | BD  |           |           |

|            | PDI[19]/RX_D(3)[2]             | BD      | PDI[19]           | BD | RX_D(3)[2]       | I   | PDI[19]     | BD  |           |           |

|            | PDI[20]/RX_D(3)[3]             | BD      | PDI[20]           | BD | RX_D(3)[3]       | I   | PDI[20]     | BD  |           |           |

|            | PDI[21]/LINK_MII(3)            | BD      | PDI[21]           | BD | LINK_MII(3)      | I   | PDI[21]     | BD  |           |           |

|            | PDI[22]/TX_D(3)[3]             | BD      | PDI[22]           | BD | TX_D(3)[3]       | O   | PDI[22]     | BD  |           |           |

|            | PDI[23]/TX_D(3)[2]             | BD      | PDI[23]           | BD | TX_D(3)[2]       | O   | PDI[23]     | BD  |           |           |

| PDI Byte 3 | PDI[24]/TX_D(3)[1]/LVDS(3)-TX- | BD/ LO  | PDI[24]           | BD | TX_D(3)[1]       | O   | LVDS(3)-TX- | LO- |           |           |

|            | PDI[25]/TX_D(3)[0]             | BD      | PDI[25]           | BD | TX_D(3)[0]       | O   |             | UI  |           |           |

|            | PDI[26]/TX_ENA(3)/LVDS(3)-TX+  | BD/ LO+ | PDI[26]           | BD | TX_ENA(3)        | O/I | LVDS(3)-TX+ | LO+ |           |           |

|            | PDI[27]/RX_DV(3)/LVDS(3)-RX-   | BD/ LI  | PDI[27]           | BD | RX_DV(3)         | I   | LVDS(3)-RX- | LI- |           | 27 kΩ PU  |

|            | PDI[28]/PERR(3)/TRANS(3)       | BD      | PDI[28]           | BD | PERR(3)/TRANS(3) | O/I | PERR(3)     | O   | RESERVED  |           |

|            | PDI[29]/RX_D(3)[1]/LVDS(3)-RX+ | BD/ LI+ | PDI[29]           | BD | RX_D(3)[1]       | I   | LVDS(3)-RX+ | LI+ |           | 27 kΩ PD  |

|            | PDI[30]/LINKACT(3)/P_CONF(3)   | BD      | PDI[30]           | BD | LINKACT(3)       | O   | LINKACT(3)  | O   | P_CONF[3] |           |

|            | PDI[31]/CLK25OUT2              | BD      | PDI[31]/CLK25OUT2 | BD | CLK25OUT2        | O   | CLK25OUT2   | O   |           |           |

表格 3-39 物理端口 2/PDI Byte2 和 Byte3

## PDI Byte0 和 Byte1

下表为 PDI Byte0 和 Byte1 (PDI[15:0])。所有 PDI 引脚的方向根据存储在 SII EEPROM 中的 PDI 配置决定。

|               |           | 管脚             |    | PDI, CLK_MODE=00 |    | PDI, CLK_MODE=00 |    |

|---------------|-----------|----------------|----|------------------|----|------------------|----|

|               |           | 名称             | 方向 | 信号               | 方向 | 信号               | 方向 |

| PDI<br>Byte 0 | PDI[7:0]  | PDI[0]         | BD | PDI[0]           | BD | PDI[0]           | BD |

|               |           | PDI[1]         | BD | PDI[1]           | BD | PDI[1]           | BD |

|               |           | PDI[2]         | BD | PDI[2]           | BD | PDI[2]           | BD |

|               |           | PDI[3]         | BD | PDI[3]           | BD | PDI[3]           | BD |

|               |           | PDI[4]         | BD | PDI[4]           | BD | PDI[4]           | BD |

|               |           | PDI[5]         | BD | PDI[5]           | BD | PDI[5]           | BD |

|               |           | PDI[6]         | BD | PDI[6]           | BD | PDI[6]           | BD |

|               |           | PDI[7]/CPU_CLK | BD | PDI[7]           | BD | CPU_CLK          | O  |

| PDI<br>Byte 1 | PDI[8:15] | PDI[8]         | BD | PDI[8]           | BD | PDI[8]           | BD |

|               |           | PDI[9]         | BD | PDI[9]           | BD | PDI[9]           | BD |

|               |           | PDI[10]        | BD | PDI[10]          | BD | PDI[10]          | BD |

|               |           | PDI[11]        | BD | PDI[11]          | BD | PDI[11]          | BD |

|               |           | PDI[12]        | BD | PDI[12]          | BD | PDI[12]          | BD |

|               |           | PDI[13]        | BD | PDI[13]          | BD | PDI[13]          | BD |

|               |           | PDI[14]        | BD | PDI[14]          | BD | PDI[14]          | BD |

|               |           | PDI[15]        | BD | PDI[15]          | BD | PDI[15]          | BD |

表格 3-40 PDI Byte0 和 Byte1

## PDI 接口

CLM1100 芯片的应用数据接口成为过程数据接口 ( Process Data Interface ) 或物理设备接口

( Physical Device Interface ) ,即 PDI 接口。根据选择的 PDI ( SII EEPROM ) 引进对 PDI 信号进行引脚分配。PDI 的选择和 PDI 信号引脚分配服从端口配置的约束。数字量 I/O 和 SPI 接口的 PDI 在任何配置中都是可用的 , 但是数字量 I/O 的字节量根据配置可以减少。用于微处理器的 PDI 接口最多 3 个端口 , 根据配置数据总线的宽度可以减少。

## 数字量 I/O 接口

|           | 数字量 I/O           | PDI 信号  | 2 端口或者 3 端口最少 1xLVDS |                | 3xMII, 0xLVDS CTRL_STATUS_MOVE= |                |          |                |          |

|-----------|-------------------|---------|----------------------|----------------|---------------------------------|----------------|----------|----------------|----------|

|           |                   |         |                      |                | 0                               |                | 1        |                |          |

|           |                   |         | 信号                   | 方向             | 信号                              | 方向             | 信号       | 方向             |          |

| PDI Byte0 | PDI[15:0]         | PDI[0]  | PDI[0]               | I/O[0]         | I/O/BD                          | I/O[0]         | I/O/BD   | I/O[0]         | I/O/BD   |

|           |                   |         | PDI[1]               | I/O[1]         | I/O/BD                          | I/O[1]         | I/O/BD   | I/O[1]         | I/O/BD   |

|           |                   |         | PDI[2]               | I/O[2]         | I/O/BD                          | I/O[2]         | I/O/BD   | I/O[2]         | I/O/BD   |

|           |                   |         | PDI[3]               | I/O[3]         | I/O/BD                          | I/O[3]         | I/O/BD   | I/O[3]         | I/O/BD   |

|           |                   |         | PDI[4]               | I/O[4]         | I/O/BD                          | I/O[4]         | I/O/BD   | I/O[4]         | I/O/BD   |

|           |                   |         | PDI[5]               | I/O[5]         | I/O/BD                          | I/O[5]         | I/O/BD   | I/O[5]         | I/O/BD   |

|           |                   |         | PDI[6]               | I/O[6]         | I/O/BD                          | I/O[6]         | I/O/BD   | I/O[6]         | I/O/BD   |

|           |                   | PDI[7]  | PDI[7]/CPU_CLK       | I/O[7]/CPU_CLK | I/O/BD/O                        | I/O[7]/CPU_CLK | I/O/BD/O | I/O[7]/CPU_CLK | I/O/BD/O |

|           |                   |         | PDI[8]               | I/O[8]         | I/O/BD                          | I/O[8]         | I/O/BD   | I/O[8]         | I/O/BD   |

|           |                   |         | PDI[9]               | I/O[9]         | I/O/BD                          | I/O[9]         | I/O/BD   | I/O[9]         | I/O/BD   |

|           |                   |         | PDI[10]              | I/O[10]        | I/O/BD                          | I/O[10]        | I/O/BD   | I/O[10]        | I/O/BD   |

|           |                   |         | PDI[11]              | I/O[11]        | I/O/BD                          | I/O[11]        | I/O/BD   | I/O[11]        | I/O/BD   |

|           |                   |         | PDI[12]              | I/O[12]        | I/O/BD                          | I/O[12]        | I/O/BD   | I/O[12]        | I/O/BD   |

|           |                   |         | PDI[13]              | I/O[13]        | I/O/BD                          | I/O[13]        | I/O/BD   | I/O[13]        | I/O/BD   |

|           |                   |         | PDI[14]              | I/O[14]        | I/O/BD                          | I/O[14]        | I/O/BD   | I/O[14]        | I/O/BD   |

|           |                   |         | PDI[15]              | I/O[15]        | I/O/BD                          | I/O[15]        | I/O/BD   | I/O[15]        | I/O/BD   |

| PDI Byte1 | PDI[23:16]/MII(3) | PDI[16] | PDI[16]              | I/O[16]        | I/O/BD                          | I/O[16]        | I/O/BD   | I/O[16]        | I/O/BD   |

|           |                   |         | PDI[17]              | I/O[17]        | I/O/BD                          | I/O[17]        | I/O/BD   | I/O[17]        | I/O/BD   |

|           |                   |         | PDI[18]              | I/O[18]        | I/O/BD                          | I/O[18]        | I/O/BD   | I/O[18]        | I/O/BD   |

|           |                   |         | PDI[19]              | I/O[19]        | I/O/BD                          | I/O[19]        | I/O/BD   | I/O[19]        | I/O/BD   |

|           |                   |         | PDI[20]              | I/O[20]        | I/O/BD                          | I/O[20]        | I/O/BD   | I/O[20]        | I/O/BD   |

|           |                   |         | PDI[21]              | I/O[21]        | I/O/BD                          | I/O[21]        | I/O/BD   | I/O[21]        | I/O/BD   |

|           |                   |         | PDI[22]              | I/O[22]        | I/O/BD                          | I/O[22]        | I/O/BD   | I/O[22]        | I/O/BD   |

|           |                   |         | PDI[23]              | I/O[23]        | I/O/BD                          | I/O[23]        | I/O/BD   | I/O[23]        | I/O/BD   |

| PDI Byte2 | PDI[31:24]/MII(3) | PDI[24] | PDI[24]              | I/O[24]        | I/O/BD                          | I/O[24]        | I/O/BD   | SOF            | O        |

|           |                   |         | PDI[25]              | I/O[25]        | I/O/BD                          | I/O[25]        | I/O/BD   | OE_EXT         | I        |

|           |                   |         | PDI[26]              | I/O[26]        | I/O/BD                          | I/O[26]        | I/O/BD   | OUTVALID       | O        |

|           |                   |         | PDI[27]              | I/O[27]        | I/O/BD                          | I/O[27]        | I/O/BD   | WD_TRIG        | O        |

|           |                   |         | PDI[28]              | I/O[28]        | I/O/BD                          | I/O[28]        | I/O/BD   | LATCH_IN       | I        |

|           |                   |         | PDI[29]              | I/O[29]        | I/O/BD                          | I/O[29]        | I/O/BD   | OE_CONF        | I        |

|           |                   |         | PDI[30]              | I/O[30]        | I/O/BD                          | I/O[30]        | I/O/BD   | EEPROM_LOADED  | O        |

|           |                   |         | PDI[31]/CLK25OUT2    | I/O/CLK25OUT2  | I/O/BD/O                        | I/O/CLK25OUT2  | I/O/BD/O | --/CLK25OUT2   | --/O     |

| PDI Byte4 | PDI[39:32]/MII(2) | PDI[32] | PDI[32]              | SOF            | O                               | MII(2)         |          | MII(2)         |          |

|           |                   |         | PDI[33]              | OE_EXT         | I                               |                |          |                |          |

|           |                   |         | PDI[34]              | OUTVALID       | O                               |                |          |                |          |

|           |                   |         | PDI[35]              | WD_TRIG        | O                               |                |          |                |          |

|           |                   |         | PDI[36]              | LATCH_IN       | I                               |                |          |                |          |

|           |                   |         | PDI[37]              | OE_CONF        | I                               |                |          |                |          |

|           |                   |         | PDI[38]              | EEPROM_LOADED  | O                               |                |          |                |          |

|           |                   |         | PDI[39]              | --             | --                              |                |          |                |          |

表格 3-41 数字量 I/O 接口的映射 ( 1 )

|           | 数字量 I/O                    | PDI 信号            | 4 端口最少 2xLVDS   |          | 3xMII, 1xLVDS CTRL_STATUS_MOVE |          |                 |          |

|-----------|----------------------------|-------------------|-----------------|----------|--------------------------------|----------|-----------------|----------|

|           |                            |                   |                 |          | 0                              |          | 1               |          |

|           |                            |                   | 信号              | 方向       | 信号                             | 方向       | 信号              | 方向       |

| PDI Byte0 | PDI[15:0]                  | PDI[0]            | I/O[0]          | I/O/BD   | I/O[0]                         | I/O/BD   | I/O[0]          | I/O/BD   |

|           |                            | PDI[1]            | I/O[1]          | I/O/BD   | I/O[1]                         | I/O/BD   | I/O[1]          | I/O/BD   |

|           |                            | PDI[2]            | I/O[2]          | I/O/BD   | I/O[2]                         | I/O/BD   | I/O[2]          | I/O/BD   |

|           |                            | PDI[3]            | I/O[3]          | I/O/BD   | I/O[3]                         | I/O/BD   | I/O[3]          | I/O/BD   |

|           |                            | PDI[4]            | I/O[4]          | I/O/BD   | I/O[4]                         | I/O/BD   | I/O[4]          | I/O/BD   |

|           |                            | PDI[5]            | I/O[5]          | I/O/BD   | I/O[5]                         | I/O/BD   | I/O[5]          | I/O/BD   |

|           |                            | PDI[6]            | I/O[6]          | I/O/BD   | I/O[6]                         | I/O/BD   | I/O[6]          | I/O/BD   |

|           |                            | PDI[7]/CPU_CLK    | I/O[7] /CPU_CLK | I/O/BD/O | I/O[7]/CPU_CLK                 | I/O/BD/O | I/O[7] /CPU_CLK | I/O/BD/O |

|           |                            | PDI[8]            | I/O[8]          | I/O/BD   | I/O[8]                         | I/O/BD   | I/O[8]          | I/O/BD   |

|           |                            | PDI[9]            | I/O[9]          | I/O/BD   | I/O[9]                         | I/O/BD   | I/O[9]          | I/O/BD   |

|           |                            | PDI[10]           | I/O[10]         | I/O/BD   | I/O[10]                        | I/O/BD   | I/O[10]         | I/O/BD   |

|           |                            | PDI[11]           | I/O[11]         | I/O/BD   | I/O[11]                        | I/O/BD   | I/O[11]         | I/O/BD   |

|           |                            | PDI[12]           | I/O[12]         | I/O/BD   | I/O[12]                        | I/O/BD   | I/O[12]         | I/O/BD   |

|           |                            | PDI[13]           | I/O[13]         | I/O/BD   | I/O[13]                        | I/O/BD   | I/O[13]         | I/O/BD   |

|           |                            | PDI[14]           | I/O[14]         | I/O/BD   | I/O[14]                        | I/O/BD   | I/O[14]         | I/O/BD   |

|           |                            | PDI[15]           | I/O[15]         | I/O/BD   | I/O[15]                        | I/O/BD   | I/O[15]         | I/O/BD   |

| PDI Byte1 | PDI[23:16]/MII(3)          | PDI[16]           | I/O[16]         | I/O/BD   | I/O[16]                        | I/O/BD   | SOF             | O        |

|           |                            | PDI[17]           | I/O[17]         | I/O/BD   | I/O[17]                        | I/O/BD   | OE_EXT          | I        |

|           |                            | PDI[18]           | I/O[18]         | I/O/BD   | I/O[18]                        | I/O/BD   | OUTVALID        | O        |

|           |                            | PDI[19]           | I/O[19]         | I/O/BD   | I/O[19]                        | I/O/BD   | WD_TRIG         | O        |

|           |                            | PDI[20]           | I/O[20]         | I/O/BD   | I/O[20]                        | I/O/BD   | LATCH_IN        | I        |

|           |                            | PDI[21]           | I/O[21]         | I/O/BD   | I/O[21]                        | I/O/BD   | OE_CONF         | I        |

|           |                            | PDI[22]           | I/O[22]         | I/O/BD   | I/O[22]                        | I/O/BD   | EEPROM_LOADED   | O        |

|           |                            | PDI[23]           | I/O[23]         | I/O/BD   | I/O[23]                        | I/O/BD   | --              | --       |

| PDI Byte2 | PDI[31:24]/MII(3) /LVDS(3) | PDI[24]           | LVDS(3)         |          | LVDS(3)                        |          | LVDS(3)         |          |

|           |                            | PDI[25]           |                 |          |                                |          |                 |          |

|           |                            | PDI[26]           |                 |          |                                |          |                 |          |

|           |                            | PDI[27]           |                 |          |                                |          |                 |          |

|           |                            | PDI[28]           |                 |          |                                |          |                 |          |

|           |                            | PDI[29]           |                 |          |                                |          |                 |          |

|           |                            | PDI[30]           |                 |          |                                |          |                 |          |

|           |                            | PDI[31]/CLK25OUT2 |                 |          |                                |          |                 |          |

| PDI Byte3 | PDI[39:32]/MII(2)          | PDI[32]           | SOF             | O        | MII(2)                         |          | MII(2)          |          |

|           |                            | PDI[33]           | OE_EXT          | I        |                                |          |                 |          |

|           |                            | PDI[34]           | OUTVALID        | O        |                                |          |                 |          |

|           |                            | PDI[35]           | WD_TRIG         | O        |                                |          |                 |          |

|           |                            | PDI[36]           | LATCH_IN        | I        |                                |          |                 |          |

|           |                            | PDI[37]           | OE_CONF         | I        |                                |          |                 |          |

|           |                            | PDI[38]           | EEPROM_LOADED   | O        |                                |          |                 |          |

|           |                            | PDI[39]           | --              | --       |                                |          |                 |          |

表格 3-42 数字量 I/O 接口的映射 (2)

|              | 数字量 I/O                       | PDI 信号            | 4xMII, 0xLVDS CTRL_STATUS_MOVE= |          |                 |          |

|--------------|-------------------------------|-------------------|---------------------------------|----------|-----------------|----------|

|              |                               |                   | 0                               |          | 1               |          |

|              |                               |                   | 信号                              | 方向       | 信号              | 方向       |

| PDI<br>Byte0 | PDI[15:0]                     | PDI[0]            | I/O[0]                          | I/O/BD   | I/O[0]          | I/O/BD   |

|              |                               | PDI[1]            | I/O[1]                          | I/O/BD   | I/O[1]          | I/O/BD   |

|              |                               | PDI[2]            | I/O[2]                          | I/O/BD   | I/O[2]          | I/O/BD   |

|              |                               | PDI[3]            | I/O[3]                          | I/O/BD   | I/O[3]          | I/O/BD   |

|              |                               | PDI[4]            | I/O[4]                          | I/O/BD   | I/O[4]          | I/O/BD   |

|              |                               | PDI[5]            | I/O[5]                          | I/O/BD   | I/O[5]          | I/O/BD   |

|              |                               | PDI[6]            | I/O[6]                          | I/O/BD   | I/O[6]          | I/O/BD   |

|              |                               | PDI[7]/CPU_CLK    | I/O[7] /CPU_CLK                 | I/O/BD/O | I/O[7] /CPU_CLK | I/O/BD/O |

|              |                               | PDI[8]            | I/O[8]                          | I/O/BD   | SOF             | O        |

|              |                               | PDI[9]            | I/O[9]                          | I/O/BD   | OE_EXT          | I        |

|              |                               | PDI[10]           | I/O[10]                         | I/O/BD   | OUTVALID        | O        |

|              |                               | PDI[11]           | I/O[11]                         | I/O/BD   | WD_TRIG         | O        |

|              |                               | PDI[12]           | I/O[12]                         | I/O/BD   | LATCH_IN        | I        |

|              |                               | PDI[13]           | I/O[13]                         | I/O/BD   | OE_CONF         | I        |

|              |                               | PDI[14]           | I/O[14]                         | I/O/BD   | EEPROM_LOADED   | O        |

|              |                               | PDI[15]           | I/O[15]                         | I/O/BD   | --              | --       |

| PDI<br>Byte2 | PDI[23:16]/MII(3)             | PDI[16]           | MII(3)                          |          | MII(3)          |          |

|              |                               | PDI[17]           |                                 |          |                 |          |

|              |                               | PDI[18]           |                                 |          |                 |          |

|              |                               | PDI[19]           |                                 |          |                 |          |

|              |                               | PDI[20]           |                                 |          |                 |          |

|              |                               | PDI[21]           |                                 |          |                 |          |

|              |                               | PDI[22]           |                                 |          |                 |          |

|              |                               | PDI[23]           |                                 |          |                 |          |

| PDI<br>Byte3 | PDI[31:24]/MII(3)<br>/LVDS(3) | PDI[24]           | MII(3)                          |          | MII(3)          |          |

|              |                               | PDI[25]           |                                 |          |                 |          |

|              |                               | PDI[26]           |                                 |          |                 |          |

|              |                               | PDI[27]           |                                 |          |                 |          |

|              |                               | PDI[28]           |                                 |          |                 |          |