## 2A 6-Channel Load Switch with Slew Rate Control

#### **FEATURES**

Integrated 6 P-channel MOSFETs

Supply voltage: 1.5V to 5.5V

Input voltage: 1.2V to 5.5V

Typical on-state resistance R<sub>ON</sub> (V<sub>VSYS</sub>=1.8V):

$R_{ON}$ =56m $\Omega$  at  $V_{INX}$ =5.0V  $R_{ON}$ =71m $\Omega$  at  $V_{INX}$ =3.3V

$R_{ON}=122m\Omega$  at  $V_{INX}=1.8V$

Ultra-low quiescent and shutdown current

I<sup>2</sup>C configuration (per channel):

On/Off control & power sequence

Programmable slew rate control (4 options)

Selectable quick output discharge (QOD)

Selectable reverse current blocking

- 2A maximum continuous current for V<sub>INX</sub>>1.8V

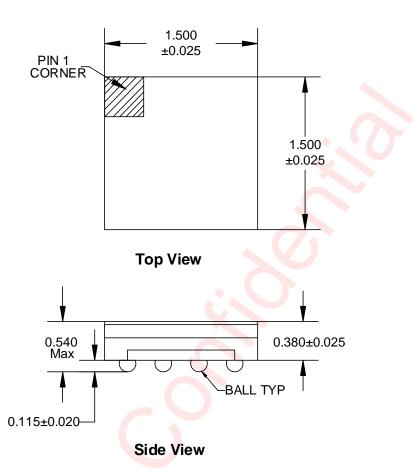

- FOWLP 1.50mm x 1.50mm x 0.495mm 16B package

#### **APPLICATIONS**

- Smartphones and tablets

- Portable and wearable devices

#### **GENERAL DESCRIPTION**

The AW35206 is a 6-channel, low R<sub>ON</sub> load switch with user programmable features. The device integrates six P-channel MOSFETs that operates over the input voltage from 1.2V to 5.5V. While the supply voltage range of the system is 1.5V ~5.5V. All load switches are controlled through I<sup>2</sup>C BUS which makes it realizable for usage with processors having limited GPIO available.

The rising time of output voltage is programmable to avoid inrush current. Each output integrates a quick output discharge (QOD) function block that can be disabled via I<sup>2</sup>C BUS. Also every load switch has the ability that cuts off current when the output voltage is higher than the input while it can be disabled for low quiescent current. Single switch supports the maximum current 2A for V<sub>INX</sub>>1.8V.

The AW35206 is available in FOWLP package (0.35-mm pitch) and characterized for operation over the free-air temperature range of -40°C to 85°C.

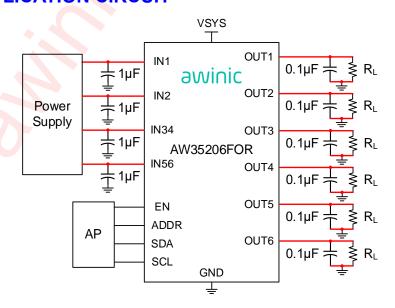

## TYPICAL APPLICATION CIRCUIT

Figure 1 Typical application circuit of AW35206

1

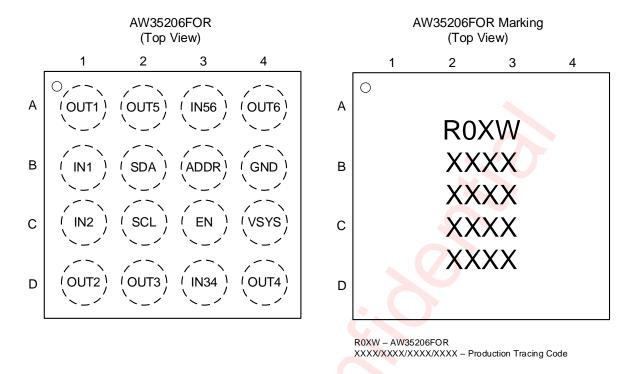

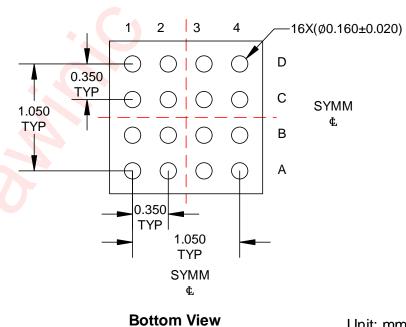

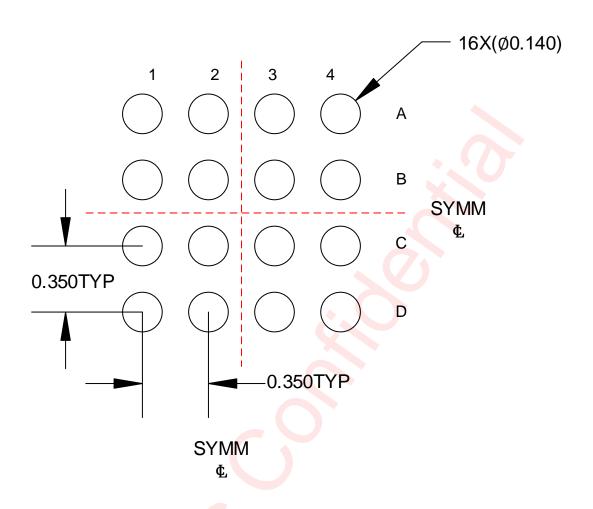

## PIN CONFIGURATION AND TOP MARK

Figure 2 Pin Configuration and Top Mark

## **PIN DEFINITION**

| No. | NAME | DESCRIPTION                            |

|-----|------|----------------------------------------|

| A1  | OUT1 | Load switch 1 output                   |

| A2  | OUT5 | Load switch 5 output                   |

| А3  | IN56 | Load switch 5 and 6 input              |

| A4  | OUT6 | Load switch 6 output                   |

| B1  | IN1  | Load switch 1 input                    |

| B2  | SDA  | Serial data input or output            |

| В3  | ADDR | Device address pin                     |

| B4  | GND  | Device ground                          |

| C1  | IN2  | Load switch 2 input                    |

| C2  | SCL  | Serial clock input                     |

| С3  | EN   | Load switch enable pin (actively high) |

| C4  | VSYS | Power supply to the device             |

| D1  | OUT2 | Load switch 2 output                   |

| D2  | OUT3 | Load switch 3 output                   |

| D3  | IN34 | Load switch 3 and 4 input              |

| D4  | OUT4 | Load switch 4 output                   |

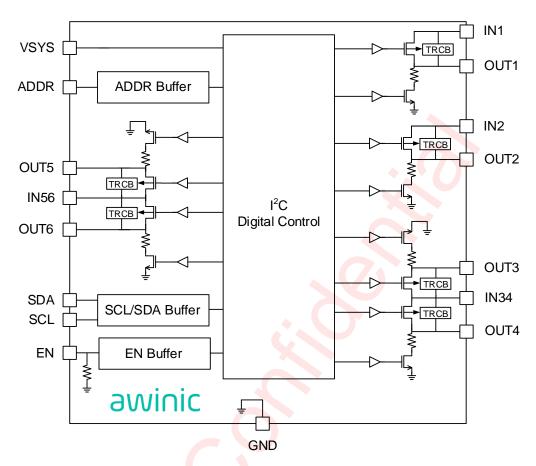

## **FUNCTIONAL BLOCK DIAGRAM**

NOTE: TRCB is "True Reverse Current Blocking", this block cuts off current when  $V_{OUT} > V_{IN}$  if this function is enabled by  $I^2C$ .

Figure 3 Functional Block Diagram

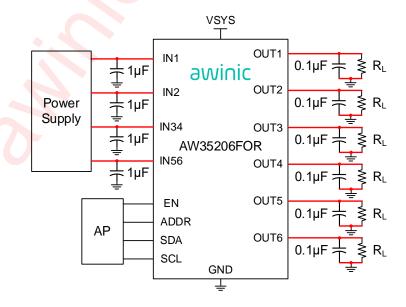

## TYPICAL APPLICATION CIRCUITS

Figure 4 Typical Application circuit of AW35206

## **ORDERING INFORMATION**

| Par | t Number | Temperature | Package                                | Markin<br>g | Moisture<br>Sensitivity<br>Level | Environmental<br>Information | Delivery<br>Form                |

|-----|----------|-------------|----------------------------------------|-------------|----------------------------------|------------------------------|---------------------------------|

| AW3 | 35206FOR | -40°C~85°C  | FOWLP<br>1.50mm×1.50mm<br>×0.495mm-16B | R0XW        | MSL1                             | RoHS+HF                      | 4500 units/<br>Tape and<br>Reel |

## **ABSOLUTE MAXIMUM RATINGS**(NOTE1)

| PAI                                               | RAMETERS                                                          | RANGE                     |  |  |

|---------------------------------------------------|-------------------------------------------------------------------|---------------------------|--|--|

| Power IN/OUT Pins and<br>Supply Pin Voltage Range | IN1, IN2, IN34, IN56, OUT1, OUT2,<br>OUT3, OUT4, OUT5, OUT6, VSYS | -0.3V to 6V               |  |  |

| Other Pins Voltage Range                          | EN, ADDR, SCL, SDA                                                | -0.3V to $V_{VSYS}$ +0.3V |  |  |

| Each Load Switch Maximum C                        | continuous Current for V <sub>INX</sub> >1.8V (NOTE 2)            | 2A                        |  |  |

| Maximum Peak Swit                                 | ch Current for V <sub>INX</sub> >2V (NOTE 3)                      | 2.5A                      |  |  |

| Junction-to-ambient                               | Thermal Resistance θ <sub>JA</sub> <sup>(NOTE 4)</sup>            | 122°C/W                   |  |  |

| Operating Free                                    | -40°C to 85°C                                                     |                           |  |  |

| Maximum Juno                                      | ction Temperature T <sub>JMAX</sub>                               | 150°C                     |  |  |

| Storage                                           | Temperature T <sub>STG</sub>                                      | -65°C to 150°C            |  |  |

| Lead Temperatur                                   | e (Soldering 10 Seconds)                                          | 260°C                     |  |  |

|                                                   | ESD & Latch-Up                                                    |                           |  |  |

| HBM (Huma                                         | n Body Model) (NOTE 5)                                            | ±2kV                      |  |  |

| CDM(Charged                                       | d Device Model) (NOTE 6)                                          | ±1.5kV                    |  |  |

| Lat                                               | Latch-Up <sup>(NOTE 7)</sup>                                      |                           |  |  |

| Lau                                               | ын-ор <sup>ес</sup>                                               | -IT: -200mA               |  |  |

NOTE1: Conditions out of those ranges listed in "absolute maximum ratings" may cause permanent damages to the device. In spite of the limits above, functional operation conditions of the device should be within the ranges listed in "recommended operating conditions". Exposure to absolute-maximum-rated conditions for prolonged periods may affect device reliability.

NOTE2: Limited by thermal design.

NOTE3: Limited by thermal design, and tested in 10ms width pulse current.

NOTE4: Thermal resistance from junction to ambient is highly dependent on PCB layout.

NOTE5: The human body model is a 100pF capacitor discharged through a 1.5k $\Omega$  resistor into each pin. Test method: ESDA/JEDEC JS-001-2017.

NOTE6: All pins. Test Condition: ESDA/JEDEC JS-002-2018.

NOTE7: Test Condition: JESD78E.

## RECOMMENDED OPERATING CONDITIONS

| Symbol                             | Parameter               | Min. | Тур. | Max. | Unit     |

|------------------------------------|-------------------------|------|------|------|----------|

| V <sub>VSYS</sub>                  | VSYS voltage            | 1.5  |      | 5.5  | <b>V</b> |

| $V_{\text{IN}}$                    | Input voltage           | 1.2  |      | 5.5  | V        |

| Vout                               | Output voltage          | 0    |      | VIN  | V        |

| V <sub>EN</sub>                    | EN voltage              | 0    |      | 5.5  | V        |

| $V_{ADDR}$                         | ADDR voltage            | 0    |      | 5.5  | V        |

| V <sub>SCL</sub> /V <sub>SDA</sub> | SCL/SDA voltage         | 0    |      | 5.5  | V        |

| Cin                                | Input capacitance       | 0.1  | 1    |      | μF       |

| C <sub>OUT</sub>                   | Output load capacitance |      | 0.1  |      | μF       |

## **ELECTRICAL CHARACTERISTICS**

## **DC Electrical Characteristics**

$V_{VSYS}$ =1.8V,  $V_{INX}$ =3.3V,  $R_L$ =150 $\Omega$ ,  $C_{IN}$ =1 $\mu$ F,  $C_{OUT}$ =0.1 $\mu$ F,  $T_A$ =25°C for typical values (unless otherwise noted).

|                      | PARAMETER                                 | TEST CONDITION                                                                              |                      | MIN | TYP  | MAX | UNIT |

|----------------------|-------------------------------------------|---------------------------------------------------------------------------------------------|----------------------|-----|------|-----|------|

| POWER                | SUPPLY CURRENTS AN                        | ID LEAKAGES                                                                                 |                      |     |      |     |      |

|                      | Quiescent current for                     | V <sub>VSYS</sub> =V <sub>EN</sub> =5.0V, all switches on                                   |                      |     | 0.3  | 0.5 |      |

| I <sub>Q_VSYS</sub>  | VSYS when reverse current blocking of all | V <sub>VSYS</sub> =V <sub>EN</sub> =3.3V, all switches on                                   |                      | 0.2 | 0.5  | μΑ  |      |

|                      | channels off                              | V <sub>VSYS</sub> =V <sub>EN</sub> =1.8V, all switches on                                   |                      |     | 0.1  | 0.5 |      |

|                      | Quiescent current for                     | V <sub>VSYS</sub> =V <sub>EN</sub> =5.0V, all switches on                                   |                      |     | 1.9  | 4   |      |

| I <sub>QB_VSYS</sub> | VSYS when reverse current blocking of all | V <sub>VSYS</sub> =V <sub>EN</sub> =3.3V, all switches on                                   |                      |     | 1.5  | 3   | μΑ   |

|                      | channels on                               | V <sub>VSYS</sub> =V <sub>EN</sub> =1.8V, all switches on                                   |                      |     | 1.1  | 2   |      |

|                      |                                           | V <sub>VSYS</sub> =V <sub>SDA</sub> =V <sub>SCL</sub> =5.0V, V <sub>EN</sub> =0V            |                      |     | 10   | 500 |      |

| I <sub>SD_VSYS</sub> | Shutdown current for VSYS                 | V <sub>VSYS</sub> =V <sub>SDA</sub> =V <sub>SCL</sub> =3.3V, V <sub>EN</sub> =0V            |                      |     | 3    | 200 | nA   |

|                      | 1010                                      | V <sub>VSYS</sub> =V <sub>SDA</sub> =V <sub>SCL</sub> =1.8V, V <sub>EN</sub> =0V            |                      |     | 2    | 150 |      |

|                      | Quiescent current for                     | VINX=5.0V, VVSYS=VEN=1.8V, IOUT                                                             | <=0A                 |     | 125  | 550 |      |

| I <sub>Q_INX</sub>   | the input of any channel when reverse     |                                                                                             |                      |     | 30   | 500 | nA   |

|                      | current blocking off                      | VINX=1.8V, VVSYS=VEN=1.8V, IOUT                                                             | <=0A                 |     | 5    | 150 |      |

|                      | Quiescent current for                     | VINX=5.0V, VVSYS=VEN=1.8V, IOUT                                                             | <=0A                 |     | 0.62 | 1.5 |      |

| I <sub>QB_INX</sub>  | the input of any channel when reverse     | VINX=3.3V, VVSYS=VEN=1.8V, IOUT                                                             | <=0A                 |     | 0.49 | 1.3 | μA   |

|                      | current blocking on                       | V <sub>INX</sub> =1.8V, V <sub>VSYS</sub> =V <sub>EN</sub> =1.8V, I <sub>OUT</sub>          | <=0A                 |     | 0.47 | 1.2 |      |

|                      | ,                                         | $V_{INX}$ =5.0V, $V_{VSYS}$ =1.8V, $V_{EN}$ =0V $\vdash$                                    | T <sub>A</sub> =25°C |     | 30   | 800 |      |

|                      |                                           |                                                                                             | T <sub>A</sub> =85°C |     | 390  |     | nA   |

|                      | Shutdown current for                      | V -2.2V V -4.2V V -0V                                                                       | T <sub>A</sub> =25°C |     | 6    | 500 |      |

| I <sub>SD_INX</sub>  | channel                                   | ne input of any V <sub>INX</sub> =3.3V, V <sub>VSYS</sub> =1.8V, V <sub>EN</sub> =0V hannel | T <sub>A</sub> =85°C |     | 143  |     |      |

|                      |                                           | V -4 0V V -4 0V V -0V                                                                       | T <sub>A</sub> =25°C |     | 2    | 400 |      |

|                      |                                           | $V_{INX}$ =1.8V, $V_{VSYS}$ =1.8V, $V_{EN}$ =0V                                             | T <sub>A</sub> =85°C |     | 115  |     |      |

| I <sub>EN</sub>      | EN leakage current                        | V <sub>VSYS</sub> =1.5V~5.5V, V <sub>EN</sub> =0V~5.5V                                      |                      |     |      | 0.3 | μA   |

| I <sub>ADDR</sub>    | ADDR leakage current                      | V <sub>VSYS</sub> =1.5V~5.5V, V <sub>ADDR</sub> =0V~5.5                                     | V                    |     |      | 0.3 | μA   |

| I <sub>SCL</sub>     | SCL leakage current                       | V <sub>VSYS</sub> =1.5V~5.5V, V <sub>SCL</sub> =5V                                          |                      |     |      | 0.1 | μA   |

| I <sub>SDA</sub>     | SDA leakage current                       | V <sub>VSYS</sub> =1.5V~5.5V, V <sub>SDA</sub> =5V                                          |                      |     |      | 0.1 | μA   |

| RESISTA              | NCE CHARACTERISTIC                        | S                                                                                           |                      |     |      |     |      |

|                      |                                           | V <sub>INX</sub> =5.0V, I <sub>OUTX</sub> =200mA                                            |                      |     | 56   | 80  |      |

| Ron                  | on-state resistance of any channel        | V <sub>INX</sub> =3.3V, I <sub>OUTX</sub> =200mA                                            |                      |     | 71   | 100 | mΩ   |

|                      | any onamor                                | V <sub>INX</sub> =1.8V, I <sub>OUTX</sub> =200mA                                            |                      |     | 122  | 150 |      |

| R <sub>PD</sub>      | OUT port discharge resistance             | V <sub>VSYS</sub> =1.8V, V <sub>IN</sub> =3.3V, V <sub>OUT</sub> =1.0V                      | /                    | 35  | 68   | 100 | Ω    |

|                       | PARAMETER                            | TEST CONDITION                                                                | MIN | TYP | MAX | UNIT |

|-----------------------|--------------------------------------|-------------------------------------------------------------------------------|-----|-----|-----|------|

| R <sub>EN</sub>       | EN pin pull-down resistance          | V <sub>VSYS</sub> =1.5V~5.5V                                                  | 8   |     |     | МΩ   |

| Raddr                 | ADDR pin pull-down resistance        | V <sub>VSYS</sub> =1.5V~5.5V                                                  |     |     |     | МΩ   |

| THERSH                | OLD CHARACTERISTIC                   | S                                                                             |     |     |     |      |

| V <sub>IH</sub>       | High-level input voltage for EN/ADDR |                                                                               | 1.0 |     |     | V    |

| VIL                   | Low-level input voltage for EN/ADDR  | •                                                                             |     |     | 0.4 | V    |

| TRUE RE               | VERSE CURRENT BLO                    | CKING CHARACTERISTICS                                                         |     |     |     |      |

| V <sub>T_RCB</sub>    | RCB protection trip point            | V <sub>IN</sub> =3.3V, V <sub>T_RCB</sub> =V <sub>OUT</sub> -V <sub>INX</sub> |     | 70  | 125 | mV   |

| V <sub>R_RCB</sub>    | RCB protection release point         | VIN=3.3V, VR_RCB=VINX-VOUT                                                    |     | 70  | 105 | mV   |

| V <sub>H_RCB</sub>    | RCB hysteresis voltage               | VIN=3.3V, VH_RCB= VT_RCB+VR_RCB                                               |     | 140 |     | mV   |

| I <sub>SD_OUT</sub>   | Shutdown current for OUT when RCB on | V <sub>IN</sub> =0V, V <sub>OUT</sub> =3.3V                                   |     | 280 | 800 | nA   |

| I <sup>2</sup> C CHAF | RACTERISTICS                         |                                                                               |     |     |     |      |

| V <sub>IH</sub> _IIC  | High-level input voltage for SCL/SDA |                                                                               | 1.0 |     |     | V    |

| V <sub>IL_IIC</sub>   | Low-level input voltage for SCL/SDA  |                                                                               |     |     | 0.4 | V    |

| Vol_sda               | Low output voltage for SDA           | Isink_sda=3mA                                                                 |     |     | 0.3 | V    |

| f <sub>SCL</sub>      | Clock frequency                      |                                                                               |     | 400 |     | kHz  |

## Switch Characteristics(1)

$V_{VSYS}=1.8V$ ,  $V_{INX}=3.3V$ ,  $R_L=150\Omega$ ,  $C_{OUT}=0.1\mu F$ ,  $T_A=25^{\circ}C$

|                      | PARAMETER                     | REG04h[7:0] | REG09h[7:0] | MIN | TYP  | MAX  | UNIT |

|----------------------|-------------------------------|-------------|-------------|-----|------|------|------|

|                      |                               | 0x00        | 0x00        | 180 | 512  | 880  | μs   |

| ton Voutx turn-on ti | V <sub>2</sub> - turn on time | 0x3F        | 0x00        | 20  | 56   | 95   | μs   |

|                      | VOUTX turn-on time            | 0x00        | 0x3F        | 80  | 244  | 500  | μs   |

|                      |                               | 0x3F        | 0x3F        | 500 | 1571 | 3000 | μs   |

|                      |                               | 0x00        | 0x00        | 200 | 380  | 560  | μs   |

|                      | V riging time                 | 0x3F        | 0x00        | 20  | 46   | 75   | μs   |

| <b>t</b> R           | Voutx rising time             | 0x00        | 0x3F        | 105 | 175  | 265  | μs   |

|                      |                               | 0x3F        | 0x3F        | 550 | 1100 | 1700 | μs   |

|                                    | PARAMETER                        | REG04h[7:0] | REG09h[7:0] | MIN | TYP | MAX | UNIT |

|------------------------------------|----------------------------------|-------------|-------------|-----|-----|-----|------|

|                                    |                                  | 0x00        | 0x00        |     | 320 |     | μs   |

| <b>4</b> (2)                       | V ON delevitime                  | 0x3F        | 0x00        |     | 34  |     | μs   |

| t <sub>DON</sub> <sup>(2)</sup>    | V <sub>OUTX</sub> ON delay time  | 0x00        | 0x3F        |     | 150 |     | μs   |

|                                    |                                  | 0x3F        | 0x3F        |     | 900 |     | μs   |

|                                    |                                  | 0x00        | 0x00        |     | 4   |     | μs   |

| t <sub>OFF</sub> (2)               | Voutx turn-off time              | 0x3F        | 0x00        |     | 4   |     | μs   |

| lOFF(=)                            |                                  | 0x00        | 0x3F        |     | 4   |     | μs   |

|                                    |                                  | 0x3F        | 0x3F        |     | 4   |     | μs   |

|                                    |                                  | 0x00        | 0x00        |     | 1   |     | μs   |

| +(2)                               | V OFF doloy time                 | 0x3F        | 0x00        |     | 1   |     | μs   |

| t <sub>DOFF</sub> (2)              | V <sub>OUTX</sub> OFF delay time | 0x00        | 0x3F        | 7   | 1   |     | μs   |

|                                    |                                  | 0x3F        | 0x3F        |     | 1   |     | μs   |

|                                    |                                  | 0x00        | 0x00        |     | 14  |     | μs   |

| t <sub>F</sub> (2)                 | V <sub>OUTX</sub> falling time   | 0x3F        | 0x00        |     | 14  |     | μs   |

| \(\mathbb{l}\mathbb{F}\^{\sigma}\) |                                  | 0x00        | 0x3F        | _   | 14  |     | μs   |

|                                    |                                  | 0x3F        | 0x3F        |     | 14  |     | μs   |

$V_{VSYS}=1.8V$ ,  $V_{INX}=3.3V$ ,  $R_L=500\Omega$ ,  $C_{OUT}=0.1\mu F$ ,  $T_A=25^{\circ}C$

|                                 | PARAMETER                       | REG04h[7:0] | REG09h[7:0] | MIN | TYP  | MAX | UNIT |

|---------------------------------|---------------------------------|-------------|-------------|-----|------|-----|------|

|                                 |                                 | 0x00        | 0x00        |     | 472  |     | μs   |

| t <sub>ON</sub> (2)             | Vturn on time                   | 0x3F        | 0x00        |     | 54   |     | μs   |

| lON(=)                          | V <sub>OUTX</sub> turn-on time  | 0x00        | 0x3F        |     | 223  |     | μs   |

|                                 |                                 | 0x3F        | 0x3F        |     | 1487 |     | μs   |

|                                 |                                 | 0x00        | 0x00        |     | 364  |     | μs   |

| t <sub>R</sub> (2)              | Voutx rising time               | 0x3F        | 0x00        |     | 39   |     | μs   |

| IR(=)                           |                                 | 0x00        | 0x3F        |     | 165  |     | μs   |

|                                 |                                 | 0x3F        | 0x3F        |     | 1026 |     | μs   |

|                                 |                                 | 0x00        | 0x00        |     | 295  |     | μs   |

| <b>+</b> (2)                    | V ON dolov timo                 | 0x3F        | 0x00        |     | 34   |     | μs   |

| t <sub>DON</sub> <sup>(2)</sup> | V <sub>OUTX</sub> ON delay time | 0x00        | 0x3F        |     | 140  |     | μs   |

|                                 |                                 | 0x3F        | 0x3F        |     | 840  |     | μs   |

|                       | PARAMETER                        | REG04h[7:0] | REG09h[7:0] | MIN | TYP | MAX | UNIT |

|-----------------------|----------------------------------|-------------|-------------|-----|-----|-----|------|

|                       |                                  | 0x00        | 0x00        |     | 5   |     | μs   |

| toff <sup>(2)</sup>   | V <sub>OUTX</sub> turn-off time  | 0x3F        | 0x00        |     | 5   |     | μs   |

| (OFF(=)               | Voorx turn-on time               | 0x00        | 0x3F        |     | 5   |     | μs   |

|                       |                                  | 0x3F        | 0x3F        |     | 5   |     | μs   |

|                       | V <sub>OUTX</sub> OFF delay time | 0x00        | 0x00        |     | 1   |     | μs   |

| t <sub>DOFF</sub> (2) |                                  | 0x3F        | 0x00        |     | 1   |     | μs   |

| LDOFF(=)              |                                  | 0x00        | 0x3F        |     | 1   |     | μs   |

|                       |                                  | 0x3F        | 0x3F        |     | 1   |     | μs   |

|                       |                                  | 0x00        | 0x00        |     | 15  |     | μs   |

| t <sub>F</sub> (2)    | Voutx falling time               | 0x3F        | 0x00        |     | 15  |     | μs   |

| LF(=)                 |                                  | 0x00        | 0x3F        |     | 15  |     | μs   |

|                       |                                  | 0x3F        | 0x3F        |     | 15  |     | μs   |

NOTE1: X=1,2,3,4,5,6

NOTE2:This parameter is guaranteed by design and characterization; not production tested.

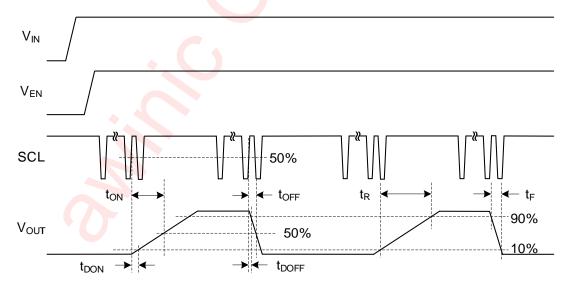

## **TIMING DIAGRAM**

Figure 5 AW35206 Timing Diagram

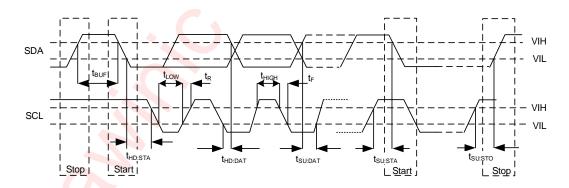

## **12C INTERFACE TIMING**

| SYMBOL              | DESCRIPTION                               |       | MIN | TYP | MAX | UNIT |

|---------------------|-------------------------------------------|-------|-----|-----|-----|------|

| FscL                | Interface Clock Frequency                 |       |     |     | 400 | kHz  |

| 4                   | Decliteb Time                             | SCL   |     | 83  |     | ns   |

| <b>t</b> DEGLITCH   | Deglitch Time                             | SDA   | 4   | 115 |     | ns   |

| t <sub>HD:STA</sub> | (Repeat-Start) Start Condition Hold Ti    | me    | 0.6 |     | •   | μs   |

| t <sub>LOW</sub>    | Low Level Width of SCL                    |       |     | U   |     | μs   |

| tніgн               | High Level Width of SCL                   |       |     | ,   |     | μs   |

| tsu:sta             | (Repeat-Start) Start Condition Setup Time |       |     |     |     | μs   |

| thd:dat             | Data Hold Time                            | . (7) | 0   |     |     | μs   |

| SYMBOL              | DESCRIPTION                               |       | MIN | TYP | MAX | UNIT |

| tsu:dat             | Data Setup Time                           |       | 0.1 |     |     | μs   |

| t <sub>R</sub>      | Rising Time of SDA and SCL                |       |     |     | 0.3 | μs   |

| t <sub>F</sub>      | Falling Time of SDA and SCL               |       |     |     | 0.3 | μs   |

| tsu:sто             | Stop Condition Setup Time                 |       |     |     |     | μs   |

| t <sub>BUF</sub>    | Time Between Start and Stop Condition     | on    | 1.3 |     |     | μs   |

Figure 6 I<sup>2</sup>C Interface Timing

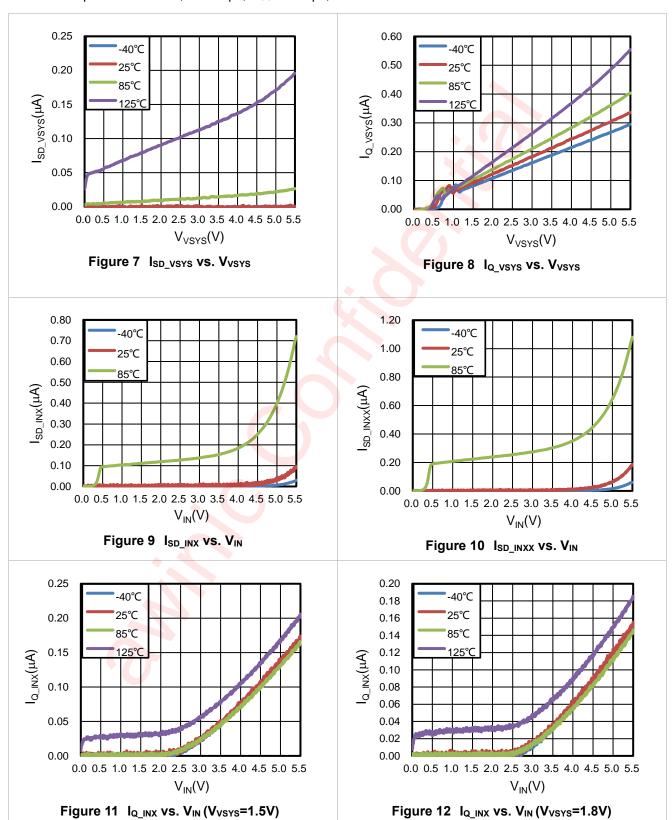

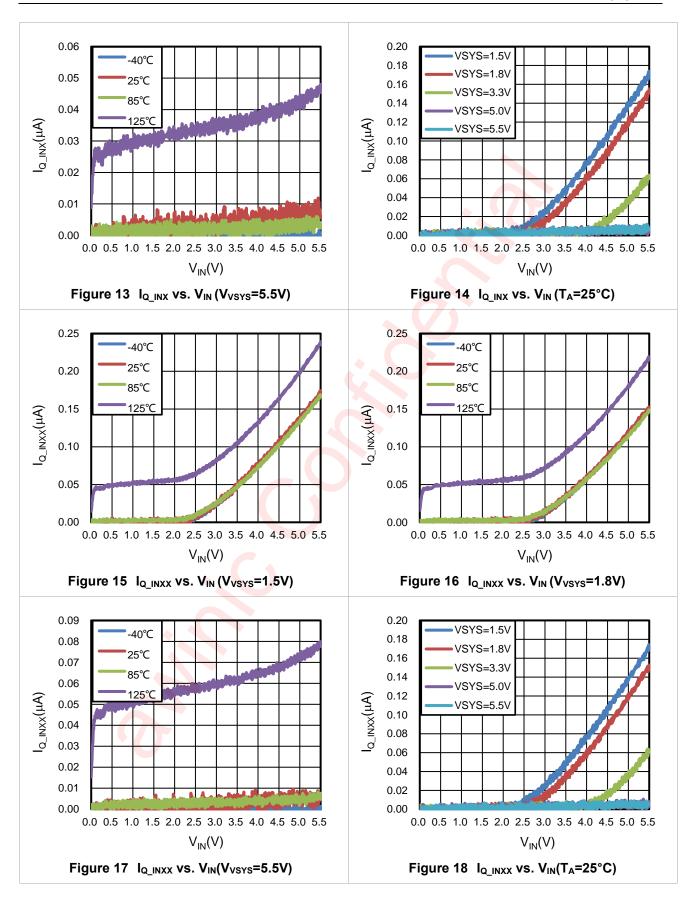

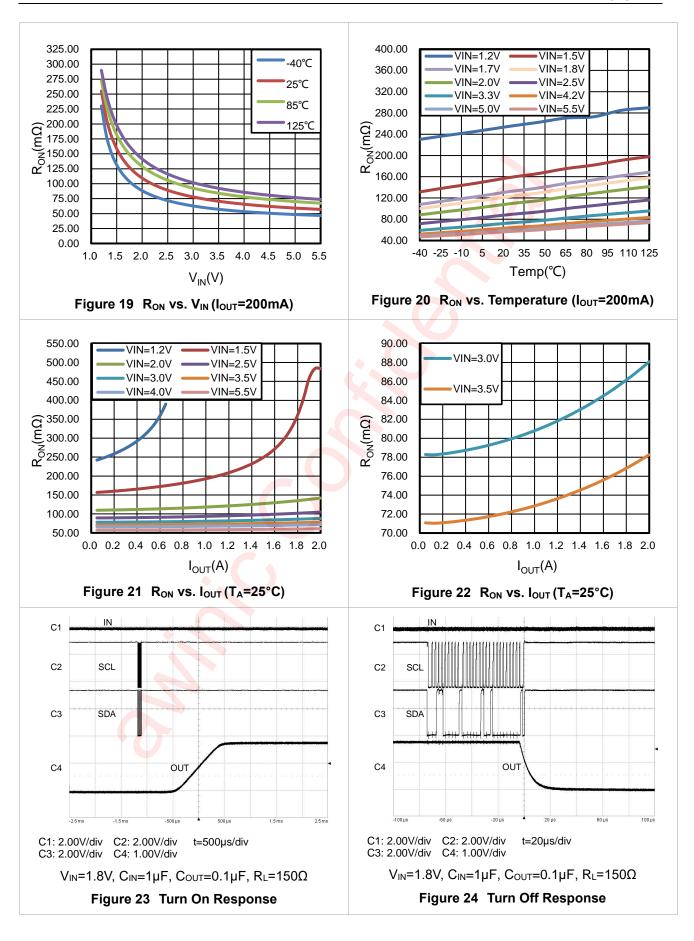

## **TYPICAL CHARACTERISTICS**

Ambient temperature is 25°C,  $C_{IN}$  = 1 $\mu$ F,  $C_{OUT}$  = 0.1 $\mu$ F, unless otherwise noted.

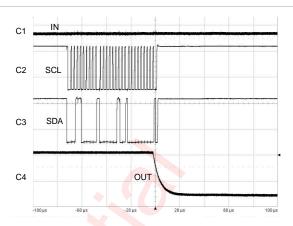

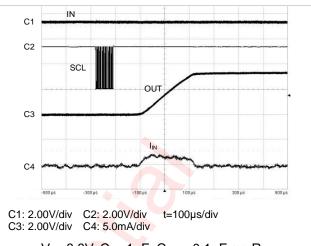

$V_{\text{IN}}$ =3.3V,  $C_{\text{IN}}$ =1 $\mu$ F,  $C_{\text{OUT}}$ =0.1 $\mu$ F,  $R_{\text{L}}$ =150 $\Omega$

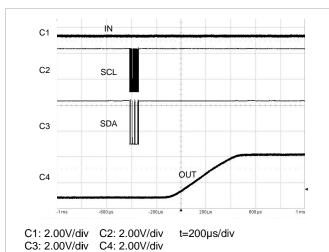

Figure 25 Turn On Response

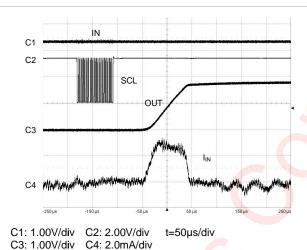

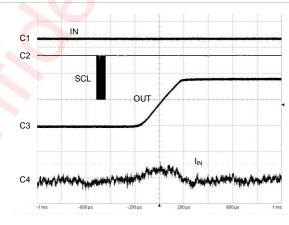

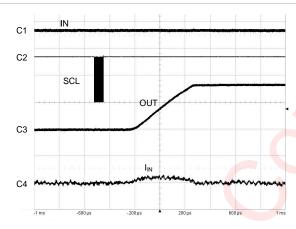

V<sub>IN</sub>=1.8V, C<sub>IN</sub>=1μF, C<sub>OUT</sub>=0.1μF, no R<sub>L</sub>

Figure 27 Inrush Current (Idsw\_tr1/0=01)

C1: 1.00V/div C2: 2.00V/div t=500µs/div C3: 1.00V/div C4: 2.0mA/div

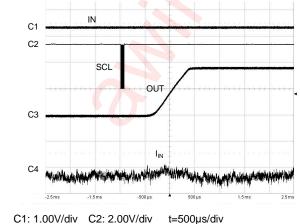

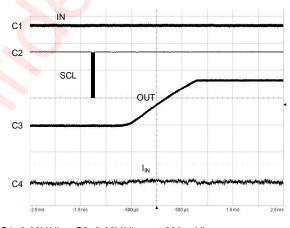

$V_{IN}=1.8V$ ,  $C_{IN}=1\mu F$ ,  $C_{OUT}=0.1\mu F$ , no  $R_L$

Figure 29 Inrush Current (ldsw\_tr1/0=00)

C1: 2.00V/div C2: 2.00V/div t=20µs/div C3: 2.00V/div C4: 2.00V/div

$V_{IN}$ =3.3V,  $C_{IN}$ =1 $\mu$ F,  $C_{OUT}$ =0.1 $\mu$ F,  $R_L$ =150 $\Omega$

Figure 26 Turn Off Response

C1: 1.00V/div C2: 2.00V/div  $t=200\mu s/div$  C3: 1.00V/div C4: 2.0mA/div

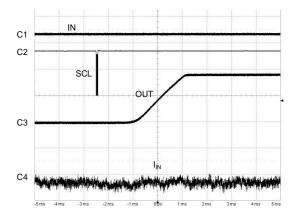

$V_{IN}$ =1.8V,  $C_{IN}$ =1 $\mu$ F,  $C_{OUT}$ =0.1 $\mu$ F, no  $R_L$

Figure 28 Inrush Current (Idsw\_tr1/0=10)

C1: 1.00V/div C2: 2.00V/div t=1ms/div C3: 1.00V/div C4: 2.0mA/div

$V_{IN}$ =1.8V,  $C_{IN}$ =1 $\mu$ F,  $C_{OUT}$ =0.1 $\mu$ F, no  $R_L$

Figure 30 Inrush Current (Idsw\_tr1/0=11)

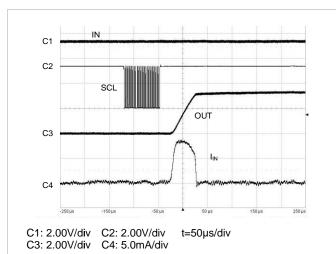

V<sub>IN</sub>=3.3V, C<sub>IN</sub>=1μF, C<sub>OUT</sub>=0.1μF, no R<sub>L</sub>

Figure 31 Inrush Current (Idsw\_tr1/0=01)

V<sub>IN</sub>=3.3V, C<sub>IN</sub>=1μF, C<sub>OUT</sub>=0.1μF, no R<sub>L</sub> Figure 32 Inrush Current (Idsw\_tr1/0=10)

C1: 2.00V/div C2: 2.00V/div t=200µs/div C3: 2.00V/div C4: 5.0mA/div

$V_{IN}=3.3V$ ,  $C_{IN}=1\mu F$ ,  $C_{OUT}=0.1\mu F$ ,  $n_O$   $R_L$

Figure 33 Inrush Current (Idsw\_tr1/0=00)

C1: 2.00V/div C2: 2.00V/div t=200µs/div C3: 2.00V/div C4: 5.0mA/div

$V_{IN}$ =3.3V,  $C_{IN}$ =1 $\mu F$ ,  $C_{OUT}$ =0.1 $\mu F$ , no  $R_L$

Figure 34 Inrush Current (Idsw\_tr1/0=11)

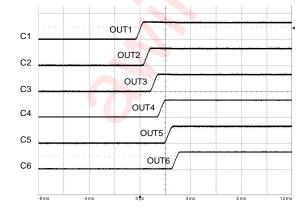

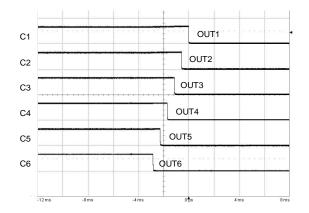

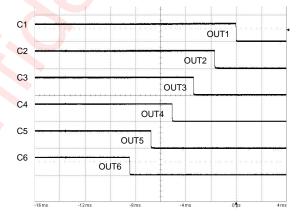

C1: 5.00V/div C2: 5.00V/div C3: 5.00V/div t=2.0ms/div C4: 5.00V/div C5: 5.00V/div C6: 5.00V/div

$V_{\text{IN}}$ =3.3V,  $C_{\text{IN}}$ =1 $\mu$ F,  $C_{\text{OUT}}$ =0.1 $\mu$ F,  $R_{\text{L}}$ =150 $\Omega$

Figure 35 Power up with seq\_speed<1:0>=00

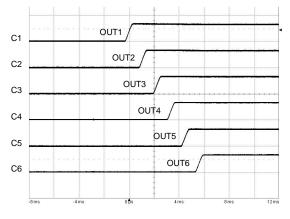

C1: 5.00V/div C2: 5.00V/div C3: 5.00V/div t=2.0ms/div C4: 5.00V/div C5: 5.00V/div C6: 5.00V/div

$V_{IN}=3.3V$ ,  $C_{IN}=1\mu F$ ,  $C_{OUT}=0.1\mu F$ ,  $R_{L}=150\Omega$

Figure 36 Power down with seq\_speed<1:0>=00

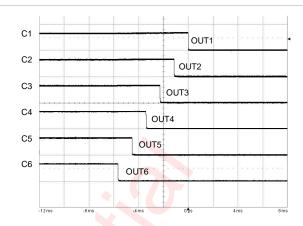

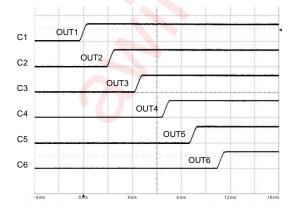

C1: 5.00V/div C2: 5.00V/div C3: 5.00V/div t=2.0ms/div C4: 5.00V/div C5: 5.00V/div C6: 5.00V/div

$V_{IN}=3.3V$ ,  $C_{IN}=1\mu F$ ,  $C_{OUT}=0.1\mu F$ ,  $R_{L}=150\Omega$

Figure 37 Power up with seq\_speed<1:0>=01

C1: 5.00V/div C2: 5.00V/div C3: 5.00V/div t=2.0ms/div C4: 5.00V/div C5: 5.00V/div C6: 5.00V/div

$V_{IN}=3.3V$ ,  $C_{IN}=1\mu F$ ,  $C_{OUT}=0.1\mu F$ ,  $R_{L}=150\Omega$

Figure 38 Power down with seq\_speed<1:0>=01

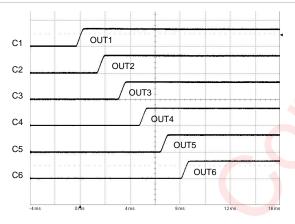

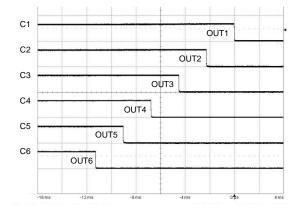

C1: 5.00V/div C2: 5.00V/div C3: 5.00V/div t=4.0ms/div C4: 5.00V/div C5: 5.00V/div C6: 5.00V/div

$V_{IN}=3.3V$ ,  $C_{IN}=1\mu F$ ,  $C_{OUT}=0.1\mu F$ ,  $R_{L}=150\Omega$

Figure 39 Power up with seq\_speed<1:0>=10

C1: 5.00V/div C2: 5.00V/div C3: 5.00V/div t=4.0ms/div C4: 5.00V/div C5: 5.00V/div C6: 5.00V/div

$V_{IN}=3.3V$ ,  $C_{IN}=1\mu F$ ,  $C_{OUT}=0.1\mu F$ ,  $R_L=150\Omega$

Figure 40 Power down with seq\_speed<1:0>=10

C1: 5.00V/div C2: 5.00V/div C3: 5.00V/div t=4.0ms/div C4: 5.00V/div C5: 5.00V/div C6: 5.00V/div

$V_{\text{IN}}$ =3.3V,  $C_{\text{IN}}$ =1 $\mu$ F,  $C_{\text{OUT}}$ =0.1 $\mu$ F,  $R_{\text{L}}$ =150 $\Omega$

Figure 41 Power up with seq\_speed<1:0>=11

C1: 5.00V/div C2: 5.00V/div C3: 5.00V/div t=4.0ms/div C4: 5.00V/div C5: 5.00V/div C6: 5.00V/div

$V_{IN}=3.3V$ ,  $C_{IN}=1\mu F$ ,  $C_{OUT}=0.1\mu F$ ,  $R_{L}=150\Omega$

Figure 42 Power down with seq\_speed<1:0>=11

AW35206 Feb. 2023 V1.4

#### **DETAILED FUNCTIONAL DESCRIPTION**

The AW35206 integrates six PMOS load switches, and provides a low on-resistance for a low voltage drop across the device. The supply voltage of the device is from 1.5V to 5.5V and the input of the load switch is 1.2V~5.5V. All channels are controlled through I<sup>2</sup>C BUS for processors. Each output integrates a selectable quick discharge function block for necessity. A controlled slew rate is used in applications to limit the inrush current. Any load switch has the ability to block reverse current when the output voltage is higher than the input. Also this function can be disabled by I<sup>2</sup>C for low quiescent current.

#### TURN ON/OFF CONTROL

All channels of the device are opened when EN pin is tied low (disable) or pulled down by internal  $12M\Omega$  resistor, forcing PMOS switch off. The IN/OUT path is activated under a minimum input voltage of 1.2V if the corresponding channel is closed. Each load switch of the AW35206 can be enabled in two ways using the I<sup>2</sup>C interface if the EN pin is pulled high.

1. Setting Idswx\_seq<2:0>=000 in 0x05(LDSW12\_SEQ) or 0x06(LDSW34\_SEQ) or 0x07(LDSW56\_SEQ), making Idswx\_en=1 assigned to the load switch in register can enable the corresponding channel otherwise disable it.

EN

Idswx\_en

INX to OUTX

Low

OFF

High

OFF

ON

Table 1. Functional Table when LDSWXX SEQ Registers are 0x00

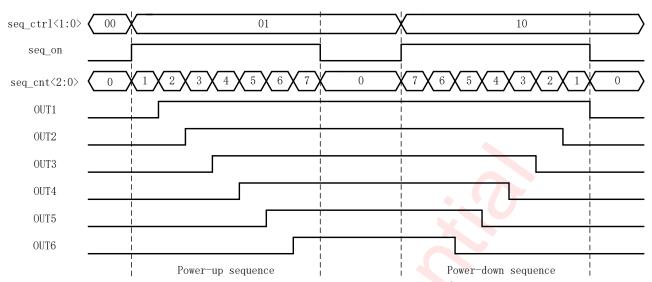

2. Setting Idswx\_seq<2:0>≠000 in 0x05(LDSW12\_SEQ) or 0x06(LDSW34\_SEQ) or 0x07(LDSW56\_SEQ), the corresponding load switch is controlled by power sequence in the register "SEQ\_CTR".

Writing "01" in seq\_ctrl<1:0> when seq\_on="0" executes a power-up sequence and seq\_cnt<2:0> will increase from "000" to "111", and the value of the seq\_cnt<2:0> is defined as slot. The bit seq\_on will be set "1" until the power-up sequence is finished, the load switch x turns on when the value of seq\_cnt<2:0> equals that of ldswx\_seq<2:0> after the time interval set by seq\_speed<1:0>. Seq\_on will be reset to "0" after seq\_cnt<2:0> finishes an increasing counting and seq\_cnt<2:0> is also reset to "000", which indicates the power-up sequence is over.

Similarly, a power-down sequence is triggered when the seq\_ctrl<1:0> is wrote "10", and seq\_cnt<2:0> will decrease from "111" to "000". The bit seq\_on will be set "1" until the power-down sequence is finished, the load switch x turns off when the value of seq\_cnt<2:0> equals that of ldswx\_seq<2:0> after the time interval defined by seq\_speed<1:0>. Seq\_on will be reset to "0" after seq\_cnt<2:0> finishes a decreasing counting and seq\_cnt<2:0> is also reset to "000", which indicates the power-down sequence is over.

A typical power-up/down sequence is illustrated in the figure 43 below, provided voltages of all the input pins are good enough.

17

NOTE: The register bit  $ldswx_seq<2:0>(x=1,2,...,6)$  is set "001" to "110" by  $l^2C$  interface.

Figure 43 A typical power-up/down sequence

#### **SLEW RATE CONTROL**

When the switch is enabled, the device regulates the gate voltage of MOSFET, and controls the  $V_{OUT}$  slew rate during  $t_R$  to avoid a large input inrush current. The rising time of the  $V_{OUT}$  can be set in four levels through  $I^2C$  BUS. The feature reduces the interference to the power supply.

#### QUICK OUTPUT DISCHARGE

The AW35206 includes the Quick Output Discharge (QOD) feature for the output of every load switch, in order to discharge the application capacitor connected on OUT pin. This function can be disabled by  $I^2C$  and is turned on by default. When EN pin or the control bit in register LDSW\_EN is set to low level (disable state), a discharge resistance with a typical value of  $68\Omega$  connected between the output and ground, pulls down the output and prevents it from floating.

#### REVERSE CURRENT BLOCKING

The AW35206 integrates a function block that can block reverse current for each load switch, which can prevent the current from flowing through the P-FET or the body diode when the output voltage is higher than the input. This ability can be turned off for low current consumption in the register LDSW\_RCB.

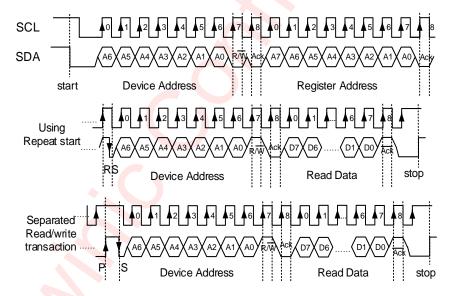

#### **GENERAL I<sup>2</sup>C OPERATION**

The AW35206 is compatible with I<sup>2</sup>C interface. The SCL line is an input and the SDA line is a bi-directional open-drain output. The I<sup>2</sup>C salve address of AW35206 is 0011000b (ADDR pin connected to GND) or 0011001b (ADDR pin connected to VSYS). The I<sup>2</sup>C interface is accessible as long as the supply voltage is above 1.5V.

**Table 2. Device Address**

| A7 | A6 | A5 | A4 | A3 | A2 | A1   | Α0  |

|----|----|----|----|----|----|------|-----|

| 0  | 0  | 1  | 1  | 0  | 0  | ADDR | R/W |

ADDR=0: slave address=0x18H;

ADDR=1: slave address=0x19H.

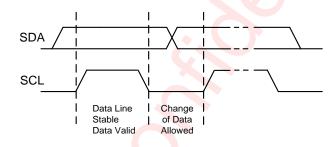

#### DATA VALIDATION

When SCL is high level, SDA level must be constant. SDA can be changed only when SCL is low level.

Figure 44 Data Validation Diagram

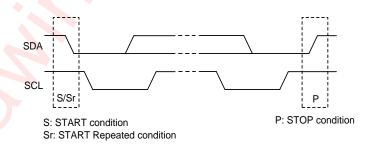

#### I<sup>2</sup>C START/STOP

I<sup>2</sup>C start: SDA changes from high level to low level when SCL is high level.

I<sup>2</sup>C stop: SDA changes from low level to high level when SCL is high level.

Figure 45 Start and Stop Conditions

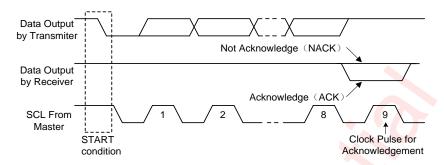

## **ACK (ACKNOWLEDGEMENT)**

ACK means the successful transfer of I<sup>2</sup>C bus data. After master sends 8bits data, SDA must be released; SDA is pulled to GND by slave device when slave acknowledges.

When master reads, slave device sends 8bit data, releases the SDA and waits for ACK from master. If ACK is send and I<sup>2</sup>C stop is not send by master, slave device sends the next data. If ACK is not send by master, slave device stops to send data and waits for I<sup>2</sup>C stop.

Figure 46 Acknowledgement Diagram

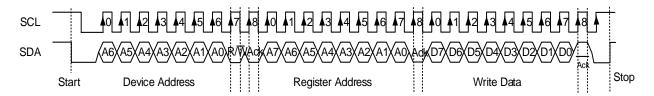

#### **WRITE PROCESS**

One data bit is transferred during each clock pulse. Data is sampled during the high state of the serial clock (SCL). Consequently, throughout the clock's high period, the data should remain stable. Any changes on the SDA line during the high state of the SCL and in the middle of a transaction, aborts the current transaction. New data should be sent during the low SCL state. This protocol allows a single data line to transfer both command/control information and data using the synchronous serial clock.

Each data transaction is composed of a Start Condition, a number of byte transfers (set by the software) and a Stop Condition to terminate the transaction. Every byte written to the SDA bus must be 8 bits long and is transferred with the most significant bit first. After each byte, an Acknowledge signal must follow.

In a write process, the following steps should be followed:

- a) Master device generates START condition. The "START" signal is generated by lowering the SDA signal while the SCL signal is high.

- b) Master device sends slave address (7-bit) and the data direction bit (r/w = 0).

- c) Slave device sends acknowledge signal if the slave address is correct.

- d) Master sends control register address (8-bit)

- e) Slave sends acknowledge signal

- f) Master sends data byte to be written to the addressed register

- g) Slave sends acknowledge signal

- h) If master will send further data bytes the control register address will be incremented by one after acknowledge signal (repeat steps f and g)

- i) Master generates STOP condition to indicate write cycle end

Figure 47 I<sup>2</sup>C Write Timing

## **READ PROCESS**

In a read cycle, the following steps should be followed:

- a) Master device generates START condition

- b) Master device sends slave address (7-bit) and the data direction bit (R/W = 0).

- c) Slave device sends acknowledge signal if the slave address is correct.

- d) Master sends control register address (8-bit)

- e) Slave sends acknowledge signal

- f) Master generates STOP condition followed with START condition or REPEAT START condition

- g) Master device sends slave address (7-bit) and the data direction bit (R/W = 1).

- h) Slave device sends acknowledge signal if the slave address is correct.

- i) Slave sends data byte from addressed register.

- j) If the master device sends acknowledge signal, the slave device will increase the control register address by one, then send the next data from the new addressed register.

- k) If the master device generates STOP condition, the read cycle is ended.

Figure 48 I<sup>2</sup>C Read Timing

## APPLICATION INFORMATION

#### POWER SUPPLY RECOMMENDATIONS

The device is designed to operate with a Vvsys range of 1.5V to 5.5V while the input voltage of each load switch is 1.2V~5.5V. The supply must be well regulated and placed as close to the device VSYS terminal as possible. It must also be able to withstand all transient and load currents, using a recommended input capacitance of 1µF if necessary. If the supply is located more than a few inches from the device terminals, additional bulk capacitance may be required in addition to the ceramic bypass capacitors. If additional bulk capacitance is required, an electrolytic, tantalum, or ceramic capacitor of 10µF may be sufficient.

#### MANAGING INRUSH CURRENT

When the switch is enabled, the output capacitors must be charged up from 0V to V<sub>IN</sub>. An input inrush current will appear. The Inrush current can be calculated using Equation 1:

$$I_{inrush} = C_{OUT} \frac{dV_{OUT}}{dt}$$

(1)

where:

- Cout = Output capacitance

- $dV_{OUT}$  = Change of output voltage, equals to  $V_{IN}$

- dt = Rise time t<sub>R</sub>.

The AW35206 offers a controlled slew rate for minimizing inrush current.

#### POWER DISSIPATION

The power dissipation produced by the power MOSFET in on-state can be calculated with the following equation:

$$P_{\rm D} = R_{\rm ON} \times I_{\rm OUT}^2 \tag{2}$$

Where:

- P<sub>D</sub> = Power dissipation (W)

- R<sub>ON</sub> = Power MOSFET on-state resistance (Ω)

- I<sub>OUT</sub> = Output current (A)

#### THERMAL CONSIDERATIONS

Main contributor in term of junction temperature T<sub>J</sub>(max) is the power dissipation, and T<sub>J</sub>(max) should be restricted to 125°C under on-state. Junction temperature is directly proportional to power dissipation in the device, it can be calculated by the following equation:

$$T_{I} = T_{A} + R_{HIA} \times P_{D} \tag{3}$$

Where: • T<sub>J</sub> = Junction temperature of the device

- T<sub>A</sub> = Ambient temperature

- PD = Power dissipation of the device

- ReJA = Junction to ambient thermal resistance. This parameter is highly dependent on board layout.

# **Register Configuration**

## **Register List**

| ADDR | NAME       | Bit7    | Bit6    | Bit5      | Bit4           | Bit3      | Bit2         | Bit1           | Bit0      | Default |

|------|------------|---------|---------|-----------|----------------|-----------|--------------|----------------|-----------|---------|

| 00h  | CHIPID     | 0       | 0       | 1         | 1              | 0         | 0            | chip_id<1:0>   |           | 0x33    |

| 01h  | VERID      | 0       | 0       | 0         | 0              | 0         | 0            | ver_id         | l<1:0>    | 0x00    |

| 02h  | LDSW_EN    | 0       | 0       | ldsw6_en  | ldsw5_en       | ldsw4_en  | ldsw3_en     | ldsw2_en       | ldsw1_en  | 0x00    |

| 03h  | LDSW_DIS   | 0       | 0       | ldsw6_dis | ldsw5_dis      | ldsw4_dis | ldsw3_dis    | ldsw2_dis      | ldsw1_dis | 0x3F    |

| 04h  | LDSW_TR0   | 0       | 0       | ldsw6_tr0 | ldsw5_tr0      | ldsw4_tr0 | ldsw3_tr0    | ldsw2_tr0      | ldsw1_tr0 | 0x00    |

| 05h  | LDSW12_SEQ | 0       | 0       | lo        | ldsw2_seq<2:0> |           |              | ldsw1_seq<2:0> |           |         |

| 06h  | LDSW34_SEQ | 0       | 0       | lo        | dsw4_seq<2:0   | >         | lo           | ldsw3_seq<2:0> |           |         |

| 07h  | LDSW56_SEQ | 0       | 0       | lo        | dsw6_seq<2:0   | >         | lo           | dsw5_seq<2:0   | 0x00      |         |

| 08h  | SEQ_CTR    | seq_spe | ed<1:0> | seq_ct    | rl<1:0>        | seq_on    | seq_cnt<2:0> |                |           | 0x00    |

| 09h  | LDSW_TR1   | 0       | 0       | ldsw6_tr1 | ldsw5_tr1      | ldsw4_tr1 | ldsw3_tr1    | ldsw2_tr1      | ldsw1_tr1 | 0x00    |

| 0Ah  | LDSW_RCB   | 0       | 0       | ldsw6_rcb | ldsw5_rcb      | ldsw4_rcb | ldsw3_rcb    | ldsw2_rcb      | ldsw1_rcb | 0x00    |

| 0Bh  | LDSW_ON    | 0       | 0       | ldsw6_on  | ldsw5_on       | ldsw4_on  | ldsw3_on     | ldsw2_on       | ldsw1_on  | 0x00    |

| 69h  | RSTN       | 0       | 0       | 0         | 0              | 0         | 0            | 0              | 0         | 0x00    |

## **Register Detailed Description**

## • CHIPID: Chip ID register(Address 00h)

| Bi  | it | Symbol       | R/W | Description                  | Default |

|-----|----|--------------|-----|------------------------------|---------|

| 7:2 | 2  | Chip_id<7:2> | R   | The product ID with revision | 001100  |

| 1:0 | 0  | Chip_id<1:0> | R   | The product is with revision | 11      |

## VERID: Version ID register(Address 01h)

| Bit | Symbol      | R/W | Description                 | Default |

|-----|-------------|-----|-----------------------------|---------|

| 7:2 | Ver_id<7:2> | R   | The device ID with revision | 000000  |

| 1:0 | Ver_id<1:0> | R   | The device is with revision | 00      |

#### LDSW\_EN: Load switch enable register(Address 02h)

This is load switch enable control register by I<sup>2</sup>C while the EN pin is pulled high. This register can be written to enable or disable the corresponding load switch.

| Bit | Symbol   | R/W | Description                                  | Default |

|-----|----------|-----|----------------------------------------------|---------|

| 7:6 | Reserved | R   | Reserved                                     | 00      |

| 5   | Ldsw6_en | R/W | Load switch 6 control:  0: Disable 1: Enable | 0       |

| 4   | Ldsw5_en | R/W | Load switch 5 control:  0: Disable 1: Enable | 0       |

| 3   | Ldsw4_en | R/W | Load switch 4 control:  0: Disable 1: Enable | 0       |

| 2 | Ldsw3_en   | R/W   | Load switch 3 control: | 0 |  |  |

|---|------------|-------|------------------------|---|--|--|

|   |            |       | 0: Disable 1: Enable   | 0 |  |  |

| 1 | Ldsw2 en   | R/W   | Load switch 2 control: | 0 |  |  |

| 1 | Luswz_en   | FX/VV | 0: Disable 1: Enable   |   |  |  |

| 0 | l dourt on | D/M   | Load switch 1 control: | 0 |  |  |

| 0 | Ldsw1_en   | R/W   | 0: Disable 1: Enable   | 0 |  |  |

## LDSW\_DIS: Load switch output discharge selecting register(Address 03h)

This register sets the discharge function of each load switch output.

| Bit | Symbol    | R/W | Description                                                                                   | Default |

|-----|-----------|-----|-----------------------------------------------------------------------------------------------|---------|

| 7:6 | Reserved  | R   | Reserved                                                                                      | 00      |

|     |           |     | Load switch 6 discharge function:                                                             |         |

| 5   | Ldsw6_dis | R/W | 0: Disable. OUT6 discharge will not be activated when load switch 6 is disabled by any event. | 1       |

|     |           |     | 1: Enable. OUT6 discharge will be activated when load switch 6 is disabled.                   |         |

|     |           |     | Load switch 5 discharge function:                                                             |         |

| 4   | Ldsw5_dis | R/W | 0: Disable. OUT5 discharge will not be activated when load switch 5 is disabled by any event. | 1       |

|     |           |     | 1: Enable. OUT5 discharge will be activated when load switch 5 is disabled.                   |         |

|     |           |     | Load switch 4 discharge function:                                                             |         |

| 3   | Ldsw4_dis | R/W | 0: Disable. OUT4 discharge will not be activated when load switch 4 is disabled by any event. | 1       |

|     |           | C   | 1: Enable. OUT4 discharge will be activated when load switch 4 is disabled.                   |         |

|     |           |     | Load switch 3 discharge function:                                                             |         |

| 2   | Ldsw3_dis | R/W | 0: Disable. OUT3 discharge will not be activated when load switch 3 is disabled by any event. | 1       |

|     |           |     | 1: Enable. OUT3 discharge will be activated when load switch 3 is disabled.                   |         |

|     |           |     | Load switch 2 discharge function:                                                             |         |

| 1   | Ldsw2_dis | R/W | 0: Disable. OUT2 discharge will not be activated when load switch 2 is disabled by any event. | 1       |

|     |           |     | 1: Enable. OUT2 discharge will be activated when load switch 2 is disabled.                   |         |

|     |           |     | Load switch 1 discharge function:                                                             |         |

| 0   | Ldsw1_dis | R/W | 0: Disable. OUT1 discharge will not be activated when load switch 1 is disabled by any event. | 1       |

|     |           |     | 1: Enable. OUT1 discharge will be activated when load switch 1 is disabled.                   |         |

# LDSW\_TR0 & LDSW\_TR1: Load switch output voltage rising time setting register(Address 04h & 09h)

Typically,  $V_{INX}$  =3.3V,  $R_L$ =150 $\Omega$ ,  $C_{OUT}$ =0.1 $\mu$ F,  $T_A$ =25 $^{\circ}$ C.

| Bit | Symbol                 | R/W | Description                                                                                                    | Default |

|-----|------------------------|-----|----------------------------------------------------------------------------------------------------------------|---------|

| 7:6 | Reserved               | R   | Reserved                                                                                                       | 00      |

| 5   | Ldsw6_tr1<br>Ldsw6_tr0 | R/W | Load switch 6 output voltage (from 10% to 90%) rising time setting: 00: 380µs; 01: 46µs; 10: 175µs; 11: 1100µs | 0/0     |

| 4   | Ldsw5_tr1<br>Ldsw5_tr0 | R/W | Load switch 5 output voltage (from 10% to 90%) rising time setting: 00: 380µs; 01: 46µs; 10: 175µs; 11: 1100µs | 0/0     |

| 3   | Ldsw4_tr1<br>Ldsw4_tr0 | R/W | Load switch 4 output voltage (from 10% to 90%) rising time setting: 00: 380µs; 01: 46µs; 10: 175µs; 11: 1100µs | 0/0     |

| 2   | Ldsw3_tr1<br>Ldsw3_tr0 | R/W | Load switch 3 output voltage (from 10% to 90%) rising time setting: 00: 380µs; 01: 46µs; 10: 175µs; 11: 1100µs | 0/0     |

| 1   | Ldsw2_tr1<br>Ldsw2_tr0 | R/W | Load switch 2 output voltage (from 10% to 90%) rising time setting: 00: 380µs; 01: 46µs; 10: 175µs; 11: 1100µs | 0/0     |

| 0   | Ldsw1_tr1<br>Ldsw1_tr0 | R/W | Load switch 1 output voltage (from 10% to 90%) rising time setting: 00: 380µs; 01: 46µs; 10: 175µs; 11: 1100µs | 0/0     |

#### LDSW\_SEQ12: Load switch power sequence setting register(Address 05h)

There are 7 time slots for every load switch to turn on/off. The power-up sequence starts from slot1 to slot7, and the power-down sequence is on the contrary. Turning on and off of each load switch can be set at any time slot as defined below.

| Bit | Symbol         | R/W | Description                                    | Default |

|-----|----------------|-----|------------------------------------------------|---------|

| 7:6 | Reserved       | R   | Reserved                                       | 00      |

|     |                |     | 000: Controlled by the bit ldsw2_en;           |         |

| 5:3 | Ldsw2_seq<2:0> | R/W | 001: slot1; 010: slot2; 011: slot3;            | 000     |

|     |                |     | 100: slot4; 101: slot5; 110: slot6; 111: slot7 |         |

|     |                |     | 000: Controlled by the bit ldsw1_en;           |         |

| 2:0 | Ldsw1_seq<2:0> | R/W | 001: slot1; 010: slot2; 011: slot3;            | 000     |

|     |                |     | 100: slot4; 101: slot5; 110: slot6; 111: slot7 |         |

#### LDSW\_SEQ34: Load switch power sequence setting register(Address 06h)

There are 7 time slots for every load switch to turn on/off. The power-up sequence starts from slot1 to slot7, and the power-down sequence is on the contrary. Turning on and off of each load switch can be set at any time slot as defined below.

| Bit | Symbol         | R/W | Description                                    | Default |

|-----|----------------|-----|------------------------------------------------|---------|

| 7:6 | Reserved       | R   | Reserved                                       | 00      |

|     |                |     | 000: Controlled by the bit ldsw4_en;           |         |

| 5:3 | Ldsw4_seq<2:0> | R/W | 001: slot1; 010: slot2; 011: slot3;            | 000     |

|     |                |     | 100: slot4; 101: slot5; 110: slot6; 111: slot7 |         |

|     |                |     | 000: Controlled by the bit ldsw3_en;           |         |

| 2:0 | Ldsw3_seq<2:0> | R/W | 001: slot1; 010: slot2; 011: slot3;            | 000     |

|     |                |     | 100: slot4; 101: slot5; 110: slot6; 111: slot7 |         |

#### LDSW\_SEQ56: Load switch power sequence setting register(Address 07h)

There are 7 time slots for every load switch to turn on/off. The power-up sequence starts from slot1 to slot7, and the power-down sequence is on the contrary. Turning on and off of each load switch can be set at any time slot as defined below.

| Bit | Symbol         | R/W | Description                                                   | Default |

|-----|----------------|-----|---------------------------------------------------------------|---------|

| 7:6 | Reserved       | R   | Reserved                                                      | 00      |

|     |                |     | 000: Controlled by the bit ldsw6_en;                          |         |

| 5:3 | Ldsw6_seq<2:0> | R/W | 00 <mark>1: slot1;                                    </mark> | 000     |

|     |                |     | 100: slot4; 101: slot5; 110: slot6; 111: slot7                |         |

|     |                |     | 000: Controlled by the bit ldsw5_en;                          |         |

| 2:0 | Ldsw5_seq<2:0> | R/W | 001: slot1; 010: slot2; 011: slot3;                           | 000     |

|     | •              |     | 100: slot4; 101: slot5; 110: slot6; 111: slot7                |         |

## SEQ\_CTR: Power sequence setting and status register(Address 08h)

This register enables the power sequence function and reveals the relevant information at present.

| Bit | Symbol         | R/W | Description                                                                                                                                                                                                                                           | Default |

|-----|----------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 7:6 | Seq_speed<1:0> | R/W | Time interval between two adjacent slots: 00: 0.5ms; 01: 1.0ms; 10: 1.5ms; 11: 2.0ms                                                                                                                                                                  | 00      |

| 5:4 | Seq_ctrl<1:0>  | R/W | Power sequence controlling bits: 00: Suspend the current sequence event 01: Execute a power-up sequence 10: Execute a power-down sequence 11: No effect Note: the chip responds once after writing to these two bits, which are always read out "00". | 00      |

| 3   | Seq_on         | R   | Indicator of the power sequence:  0: Indicates that the sequence is not in progress                                                                                                                                                                   | 0       |

|     |              |   | 1: Indicates that the chip is carrying out a power sequence and will return to "0" automatically after the sequence is finished.                                                                                                                                                                                                                                               |     |

|-----|--------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2:0 | Seq_cnt<2:0> | R | Indicates the slot number at present:  000: Power Sequence is not in progress or has finished  001: slot 1 during the power sequence  010: slot 2 during the power sequence  011: slot 3 during the power sequence  100: slot 4 during the power sequence  101: slot 5 during the power sequence  111: slot 6 during the power sequence  111: slot 7 during the power sequence | 000 |

## LDSW\_RCB: Load switch reserve current blocking function selecting register(Address 0Ah)

This register enables the function that blocks the current of load switch when the output voltage is higher than input.

| Bit | Symbol    | R/W | Description                                                             | Default |

|-----|-----------|-----|-------------------------------------------------------------------------|---------|

| 7:6 | Reserved  | R   | Reserved                                                                | 00      |

| 5   | Ldsw6_rcb | R/W | Load switch 6 reverse current blocking function:  0: Disable; 1: Enable | 0       |

| 4   | Ldsw5_rcb | R/W | Load switch 5 reverse current blocking function:  0: Disable; 1: Enable | 0       |

| 3   | Ldsw4_rcb | R/W | Load switch 4 reverse current blocking function:  0: Disable; 1: Enable | 0       |

| 2   | Ldsw3_rcb | R/W | Load switch 3 reverse current blocking function:  0: Disable; 1: Enable | 0       |

| 1   | Ldsw2_rcb | R/W | Load switch 2 reverse current blocking function:  0: Disable; 1: Enable | 0       |

| 0   | Ldsw1_rcb | R/W | Load switch 1 reverse current blocking function:  0: Disable; 1: Enable | 0       |

## • LDSW\_ON: Load switch status indicator register(Address 0Bh)

This register indicates the status (ON or OFF) of each load switch.

| Bit | Symbol   | R/W | Description                                   | Default |

|-----|----------|-----|-----------------------------------------------|---------|

| 7:6 | Reserved | R   | Reserved                                      | 00      |

| 5   | Ldsw6_on | R   | Load switch 6 status indicator: 0: Off; 1: On | 0       |

| 4   | Ldsw5_on | R   | Load switch 5 status indicator: 0: Off; 1: On | 0       |

| 3   | Ldsw4_on | R   | Load switch 4 status indicator:               | 0       |

|   |           |   | 0: Off; 1: On                   |   |  |

|---|-----------|---|---------------------------------|---|--|

| 2 | Ldow2 on  | D | Load switch 3 status indicator: | 0 |  |

| 2 | Ldsw3_on  | R | 0: Off; 1: On                   | 0 |  |

| 1 | I dow? on | В | Load switch 2 status indicator: | 0 |  |

| ' | Ldsw2_on  | R | 0: Off; 1: On                   | 0 |  |

| 0 | l doud on | П | Load switch 1 status indicator: | 0 |  |

| 0 | Ldsw1_on  | R | 0: Off; 1: On                   | 0 |  |

## • RSTN: Reset register(Address 69h)

Writing "0xAE" to this register can reset all registers and disable all load switches when the chip works out of control or other unusual circumstances come out.

| Bit | Symbol   | R/W | Description                                        | Default |

|-----|----------|-----|----------------------------------------------------|---------|

| 7:0 | Reserved | R/W | Read always 00 Write "0xAE" to reset all registers | 00      |

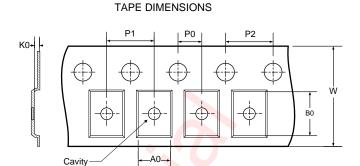

## TAPE AND REEL INFORMATION

# **REEL DIMENSIONS** 0 Ď1

- A0: Dimension designed to accommodate the component width B0: Dimension designed to accommodate the component length K0: Dimension designed to accommodate the component thickness W: Overall width of the carrier tape

- P0: Pitch between successive cavity centers and sprocket hole

- P1: Pitch between successive cavity centers

- P2: Pitch between sprocket hole

- D1: Reel Diameter

- D0: Reel Width

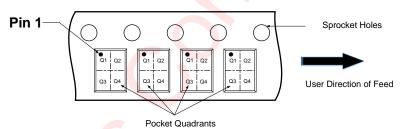

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

Note: The above picture is for reference only. Please refer to the value in the table below for the actual size DIMENSIONS AND PIN1 ORIENTATION

| D1     | D0   | A0   | В0   | K0   | P0   | P1   | P2   | W    | Pin1 Quadrant  |

|--------|------|------|------|------|------|------|------|------|----------------|

| (mm)   | (mm) | (mm) | (mm) | (mm) | (mm) | (mm) | (mm) | (mm) | Fiiii Quaurani |

| 179.00 | 9.00 | 1.63 | 1.63 | 0.67 | 2.00 | 4.00 | 4.00 | 8.00 | Q1             |

All dimensions are nominal

# **PACKAGE DESCRIPTION**

Unit: mm

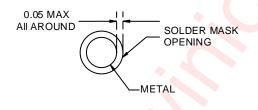

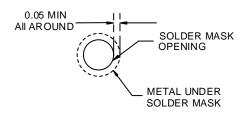

## **LAND PATTERN DATA**

NON-SOLDER MASK DEFINED

SOLDER MASK DEFINED

Unit: mm

## **REVISION HISTORY**

| Version | Date      | Change Record                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|---------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| V1.0    | Dec. 2020 | Datasheet V1.0 Released                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| V1.1    | Oct.2021  | <ol> <li>Modified the definition of Production Tracing Code (Page 2)</li> <li>Changed the upper limit ranges of I<sub>Q_INX</sub>, I<sub>QB_INX</sub> and I<sub>SD_VSYS</sub> in Electrical Characteristics table (Page 6)</li> <li>Added the test condition of I<sub>SD_INX</sub> in Electrical Characteristics table (Page 6)</li> <li>Added the upper limit ranges of V<sub>T_RCB</sub> and V<sub>R_RCB</sub> in Electrical Characteristics table (Page 7)</li> <li>Changed the lower limit of V<sub>IH_IIC</sub> in Electrical Characteristics table (Page 7)</li> <li>Modified the description of Device Address (Page 17)</li> <li>Modified the description of CHIPID (Page 21)</li> <li>Modified the description of LDSW_SEQ (Page 23 and Page 24)</li> <li>Changed Side view (Page 27)</li> </ol> |  |  |  |  |

| V1.2    | Nov.2021  | <ol> <li>Modified the Figure 5(Page 8)</li> <li>Added the SWITCHING CHARACTERISTICS in Electrical Characteristics table (Page 7 and Page 8)</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| V1.3    | Jul.2022  | <ol> <li>Changed the upper limit range of VolsDA from 0.2V to 0.3V (Page 7)</li> <li>Added I2C INTERFACE TIMING in Electrical Characteristics table (Page 9)</li> <li>Updated figure index number from Figure 6 to Figure 48 (Page 9 to Page 20)</li> <li>Added Ron vs. Temperature curves in Figure 20 with VIN=1.7V and 1.8V (Page 12)</li> <li>Added package thickness in ORDERING INFORMATION (Page 4)</li> <li>Added description table of reset register (Page 27)</li> </ol>                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| V1.4    | Feb.2023  | <ol> <li>Added the upper limit range and lower range of R<sub>PD</sub>, I<sub>SD_OUT</sub>, to<sub>N</sub> and t<sub>R</sub> in Electrical Characteristics table (Page 6,7).</li> <li>Added t<sub>DON</sub> and t<sub>DOFF</sub> in Electrical Characteristics table (Page 8,9).</li> <li>Updated figure Timing diagram and added the definition of t<sub>DON</sub> and t<sub>DOFF</sub>.(Page 9).</li> <li>Updated pin1 in figure2 from a solid circle to a hollow circle. (Page 2).</li> <li>Updated the production tracing code in figure2 (Page 2).</li> </ol>                                                                                                                                                                                                                                        |  |  |  |  |

#### **DISCLAIMER**

Information in this document is believed to be accurate and reliable. However, Shanghai AWINIC Technology Co., Ltd (AWINIC Technology) does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

AWINIC Technology reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. Customers shall obtain the latest relevant information before placing orders and shall verify that such information is current and complete. This document supersedes and replaces all information supplied prior to the publication hereof.

AWINIC Technology products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an AWINIC Technology product can reasonably be expected to result in personal injury, death or severe property or environmental damage. AWINIC Technology accepts no liability for inclusion and/or use of AWINIC Technology products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

Applications that are described herein for any of these products are for illustrative purposes only. AWINIC Technology makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

All products are sold subject to the general terms and conditions of commercial sale supplied at the time of order acknowledgement.

Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

Reproduction of AWINIC information in AWINIC data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. AWINIC is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of AWINIC components or services with statements different from or beyond the parameters stated by AWINIC for that component or service voids all express and any implied warranties for the associated AWINIC component or service and is an unfair and deceptive business practice. AWINIC is not responsible or liable for any such statements.