# **Earth Leakage Current Detector**

**SS4125**

### **FEATURES**

- 输入电压: 45 V<sub>AC</sub> to 220 V<sub>AC</sub> (50Hz-60Hz)

- 静态工作电流: 200µA(典型)

- 电磁干扰(EMC)防护能力:

- 无外部滤波电路: ≥10V/m

- 増加外部 π型滤波: ≥18V/m

- 适用于检测 AC 型漏电信号

- 针对延时型的高频漏电流抑制

- 外部固定延迟调整 (不受漏电信号大小影响)

- 外部反延时调整(随不同倍率漏电流变化)

- 高输入灵敏度: V<sub>T</sub>=4.95mV (典型)

- 双输出驱动信号:

- 10V (type) 高压 MOS 驱动(OS\_HV)

- 5V (type)可控硅驱动(OS\_LV)

- 不能跳闸时,同步输出:

- OS\_LV 输出 3 个 30ms: 100ms 占空比脉冲控制信号

- OS\_HV 输出 3 个 30ms: 100ms 占空比脉冲控制信号

- 符合国标 GB16916, GB16917 和 GB14048 标准

- 宽的温度范围(Ta=-40~+125℃)

- 8-lead SOP

### **APPLICATIONS**

- 下进线塑壳式断路器

- 高速漏电保护装置

- 防漏电插座

- 带有漏电保护的小家电

### **GENERAL DESCRIPTION**

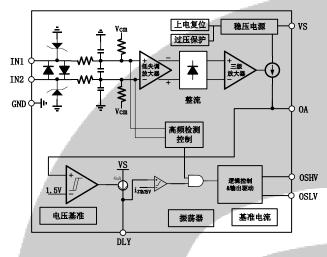

SS4125 是一款针对<mark>下进线</mark>应用的高性能、高可靠延时型高频漏电流抑制型 AC 漏电保护器专用芯片,用于检测火线和零线上的漏电信号。

SS4125 检测到漏电流信号, OA 通过外部电容产生积分信号,当 OA 电压高于 1.5V 阈值电压后,经过 DLY 端口进行延时,当延迟结束后,与高频检测电路的判断结果进行与操作,从而确定漏电流是否满足跳闸要求。当全部满足时,输出驱动高电平信号。当断路器不能正常跳闸时,内部数字处理器将输出占空比为 30ms:100ms 的 3 个脉冲控制信号,从而保证断路器彻底关断,有效地保护触电危险。同时 SS4125 针对不同的应用场景,具有双路输出驱动,可同时驱动高压 MOS 和可控硅,增强了产品的应用场景。

芯片的反延时特性可通过调节 OA 外接电容来实现,固定延迟可通过调节 DLY 端口的外部电容来实现。当芯片检测到高频漏电信号时,高频检测模块识别后,不输出使能信号,即使积分延时满足了阈值指标,在与逻辑下输出驱动信号无法使能。

本芯片可稳定通过 GB14048 中 10V/m 电磁干扰、5KHz/100KHz EFT 群脉冲、雷击浪涌、周波跌落、工频磁场等等可靠性实验。

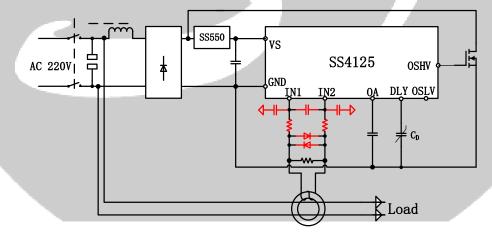

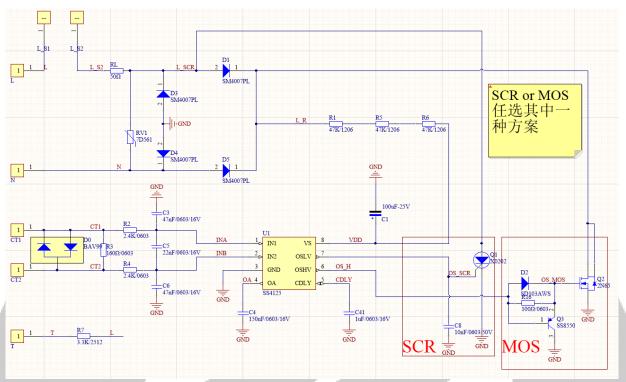

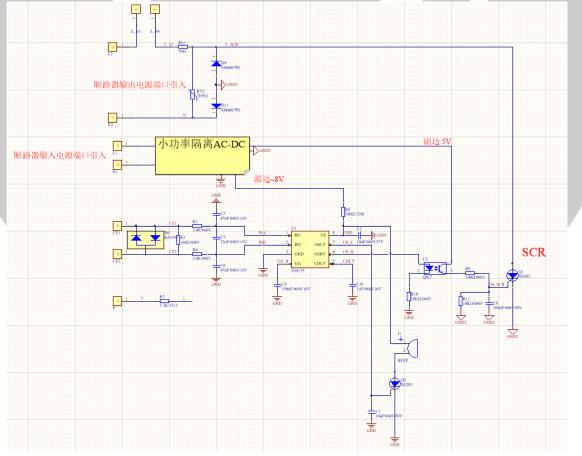

## TYPICAL APPLICATION CIRCUIT

Figure 1. Typical Application Circuit

SS4125 Datasheet

## **SPECIFICATIONS**

$T_A = 25$ °C, unless otherwise noted.

Table 1.

| Parameter      | Symbol                  | Conditions                          | Min                                           | Тур | Max  | Unit |

|----------------|-------------------------|-------------------------------------|-----------------------------------------------|-----|------|------|

| 电源端稳压电压        | V <sub>S1</sub>         | 钳位二极管电压@钳位电流 ls=1mA; 常温             | 12                                            |     |      | V    |

| 电源端稳压电压        | V <sub>S2</sub>         | 钳位二极管电压@钳位电流 ls=1mA; 全温区            | 11                                            |     | 13   |      |

| 供电电流(功耗 1)     | I <sub>S1</sub>         | V <sub>s</sub> =8V; IN1-IN2=0mV; 常温 | 168                                           |     | 252  | μΑ   |

| 供电电流(功耗 2)     | I <sub>S2</sub>         | Vs=8V; IN1-IN2=0mV; 全温区             | 150                                           |     | 295  | μΑ   |

| OS_HV 输出驱动电压   | V <sub>OS_LV</sub>      | V <sub>S</sub> =12V; IN1-IN2=20mV   |                                               | 10  | 12   | V    |

| OS_LV 输出驱动电压   | I <sub>OS_LV</sub>      | V <sub>S</sub> =12V; IN1–IN2=20mV   |                                               | 5   | 6    | ٧    |

| OS_LV 输出驱动电流 1 | los_LV1                 | OS=0.8V; IN1-IN2=20mV; 常温           | 250                                           |     | 850  | μΑ   |

| OS_LV 输出驱动电流 2 | I <sub>OS_LV2</sub>     | OS=0.8V; IN1-IN2=20mV; 全温区          | 130                                           |     | 1500 | μΑ   |

| 漏电动作电压         | V <sub>T</sub>          | IN1-IN2 ; C <sub>OD</sub> =3.3nF    | 4.75 4.95                                     |     | 5.25 | mV   |

| 漏电比较电压         | V <sub>REFSC</sub>      |                                     | 1.5                                           |     |      | V    |

| 延迟注入电流         | I <sub>DLY</sub>        | V <sub>OA</sub> =1.6V; IN1–IN2=20mV | / <sub>OA</sub> =1.6V; IN1–IN2=20mV 2.7 3 3.3 |     | 3.3  | μΑ   |

| 延迟比较电压         | VREFCDLY                |                                     | 1.5                                           |     |      | V    |

| 漏电信号锁存时间       | Ton                     | IN1-IN2=20mV                        | 2=20mV 28                                     |     |      | ms   |

| OS 驱动脉冲个数      |                         | V <sub>S</sub> =8V; IN1–IN2=20mV    | mV 3                                          |     | 3    |      |

| 高频漏电流抑制频率      | <b>f</b> <sub>SUP</sub> | 漏电检测延时时间>120ms                      | 80 100                                        |     | Hz   |      |

<sup>\*</sup>遵守国标 GB16916 标准要求

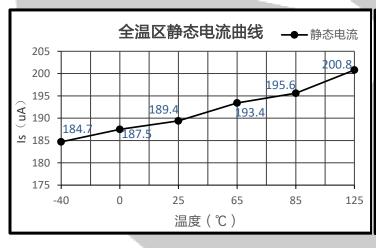

Figure 2. Is Curve In-40 °C~125 °C

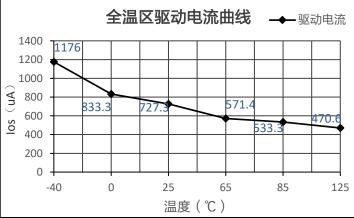

Figure 3. losCurve In-40 ℃~125 ℃

Datasheet SS4125

### **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                            | Rating          |  |

|--------------------------------------|-----------------|--|

| I <sub>SMAX</sub>                    | 8mA             |  |

| VS to GND                            | -0.3V to +24V   |  |

| OSHV to GND                          | -0.3V to +15V   |  |

| OSLV to GND                          | -0.3V to +6V    |  |

| Input Voltage to GND                 | -0.3V to +6V    |  |

| Output Voltage to GND                | -0.3V to +6V    |  |

| Storage Temperature Range            | −65°C to +150°C |  |

| Operating Junction Temperature Range | -40°C to +125°C |  |

| Operating Ambient Temperature Range  | −40°C to +85°C  |  |

| Soldering Conditions                 | JEDEC J-STD-020 |  |

注意,超出上述绝对最大额定值可能会导致器件永久性损坏。 这只是额定应力值,不涉及器件在这些或任何其他条件下 超出本技术规格指标的功能性操作。长期在绝对最大额定 值条件下工作会影响器件的可靠性。

#### THERMAL DATA

绝对最大额定值仅适合单独应用,但不适合组合使用。结温高于限制值时,会损坏 SS4125。监控环境温度并不能保证 T」不会超出额定温度限值。在功耗高、热阻差的应用中,可能必须降低最大环境温度。

在功耗适中、PCB 热阻较低的应用中,只要结温处于额定限值以内,最大环境温度可以超过最大限值。器件的结温  $(T_J)$  取决于环境温度  $(T_A)$  、器件的功耗  $(P_D)$  和封装的结到环境热阻  $(\theta_{JA})$ 。

最高结温(T<sub>J</sub>)由环境温度(T<sub>A</sub>)和功耗(P<sub>D</sub>)通过下式计算:

$$T_J = T_A + (P_D \times \theta_{JA})$$

封装的结到环境热阻 (θ<sub>JA</sub>) 基于使用 4 层板的建模和计算方法,主要取决于应用和板布局。在功耗较高的应用中,需

要特别注意热板设计。 $\theta_{JA}$  的值可能随 PCB 材料、布局和环境条件不同而异。 $\theta_{JA}$  的额定值基于  $4" \times 3"$  的 4 层电路板。有关板结构的详细信息,请参考 JESD 51-7 和 JESD 51-9。

$\Psi_{IB}$  是结到板热特性参数,单位为 °C/W. 封装的  $\Psi_{IB}$  基于使用 4 层板的建模和计算方法。JESD51-12——"报告和使用电子封装热信息指南"中声明,热特性参数和热阻不是一回事。  $\Psi_{IB}$  衡量沿多条热路径流动的器件功率,而  $\theta_{IB}$  只涉及一条路径。因此,  $\Psi_{IB}$  热路径包括来自封装顶部的对流和封装的辐射,这些因素使得  $\Psi_{IB}$  在现实应用中更有用。最高结温  $(T_{IB})$  由板温度  $(T_{IB})$  和功耗  $(P_{D})$ 通过下式计算:

$$T_J = T_B + (P_D \times \Psi_{JB})$$

有关 Ψ<sub>B</sub> 的详细信息,请参考 JESD51-8 和 JESD51-12。

#### THERMAL RESISTANCE

$\theta_{JA}$ 和  $\Psi_{JB}$ 针对最差条件,即器件焊接在电路板上以实现表贴封装。

**Table 3. Thermal Resistance**

| Package Type | θ <sub>JA</sub> | <b>Ө</b> лс | Unit  |

|--------------|-----------------|-------------|-------|

| 8-Lead SOP   | 96              | 55          | °C /W |

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

SS4125 Datasheet

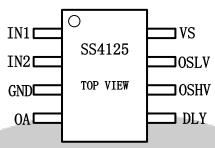

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 4. Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic | Description    |

|---------|----------|----------------|

| 1       | IN1      | 运放输入管脚 1       |

| 2       | IN2      | 运放输入管脚 2       |

| 3       | GND      | 芯片地            |

| 4       | OA       | 滤波、反时线延时可调输出管脚 |

| 5       | DLY      | 固定延迟管脚,外接延迟电容  |

| 6       | OSHV     | 高压 MOS 触发输出管脚  |

| 7       | OSLV     | 可控硅触发输出管脚      |

| 8       | VS       | 电源管脚           |

Datasheet SS4125

### **HEORY OF OPERATION**

SS4125 是一款高性能、高可靠 AC 型漏电保护器专用芯片,用于检测火线和零线上的漏电信号。采用小于 12V 电源供电,最小 SCR 驱动电流 0.2mA,最小高压 MOS 驱动电流 5mA。在无驱动时静态电流典型值低至 200μA,因此SS4125 可使用小功率分流电阻,降低了系统成本。

Figure 5. 芯片内部框图

### 工作原理:

SS4125 检测到漏电流信号, OA 通过外部电容产生积分信号,当 OA 电压高于 1.5V 阈值电压后,经过 DLY 端口进行延时,当延迟结束后,与高频检测电路的判断结果进行与操作,从而确定漏电流是否满足跳闸要求。当全部满足时,输出驱动高电平信号。

芯片的反延时特性可通过调节 OA 外接电容来实现,固定延迟可通过调节 DLY 端口的外部电容来实现。当芯片检测到高频漏电信号时,高频检测模块识别后,不输出使能信号,即使积分延时满足了阈值指标,在与逻辑下输出驱动信号无法使能。

OA 积分延迟环路必须满足 120ms 以上的延迟最低要求, 否则高频检测环路会出现误判,造成误动作。

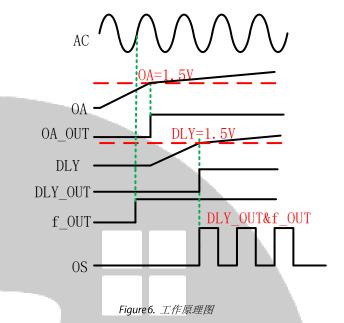

图 6 中,AC 是输入漏电流;OA\_OUT 是 OA 比较器的输出;f\_OUT 为高频滤波器判断输出(高电平表示输入频率正常,低电平表示超出设定频率), DLY\_OUT 为延迟比较器输出。

DLY 工作原理

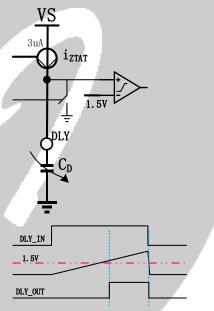

Figure 7.RC Time set circuit diagram

DLY 是输出固定延时控制端口。通过连接外部的电容,并调节电容大小,可以产生不同的输出控制信号延迟。

$$T_D = \frac{C_D \times V_{REF}}{I_D}$$

当 VREF = 1.5V, CD = 3.42uF(1 $\mu$ F+2.2 $\mu$ F+0.22 $\mu$ F), ID = 3 $\mu$ A 时,

SS4125 Datasheet

$TD \approx 1.71s$

当 VREF = 1.5V, CD = 1.83uF(1.5 $\mu$ F+0.33 $\mu$ F), ID = 3 $\mu$ A 时,

$TD\approx 0.915s$

当 VREF = 1.5V, CD =  $0.8 u F(0.47 \mu F + 0.33 \mu F)$ , ID =  $3 \mu A$  时,

TD  $\approx 0.4$

### 反延时工作原理

OA 端口外接电容,可实现在不同倍率下漏电流的延时 反比例曲线。SS4125 的电流放大倍数在 300 倍左右,当不 同倍率的漏电流施加后,在 OA 端口产生不同幅度的输出 驱动电流,因电容与电流满足电荷公式满足:

$$i \times t = U \times C_{OA}$$

$$i = \frac{I_{RC} \times R_S}{CT \times 1K}$$

其中 IRC 为输入漏电流,CT 为互感器匝数,RS 为互感器采样电阻, U 为比较电压 1.5V, 从而得出时间 t 与输入漏电流和电容之间的公式:

$$t = \frac{CT \times 1K \times 1.5 \times C_{OA}}{I_{RC} \times R_S}$$

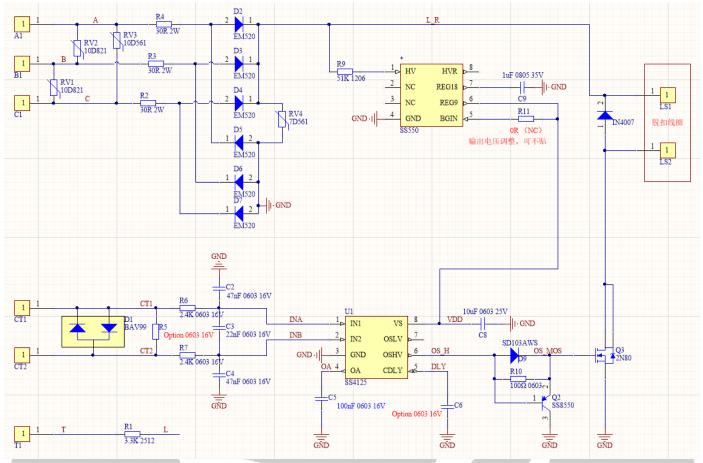

# 应用电路:

Figure 8.SS4125 high performance application

Figure 9.SS4125 high performance application with Beep Warning Rev. **A** | Page 7 of 14

Figure 10.SS4125 三相下进线应用

Table 5. 三相下进线应用参数选择

| 延时电容  |       |  |       |       |           |  |

|-------|-------|--|-------|-------|-----------|--|

|       | 0.15  |  | 0.25  | 0.5\$ | 15        |  |

| Сод   | 100nF |  | 100nF | 100nF | 100nF     |  |

| CDLY  | 56nF  |  | 220nF | 680nF | 1uF+330nF |  |

| 采样电阻  |       |  |       |       |           |  |

| 100   |       |  | 62R   |       |           |  |

| 300mA |       |  | 21R   |       |           |  |

| 500mA |       |  |       | 12R   |           |  |

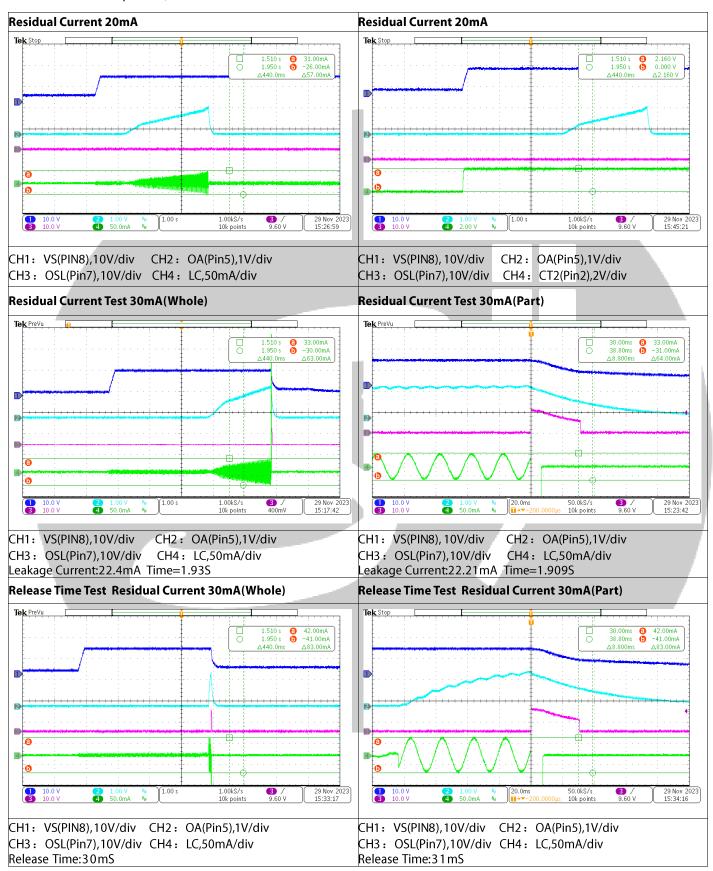

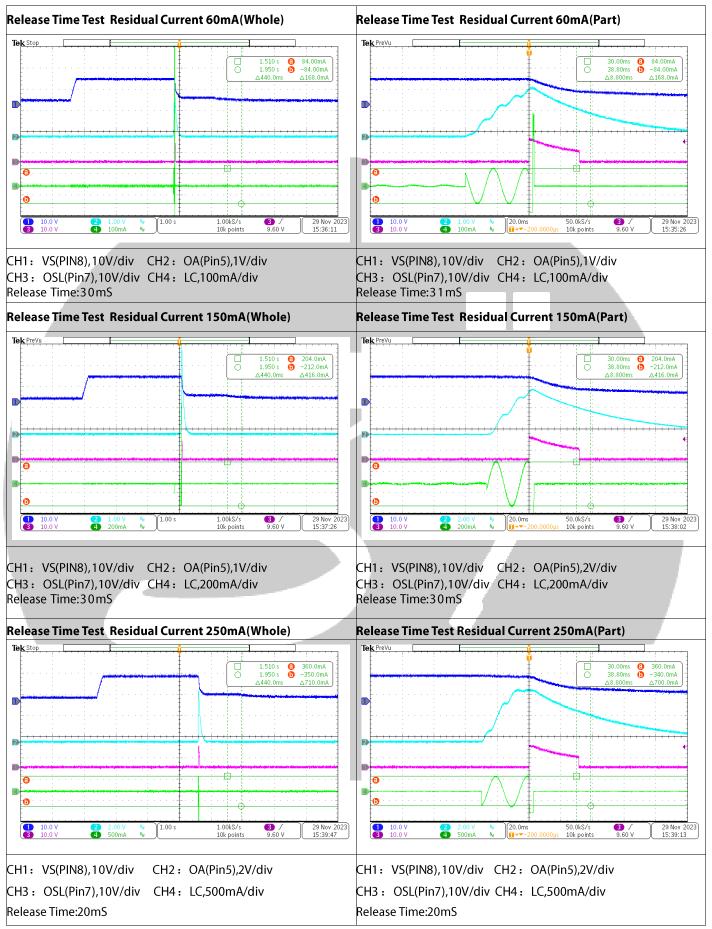

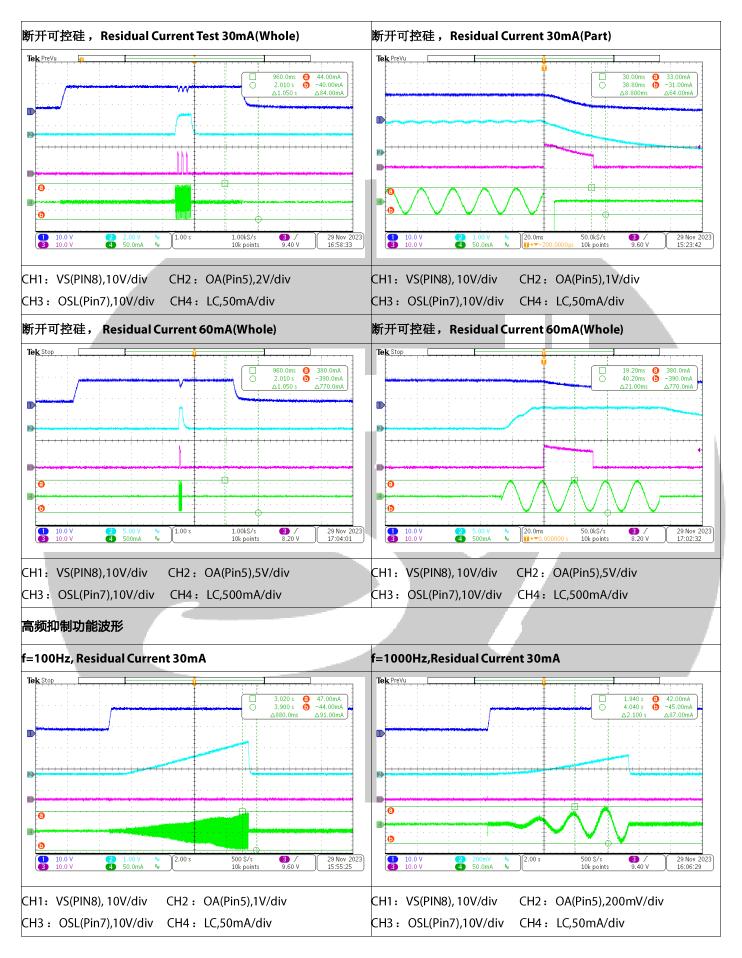

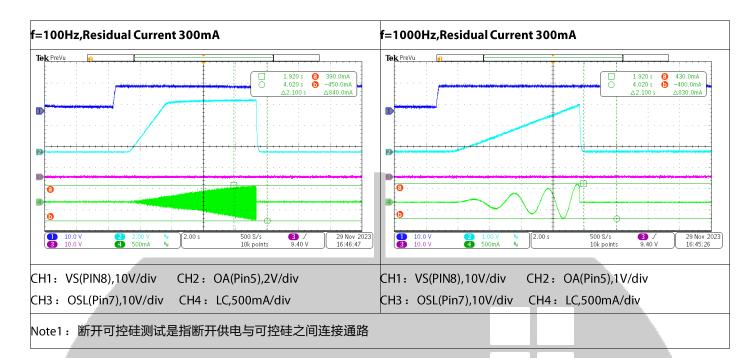

### TYPICAL PERFORMANCE CHARACTERISTICS

Unless otherwise specified, TA = 25℃

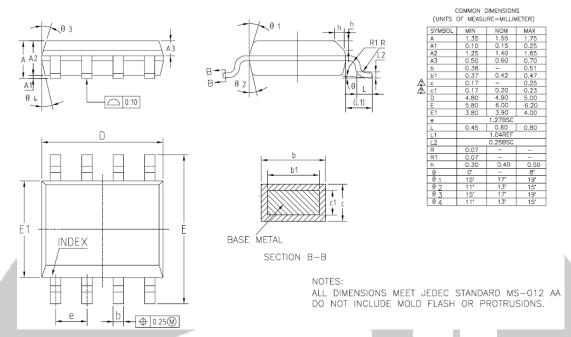

### **OUTLINE DIMENSIONS**

Figure 11.8-Lead Small Outline Package [SOP]

Dimensions show in millimeters

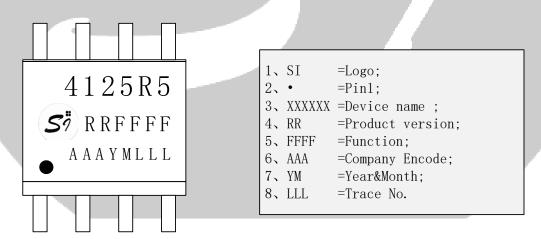

### **ORDERING GUIDE**

| 型号     | 封装形式 | 温度范围             | MK code                      | 包装方式   | 卷盘尺寸   |

|--------|------|------------------|------------------------------|--------|--------|

| SS4125 | SOP8 | -40°C to +125 °C | 4125R5<br>G3PPDA<br>AAAYMLLL | 3000/盘 | 13 寸卷盘 |

注:本公司保留不预先通知而修改此文件的权利

©2023 Sinasilicon, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D00000-0-1/15(A)

www.sinasilicon.com

# 版本更新

| 版本号 | 发布日期    | 页数 | 章节或图表                           | 更改说明    |

|-----|---------|----|---------------------------------|---------|

| 1.0 | 2023.12 | 13 |                                 | 首次发布    |

| 1.1 | 2024.2  | 14 | Figure 6、Table 5                | 增加图表    |

| 1.2 | 2024.3  | 14 | Figure 8、Figure 9、<br>Figure 10 | 更新应用图参数 |