## 1. **DESCRIPTION**

The XL65HVD08DR/XL65HVD08P combines a 3-state differential line driver and differential line receiver designed for balanced data transmission and interoperation with ANSI TIA/EIA-485-A and ISO-8482 Estandard compliant devices.

The wide supply voltage range and low quiescent current requirements allow the XL65HVD08DR/XL65HVD08P to operate from a 5-V power bus in the cable with as much as a 2V line voltage drop. Busing power in the cable can alleviate the need for isolated power to be generated at each connection of a ground-isolated bus.

The driver differential outputs and receiver differential inputs connect internally to form a differential input/output (I/O) bus port that is designed to offer minimum loading to the bus whenever the driver is disabled or not powered. The drivers and receivers have active-high and active-low enables respectively, which can be externally connected together to function as a direction control.

## 2. FEATURES

- Operates With a 3-V to 5.5-V Supply

- Consumes Less Than 90-mW Quiescent Power

- Open-Circuit, Short-Circuit, and Idle-Bus Failsafe Receiver

- 1/8<sup>th</sup> Unit-Load (up to 256 nodes on the bus)

- Bus-Pin ESD Protection Exceeds 16-kV HBM

- Driver Output Voltage Slew-Rate Limited for Optimum Signal Quality at 10 Mbps

- Electrically Compatible With ANSI TIA/EIA-485 Standard

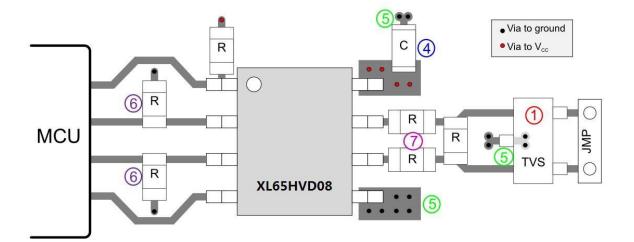

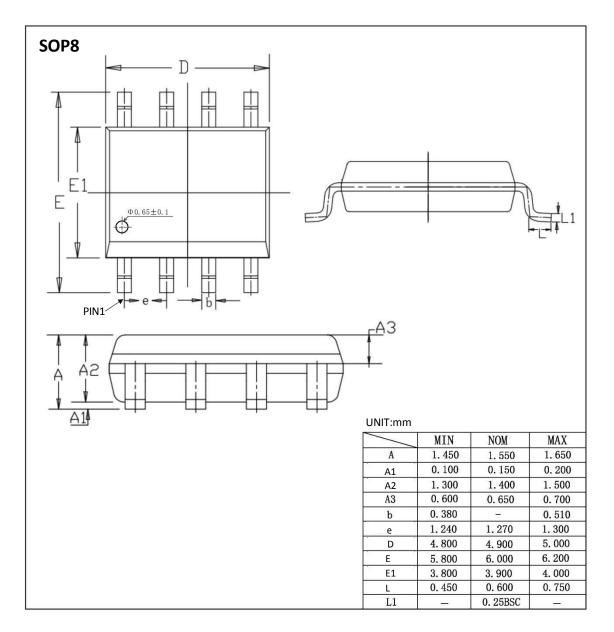

- Package option: XL65HVD08DR (SOP8), XL65HVD08P (DIP8)

# 3. APPLICATIONS

- Data Transmission With Remote Stations Powered From the Host

- Isolated Multipoint Data Buses

- Industrial Process Control Networks

- Point-of-Sale Networks

- Electric Utility Metering

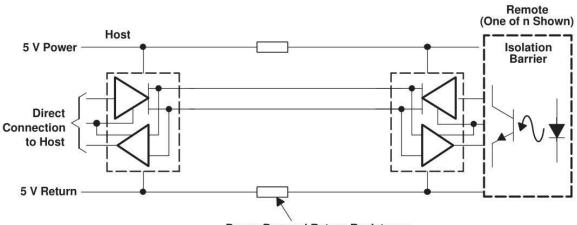

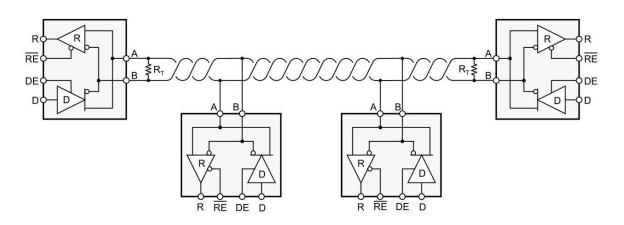

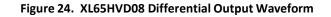

# 4. TYPICAL APPLICATION SCHEMATIC

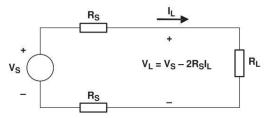

Power Bus and Return Resistance

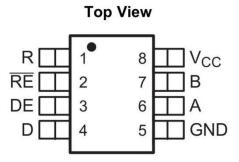

# 5. PIN CONFIGURATIONS AND FUNCTIONS

| PIN             |     |                     |                                                       |  |

|-----------------|-----|---------------------|-------------------------------------------------------|--|

| NAME            | NO. | ТҮРЕ                | DESCRIPTION                                           |  |

| А               | 6   | Bus input / output  | Driver output and receiver input (complementary to B) |  |

| В               | 7   | Bus input / output  | Driver output and receiver input (complementary to A) |  |

| D               | 4   | Digital input       | Driver data input                                     |  |

| DE              | 3   | Digital input       | Driver enable high                                    |  |

| GND             | 5   | Reference potential | Local device ground                                   |  |

| R               | 1   | Digital output      | Receive data output                                   |  |

| RE              | 2   | Digital input       | Receiver enable low                                   |  |

| V <sub>CC</sub> | 8   | Supply              | 3-V to 5.5-V supply                                   |  |

# 6. SPECIFICATIONS

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range unless otherwise noted<sup>(1) (2)</sup>

|                                                               | MIN  | MAX                   | UNIT |

|---------------------------------------------------------------|------|-----------------------|------|

| Supply voltage, V <sub>cc</sub>                               | -0.3 | 6                     | V    |

| Voltage at A or B                                             | -9   | 14                    | V    |

| Input voltage at D, DE, R or RE                               | -0.5 | V <sub>cc</sub> + 0.5 | V    |

| Voltage input, transient pulse, A and B, through 100 $\Omega$ | -25  | 25                    | V    |

| Receiver ouput current, Io                                    | -11  | 11                    | mA   |

| Maximum Junction Temperature, T <sub>J</sub>                  |      | 150                   | °C   |

| Storage Temperature, T <sub>STG</sub>                         | -65  | 150                   | °C   |

[1] Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

[2] All voltage values, except differential I/O bus voltages, are with respect to network ground terminal.

## 6.2 ESD Ratings

|                    |               |                                                        |                                                                                |       | UNIT |

|--------------------|---------------|--------------------------------------------------------|--------------------------------------------------------------------------------|-------|------|

|                    | Electrostatic | Human body model (HBM), per ANSI/ESDA/JEDEC JS- 001(1) | A, B, and GND                                                                  | 16000 |      |

| V <sub>(ESD)</sub> | discharge     |                                                        | All pins                                                                       | 4000  | V    |

| uischarge          |               | Charged-device model (CDM), per JEDEC specification JE | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> |       |      |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommend Operating Conditions

|                                                   |                                                          | MIN  | NOM MAX | UNIT |  |

|---------------------------------------------------|----------------------------------------------------------|------|---------|------|--|

| S                                                 | Supply voltage, V <sub>cc</sub>                          |      | 5.5     | V    |  |

| Input voltage at any bus ter                      | minal (separately or common mode), V $_{\rm I}$ $^{(1)}$ | -7   | 12      | V    |  |

| High-level input voltage, VIH                     |                                                          | 2.25 | Vcc     |      |  |

| Low-level input voltage, VIL                      | Driver, driver enable, and receiver enable<br>inputs     | 0    | 0.8     | V    |  |

| Differe                                           | Differential input voltage, V <sub>ID</sub>              |      | 12      |      |  |

|                                                   | Driver                                                   |      | -60     |      |  |

| High-level output current, I <sub>OH</sub>        | Receiver                                                 |      | -8      | mA   |  |

|                                                   | Driver                                                   |      | 60      |      |  |

| Low-level output current, I <sub>OL</sub>         | Receiver                                                 |      | 8       | mA   |  |

| Operating free-air<br>temperature, T <sub>A</sub> | XL65HVD08                                                | -40  | 85      | °C   |  |

(1) The algebraic convention, in which the least positive (most negative) limit is designated as minimum is used in this data sheet.

## 6.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup> |                                              | 65HVD08  |      |

|-------------------------------|----------------------------------------------|----------|------|

|                               |                                              | D (SOIC) | UNIT |

|                               |                                              | 8 PINS   |      |

| R <sub>θJA</sub>              | Junction-to-ambient thermal resistance       | 175.4    | °C/W |

| R <sub>0JC(top)</sub>         | Junction-to-case (top) thermal resistance    | 53.6     | °C/W |

| R <sub>θJB</sub>              | Junction-to-board thermal resistance         | 45.1     | °C/W |

| ΨJT                           | Junction-to-top characterization parameter   | 10.1     | °C/W |

| $\psi_{JB}$                   | Junction-to-board characterization parameter | 44.4     | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 6.5 Electrical Characteristics

over recommended operating conditions unless otherwise noted

| PAR/                | AMETER                                                                                            | TEST CONDITIONS                                                               | MIN  | ТҮР  | MAX             | UNI<br>T |

|---------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------|------|-----------------|----------|

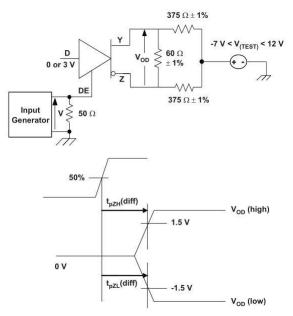

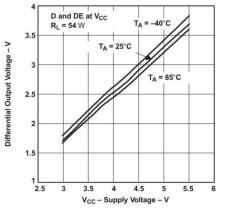

| V <sub>od</sub>     | Driver differential output voltage<br>magnitude                                                   | R <sub>L</sub> = 60 Ω, 375 Ω on each output to<br>- 7 V to 12 V, See Figure 7 | 1.5  |      | V <sub>cc</sub> | v        |

| Δ V <sub>od</sub>   | Change in magnitude of driver<br>differential output voltage                                      | R <sub>L</sub> = 54 Ω                                                         | -0.2 |      | 0.2             | v        |

| V <sub>OC(PP)</sub> | Peak-to-peak driver common-mode<br>output voltage                                                 | Center of two 27-Ω load resistors, See Figure 8                               |      | 0.5  |                 | v        |

| V <sub>IT+</sub>    | Positive-going receiver differential<br>input voltage threshold                                   |                                                                               |      |      | -10             | mV       |

| V <sub>IT-</sub>    | Negative-going receiver differential<br>input voltage threshold                                   |                                                                               |      | -200 |                 | mV       |

| V <sub>hys</sub>    | Receiver differential input voltage<br>threshold hysteresis(V <sub>IT+</sub> - V <sub>IT-</sub> ) |                                                                               |      | 35   |                 | mV       |

| V <sub>OH</sub>     | Receiver high-level output voltage                                                                | I <sub>он</sub> = -8 mA                                                       |      | 2.4  |                 | V        |

| V <sub>OL</sub>     | Receiver low-level output voltage                                                                 | I <sub>OL</sub> = 8 mA                                                        |      |      | 0.4             | V        |

| Цін                 | Driver input, driver enable, and<br>receiver enable high-level input<br>current                   |                                                                               | -100 |      | 100             | μΑ       |

| I <sub>IL</sub>     | Driver input, driver enable, and<br>receiver enable low-level input<br>current                    |                                                                               | -100 |      | 100             | μΑ       |

| I <sub>OS</sub>     | Driver short-circuit output current                                                               | 7 V < V <sub>0</sub> < 12 V                                                   | -265 |      | 265             | mA       |

## **Electrical Characteristics (continued)**

over recommended operating conditions unless otherwise noted

| PARAMETER |                                        | TEST CONDITIONS                               | MIN  | ТҮР | MAX | UNIT |

|-----------|----------------------------------------|-----------------------------------------------|------|-----|-----|------|

|           |                                        | V <sub>I</sub> = 12 V                         |      |     | 130 |      |

|           |                                        | V1 = -7 V                                     | -100 |     |     |      |

| կ         | Bus input current<br>(disabled driver) | $V_{I} = 12 V, V_{CC} = 0 V$                  |      |     | 130 | μA   |

|           |                                        | $V_1 = -7 V. V_{CC} = 0 V$                    | -100 |     |     |      |

|           |                                        | Receiver enabled, driver<br>disabled, no load |      |     | 10  |      |

| lcc       | Supply current                         | Driver enabled, receiver<br>disabled, no load |      |     | 16  | mA   |

|           |                                        | Both disabled                                 |      |     | 5   | μA   |

|           |                                        | Both enabled, no load                         |      |     | 16  | mA   |

## 6.6 Driver Switching Characteristics

over recommended operating conditions unless otherwise noted

|                    | PARAMETER                                                                    | TEST CONDITIONS                                  | MIN | ТҮР | MAX | UNIT |

|--------------------|------------------------------------------------------------------------------|--------------------------------------------------|-----|-----|-----|------|

| t <sub>PHL</sub>   | Driver high-to-low propagation delay time                                    |                                                  | 18  |     | 40  |      |

| t <sub>PLH</sub>   | Driver low-to-high propagation delay time                                    |                                                  | 18  |     | 40  |      |

| tr                 | Driver 10%-to-90% differential output rise time                              | $R_L = 54 \Omega$ , $C_L = 50 pF$ , See Figure 9 | 10  |     | 55  | ns   |

| t <sub>f</sub>     | Driver 90%-to-10% differential output fall<br>time                           |                                                  | 10  |     | 55  |      |

| t <sub>SK(P)</sub> | Driver differential output pulse skew, $ t_{\text{PHL}}$ – $t_{\text{PLH}} $ |                                                  |     |     | 2.5 |      |

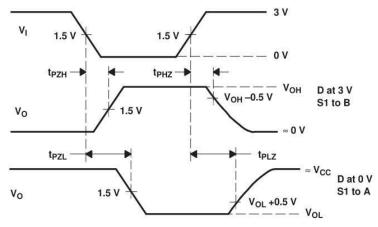

| t <sub>en</sub>    | Driver enable time                                                           | Receiver enabled, See Figures 4<br>and 5         |     |     | 55  | ns   |

|                    |                                                                              | Receiver disabled, See Figures 4<br>and 5        |     |     | 6   | μs   |

| t <sub>dis</sub>   | Driver disable time                                                          | Receiver enabled, See Figures 4<br>and 5         |     |     | 90  | ns   |

## 6.7 Receiver Switching Characteristics

over recommended operating conditions unless otherwise noted

|                                                                  | PAR              | AMETER                                                                    | TEST CONDITIONS                  | MIN | ТҮР | MAX | UNIT |

|------------------------------------------------------------------|------------------|---------------------------------------------------------------------------|----------------------------------|-----|-----|-----|------|

| <b>t</b> PHL                                                     | Receive          | er high-to-low propagation delay time                                     |                                  |     |     | 70  |      |

| t <sub>PLH</sub>                                                 | Receive          | er low-to-high propagation delay time                                     | p-high propagation delay time 7( |     | 70  |     |      |

| t <sub>r</sub> Receiver 10%-to-90% differential output rise time |                  | $C_L = 15 \text{ pF}$ , See Figure 12                                     | 5                                |     | 5   | ns  |      |

| t <sub>f</sub>                                                   | Receiver         | 90%-to-10% differential output fall time                                  |                                  |     |     | 5   |      |

| t <sub>sk(P)</sub>                                               | Receiver         | r differential output pulse skew,  t <sub>PHL</sub> -<br>t <sub>PLH</sub> |                                  |     |     | 4.5 |      |

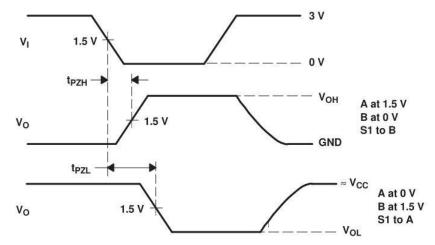

|                                                                  |                  | Dessiver enable time                                                      | Driver enabled, See Figure 13    |     |     | 15  | ns   |

|                                                                  | t <sub>en</sub>  | Receiver enable time                                                      | Driver disabled, See Figure 14   |     |     | 6   | μs   |

|                                                                  | t <sub>dis</sub> | Receiver disable time                                                     | Driver enabled, See Figure 13    |     |     | 20  | ns   |

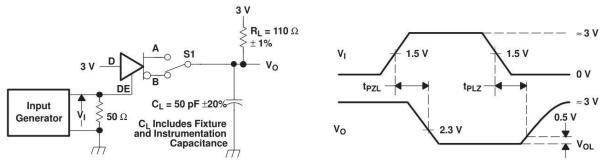

Figure 1. Driver Enable Time From DE to  $\mathrm{V}_{\mathrm{OD}}$

The time  $t_{pZL}(x)$  is the measure from DE to  $V_{OD}(x)$ .  $V_{OD}$  is valid when it is greater than 1.5 V.

## 6.8 Typical Characteristics

Figure 2. Differential Output Voltage vs Supply Voltage

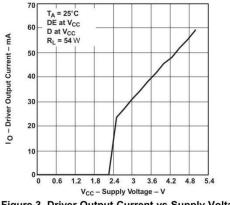

Figure 3. Driver Output Current vs Supply Voltage

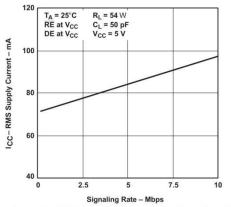

Figure 4. RMS Supply Current vs Signaling Rate

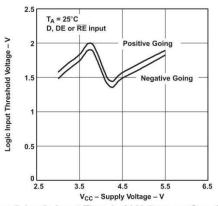

Figure 5. Logic Input Threshold Voltage vs Supply Voltage

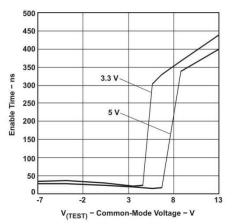

Figure 6. Enable Time vs Common-Mode Voltage (See Figure 1)

## 7. PARAMETER MEASUREMENT INFORMATION

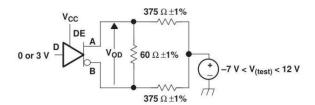

Figure 7. Driver  $V_{OD}$  With Common-Mode Loading Test Circuit

Input: PRR = 500 kHz, 50% Duty Cycle, $t_r$ <6ns,  $t_f$ <6ns,  $Z_0$  = 50  $\Omega$

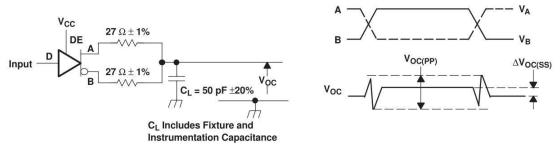

#### Figure 8. Test Circuit and Definitions for the Driver Common-Mode Output Voltage

Generator: PRR = 500 kHz, 50% Duty Cycle, t<sub>r</sub> <6 ns, t<sub>f</sub> <6 ns, Z<sub>o</sub> = 50  $\Omega$

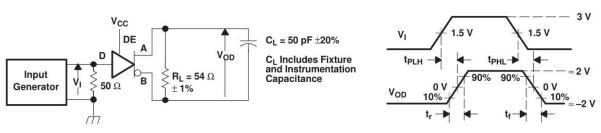

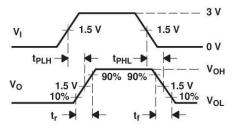

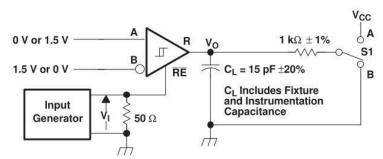

Figure 9. Driver Switching Test Circuit and Voltage Waveforms

Generator: PRR = 500 kHz, 50% Duty Cycle,  $t_r$  <6 ns,  $t_f$  <6 ns,  $Z_o$  = 50  $\Omega$

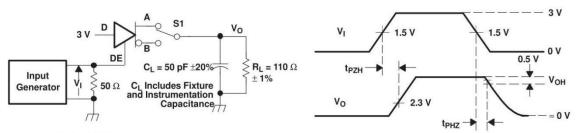

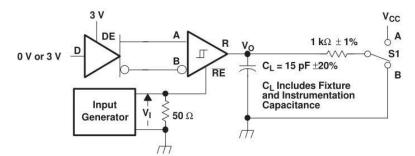

Figure 10. Driver High-Level Enable and Disable Time Test Circuit and Voltage Waveforms

Generator: PRR = 500 kHz, 50% Duty Cycle,  $t_r$  <6 ns,  $t_f$  <6 ns,  $Z_o$  = 50  $\Omega$

Generator: PRR = 500 kHz, 50% Duty Cycle, t<sub>r</sub> <6 ns, t<sub>f</sub> <6 ns, Z<sub>o</sub> = 50  $\Omega$

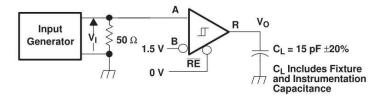

Figure 12. Receiver Switching Test Circuit and Voltage Waveforms

Generator: PRR = 500 kHz, 50% Duty Cycle,  $t_r$  <6 ns,  $t_f$  <6 ns,  $Z_o$  = 50  $\Omega$

Figure 13. Receiver Enable and Disable Time Test Circuit and Voltage Waveforms With Drivers Enabled

Generator: PRR = 100 kHz, 50% Duty Cycle,  $t_r < 6$  ns,  $t_f < 6$  ns,  $Z_o = 50 \Omega$

Figure 14. Receiver Enable Time From Standby (Driver Disabled)

## 8. DETAILED DESCRIPTION

#### 8.1 Overview

The XL65HVD08 is a 3-V to 5.5-V, half-duplex, RS-485 transceiver suitable for data transmission up to 10 Mbps.

This device has an active-high driver enable and active-low receiver enable. A standby current of less than 5  $\mu$ A can be achieved by disabling both driver and receiver.

Device operation is specified over a wide temperature range from -40°C to +85°C.

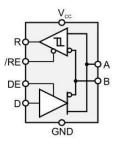

#### 8.2 Functional Block Diagram

Figure 15. Logic Diagram (Positive)

#### 8.3 Feature Description

Internal ESD protection circuits protect the transceiver bus terminals against  $\pm 16$  kV Human Body Model (HBM) electrostatic discharges and all other pins up to  $\pm 4$  kV.

The XL65HVD08 provides internal biasing of the receiver input thresholds for open-circuit, busidle, or short- circuit failsafe conditions, and a typical receiver hysteresis of 35 mV.

## 8.4 Device Functional Modes

| INPUT | ENABLE | OUTPUTS |   |  |

|-------|--------|---------|---|--|

| D     | DE     | А       | В |  |

| н     | н      | н       | L |  |

| L     | н      | L       | н |  |

| Х     | L      | Z       | Z |  |

| Open  | н      | н       | L |  |

| Table 1. Function Table: Dr | river |

|-----------------------------|-------|

|-----------------------------|-------|

Table 2. Function Table: Receiver

| DIFFERENTIAL INPUTS                | ENABLE <sup>(1)</sup> | OUTPUT <sup>(1)</sup> |

|------------------------------------|-----------------------|-----------------------|

| $V_{ID} = V_A - V_B$               | RE                    | R                     |

| V <sub>ID</sub> ≤ -0.2 V           | L                     | L                     |

| -0.2 V < V <sub>ID</sub> < -0.01 V | L                     | ?                     |

| -0.01 V ≤ V <sub>ID</sub>          | L                     | н                     |

| X                                  | Н                     | Z                     |

| Open Circuit                       | L                     | Н                     |

| Short Circuit                      | L                     | Н                     |

(1) H = high level; L = low level; Z = high impedance; X = irrelevant;

? = indeterminate

www.xinluda.com

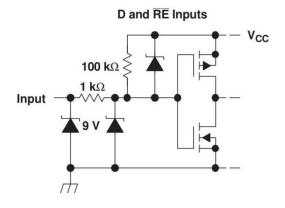

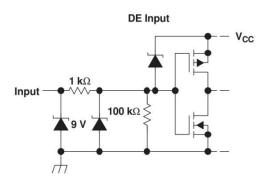

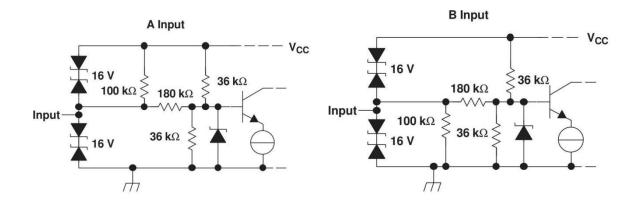

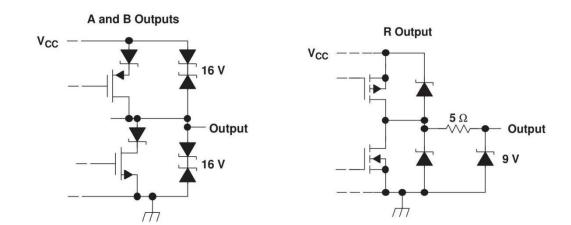

Figure 16. Equivalent Input and Output Schematic Diagrams

## 9. APPLICATION AND IMPLEMENTATION

#### NOTE

Information in the following applications sections is not part of the Xinluda component specification, and Xinluda does not warrant its accuracy or completeness. Xinluda's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 9.1. Application Information

As electrical loads are physically distanced from their power source, the effects of supply and return line impedance and the resultant voltage drop must be accounted. If the supply regulation at the load cannot be maintained to the circuit requirements, it forces the use of remote sensing, additional regulation at the load, bigger or shorter cables, or a combination of these. The XL65HVD08 eases this problem by relaxing the supply requirements to allow for more variation in the supply voltage over typical RS-485 transceivers.

#### 9.1.1 Supply Source Impedance

In the steady state, the voltage drop from the source to the load is simply the wire resistance times the load current as modeled in Figure 17.

Figure 17. Steady-State Circuit Model

For example, if you were to provide 5-V  $\pm$ 5% supply power to a remote circuit with a maximum load requirement of 0.1 A (one XL65HVD08), the voltage at the load would fall below the 4.5-V minimum of most 5-V circuits with as little as 5.8 m of 28-GA conductors. Table 3 summarizes wire resistance and the length for 4.5 V and 3 V at the load with 0.1 A of load current. The maximum lengths would scale linearly for higher or lower load currents.

| Voltages at 0.1 A Load |            |                       |                    |  |  |

|------------------------|------------|-----------------------|--------------------|--|--|

| WIRE SIZE              | RESISTANCE | 4.5-V LENGTH AT 0.1 A | 3-VLENGTH AT 0.1 A |  |  |

| 28 Gauge               | 0.213 Ω/m  | 5.8 m                 | 41.1 m             |  |  |

| 24 Gauge               | 0.079 Ω/m  | 15.8 m                | 110.7 m            |  |  |

| 22 Gauge               | 0.054 Ω/m  | 23.1 m                | 162.0 m            |  |  |

| 20 Gauge               | 0.034 Ω/m  | 36.8 m                | 257.3 m            |  |  |

| 18 Gauge               | 0.021 Ω/m  | 59.5 m                | 416.7 m            |  |  |

# Table 3. Maximum Cable Lengths for Minimum LoadVoltages at 0.1 A Load

Under dynamic load requirements, the distributed inductance and capacitance of the power lines may not be ignored and decoupling capacitance at the load is required. The amount depends upon the magnitude and frequency of the load current change but, if only powering the XL65HVD08, a 0.1  $\mu$ F ceramic capacitor is usually sufficient.

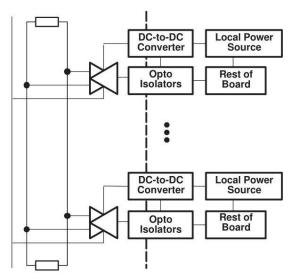

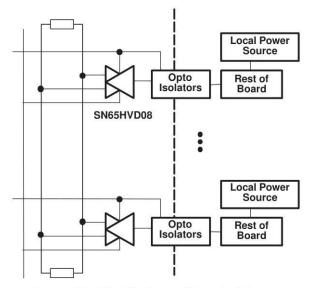

#### 9.1.2 Opto-Isolated Data Buses

Long RS-485 circuits can create large ground loops and pick up common-mode noise voltages in excess of the range tolerated by standard RS-485 circuits. A common remedy is to provide galvanic isolation of the data circuit from earth or local grounds.

## **Application Information (continued)**

Transformers, capacitors, or phototransistors most often provide isolation of the bus and the local node. Transformers and capacitors require changing signals to transfer the information over the isolation barrier and phototransistors (opto-isolators) can pass steady-state signals. Each of these methods incurs additional costs and complexity, the former in clock encoding and decoding of the data stream and the latter in requiring an isolated power supply.

Quite often, the cost of isolated power is repeated at each node connected to the bus as shown in Figure 18. The possibly lower-cost solution is to generate this supply once within the system and then distribute it along with the data line(s) as shown in Figure 19.

Figure 18. Isolated Power at Each Node

Figure 19. Distribution of Isolated Power

The features of the XL65HVD08 are particularly good for the application of Figure 19. Due to added supply source impedance, the low quiescent current requirements and wide supply voltage tolerance allow for the poorer load regulation.

## Application Information (continued)

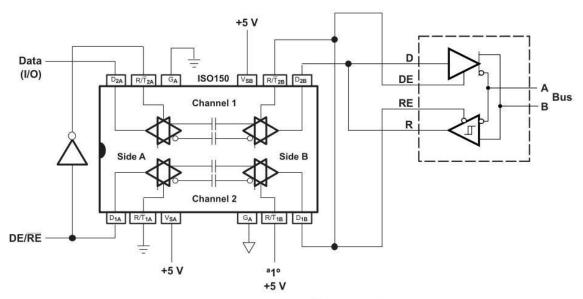

#### 9.1.2 Opto Alternative

The ISO150 is a two-channel, galvanically isolated data coupler capable of data rates of 80 Mbps. Each channel can be individually programmed to transmit data in either direction.

Data is transmitted across the isolation barrier by coupling complementary pulses through high-voltage 0.4-pF capacitors. Receiver circuitry restores the pulses to standard logic levels. Differential signal transmission rejects isolation-mode voltage transients up to 1.6 kV/ms.

ISO150 avoids the problems commonly associated with opto-couplers. Optically-isolated couplers require high current pulses and allowance must be made for LED aging. The ISO150's Bi-CMOS circuitry operates at 25 mW per channel with supply voltage range matching that of the XL65HVD08 of 3 V to 5.5 V.

Figure 20 shows a typical circuit.

Figure 20. Isolated RS-485 Interface

# 9.2. Typical Application

An RS-485 bus consists of multiple transceivers connecting in parallel to a bus cable. To eliminate line reflections, each cable end is terminated with a termination resistor,  $R_T$ , whose value matches the characteristic impedance,  $Z_0$ , of the cable. This method, known as parallel termination, allows for higher data rates over longer cable length.

Figure 21. Typical Application Diagram

#### 9.2.1 Design Requirements

RS-485 is a robust electrical standard suitable for long-distance networking that may be used in a wide range of applications with varying requirements, such as distance, data rate, and number of nodes.

#### 9.2.1.1 Data Rate and Bus Length

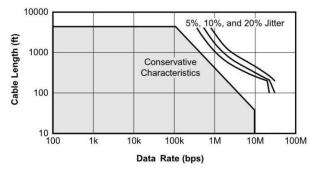

There is an inverse relationship between data rate and bus length, meaning the higher the data rate, the shorter the cable length; and conversely, the lower the data rate, the longer the cable may be without introducing data errors. While most RS-485 systems use data rates between 10 kbps and 100 kbps, some applications require data rates up to 250 kbps at distances of 4000 feet and longer. Longer distances are possible by allowing for small signal jitter of up to 5 or 10%.

Figure 22. Cable Length vs Data Rate Characteristic

## **Typical Application (continued)**

#### 9.2.1.2 Stub Length

When connecting a node to the bus, the distance between the transceiver inputs and the cable trunk, known as the stub, should be as short as possible. Stubs present a non-terminated piece of bus line which can introduce reflections as the length of the stub increases. As a general guideline, the electrical length, or round-trip delay, of a stub should be less than one-tenth of the rise time of the driver, thus giving a maximum physical stub length as shown in Equation 1.

$L_{stub} \le 0.1 \times t_r \times v \times c$

Where:

- t<sub>r</sub> is the 10/90 rise time of the driver

- c is the speed of light  $(3 \times 10^8 \text{ m/s})$

- v is the signal velocity of the cable or trace as a factor of c

Per Equation 1, the maximum recommended stub length for the minimum driver output rise time of the X L 6 5 H V D 0 8 for a signal velocity of 78% is 0.23 meters (0.75 feet).

#### 9.2.1.3 Bus Loading

The RS-485 standard specifies that a compliant driver must be able to driver 32 unit loads (UL), where 1 unit load represents a load impedance of approximately 12 k $\Omega$ . Because the X L 6 5 H V D 0 8 are each 1/8 UL transceivers.

it is possible to connect up to 256 receivers to the bus.9.2.1.4 Receiver Failsafe

The differential receivers of the XL65HVD08 family are "failsafe" to invalid bus states caused by:

- Open bus conditions, such as a disconnected connector

- Shorted bus conditions, such as cable damage shorting the twisted-pair together

- Idle bus conditions that occur when no driver on the bus is actively driving

In any of these cases, the differential receiver will output a failsafe logic High state so that the output of the receiver is not indeterminate.

Receiver failsafe is accomplished by offsetting the receiver thresholds such that the "input indeterminate" range does not include zero volts differential.

In order to comply with the RS-422 and RS-485 standards, the receiver output must output a High when the differential input VID is more positive than +200 mV, and must output a Low when VID is more negative than -200 mV. The receiver parameters which determine the failsafe performance are VIT(+) and VIT(-).

As shown in the Electrical Characteristics table, differential signals more negative than -200 mV will always cause a Low receiver output, and differential signals more positive than -10 mV will always cause a High receiver output. Thus, when the differential input signal is close to zero, it is still above the maximum VIT(+) threshold of - 10 mV, and the receiver output will be High.

## **Typical Application (continued)**

#### 9.2.2 Detailed Design Procedure

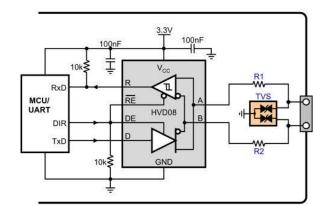

In order to protect bus nodes against high-energy transients, the implementation of external transient protection devices is necessary.

Figure 23. Transient protection against ESD, EFT, and Surge transients

Figure 23 suggests a protection circuit against 10 kV ESD (IEC 61000-4-2), 4 kV EFT (IEC 61000-4-4), and 1 kV surge (IEC 61000-4-5) transients. Table 4 shows the associated Bill of Materials.

| Table | 4 | Rill | of  | Materials |

|-------|---|------|-----|-----------|

| Iable |   |      | UI. | materials |

| DEVICE | FUNCTION                                 | ORDER NUMBER       | MANUFACTURER |  |

|--------|------------------------------------------|--------------------|--------------|--|

| XCVR   | 3.3 V to 5 V, 10 Mbps RS-485 Transceiver | XL65HVD08          | XINLUDA      |  |

| R1, R2 | 10 Ω, Pulse-Proof Thick-Film Resistor    | CRCW0603010RJNEAHP | Vishay       |  |

| TVS    | Bidirectional 400 W Transient Suppressor | CDSOT23-SM712      | Bourns       |  |

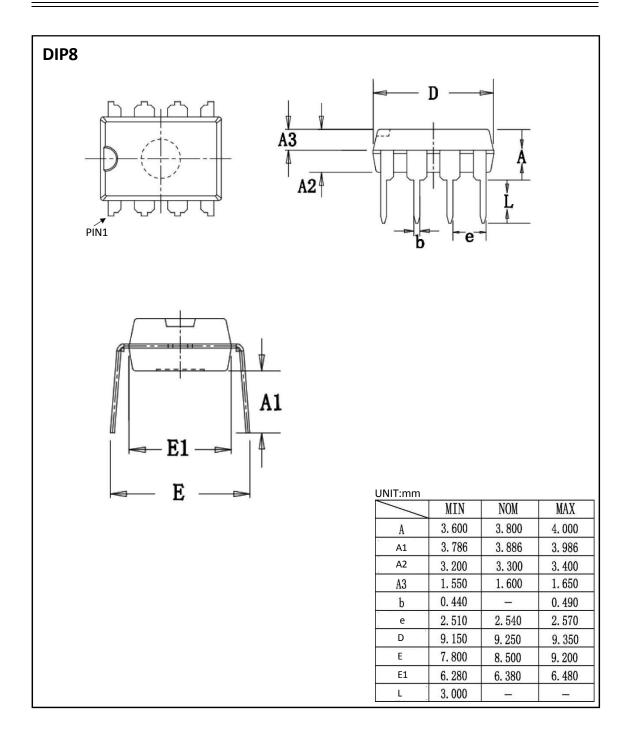

#### 9.2.3 Application Curve

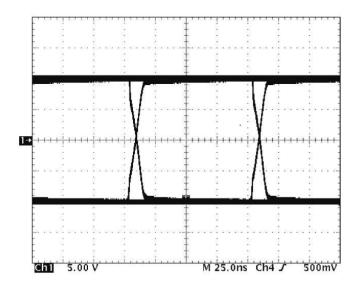

Figure 24 demonstrates operation of the XL65HVD08 at a signaling rate of 10 Mbps.

# **10. POWER SUPPLY RECOMMENDATIONS**

To ensure reliable operation at all data rates and power supply voltages, each power supply should be buffered The 100nF ceramic capacitor is located as close to the power pin as possible. TI manufacturer 's TPS76333 and TPS76350 is paired with linear voltage regulators suitable for 3.3V and 5V power supplies, respectively.

# 11. LAYOUT 11.1. Layout Guidelines

On-chip IEC-ESD protection is sufficient for laboratory and portable equipment but insufficient for EFT and surge transients occurring in industrial environments. Therefore, robust and reliable bus node design requires the use of external transient protection devices.

Because ESD and EFT transients have a wide frequency bandwidth from approximately 3 MHz to 3 GHz, high frequency layout techniques must be applied during PCB design.

- 1. Place the protection circuitry close to the bus connector to prevent noise transients from entering the board.

- 2. Use VCC and ground planes to provide low-inductance. Note that high-frequency currents follow the path of least inductance and not the path of least impedance.

- 3. Design the protection components into the direction of the signal path. Do not force the transient currents to divert from the signal path to reach the protection device.

- 4. Apply 100-nF to 220-nF bypass capacitors as close as possible to the VCC-pins of transceiver, UART, or controller ICs on the board.

- 5. Use at least two vias for VCC and ground connections of bypass capacitors and protection devices to minimize effective via-inductance.

- 6. Use  $1-k\Omega$  to  $10-k\Omega$  pullup and pulldown resistors for enable lines to limit noise currents in these lines during transient events.

- 7. Insert series pulse-proof resistors into the A and B bus lines if the TVS clamping voltage is higher than the specified maximum voltage of the transceiver bus terminals. These resistors limit the residual clamping current into the transceiver and prevent it from latching up.

- 8. While pure TVS protection is sufficient for surge transients up to 1 kV, higher transients require metal-oxide varistors (MOVs) which reduce the transients to a few hundred volts of clamping voltage, and transient blocking units (TBUs) that limit transient current to less than 1 mA.

## 11.2. Layout Example

Figure 25.XL65HVD08 Layout example

# **12. ORDERING INFORMATION**

| č           |                   |                 |                   |                     |      |                    |                     |  |

|-------------|-------------------|-----------------|-------------------|---------------------|------|--------------------|---------------------|--|

| Part Number | Device<br>Marking | Package<br>Type | Body size<br>(mm) | Temperature<br>(°C) | MSL  | Transport<br>Media | Package<br>Quantity |  |

| XL65HVD08DR | XL65HVD08         | SOP8            | 4.90 * 3.90       | - 40 to 85          | MSL3 | T&R                | 2500                |  |

| XL65HVD08P  | 65HVD08P          | DIP8            | 9.25 * 6.38       | - 40 to 85          | MSL3 | Tube 50            | 2000                |  |

#### **Ordering Information**

# **13. DIMENSIONAL DRAWINGS**

[if you need helpcontact us. Xinluda reserves the right to change the above information without prior notice]