# 1.0MHz, 1.2A/1.5A Synchronous Step-Down Converter

# **FEATURES**

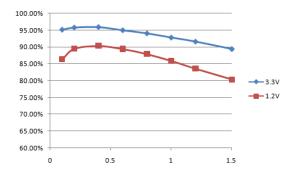

- . High Efficiency: Up to 96%(@3.3V)

- . 1.0MHz Constant Frequency Operation

- . 1.5A Output Current

- No Schottky Diode Required

- . 2.3V to 6V Input Voltage Range

- Output Voltage as Low as 0.6V

- PFM Mode for High Efficiency in Light Load

- . 100% Duty Cycle in Dropout Operation

- . Low Quiescent Current: 40μA

- . Short Circuit Protection

- . Thermal Fault Protection

- Inrush Current Limit and Soft Start

- . Input overvoltage protection(OVP)

- . <1µA Shutdown Current

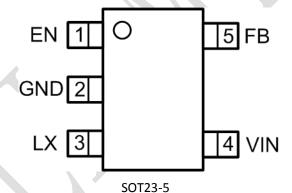

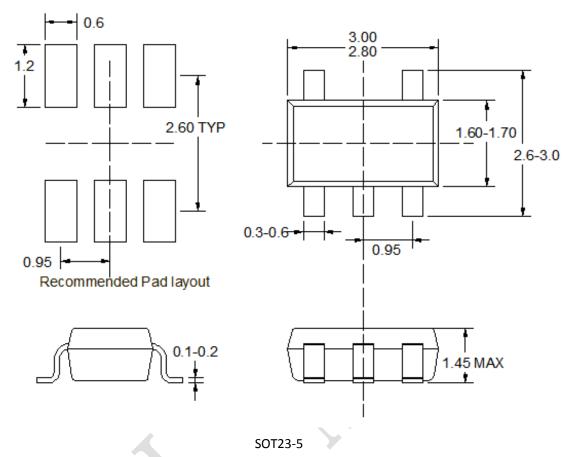

- SOT23-5 package

## **APPLICATIONS**

- . Cellular and Smart Phones

- Wireless and DSL Modems

- . Portable Instruments

- . Digital Still and Video Cameras

- PC Cards

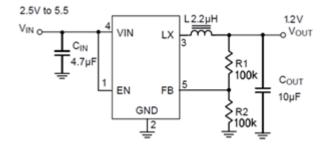

## **APPILCATIONs**

Figure 1. Basic Application Circuit

## GENERAL DESCRIPTION

The STI3410 are high-efficiency, high frequency synchronous step-down DC-DC regulator ICs capable of delivering up to 1.5A output currents. The STI3410 can operate over a wide input voltage range from 2.3V to 6.0V and integrate main switch and synchronous switch with very low RDS(ON) to minimize the conduction loss.

It is ideal for powering portable equipment that runs from a single cell Lithium-Ion (Li+) battery. The output voltage can be regulated as low as 0.6V. The STI3410 can also EN at 100% duty cycle for low dropout operation, extending battery life in portable system. This device offers two operation modes, PWM control and PFM Mode switching control, which allows a high efficiency over the wider range of the load.

The STI3410 is offered in a low profile (1mm) 5-pin, SOT package, and is available in an adjustable version.

Figure 2. Efficiency(%) vs. Load Current(A)

TMÍ SUNTO

www.toll-semi.com www.suntosemi.com

# **ABSOLUTE MAXIMUM RATINGS (Note 1)**

| Parameter                       | Value        | Unit |

|---------------------------------|--------------|------|

| Input Supply Voltage ,          | -0.3~6.0     | V    |

| LX Voltages                     | -0.3~Vin+0.3 | V    |

| EN,Vout Voltage                 | -0.3~6.0     | V    |

| Junction Temperature(Note2)     | 155          | °C   |

| Storage Temperature Range       | -65~150      | °C   |

| Lead Temperature(Soldering,10s) | 260          | °C   |

| Peak Current Limit              | 2.5          | А    |

# **PACKAGE/ORDER INFORMATION**

Top Mark: S12BXX (S12B: Device Code, XX: Inside Code)3410 S12XXX(S12: Device Code, XXX: Inside Code)3410A

| Part Number | Package | Top mark | Quantity/ Reel |

|-------------|---------|----------|----------------|

| STI3410     | SOT23-5 | S12BXX   | 3000           |

| STI3410A    | SOT23-5 | S12XXX   | 3000           |

# **PIN DESCRIPTIONS**

| Pin | Name | Function                                                                                                                                          |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | EN   | Chip Enable Pin. Drive EN above 1.5V to turn on the part. Drive EN below 0.3V to turn it off. Do not leave EN floating.                           |

| 2   | GND  | Ground Pin                                                                                                                                        |

| 3   | LX   | Power Switch Output. It is the switch node connection to Inductor. This pin connects to the drains of the internal P-ch and N-ch MOSFET switches. |

| 4   | VIN  | Power Supply Input. Must be closely decoupled to GND with a 10µF or greater ceramic capacitor.                                                    |

| 5   | VOUT | Output Voltage Feedback Pin. An internal resistive divider divides the output voltage down for comparison to the internal reference voltage.      |

# **ESD RATING**

| Items | Description                   | Value | Unit |

|-------|-------------------------------|-------|------|

| VESD  | Human Body Model for all pins | ±2000 | V    |

**JEDEC specification JS-001**

# **RECOMMENDED OPERATING CONDITIONS**

| Items         | Description                 | Min | Max | Unit |

|---------------|-----------------------------|-----|-----|------|

| Voltage Range | IN                          | 2.3 | 6   | V    |

| TA            | Operating Temperature Range | -40 | 85  | °C   |

# **ELECTRICAL CHARACTERISTICS (Note 3)**

( $V_{IN}=V_{EN}=3.6V$ , $V_{OUT}=1.8V$ ,  $T_A=25$ °C, unless otherwise noted.)

| Parameter                         | Conditions                                                                             | Min   | Тур   | Max   | Unit |

|-----------------------------------|----------------------------------------------------------------------------------------|-------|-------|-------|------|

| Input Voltage Range               |                                                                                        | 2.3   |       | 6.0   | V    |

| UVLO Threshold                    |                                                                                        | 1.7   | 1.9   | 2.1   | V    |

| Quiescent Current                 | V <sub>EN</sub> =2.0V, I <sub>OUT</sub> =0,<br>V <sub>FB</sub> =V <sub>REF</sub> *105% |       | 35    | 70    | μΑ   |

| Shutdown Current                  | EN =0                                                                                  |       | 0.1   | 1.0   | μΑ   |

| Regulated Feedback Voltage        | T <sub>A</sub> = 25°C                                                                  | 0.588 | 0.600 | 0.612 | V    |

| Decident of Feedback Valters VED  | $T_A = 0$ °C $\leq T_A \leq 85$ °C                                                     | 0.586 | 0.600 | 0.613 | V    |

| Regulated Feedback Voltage VFB    | T <sub>A</sub> = -40°C ≤ TA ≤ 85°C                                                     | 0.585 | 0.600 | 0.615 | ٧    |

| Reference Voltage Line Regulation | V <sub>IN</sub> =2.3V to 6.0V                                                          |       | 0.04  | 0.40  | %/V  |

| Output Voltage Line Regulation    | V <sub>IN</sub> = 2.3V to 6.0V                                                         |       | 0.04  | 0.4   | %    |

| Output Voltage Load Regulation    | 4 A                                                                                    |       | 0.5   |       | %    |

|                                   | Vout=100%                                                                              |       | 1.0   |       | MHz  |

| Oscillation Frequency             | Vout=0V                                                                                |       | 300   |       | KHz  |

| ON Resistance of PMOS             | I <sub>LX</sub> =100mA                                                                 |       | 0.2   |       | Ω    |

| ON Resistance of NMOS             | I <sub>LX</sub> =-100mA                                                                |       | 0.13  |       | Ω    |

| Peak Current Limit                | V <sub>IN</sub> = 3V, Vout=90% 3410A                                                   |       | 2     |       | Α    |

| Peak Current Limit                | V <sub>IN</sub> = 3V, Vout=90% 3410                                                    |       | 2.5   |       | Α    |

| EN Threshold                      |                                                                                        | 0.30  | 1.0   | 1.50  | V    |

| EN Leakage Current                |                                                                                        |       | ±0.01 | ±1.0  | μΑ   |

| LX Leakage Current                | $V_{EN}$ =0V, $V_{IN}$ = $V_{LX}$ =5V                                                  |       | ±0.01 | ±1.0  | μΑ   |

Note 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

Note 2:  $T_J$  is calculated from the ambient temperature  $T_A$  and power dissipation  $P_D$  according to the following formula:  $T_J = T_A + (P_D) \times (250^{\circ}C/W)$ .

Note 3: 100% production test at +25°C. Specifications over the temperature range are guaranteed by design and characterization.

## **OPERATION**

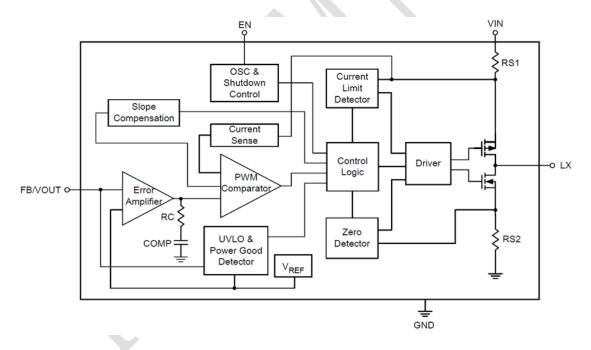

STI3410 is a synchronous buck regulator IC that integrates the PWM/PFM control, top and bottom switches on the same die to minimize the switching transition loss and conduction loss. With ultra low RDS(ON) power switches and proprietary PWM control, this regulator IC can achieve the highest efficiency and the highest switch frequency simultaneously to minimize the external inductor and capacitor size, and thus achieving the minimum solution footprint.

The STI3410 requires only three external power components (Cin, Cout and L). The adjustable version can be programmed with external feedback to any voltage, ranging from 0.6V to the input voltage. At dropout, the converter duty cycle increases to 100% and the output voltage tracks the input voltage minus the Rdson drop of the high-side MOSFET.

The internal error amplifier and compensation provides excellent transient response, load, and line regulation. Soft start function prevents input inrush current and output overshoot during start up.

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 3.STI3410 Block Diagram

# **FUNCTIONAL TEST**

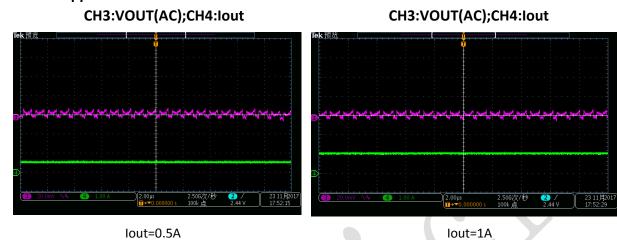

# 1.Vout ripple

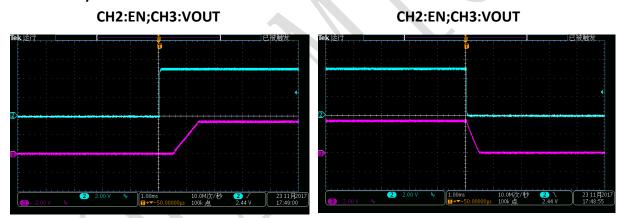

# 2.Power on/off:

#### APPLICATION INFORMATION

#### **Setting the Output Voltage**

The external resistor divider is used to set the output voltage (see Typical Application on page 1). The feedback resistor R1 also sets the feedback loop bandwidth with the internal compensation capacitor. Choose R1 to be around  $100k\Omega$  for optimal transient response. R2 is then given by:

$$R_2 = \frac{R_1}{V_{out}/V_{FB} - 1}$$

#### **Inductor Selection**

For most designs, the STI3410 operates with inductors of  $1\mu$ H to  $4.7\mu$ H. Low inductance values are physically smaller but require faster switching, which results in some efficiency loss. The inductor value can be derived from the following equation:

$$L = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times \Delta I_L \times f_{OSC}}$$

Where  $\Delta I_L$  is inductor Ripple Current. Large value inductors result in lower ripple current and small value inductors result in high ripple current. For optimum voltage-positioning load transients, choose an inductor with DC series resistance in the  $50 \text{m}\Omega$  to  $150 \text{m}\Omega$  range.

#### **Input Capacitor Selection**

With the maximum load current at 1.5A, the maximum ripple current through input capacitor is about 0.6Arms. Atypical X7R or better grade ceramic capacitor with 6V rating and greater than 10uF capacitance can handle this ripple current well. To minimize the potential noise problem, place this ceramic capacitor really close to the IN and GND pins. Care should be taken to minimize the loop area formed by CIN, and IN/GND pins.

## **Output Capacitor Selection**

The output capacitor is required to keep the output voltage ripple small and to ensure regulation loop stability. The output capacitor must have low impedance at the switching frequency. Ceramic capacitors with X5R or X7R dielectrics are recommended due to their low ESR and high ripple current ratings. The output ripple V<sub>OUT</sub> is determined by:

$$\Delta V_{OUT} \le \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times f_{OSC} \times L} \times \left(ESR + \frac{1}{8 \times f_{osc} \times C3}\right)$$

A 10µF ceramic can satisfy most applications

# STI3410A/3410

# **Layout Consideration**

When laying out the printed circuit board, the following checking should be used to ensure proper operation of the STI3410. Check the following in your layout:

- 1. The power traces, consisting of the GND trace, the LX trace and the VIN trace should be kept short, direct and wide.

- 2. Does the (+) plates of Cin connect to Vin as closely as possible. This capacitor provides the AC current to the internal power MOSFETs.

- 3. Keep the switching node, LX, away from the sensitive VOUT node.

- 4. Keep the (-) plates of Cin and Cout as close as possible

# **PACKAGE INFORMATION**

#### Note:

- 1) All dimensions are in millimeters.

- 2) Package length does not include mold flash, protrusion or gate burr.

- 3) Package width does not include inter lead flash or protrusion.

- 4) Lead popularity (bottom of leads after forming) shall be 0.10 millimeters max.

- 5) Pin 1 is lower left pin when reading top mark from left to right,