## **N-Channel 40V MOSFET**

#### E040N1P5OL1

| V <sub>DS</sub> (V) | $R_{DS(on),max}$ (m $\Omega$ ) | I <sub>D</sub> (A) |

|---------------------|--------------------------------|--------------------|

| 40V                 | 1.5 @ V <sub>GS</sub> = 10V    | 145                |

#### **Features**

- Low R<sub>DS(on)</sub> trench technology

- Low thermal impedance

- Fast switching speed

- 100% avalanche tested

# **Applications**

- DC/DC conversion

- Power switch

- PD charger

- Moto driver

# **Package And Ordering Information**

| Ordering code | Package | Marking     |  |  |

|---------------|---------|-------------|--|--|

| E040N1P5OL1   | TOLL    | E040N1P5OL1 |  |  |

### **Ordering Information**

| Package | Units/ Reel | Reels/ Inner Box | Units/ Inner Box |

|---------|-------------|------------------|------------------|

| TOLL    | 2000        | 1                | 2000             |

#### **TOLL-8**

**Key Performance Parameters**

| Parameter              | Value | Unit |

|------------------------|-------|------|

| VDS, min @ Tj(max)     | 40    | V    |

| ID, pulse              | 870   | Α    |

| RDS(ON), max @ VGS=10V | 1.5   | mΩ   |

| Qg                     | 127   | nC   |

Absolute Maximum Ratings at Tj=25°C Unless Otherwise Noted

| Parameter                                        | Symbol                | Limit                | Unit       |            |

|--------------------------------------------------|-----------------------|----------------------|------------|------------|

| Drain-source voltage                             | V <sub>DS</sub>       | 40                   |            |            |

| Gate-source voltage                              |                       |                      | ±20        | V          |

|                                                  | T <sub>C</sub> =25°C  |                      | 145        |            |

| Continuous drain current                         | T <sub>C</sub> =100°C | - I <sub>D</sub>     | •          |            |

| Pulsed drain current                             | I <sub>D,pulse</sub>  | 870                  | А          |            |

| Avalanche energy, single pulse                   | E <sub>AS</sub>       | 900                  | mJ         |            |

| Dower dissinction                                | T <sub>C</sub> =25°C  |                      | 140        |            |

| Power dissipation                                | T <sub>A</sub> =25°C  | $P_{D}$              | 2          | W          |

| Operating junction and storage temperature range |                       | TJ, T <sub>stg</sub> | -55 to 150 | $^{\circ}$ |

### **Thermal Characteristics**

| Parameter                               |              | Symbol | Max. | Uni<br>t |

|-----------------------------------------|--------------|--------|------|----------|

| Thermal resistance, junction-to-case    | Steady state | Rejc   | 1    |          |

| Thermal resistance, junction-to-ambient | Steady state | Reja   | 40   | °C/W     |

Electrical Characteristics at Tj=25°C unless otherwise specified

|                                   |                      |      |      |      | •    |                                                             |  |  |

|-----------------------------------|----------------------|------|------|------|------|-------------------------------------------------------------|--|--|

| Parameter                         | Symbol               | Min. | Тур. | Max. | Unit | Test conditions                                             |  |  |

| Static                            |                      |      |      |      |      |                                                             |  |  |

| Drain to source breakdown voltage | V <sub>(BR)DSS</sub> | 40   |      |      | ٧    | V <sub>GS</sub> = 0, I <sub>D</sub> = 250 μA                |  |  |

| Gate-source threshold voltage     | V <sub>G</sub> s(th) | 1.3  |      | 2.4  | V    | V <sub>DS</sub> = V <sub>GS</sub> , I <sub>D</sub> = 250 μA |  |  |

| Gate-body leakage                 | I <sub>GSS</sub>     |      |      | ±100 | nA   | V <sub>DS</sub> = 0 V, V <sub>GS</sub> = ±20 V              |  |  |

| Zero gate voltage drain current   | I <sub>DSS</sub>     |      |      | 1    | μΑ   | V <sub>DS</sub> = 32 V, V <sub>GS</sub> = 0 V               |  |  |

| Drain-source on-resistance        | Ros(on)              |      | 1.13 | 1.5  | mΩ   | V <sub>GS</sub> = 10 V, I <sub>D</sub> = 40 A               |  |  |

| Drain-source on-resistance        | Ros(on)              |      | 1.55 | 1.9  | mΩ   | V <sub>GS</sub> = 4.5 V, I <sub>D</sub> = 30 A              |  |  |

| Converd transcenductorses    | Gf-                 |  |         |     | S  | V -5V L - 20 A                                                           |  |

|------------------------------|---------------------|--|---------|-----|----|--------------------------------------------------------------------------|--|

| Forward transconductance     | gfs                 |  | -       |     | 5  | $V_{DS} = 5 \text{ V}, I_{D} = 30 \text{ A}$                             |  |

| Gate resistance              | Rg                  |  | 3.3     |     | Ω  | f=1MHz                                                                   |  |

| Gate Charge                  |                     |  |         |     |    |                                                                          |  |

| Total gate charge            | Qg                  |  | 124     |     |    |                                                                          |  |

| Gate-source charge           | Qgs                 |  | 25      |     | nC | $V_{DS} = 20 \text{ V}, I_D = 40 \text{ A}, V_{GS} = 10 \text{ V}$       |  |

| Gate-drain charge            | Qgd                 |  | 18      |     |    |                                                                          |  |

|                              |                     |  | Dynamic | ;   |    |                                                                          |  |

| Turn-on delay time           | t <sub>d(on)</sub>  |  | 11      |     |    |                                                                          |  |

| Rise time                    | <b>t</b> r          |  | 93      |     | ns | $V_{DS}$ = 20 V, $I_{D}$ = 40 A, $V_{GS}$ = 10 V, $R_{GEN}$ = 3 $\Omega$ |  |

| Turn-off delay time          | t <sub>d(off)</sub> |  | 144     |     |    |                                                                          |  |

| Fall time                    | t <sub>f</sub>      |  | 90      |     |    |                                                                          |  |

| Input capacitance            | C <sub>iss</sub>    |  | 9000    |     |    |                                                                          |  |

| Output capacitance           | C <sub>oss</sub>    |  | 2045    |     | pF | V <sub>DS</sub> =20 V, V <sub>GS</sub> = 0 V, f = 1MHz                   |  |

| Reverse transfer capacitance | C <sub>rss</sub>    |  | 1100    |     |    |                                                                          |  |

| Body Diode                   |                     |  |         |     |    |                                                                          |  |

| Diode forward voltage        | V <sub>SD</sub>     |  |         | 1.2 | V  | V <sub>GS</sub> = 0 V, I <sub>F</sub> = 40 A                             |  |

| Reverse recovery time        | t <sub>rr</sub>     |  | 57      |     | ns | V <sub>R</sub> = 20 V, I <sub>s</sub> =40 A, di/dt = 100                 |  |

| Reverse recovery charge      | Qrr                 |  | 58      |     | nC | A/µs                                                                     |  |

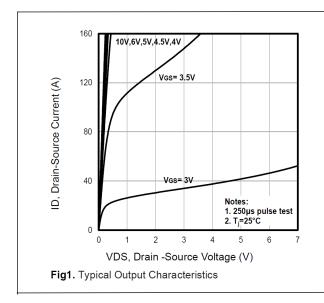

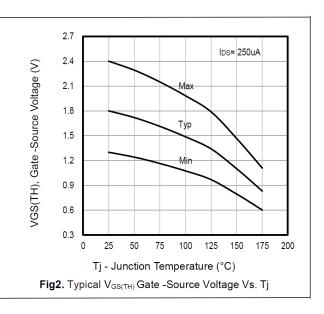

# **Electrical Characteristics Diagrams**

#### Test circuits and waveforms

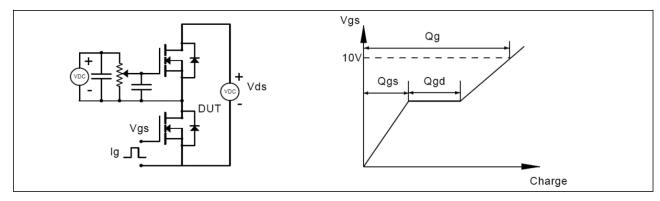

Figure 1. Gate charge test circuit & waveform

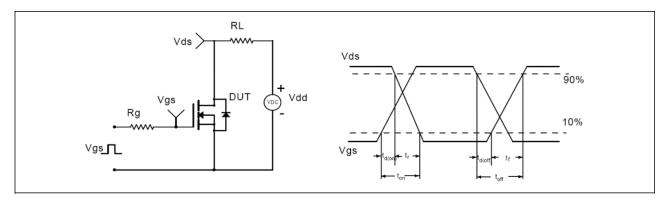

Figure 2. Switching time test circuit & waveforms

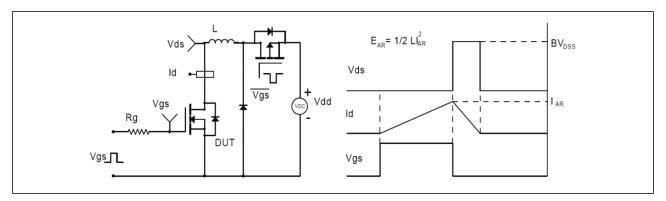

Figure 3. Unclamped inductive switching (UIS) test circuit & waveforms

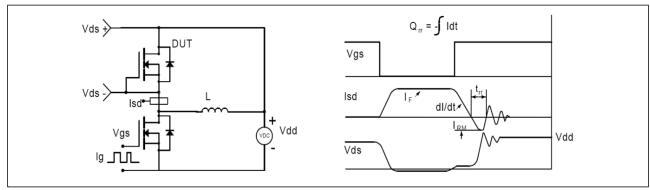

Figure 4. Diode reverse recovery test circuit & waveforms

V1.0 5 / 7

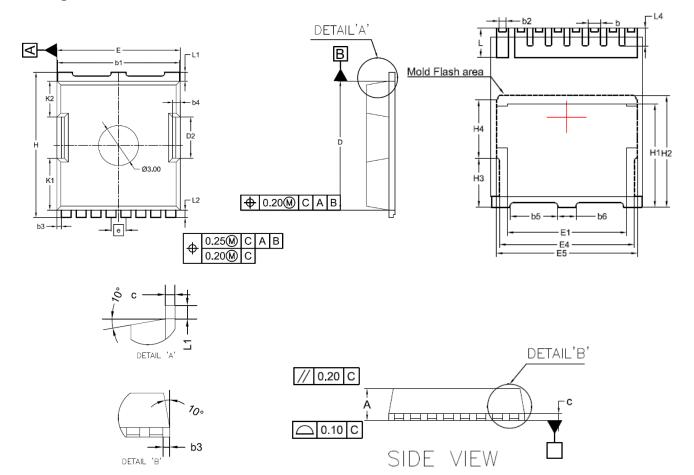

## **Package Outline Dimensions**

| SYMBOLS MIN NOM MAX MIN NOM          | MAX     |  |  |

|--------------------------------------|---------|--|--|

| * 4                                  | 1411.04 |  |  |

| * A 2.200 2.300 2.400 0.087 0.091    | 0.094   |  |  |

| c 0.492 0.500 0.508 0.019 0.020      | 0.020   |  |  |

| * D 10.280 10.380 10.480 0.405 0.409 | 0.413   |  |  |

| * E 9.800 9.900 10.000 0.386 0.390   | 0.394   |  |  |

| e 1.20 BSC 0.047 BSC                 |         |  |  |

| * H 11.580 11.680 11.780 0.456 0.460 | 0.464   |  |  |

| H1 6.650 6.750 6.850 0.262 0.266     | 0.270   |  |  |

| H2 7.300 0.287                       |         |  |  |

| H3 3.200 0.126                       |         |  |  |

| H4 3.800 0.150                       |         |  |  |

| K1 4.180 0.165                       | 0.165   |  |  |

| K2 2.900 0.114                       | 0.114   |  |  |

| * D2 3.300 0.130                     | 0.130   |  |  |

| b 0.700 0.800 0.900 0.028 0.031      | 0.035   |  |  |

| b1 9.700 9.800 9.900 0.382 0.386     | 0.390   |  |  |

| b2 0.420 0.460 0.500 0.017 0.018     | 0.020   |  |  |

| b3 0.350 0.014                       |         |  |  |

| b4 0.600 0.024                       | 0.024   |  |  |

| b5 3.100 0.122                       | 0.122   |  |  |

| b6 1.200 0.047                       | 0.047   |  |  |

| L 1.700 1.900 2.100 0.067 0.075      | 0.083   |  |  |

| L1 0.700 0.028                       | 0.028   |  |  |

| L2 0.600 0.024                       | 0.024   |  |  |

| L4 1.050 1.150 1.250 0.041 0.045     | 0.049   |  |  |

| L5 0.500 0.600 0.700 0.020 0.024     | 0.028   |  |  |

| E1 7.800 0.31                        | 0.31    |  |  |

| 21 /.800 0.31                        |         |  |  |

| E4 8.800 0.35                        |         |  |  |

#### Legal Disclaimer

The information given in this document shall be for illustrative purposes only and shall in no event be regarded as a guarantee of conditions or characteristics. Existar Technologies reserves the right to change any information herein. With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Existar Technologies or its affiliates hereby make no representation or warranty of any kind, expressed or implied, as to any information provided hereunder, including without limitation as to the accuracy, completeness or non-infringement of intellectual property rights of any third party, and they assume no liability for the consequences of use of such information. In addition, any information given in this document is subject to customer's compliance with its obligations stated herein and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Existar Technologies in customer's applications. The information contained herein is exclusively intended for technically trained staff. No license is granted by implication under any patent right, copyright, mask work right, or other intellectual property right. It is customer's sole responsibility to evaluate the suitability of the product for the intended application and the completeness of the product information given herein with respect to such application. In no event shall Existar Technologies or its affiliates be liable to any party for any direct, indirect, special, punitive, incidental or consequential damages of any nature whatsoever, including but not limited to loss of profits and loss of goodwill, whether or not such damages are based on tort or negligence, warranty, breach of contract or any other legal theory.