## 1. DESCRIPTION

The XL1000/XD1000 serves as a standalone CAN controller, designed for area network control in mobile applications as well as general industrial environments. Furthermore, it introduces a novel operational mode known as PeliCAN, which supports the CAN 2.0B protocol equipped with numerous enhanced features.

### 2. FEATURES

The XL1000/XD1000 CAN controller boasts a comprehensive feature set, including:

- Compatibility with the default BasicCAN mode

- An expanded 64-byte receive buffer (FIFO)

- Full compatibility with the CAN 2.0B protocol

- Support for both 11-bit and 29-bit identifiers

- Bit rates reaching up to 1Mbits/s

In its PeliCAN mode, it further extends its capabilities with:

- Read/write access to error counters

- Programmable error warning limits

- A register for the most recent error code

- Interrupts for every CAN bus error

- Detailed arbitration lost interrupt control through specific control bits

- Single shot transmission (without retransmission)

- Silent mode (no acknowledgment errors)

- Support for hot-plugging (software bit-rate detection)

- Expanded acceptance filter capabilities (4-byte code and 4-byte mask)

- Self-message reception (self-reception request)

Additional features include:

- A 24MHz clock frequency

- Interfaces for multiple types of microprocessors

- Programmable CAN output driver configuration

- An operating temperature range of -40°C to +125°C

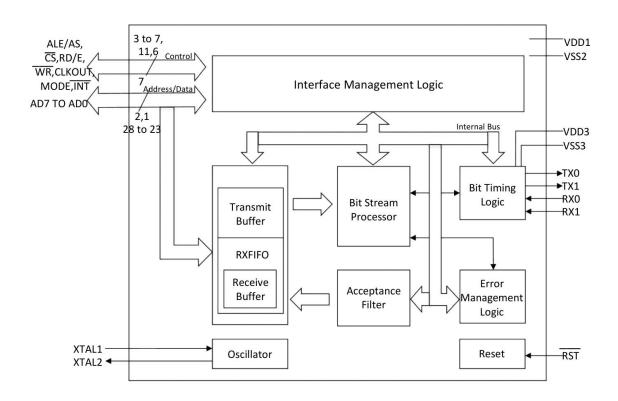

# 3. FUNCTIONAL BLOCK DIAGRAM

www.xinluda.com 2 / 6 Rev 1.1

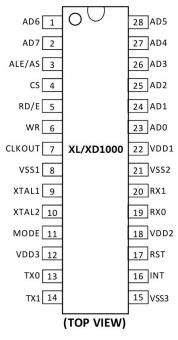

# 4. PIN CONFIGURATIONS AND FUNCTION

|            | pin configuration |                                                                                                   |  |  |  |  |  |

|------------|-------------------|---------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Symbol     | Pin               | Description                                                                                       |  |  |  |  |  |

| AD7-AD0    | 2, 1, 28-23       | Multiplexed Address/Data Bus                                                                      |  |  |  |  |  |

| ALE/AS     | 3                 | ALE Input Signal (Intel Mode), AS Input Signal (Motorola Mode)                                    |  |  |  |  |  |

| /CS        | 4                 | Chip Select Input, Low Level Enables Access to XL1000/XD1000                                      |  |  |  |  |  |

| /RD /E     | 5                 | Microcontroller's /RD Signal (Intel Mode) or E Enable Signal (Motorola Mode)                      |  |  |  |  |  |

| /WR        | 6                 | Microcontroller's /WR Signal (Intel Mode) or (R/WR) Signal (Motorola Mode)                        |  |  |  |  |  |

|            |                   | Clock Output Signal Generated by XL1000/XD1000 for Microcontroller, Derived from                  |  |  |  |  |  |

| CLKOUT     | 7                 | Internal Oscillator and Programmable, Can Be Disabled by Clock Control Register's Clock Off       |  |  |  |  |  |

|            |                   | Bit                                                                                               |  |  |  |  |  |

| VSS1       | 8                 | Ground                                                                                            |  |  |  |  |  |

| XTAL1      | 9                 | Input to Oscillator Amplifier Circuit, External Oscillator Signal Input (Note 1)                  |  |  |  |  |  |

| XTAL2      | 10                | Oscillator Amplifier Circuit Output, Left Open Circuit Output When Using External Oscillator      |  |  |  |  |  |

| XTALZ 10   |                   | Signal (Note 1)                                                                                   |  |  |  |  |  |

| MODE       | 11                | Mode Select Input<br>1 = Intel Mode<br>0 = Motorola Mode                                          |  |  |  |  |  |

| VDD3       | 12                | 5V Voltage Source for Output Drivers                                                              |  |  |  |  |  |

| TX0        | 13                | Output from CAN Output Driver 0 to Physical Line                                                  |  |  |  |  |  |

| TX1        | 14                | Output from CAN Output Driver 1 to Physical Line                                                  |  |  |  |  |  |

| VSS3       | 15                | Ground for Output Drivers                                                                         |  |  |  |  |  |

|            |                   | Interrupt Output for interrupting the microcontroller. /INT is active low when any of the         |  |  |  |  |  |

| /INT       | 16                | internal interrupt register bits are set. /INT is an open-drain output and wired-OR with other    |  |  |  |  |  |

|            |                   | /INTs in the system. A low level on this pin can activate the IC from sleep mode.                 |  |  |  |  |  |

| /RST       | 17                | Reset Input for resetting the CAN interface (active low). Connect /RST pin to VSS through a       |  |  |  |  |  |

| 71.51      |                   | capacitor and to VDD through a resistor for automatic power-on reset (e.g., C=1nF; R=50K).        |  |  |  |  |  |

| VDD2       | 18                | 5V Voltage Source for Input Comparators                                                           |  |  |  |  |  |

|            |                   | The input to the input comparator of XL1000/XD1000 from the physical CAN bus determines           |  |  |  |  |  |

|            |                   | the control level, which will wake up XL1000/XD1000 from its sleep mode. If the level of RX1      |  |  |  |  |  |

|            | 19,20             | is higher than that of RXO, the dominant control level is read. Conversely, if RXO is higher,     |  |  |  |  |  |

| RXO<br>RX1 |                   | the recessive level is read. If the CBP bit in the Clock Prescaler Register is set, the CAN input |  |  |  |  |  |

|            |                   | comparator is bypassed to reduce internal delay, assuming an external transceiver circuitry       |  |  |  |  |  |

|            |                   | is connected. In this scenario, only RXO is active; the recessive level is considered high, while |  |  |  |  |  |

|            |                   | the dominant level is considered low.                                                             |  |  |  |  |  |

| VSS2       | 21                | Ground for Input Comparators                                                                      |  |  |  |  |  |

| VDD1       | 22                | 5V Voltage Source for Logic Circuits                                                              |  |  |  |  |  |

Notes:1.The XTAL1 and XTAL2 pins must be connected to the VSS 1 through a capacitance of 15 pF.

## 5. LIMIT VALUE

| Symbol      | Parameter                                           | Condition | Min   | Max   | Unit                   |

|-------------|-----------------------------------------------------|-----------|-------|-------|------------------------|

| VDD         | Power Supply                                        |           | -0.5  | +6.5  | V                      |

| II,IO       | Input/Output Current of All Pins Except TX0 and TX1 |           | -     | ±4    | mA                     |

| IOT(sink)   | Total Current Consumption by TX0 and TX1            |           | -     | 30    | mA                     |

| IOT(source) | Combined Source Current of TX0 and TX1              |           | -     | -20   | mA                     |

| Tamb        | Operating Ambient Temperature                       |           | -40   | +125  | $^{\circ}\!\mathbb{C}$ |

| Tstg        | Storage Temperature                                 |           | -65   | +150  | °C                     |

| Ptot        | Total Power Consumption                             |           | -     | 1.0   | W                      |

|             |                                                     | Note2     | -1500 | +1500 | V                      |

| Vesd        | Discharge of Each Pin                               | Note4     | -200  | +200  | V                      |

#### Notes

- 1. During operation, IOT is a peak current with a width of t<100ms. The average output current of each TX does not exceed 10mA.

- 2. This value is based on the allowable maximum temperature and package thermal resistance, rather than the device power consumption.

- 3. Human Body Model: Equivalent to discharging a 100pF capacitor through a 1.5k  $\!\Omega$  resistor.

- 4. Machine Model: Equivalent to discharging a 200pF capacitor through an RL circuit of  $25\Omega$  and positive  $2.5\mu$ H.

### 6. DC CHARACTERISTICS

VDD = 5V (±10%); VSS = 0V; Tamb = -40°C to +125°C; All voltages are referenced to VSS unless otherwise specified.

| Symbol        | Parameter                                                     | Condition                                                                         | Min      | Max      | Unit |

|---------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------|----------|----------|------|

|               | Pow                                                           | ver Supply                                                                        |          |          | •    |

| VDD           | Voltage Source                                                |                                                                                   | 4.5      | 5.5      | ٧    |

| IDD           | Operating Current                                             | fOSC=24MHz ;note 1                                                                |          | 15       | mA   |

| Ism           | Sleep Mode Current                                            | Non-active state of oscillator note2                                              |          | 40       | uA   |

|               |                                                               | Input                                                                             |          |          |      |

| VIL1          | Low-Level Input on Pins ALE/AS/CS,<br>(/RD)/E/WR, and MODE    |                                                                                   | -0.5     | +0.8     | V    |

| VIL2          | Low-Level Input Voltage on Pins<br>XTAL1 and /INT             |                                                                                   |          | 0.3 VDD  | V    |

| VIL3          | Low-Level Input Voltage on Pins<br>/RST, ADO-AD7, and RX0     |                                                                                   | -0.5     | +0.6     | V    |

| VIH1          | High-Level Input Voltage on Pins                              |                                                                                   | 2.0      | VDD+0.5  | V    |

| VIH2          | High-Level Input Voltage on Pins<br>XTAL1 and /INT            |                                                                                   | 0.7VDD   |          | V    |

| VIH3          | High-Level Input Voltage on Pins<br>/RST, AD0-AD7, and RX0    |                                                                                   | 2.4      | VDD+0.5  | V    |

| hy sRST       | Input Hysteresis on Pins /RST, AD0-<br>AD7, and RX0           |                                                                                   | 500      | -        | mA   |

| ILI           | Leakage Current on Pins Except<br>XTAL1, RXO, and RX1         | 0.45V <vi(d)<vdd;note3< td=""><td>-</td><td>±2</td><td>uA</td></vi(d)<vdd;note3<> | -        | ±2       | uA   |

|               |                                                               | Dutput                                                                            |          |          |      |

| VOL           | Low-Level Output Voltage on Pins<br>AD0-AD7, CLKOUT, and /INT | IOL=4Ma                                                                           |          | 0.4      | V    |

| VOH           | High-Level Output Voltage on Pins AD0-AD7, CLKOUT, and /INT   |                                                                                   | VDD-0.4  |          | V    |

|               | CAN Inpu                                                      | ut Comparator                                                                     |          | •        | •    |

| Vth(I) (diff) | Differential Input Threshold Voltage                          | VDD=5V±10%;                                                                       |          | 32       | mV   |

| Vhys          | Hysteresis Voltage                                            | 1.4V <vi(rx)<vdd-1.4v< td=""><td>8</td><td>30</td><td>mV</td></vi(rx)<vdd-1.4v<>  | 8        | 30       | mV   |

| 11            | Input Current                                                 | note 4 , 6                                                                        |          | ±400     | nA   |

|               | CAN O                                                         | utput Driver                                                                      | <u> </u> | <u> </u> |      |

| VOL(TX) | Low-Level Input Voltage on Pins TX0 and TX1  | VDD=5V 10% IO=1.2mA;<br>note6 IO=10mA |                     | 0.05<br>0.4 | V |

|---------|----------------------------------------------|---------------------------------------|---------------------|-------------|---|

| VOH(TX) | High-Level Input Voltage on Pins TX0 and TX1 | VDD=5V 10% IO=1.2mA;<br>note6 IO=10mA | VDD-0.05<br>VDD-0.4 |             | V |

#### **NOTES**

- 1.AD0-AD7 = ALE = /RD = /WR = /CS = VDD; /RST = MODE = VSS; RX0 = 2.7V; RX1 = 2.3V; XTAL1 = 0.5V or VDD 0.5V; All outputs are unloaded.

- 2.AD0-AD7 = ALE = /RD = /WR = /INT = /RST = /CS = MODE = RX0 = VDD; RX1 = XTAL1 = VSS; All outputs are unloaded.

- 3.VID = Input voltage at the data input pins.

- 4.VIRX = Input voltage at RXO and RX1 pins.

- $5. Applies \ only \ when \ the \ comparator \ by pass \ mode \ is \ enabled.$

- 6.Not tested during production.

### 7. AC CHARACTERISTIC

#### VDD = 5 V $\pm$ 10%; VSS = 0 V; CL = 50 pF (output pin); Tamb = -40 $^{\sim}$ + 125; unless otherwise noted; Note 1

| Symbol       | Parameter                                  | Condition                         | Min | Max | Unit |

|--------------|--------------------------------------------|-----------------------------------|-----|-----|------|

| fOSC         | Oscillator Frequency                       |                                   |     | 24  | MHz  |

| tSU(A-AL)    | Address Setup Time for ALE/AS Low Level    | 8                                 |     | ns  |      |

| th(A-LA)     | Hold Time with ALE Low                     |                                   | 2   |     | ns   |

| tW(AL)       | Pulse Width of ALE/AS                      |                                   | 8   |     | ns   |

| tRLQV        | /RD Low for Valid Output Data              | Intel                             |     | 50  | ns   |

| tEHQV        | E High for Valid Output Data               | Motorola                          |     | 50  | ns   |

| tRHDZ        | /RD High for Data Tri-state                | Intel                             |     | 30  | ns   |

| tELDZ        | E Low for Data Tri-state                   | Motorola                          |     | 30  | ns   |

| tDVWH        | /WR High for Valid Input Data              | Intel                             | 8   |     | ns   |

| tWHDX        | Data Hold Time after /WR High              | Intel                             | 8   |     | ns   |

| tWHLH        | /WR High to Next ALE High                  |                                   | 15  |     | ns   |

| tELAH        | E Low to Next AS High                      | E Low to Next AS High Motorola 15 |     |     | ns   |

| tsu(I)(D-EL) | Input Data Setup Time with E Low           | Setup Time with E Low Motorola 8  |     |     | ns   |

| th(I)(EL-D)  | Input Data Hold Time with E Low Motorola 8 |                                   | 8   |     | ns   |

| tLLWL        | ALE Low to /WR Low Intel 1                 |                                   | 10  |     | ns   |

| tLLRL        | ALE Low to /RD Low Intel                   |                                   | 10  |     | ns   |

| tLLEH        | AS Low to E High Motorola 1                |                                   | 10  |     | ns   |

| tsu(R-EH)    | RD/(/WR) to E High Setup Time Motorola     |                                   | 5   |     | ns   |

| tW(W)        | /WR Pulse Width                            | Intel                             | 20  |     | ns   |

| tW(R)        | /RD Pulse Width                            | Intel                             | 40  |     | ns   |

| tW(E)        | E Pulse Width                              | Motorola                          | 40  |     | ns   |

| tCLWL        | /CS Low to /WR Low Intel 0                 |                                   | 0   |     | ns   |

| tCLRL        | /CS Low to /RD Low Intel                   |                                   | 0   |     | ns   |

| tCLEH        | /CS Low to E High                          | Motorola                          | 0   |     | ns   |

| tWHCH        | /WR High to /CS High                       | Intel                             | 0   |     | ns   |

| tRHCH        | /RD High to /CS High                       | /RD High to /CS High Intel        |     |     | ns   |

| tELCH        | E Low to /CS High                          | Motorola 0                        |     |     | ns   |

| tW(RST)      | T) /RST Pulse Width 100                    |                                   | 100 |     | ns   |

| '            | Input Comparator / Ou                      | tput Driver                       |     |     |      |

| tSD          | Sum of Input and Output Delays             |                                   |     | 40  | ns   |

## Notes

<sup>1.</sup> AC characteristics are not tested during production.

<sup>2.</sup> If an external transmit-receive circuit is used, the analog input comparator can be internally bypassed by setting the CBP bit in the clock prescaler register. This will reduce the delay (<26ns) for the input voltage VI(RX) at RXO and RX1 pins.

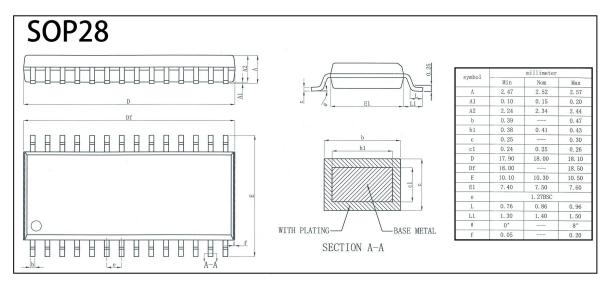

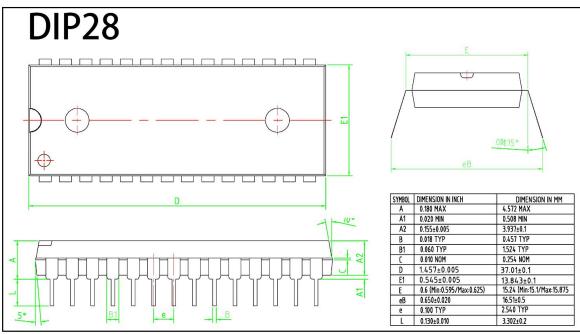

## 8. ORDERING INFORMATION

## **Ordering Information**

| Part<br>Number | Device<br>Marking | Package<br>Type | Body size<br>(mm) | Temperature<br>(°C) | MSL  | Transport<br>Media | Package<br>Quantity |

|----------------|-------------------|-----------------|-------------------|---------------------|------|--------------------|---------------------|

| XL1000         | XL1000            | SOP28           | 18.25 * 7.50      | - 0 to +70          | MSL3 | T&R                | 1000                |

| XD1000         | XD1000            | DIP28           | 37.01 * 13.84     | - 0 to +70          | MSL3 | T&R                | 260                 |

## 9. DIMENSIONAL DRAWINGS

$[if you need help contact us. Xinluda\ reserves\ the\ right\ to\ change\ the\ above\ information\ without\ prior\ notice\ ]$