# ESP32-P4 系列芯片

## 技术规格书

搭载 RISC-V 32 位双核与单核处理器的高性能 MCU

强大的图像与语音处理能力

芯片封装内可叠封 16 MB 或 32 MB PSRAM

55 个 GPIO，丰富的外设

QFN104 (10×10 mm) 封装

包括：

ESP32-P4NRW16

ESP32-P4NRW32

预发布 v0.4

乐鑫信息科技

版权 © 2024

# 产品概述

ESP32-P4 是一款高性能 MCU，支持超大片上内存，具有强大的图像和语音处理能力。该款 MCU 包含一个高性能 (HP) 系统和一个低功耗 (LP) 系统。HP 系统由 RISC-V 双核处理器驱动，包含丰富的外设；LP 系统由 RISC-V 单核处理器驱动，其外设针对低功耗应用进行了优化。

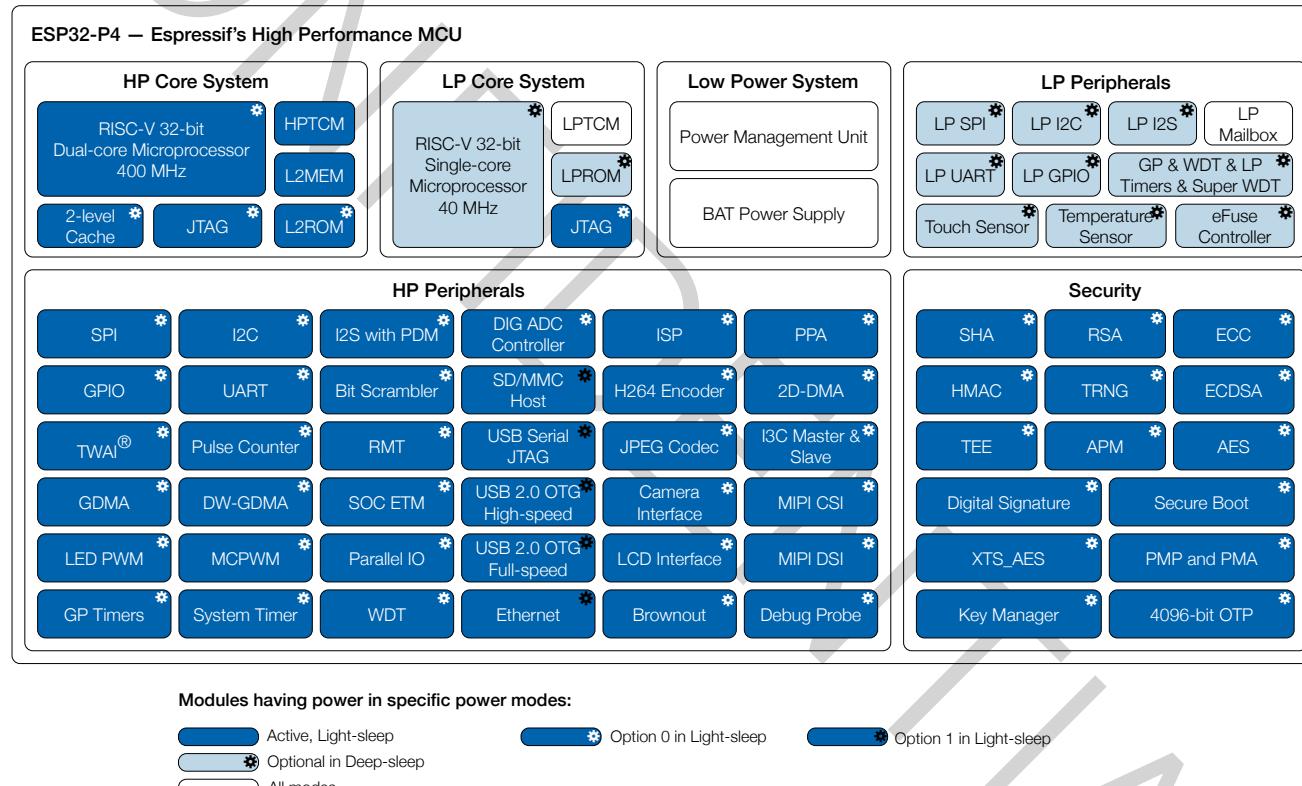

芯片的功能框图如下图所示。

ESP32-P4 功能框图

注：USB Serial JTAG 与 USB 2.0 OTG Full-Speed 功能尚未支持，将在未来的芯片版本中支持。

## 产品特性

### CPU 和存储

- 用于 HP 系统的 RISC-V 32 位双核处理器，主频高达 400 MHz

- 用于 LP 系统的 RISC-V 32 位单核处理器，主频高达 40 MHz

- 128 KB HP ROM

- 16 KB LP ROM

- 768 KB HP L2MEM

- 32 KB LP SRAM

- 8 KB 系统紧密耦合内存 (TCM)

- 多个高速外部存储器接口

- 两级高速缓存

### 高级外设接口和传感器

- 55 个可编程 GPIO

- 5 个作为 strapping 管脚

- 图像与语音处理接口：

- JPEG 编/解码器

- 像素处理加速器 (PPA)

- 图像信号处理器 (ISP)

- H264 视频编码器

- 数字接口：

- 4 个 SPI

- LP SPI

- 5 个 UART

- LP UART

- I<sup>2</sup>C

- 2 个 I<sup>2</sup>C

- LP I<sup>2</sup>C

- 3 个 I<sup>2</sup>S

- LP I<sup>2</sup>S

- 红外收发器

- LED PWM 控制器，多达 8 个通道

- 2 个电机控制脉宽调制器 (MCPWM)，多达 6 个通道

- 脉冲计数器 (PCNT), 多达 4 个通道

- 3 个 TWAI® 控制器, 兼容 ISO 11898-1

- 高速 USB 2.0 OTG

- 全速 USB 2.0 OTG

- 全速 USB 串口/JTAG 控制器

- 百兆以太网 MAC

- SD/MMC 3.0 host

- MIPI CSI-2, 2-lane x 1.5 Gbps

- MIPI DSI, 2-lane x 1.5 Gbps

- 24-bit LCD 接口

- 16-bit CAM 接口

- 2 个 GDMA 控制器

- DW-GDMA 控制器

- 2D-DMA 控制器

- 比特传输控制器

- 事件任务矩阵 (ETM)

- 并行 IO (PARLIO) 控制器

- LP 信箱控制器

- 模拟接口:

- 2 个 12 位多通道模/数转换器

- 温度传感器

- 触摸传感器, 多达 14 个通道

- 模拟电压比较器

- 欠压监测

- 定时器:

- 4 个 54 位 HP 通用定时器

- 2 个 52 位 HP 系统定时器

- 2 个 32 位 HP 看门狗定时器

- 48 位 LP 通用定时器

- 32 位 LP 看门狗定时器

- 模拟超级看门狗定时器

## 安全机制

- 安全启动

- eFuse OTP 提供的一次性写入安全性

- 加密硬件加速器：

- AES-128/256 (FIPS PUB 197, 抗 DPA 攻击)

- SHA 加速器 (FIPS PUB 180-4)

- RSA 加速器

- ECC 加速器

- ECDSA 椭圆曲线数字签名 (ECDSA)

- 数字签名

- HMAC

- 基于物理不可复制特性 (PUF) 的密钥管理器

- 访问权限管理

- 真随机数生成器 (TRNG)

- PMP 与 PMA

## 应用

低功耗芯片 ESP32-P4 专为物联网 (IoT) 设备而设计，应用领域包括：

- 智能家居

- 工业自动化

- 医疗保健

- 消费电子产品

- 智慧农业

- POS 机

- 服务机器人

- 音频设备

- 通用低功耗 IoT 传感器集线器

- 通用低功耗 IoT 数据记录器

- 摄像头视频流传输

- USB 设备

- 语音识别

- 图像识别

- 触摸和接近感应

# 目录

|                            |    |

|----------------------------|----|

| <b>产品概述</b>                | 2  |

| 产品特性                       | 3  |

| 应用                         | 5  |

| <b>1 ESP32-P4 系列型号对比</b>   | 11 |

| 1.1 命名规则                   | 11 |

| 1.2 型号对比                   | 11 |

| <b>2 管脚</b>                | 12 |

| 2.1 管脚布局                   | 12 |

| 2.2 管脚概述                   | 13 |

| 2.3 IO 管脚                  | 17 |

| 2.3.1 IO MUX 功能            | 17 |

| 2.3.2 LP IO MUX 功能         | 21 |

| 2.3.3 模拟功能                 | 22 |

| 2.3.4 GPIO 和 LP GPIO 的限制   | 24 |

| 2.4 专用数字管脚                 | 25 |

| 2.5 模拟管脚                   | 27 |

| 2.6 电源                     | 28 |

| 2.6.1 电源管脚                 | 28 |

| 2.7 芯片与 flash 的管脚对应关系      | 29 |

| <b>3 启动配置项</b>             | 30 |

| 3.1 芯片启动模式控制               | 30 |

| 3.2 ROM 日志打印控制             | 31 |

| 3.3 JTAG 信号源控制             | 31 |

| <b>4 功能描述</b>              | 33 |

| 4.1 系统                     | 33 |

| 4.1.1 微处理器和主控              | 33 |

| 4.1.1.1 高性能处理器             | 33 |

| 4.1.1.2 处理器指令拓展            | 33 |

| 4.1.1.3 低功耗处理器             | 34 |

| 4.1.2 系统 DMA               | 34 |

| 4.1.2.1 通用 DMA 控制器         | 34 |

| 4.1.2.2 DW-GDMA 控制器        | 34 |

| 4.1.2.3 2D-DMA 控制器         | 35 |

| 4.1.3 存储器组织结构              | 35 |

| 4.1.3.1 系统和存储器             | 36 |

| 4.1.3.2 eFuse 控制器          | 37 |

| 4.1.3.3 Cache              | 37 |

| 4.1.4 系统组件                 | 37 |

| 4.1.4.1 IO MUX 和 GPIO 交换矩阵 | 38 |

|          |                       |    |

|----------|-----------------------|----|

| 4.1.4.2  | 复位和时钟                 | 38 |

| 4.1.4.3  | 事件任务矩阵                | 39 |

| 4.1.4.4  | 低功耗管理                 | 39 |

| 4.1.4.5  | 系统定时器                 | 39 |

| 4.1.4.6  | 定时器组                  | 39 |

| 4.1.4.7  | 看门狗定时器                | 40 |

| 4.1.4.8  | RTC 定时器               | 40 |

| 4.1.4.9  | 访问权限管理                | 40 |

| 4.1.4.10 | LP 信箱控制器              | 41 |

| 4.1.4.11 | 欠压监测                  | 41 |

| 4.1.5    | 加密和安全组件               | 41 |

| 4.1.5.1  | AES 加速器               | 41 |

| 4.1.5.2  | ECC 加速器               | 41 |

| 4.1.5.3  | HMAC 加速器              | 42 |

| 4.1.5.4  | RSA 加速器               | 42 |

| 4.1.5.5  | SHA 加速器               | 42 |

| 4.1.5.6  | 数字签名                  | 43 |

| 4.1.5.7  | 椭圆曲线数字签名算法            | 43 |

| 4.1.5.8  | 片外存储器加密与解密            | 43 |

| 4.1.5.9  | 真随机数生成器               | 44 |

| 4.1.5.10 | 密钥管理器                 | 44 |

| 4.2      | 外设                    | 45 |

| 4.2.1    | 图像和声音处理               | 45 |

| 4.2.1.1  | JPEG 图像编解码器           | 45 |

| 4.2.1.2  | 图像信号处理器               | 45 |

| 4.2.1.3  | 像素处理加速器               | 46 |

| 4.2.1.4  | Camera-LCD 控制器        | 46 |

| 4.2.1.5  | H264 编码器              | 47 |

| 4.2.1.6  | MIPI 相机串行接口           | 48 |

| 4.2.1.7  | MIPI 显示串行接口           | 48 |

| 4.2.2    | 通讯接口                  | 48 |

| 4.2.2.1  | UART 控制器              | 48 |

| 4.2.2.2  | SPI 控制器               | 49 |

| 4.2.2.3  | I2C 控制器               | 50 |

| 4.2.2.4  | 模拟 I2C 主机             | 50 |

| 4.2.2.5  | I3C 控制器               | 50 |

| 4.2.2.6  | I2S 控制器               | 51 |

| 4.2.2.7  | LP I2S 控制器            | 51 |

| 4.2.2.8  | 脉冲计数控制器               | 51 |

| 4.2.2.9  | 高速 USB 2.0 OTG        | 52 |

| 4.2.2.10 | 全速 USB 2.0 OTG        | 53 |

| 4.2.2.11 | USB 串口/JTAG 控制器       | 54 |

| 4.2.2.12 | 以太网介质访问控制器 (EMAC)     | 54 |

| 4.2.2.13 | 双线汽车接口                | 54 |

| 4.2.2.14 | SD/MMC 主机控制器 (SDHOST) | 55 |

| 4.2.2.15 | LED PWM 控制器           | 55 |

|                             |                       |    |

|-----------------------------|-----------------------|----|

| 4.2.2.16                    | 电机控制脉宽调制器             | 56 |

| 4.2.2.17                    | 红外遥控                  | 56 |

| 4.2.2.18                    | 并行 IO 控制器             | 56 |

| 4.2.2.19                    | 比特传输控制器               | 56 |

| 4.2.3                       | 模拟信号处理                | 57 |

| 4.2.3.1                     | 触摸传感器                 | 57 |

| 4.2.3.2                     | 温度传感器                 | 57 |

| 4.2.3.3                     | 模/数转换器 (ADC)          | 57 |

| 4.2.3.4                     | 模拟电压比较器               | 57 |

| <b>5</b>                    | <b>电气特性</b>           |    |

| 5.1                         | 绝对最大额定值               | 58 |

| 5.2                         | 建议工作条件                | 58 |

| 5.3                         | VFB_VO1 输出特性          | 58 |

| 5.4                         | 直流电气特性 (3.3 V, 25 °C) | 59 |

| <b>附录 A – ESP32-P4 管脚总览</b> |                       | 60 |

| <b>修订历史</b>                 |                       | 63 |

## 表格

|      |                          |    |

|------|--------------------------|----|

| 1-1  | ESP32-P4 系列芯片对比          | 11 |

| 2-1  | 管脚概述                     | 13 |

| 2-2  | 通过 IO MUX 连接的外设信号        | 17 |

| 2-3  | IO MUX 管脚功能              | 18 |

| 2-4  | 通过 LP IO MUX 连接的 LP 外设信号 | 21 |

| 2-5  | LP IO MUX 功能             | 21 |

| 2-6  | 连接模拟功能的模拟信号              | 22 |

| 2-7  | 模拟功能                     | 22 |

| 2-8  | 专用外设信号                   | 25 |

| 2-9  | 专用数字管脚                   | 25 |

| 2-10 | 模拟管脚                     | 27 |

| 2-11 | 电源管脚                     | 28 |

| 2-12 | 芯片与封装外 flash 的管脚对应关系     | 29 |

| 3-1  | Strapping 管脚默认配置         | 30 |

| 3-2  | 系统启动模式控制                 | 30 |

| 3-3  | UARTO ROM 日志打印控制         | 31 |

| 3-4  | USB 串口/JTAG ROM 日志打印控制   | 31 |

| 3-5  | JTAG 信号源控制               | 32 |

| 5-1  | 绝对最大额定值                  | 58 |

| 5-2  | 建议工作条件                   | 58 |

| 5-3  | VFB_VO1 内部和输出特性          | 59 |

| 5-4  | 直流电气特性 (3.3 V, 25 °C)    | 59 |

## 插图

|                        |    |

|------------------------|----|

| 1-1 ESP32-P4 系列芯片命名规则  | 11 |

| 2-1 ESP32-P4 管脚布局（俯视图） | 12 |

| 4-1 地址映射结构             | 36 |

CONFIDENTIAL

# 1 ESP32-P4 系列型号对比

## 1.1 命名规则

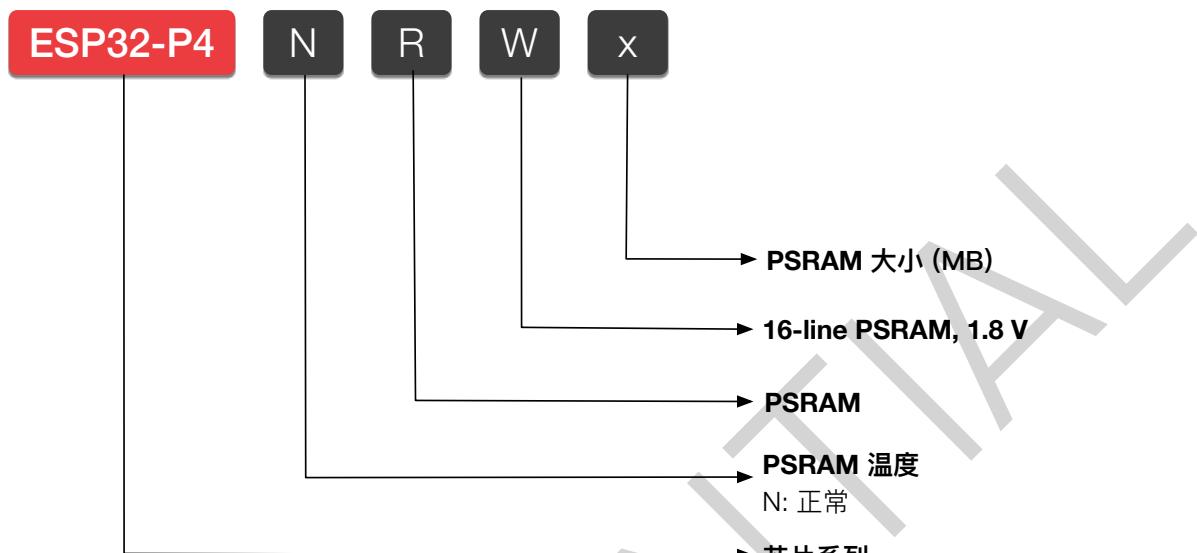

图 1-1. ESP32-P4 系列芯片命名规则

## 1.2 型号对比

表 1-1. ESP32-P4 系列芯片对比

| 订购代码          | 封装内 PSRAM                    | 环境温度 <sup>1</sup> | VDDPST 电压 <sup>2</sup> |

|---------------|------------------------------|-------------------|------------------------|

| ESP32-P4NRW16 | 16 MB (OPI/HPI) <sup>3</sup> | -40 ~ 85°C        | 1.8 V                  |

| ESP32-P4NRW32 | 32 MB (OPI/HPI) <sup>3</sup> | -40 ~ 85°C        | 1.8 V                  |

<sup>1</sup> 环境温度指乐鑫芯片外部的推荐环境温度。

<sup>2</sup> 更多关于 VDDPST 的信息, 请参考章节 2.6 电源。

<sup>3</sup> PSRAM 的 OPI 支持每个传输周期传输八位命令、地址和数据; HPI 支持每个传输周期传输八位命令和地址, 以及十六位数据。更多关于 SPI 模式的信息, 请参考章节 2.7 芯片与 flash 的管脚对应关系。

## 2 管脚

### 2.1 管脚布局

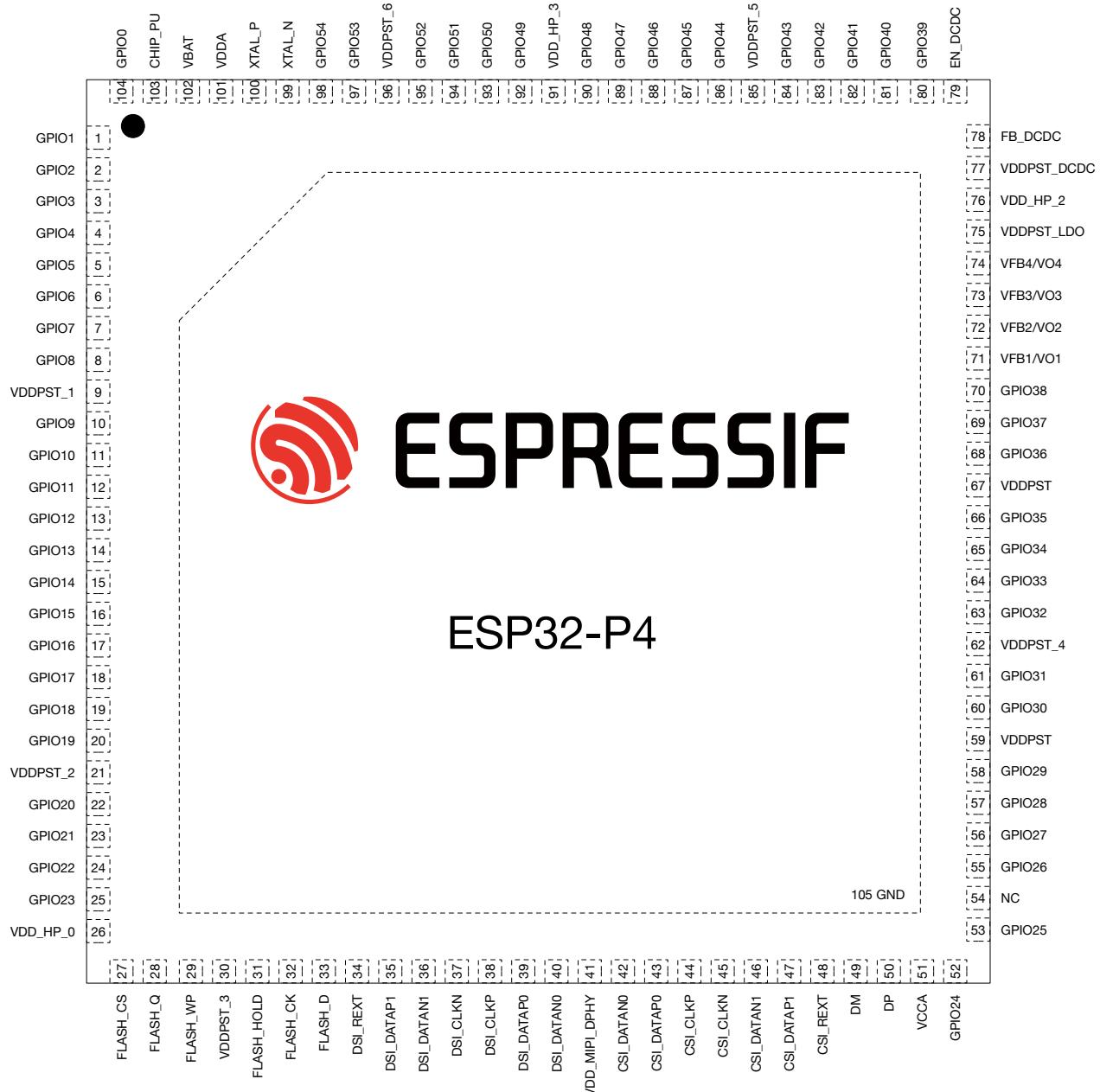

图 2-1. ESP32-P4 管脚布局 (俯视图)

## 2.2 管脚概述

ESP32-P4 芯片集成了多个需要与外界通讯的外设。由于芯片封装尺寸小、管脚数量有限，传送所有输入输出信号的唯一方法是管脚多路复用。管脚多路复用由软件可编程的寄存器控制。还有一些外设比较重要，ESP32-P4 芯片为其设置了专门用于连接这些外设的管脚，如 MIPI DSI 与 MIPI CSI 等。

总体而言，ESP32-P4 芯片的管脚可分为以下几类：

- **IO 管脚**，具有以下预设功能：

- 全部 IO 管脚预设了 **IO MUX 功能** - 见表 2-3 **IO MUX 功能**

- 部分 IO 管脚预设了 **LP IO MUX 功能** - 见表 2-5 **LP IO MUX 功能**

- 部分 IO 管脚预设了 **模拟功能** - 见表 2-7 **模拟功能**

预设功能即每个 IO 管脚直接连接至一组特定的片上组件信号。运行时，可通过映射寄存器配置连接管脚的组件信号。

- **专用数字管脚**，只可用于特定外设，如 flash、MIPI DSI、MIPI CSI 等 - 见表 2-9 **专用数字管脚**

- **模拟管脚**，专用于**模拟功能** - 见表 2-10 **模拟管脚**

- **电源管脚**，为芯片组件和非电源管脚供电 - 见表 2-11 **电源管脚**

表 2-1 管脚概述 简要介绍了所有管脚。更多信息，详见下文相应章节，或参考[附录 A - ESP32-P4 管脚总览](#)。

表 2-1. 管脚概述

| 管脚序号 | 管脚名称     | 管脚类型 | 供电管脚 <sup>2, 3</sup> | 管脚配置 <sup>4</sup> |                      | 管脚功能 <sup>1</sup> |           |    |

|------|----------|------|----------------------|-------------------|----------------------|-------------------|-----------|----|

|      |          |      |                      | 复位时               | 复位后                  | IO MUX            | LP IO MUX | 模拟 |

| 1    | GPIO1    | IO   | VDDPST_1 / VBAT      | -                 | -                    | IO MUX            | LP IO MUX | 模拟 |

| 2    | GPIO2    | IO   | VDDPST_1 / VBAT      | -                 | IE, WPU <sup>5</sup> | IO MUX            | LP IO MUX | 模拟 |

| 3    | GPIO3    | IO   | VDDPST_1 / VBAT      | -                 | IE                   | IO MUX            | LP IO MUX | 模拟 |

| 4    | GPIO4    | IO   | VDDPST_1             | -                 | IE                   | IO MUX            | LP IO MUX | 模拟 |

| 5    | GPIO5    | IO   | VDDPST_1             | -                 | -                    | IO MUX            | LP IO MUX | 模拟 |

| 6    | GPIO6    | IO   | VDDPST_1             | -                 | -                    | IO MUX            | LP IO MUX | 模拟 |

| 7    | GPIO7    | IO   | VDDPST_1             | -                 | -                    | IO MUX            | LP IO MUX | 模拟 |

| 8    | GPIO8    | IO   | VDDPST_1             | -                 | -                    | IO MUX            | LP IO MUX | 模拟 |

| 9    | VDDPST_1 | 电源   | -                    | -                 | -                    | -                 | -         | -  |

| 10   | GPIO9    | IO   | VDDPST_1             | -                 | -                    | IO MUX            | LP IO MUX | 模拟 |

| 11   | GPIO10   | IO   | VDDPST_1             | -                 | -                    | IO MUX            | LP IO MUX | 模拟 |

| 12   | GPIO11   | IO   | VDDPST_1             | -                 | -                    | IO MUX            | LP IO MUX | 模拟 |

| 13   | GPIO12   | IO   | VDDPST_1             | -                 | -                    | IO MUX            | LP IO MUX | 模拟 |

| 14   | GPIO13   | IO   | VDDPST_1             | -                 | -                    | IO MUX            | LP IO MUX | 模拟 |

| 15   | GPIO14   | IO   | VDDPST_1             | -                 | -                    | IO MUX            | LP IO MUX | 模拟 |

| 16   | GPIO15   | IO   | VDDPST_1             | -                 | -                    | IO MUX            | LP IO MUX | 模拟 |

| 17   | GPIO16   | IO   | VDDPST_2             | -                 | -                    | IO MUX            | -         | 模拟 |

| 18   | GPIO17   | IO   | VDDPST_2             | -                 | -                    | IO MUX            | -         | 模拟 |

| 19   | GPIO18   | IO   | VDDPST_2             | -                 | -                    | IO MUX            | -         | 模拟 |

| 20   | GPIO19   | IO   | VDDPST_2             | -                 | -                    | IO MUX            | -         | 模拟 |

| 21   | VDDPST_2 | 电源   | -                    | -                 | -                    | -                 | -         | -  |

| 22   | GPIO20   | IO   | VDDPST_2             | -                 | -                    | IO MUX            | -         | 模拟 |

见下页

表 2-1 - 接上页

| 管脚序号 | 管脚名称          | 管脚类型 | 供电管脚 <sup>2, 3</sup> | 管脚配置 <sup>4</sup> |        | 管脚功能 <sup>1</sup> |           |    |

|------|---------------|------|----------------------|-------------------|--------|-------------------|-----------|----|

|      |               |      |                      | 复位时               | 复位后    | IO MUX            | LP IO MUX | 模拟 |

| 23   | GPIO21        | IO   | VDDPST_2             | -                 | -      | IO MUX            | -         | 模拟 |

| 24   | GPIO22        | IO   | VDDPST_2             | -                 | -      | IO MUX            | -         | 模拟 |

| 25   | GPIO23        | IO   | VDDPST_2             | -                 | -      | IO MUX            | -         | 模拟 |

| 26   | VDD_HP_O      | 电源   | -                    | -                 | -      | -                 | -         | -  |

| 27   | FLASH_CS      | 专用   | VDDPST_3             | -                 | -      | -                 | -         | -  |

| 28   | FLASH_Q       | 专用   | VDDPST_3             | -                 | -      | -                 | -         | -  |

| 29   | FLASH_WP      | 专用   | VDDPST_3             | -                 | -      | -                 | -         | -  |

| 30   | VDDPST_3      | 电源   | -                    | -                 | -      | -                 | -         | -  |

| 31   | FLASH_HOLD    | 专用   | VDDPST_3             | -                 | -      | -                 | -         | -  |

| 32   | FLASH_CK      | 专用   | VDDPST_3             | -                 | -      | -                 | -         | -  |

| 33   | FLASH_D       | 专用   | VDDPST_3             | -                 | -      | -                 | -         | -  |

| 34   | DSI_REXT      | 专用   | VDD_MIPI_DPHY        | -                 | -      | -                 | -         | -  |

| 35   | DSI_DATAP1    | 专用   | VDD_MIPI_DPHY        | -                 | -      | -                 | -         | -  |

| 36   | DSI_DATAN1    | 专用   | VDD_MIPI_DPHY        | -                 | -      | -                 | -         | -  |

| 37   | DSI_CLKN      | 专用   | VDD_MIPI_DPHY        | -                 | -      | -                 | -         | -  |

| 38   | DSI_CLKP      | 专用   | VDD_MIPI_DPHY        | -                 | -      | -                 | -         | -  |

| 39   | DSI_DATAPO    | 专用   | VDD_MIPI_DPHY        | -                 | -      | -                 | -         | -  |

| 40   | DSI_DATANO    | 专用   | VDD_MIPI_DPHY        | -                 | -      | -                 | -         | -  |

| 41   | VDD_MIPI_DPHY | 电源   | -                    | -                 | -      | -                 | -         | -  |

| 42   | CSI_DATANO    | 专用   | VDD_MIPI_DPHY        | -                 | -      | -                 | -         | -  |

| 43   | CSI_DATAPO    | 专用   | VDD_MIPI_DPHY        | -                 | -      | -                 | -         | -  |

| 44   | CSI_CLKP      | 专用   | VDD_MIPI_DPHY        | -                 | -      | -                 | -         | -  |

| 45   | CSI_CLKN      | 专用   | VDD_MIPI_DPHY        | -                 | -      | -                 | -         | -  |

| 46   | CSI_DATAN1    | 专用   | VDD_MIPI_DPHY        | -                 | -      | -                 | -         | -  |

| 47   | CSI_DATAP1    | 专用   | VDD_MIPI_DPHY        | -                 | -      | -                 | -         | -  |

| 48   | CSI_REXT      | 专用   | VDD_MIPI_DPHY        | -                 | -      | -                 | -         | -  |

| 49   | DM            | 专用   | VCCA                 | -                 | -      | -                 | -         | -  |

| 50   | DP            | 专用   | VCCA                 | -                 | -      | -                 | -         | -  |

| 51   | VCCA          | 电源   | -                    | -                 | -      | -                 | -         | -  |

| 52   | GPIO24        | IO   | VDDPST_4             | -                 | -      | IO MUX            | -         | 模拟 |

| 53   | GPIO25        | IO   | VDDPST_4             | -                 | USB_PU | IO MUX            | -         | 模拟 |

| 54   | NC            | -    | -                    | -                 | -      | -                 | -         | -  |

| 55   | GPIO26        | IO   | VDDPST_4             | -                 | -      | IO MUX            | -         | 模拟 |

| 56   | GPIO27        | IO   | VDDPST_4             | -                 | -      | IO MUX            | -         | 模拟 |

| 57   | GPIO28        | IO   | VDDPST_4             | -                 | -      | IO MUX            | -         | -  |

| 58   | GPIO29        | IO   | VDDPST_4             | -                 | -      | IO MUX            | -         | -  |

| 59   | VDDPST        | 电源   | -                    | -                 | -      | -                 | -         | -  |

| 60   | GPIO30        | IO   | VDDPST_4             | -                 | -      | IO MUX            | -         | -  |

| 61   | GPIO31        | IO   | VDDPST_4             | -                 | -      | IO MUX            | -         | -  |

| 62   | VDDPST_4      | 电源   | -                    | -                 | -      | -                 | -         | -  |

| 63   | GPIO32        | IO   | VDDPST_4             | IE                | -      | IO MUX            | -         | -  |

| 64   | GPIO33        | IO   | VDDPST_4             | IE                | -      | IO MUX            | -         | -  |

| 65   | GPIO34        | IO   | VDDPST_4             | IE                | -      | IO MUX            | -         | -  |

| 66   | GPIO35        | IO   | VDDPST_4             | IE, WPU           | -      | IO MUX            | -         | -  |

| 67   | VDDPST        | 电源   | -                    | -                 | -      | -                 | -         | -  |

见下页

表 2-1 - 接上页

| 管脚序号 | 管脚名称        | 管脚类型 | 供电管脚 <sup>2, 3</sup> | 管脚配置 <sup>4</sup> |     | 管脚功能 <sup>1</sup> |           |    |

|------|-------------|------|----------------------|-------------------|-----|-------------------|-----------|----|

|      |             |      |                      | 复位时               | 复位后 | IO MUX            | LP IO MUX | 模拟 |

| 68   | GPIO36      | IO   | VDDPST_4             | IE                | -   | IO MUX            | -         | -  |

| 69   | GPIO37      | IO   | VDDPST_4             | IE                | -   | IO MUX            | -         | -  |

| 70   | GPIO38      | IO   | VDDPST_4             | IE                | -   | IO MUX            | -         | -  |

| 71   | VFB/V01     | 电源   | -                    | -                 | -   | -                 | -         | -  |

| 72   | VFB/V02     | 电源   | -                    | -                 | -   | -                 | -         | -  |

| 73   | VFB/V03     | 电源   | -                    | -                 | -   | -                 | -         | -  |

| 74   | VFB/V04     | 电源   | -                    | -                 | -   | -                 | -         | -  |

| 75   | VDDPST_LDO  | 电源   | -                    | -                 | -   | -                 | -         | -  |

| 76   | VDD_HP_2    | 电源   | -                    | -                 | -   | -                 | -         | -  |

| 77   | VDDPST_DCDC | 电源   | -                    | -                 | -   | -                 | -         | -  |

| 78   | FB_DCDC     | 模拟   | -                    | -                 | -   | -                 | -         | -  |

| 79   | EN_DCDC     | 模拟   | -                    | -                 | -   | -                 | -         | -  |

| 80   | GPIO39      | IO   | VDDPST_5             | -                 | -   | IO MUX            | -         | -  |

| 81   | GPIO40      | IO   | VDDPST_5             | -                 | -   | IO MUX            | -         | -  |

| 82   | GPIO41      | IO   | VDDPST_5             | -                 | -   | IO MUX            | -         | -  |

| 83   | GPIO42      | IO   | VDDPST_5             | -                 | -   | IO MUX            | -         | -  |

| 84   | GPIO43      | IO   | VDDPST_5             | -                 | -   | IO MUX            | -         | -  |

| 85   | VDDPST_5    | 电源   | -                    | -                 | -   | -                 | -         | -  |

| 86   | GPIO44      | IO   | VDDPST_5             | -                 | -   | IO MUX            | -         | -  |

| 87   | GPIO45      | IO   | VDDPST_5             | -                 | -   | IO MUX            | -         | -  |

| 88   | GPIO46      | IO   | VDDPST_5             | -                 | -   | IO MUX            | -         | -  |

| 89   | GPIO47      | IO   | VDDPST_5             | -                 | -   | IO MUX            | -         | -  |

| 90   | GPIO48      | IO   | VDDPST_5             | -                 | -   | IO MUX            | -         | -  |

| 91   | VDD_HP_3    | 电源   | -                    | -                 | -   | -                 | -         | -  |

| 92   | GPIO49      | IO   | VDDPST_6             | -                 | -   | IO MUX            | -         | 模拟 |

| 93   | GPIO50      | IO   | VDDPST_6             | -                 | -   | IO MUX            | -         | 模拟 |

| 94   | GPIO51      | IO   | VDDPST_6             | -                 | -   | IO MUX            | -         | 模拟 |

| 95   | GPIO52      | IO   | VDDPST_6             | -                 | -   | IO MUX            | -         | 模拟 |

| 96   | VDDPST_6    | 电源   | -                    | -                 | -   | -                 | -         | -  |

| 97   | GPIO53      | IO   | VDDPST_6             | -                 | -   | IO MUX            | -         | 模拟 |

| 98   | GPIO54      | IO   | VDDPST_6             | -                 | -   | IO MUX            | -         | 模拟 |

| 99   | XTAL_N      | 模拟   | -                    | -                 | -   | -                 | -         | -  |

| 100  | XTAL_P      | 模拟   | -                    | -                 | -   | -                 | -         | -  |

| 101  | VDDA        | 电源   | -                    | -                 | -   | -                 | -         | -  |

| 102  | VBAT        | 电源   | -                    | -                 | -   | -                 | -         | -  |

| 103  | CHIP_PU     | 模拟   | -                    | -                 | -   | -                 | -         | -  |

| 104  | GPIO00      | IO   | VDDPST_1 / VBAT      | -                 | -   | IO MUX            | LP IO MUX | 模拟 |

| 105  | GND         | 电源   | -                    | -                 | -   | -                 | -         | -  |

1. 加粗功能为默认启动模式下管脚的默认功能，详见章节 3.1 芯片启动模式控制。

2. 供电管脚一栏，由 VDDPST\_1 / VBAT 供电的管脚：

- 供电管脚（VDDPST\_1 或 VBAT）可通过寄存器配置。

3. GPIO24 与 GPIO25 的默认驱动电流为 40 mA。除 GPIO24 与 GPIO25 外，其他管脚的默认驱动电流为 20 mA。

4. 管脚配置一栏为复位时和复位后预设配置缩写：

- IE – 输入使能

- WPU – 内部弱上拉电阻使能

- USB\_PU – USB 上拉电阻使能

- USB 管脚(GPIO24/26 和 GPIO25/27)默认开启 USB 功能, 此时管脚是否上拉由 USB 上拉决定。USB 上拉由 USB\_SERIAL\_JTAG\_DP/DM\_PULLUP 控制, USB 上拉电阻的具体阻值可通过 USB\_SERIAL\_JTAG\_PULLUP\_VALUE 位控制。

- USB 管脚关闭 USB 功能时, 用作普通 GPIO, 默认禁用管脚内部弱上/下拉电阻, 可通过 IO\_MUX\_GPIOx\_FUN\_WPU/WPD 配置。

### 5. EFUSE\_DIS\_PAD\_JTAG 的值为

- 0 (初始默认值), 管脚复位后输入使能, 上拉电阻使能 (IE = 1, WPU = 1)

- 1 管脚复位后输入关闭, 高阻 (IE = 0)

CONFIDENTIAL

## 2.3 IO 管脚

### 2.3.1 IO MUX 功能

IO MUX 能让一个输入/输出管脚连接多个输入/输出信号。ESP32-P4 的每个 IO 管脚可在表 2-3 IO MUX 功能 列出的四个信号 (IO MUX 功能, 即 F0-F3) 中选择, 连接任意一个。

四个信号中:

- 部分源自 GPIO 交换矩阵 (**GPIO0**、**GPIO1** 等)。GPIO 交换矩阵包含内部信号传输线路, 用于映射信号, 能令管脚连接几乎任一外设信号。这种映射虽然灵活, 但可能影响传输信号的速度, 造成延迟。

- 部分直接源自特定外设 (**UOTXD**、**MTCK** 等), 包括 UART0/1、JTAG、SPI2 等 - 详见表 2-2 IO MUX 功能。

表 2-2. 通过 IO MUX 连接的外设信号

| 管脚功能                                                                                                                                                                     | 信号                                                                                                                                                                                    | 描述                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| MTCK<br>MTDO<br>MTDI<br>MTMS                                                                                                                                             | 测试时钟 (Test clock)<br>测试数据输出 (Test data out)<br>测试数据输入 (Test data in)<br>测试模式选择 (Test mode select)                                                                                     | 用于调试功能的 JTAG 接口                                                              |

| SPI2_HOLD_PAD<br>SPI2_CS_PAD<br>SPI2_D_PAD<br>SPI2_CK_PAD<br>SPI2_Q_PAD<br>SPI2_WP_PAD                                                                                   | 暂停 (Hold)<br>片选 (Chip select)<br>数据输入 (Data in)<br>时钟 (Clock)<br>数据输出 (Data out)<br>写保护 (Write protect)                                                                               | 3.3 V SPI2 接口, 既可以配置成主机模式, 又可以配置成从机模式。支持单线, 二线, 四线或八线通信模式 (八线通信模式仅在主机模式下有效)。 |

| SPI2_IO..._PAD<br>SPI2_DQS_PAD                                                                                                                                           | 数据 (Data)<br>数据选通/数据掩码 (Data strobe/data mask)                                                                                                                                        | 八线 SPI 模式下 SPI2 接口的高 4 位数据线接口及 DQS 接口                                        |

| UART...RTS_PAD<br>UART...CTS_PAD<br>UART...TXD_PAD<br>UART...RXD_PAD                                                                                                     | 请求发送 (Request to send)<br>允许发送 (Clear to send)<br>发送数据 (Transmit data)<br>接收数据 (Receive data)                                                                                         | UART0/1 接口                                                                   |

| REF_50M_CLK_PAD                                                                                                                                                          | 50 MHz 参考时钟输出                                                                                                                                                                         | 用于给芯片外部或内部模块提供 50 MHz 时钟                                                     |

| GMAC_PHY_RXDV_PAD<br>GMAC_PHY_RXD..._PAD<br>GMAC_PHY_RXER_PAD<br>GMAC_PHY_TXDV_PAD<br>GMAC_PHY_TXD..._PAD<br>GMAC_PHY_TXER_PAD<br>GMAC_PHY_TXEN_PAD<br>GMAC_RMII_CLK_PAD | 接收数据有效 (Receive data valid)<br>接收数据线 0/1<br>接收错误 (Receive error)<br>发送数据有效 (Transmit data valid)<br>发送数据线 0/1<br>发送错误 (Transmit error)<br>发送使能 (Transmit enable)<br>RMII 接口时钟 (Clock) | GMAC PHY 接口及 RMII 接口                                                         |

| SD1_CDATA..._PAD<br>SD1_CCLK_PAD<br>SD1_CCMD_PAD                                                                                                                         | SD1 卡数据线 0 ~ 7<br>SD1 卡时钟 (Card clock)<br>SD1 卡命令 (Card command)                                                                                                                      | SDIO3.0 接口                                                                   |

表 2-3 IO MUX 功能 列出了管脚的 IO MUX 功能。

表 2-3. IO MUX 管脚功能

| 管脚序号 | IO MUX / GPIO 名称 <sup>2</sup> | IO MUX 功能 <sup>1, 2, 3</sup> |                 |        |       |               |    |                 |        |

|------|-------------------------------|------------------------------|-----------------|--------|-------|---------------|----|-----------------|--------|

|      |                               | F0                           | 类型 <sup>3</sup> | F1     | 类型    | F2            | 类型 | F3              | 类型     |

| 1    | GPIO1                         | GPIO1                        | I/O/T           | GPIO1  | I/O/T | -             | -  | -               | -      |

| 2    | GPIO2                         | MTCK                         | I1              | GPIO2  | I/O/T | -             | -  | -               | -      |

| 3    | GPIO3                         | MTDI                         | I1              | GPIO3  | I/O/T | -             | -  | -               | -      |

| 4    | GPIO4                         | MTMS                         | I0              | GPIO4  | I/O/T | -             | -  | -               | -      |

| 5    | GPIO5                         | MTDO                         | O/T             | GPIO5  | I/O/T | -             | -  | -               | -      |

| 6    | GPIO6                         | GPIO6                        | I/O/T           | GPIO6  | I/O/T | -             | -  | SPI2_HOLD_PAD   | I1/O/T |

| 7    | GPIO7                         | GPIO7                        | I/O/T           | GPIO7  | I/O/T | -             | -  | SPI2_CS_PAD     | I1/O/T |

| 8    | GPIO8                         | GPIO8                        | I/O/T           | GPIO8  | I/O/T | UART0_RTS_PAD | O  | SPI2_D_PAD      | I1/O/T |

| 10   | GPIO9                         | GPIO9                        | I/O/T           | GPIO9  | I/O/T | UART0_CTS_PAD | I1 | SPI2_CK_PAD     | I1/O/T |

| 11   | GPIO10                        | GPIO10                       | I/O/T           | GPIO10 | I/O/T | UART1_TXD_PAD | O  | SPI2_Q_PAD      | I1/O/T |

| 12   | GPIO11                        | GPIO11                       | I/O/T           | GPIO11 | I/O/T | UART1_RXD_PAD | I1 | SPI2_WP_PAD     | I1/O/T |

| 13   | GPIO12                        | GPIO12                       | I/O/T           | GPIO12 | I/O/T | UART1_RTS_PAD | O  | -               | -      |

| 14   | GPIO13                        | GPIO13                       | I/O/T           | GPIO13 | I/O/T | UART1_CTS_PAD | I1 | -               | -      |

| 15   | GPIO14                        | GPIO14                       | I/O/T           | GPIO14 | I/O/T | -             | -  | -               | -      |

| 16   | GPIO15                        | GPIO15                       | I/O/T           | GPIO15 | I/O/T | -             | -  | -               | -      |

| 17   | GPIO16                        | GPIO16                       | I/O/T           | GPIO16 | I/O/T | -             | -  | -               | -      |

| 18   | GPIO17                        | GPIO17                       | I/O/T           | GPIO17 | I/O/T | -             | -  | -               | -      |

| 19   | GPIO18                        | GPIO18                       | I/O/T           | GPIO18 | I/O/T | -             | -  | -               | -      |

| 20   | GPIO19                        | GPIO19                       | I/O/T           | GPIO19 | I/O/T | -             | -  | -               | -      |

| 22   | GPIO20                        | GPIO20                       | I/O/T           | GPIO20 | I/O/T | -             | -  | -               | -      |

| 23   | GPIO21                        | GPIO21                       | I/O/T           | GPIO21 | I/O/T | -             | -  | -               | -      |

| 24   | GPIO22                        | GPIO22                       | I/O/T           | GPIO22 | I/O/T | -             | -  | -               | -      |

| 25   | GPIO23                        | GPIO23                       | I/O/T           | GPIO23 | I/O/T | -             | -  | REF_50M_CLK_PAD | O      |

| 52   | GPIO24                        | GPIO24                       | I/O/T           | GPIO24 | I/O/T | -             | -  | -               | -      |

| 53   | GPIO25                        | GPIO25                       | I/O/T           | GPIO25 | I/O/T | -             | -  | -               | -      |

| 55   | GPIO26                        | GPIO26                       | I/O/T           | GPIO26 | I/O/T | -             | -  | -               | -      |

见下页

表 2-3 - 接上页

| 管脚序号 | IO MUX / GPIO 名称 <sup>2</sup> | IO MUX 功能 <sup>1, 2, 3</sup> |                 |        |       |               |        |                   |    |

|------|-------------------------------|------------------------------|-----------------|--------|-------|---------------|--------|-------------------|----|

|      |                               | F0                           | 类型 <sup>3</sup> | F1     | 类型    | F2            | 类型     | F3                | 类型 |

| 56   | GPIO27                        | GPIO27                       | I/O/T           | GPIO27 | I/O/T | -             | -      | -                 | -  |

| 57   | GPIO28                        | GPIO28                       | I/O/T           | GPIO28 | I/O/T | SPI2_CS_PAD   | I1/O/T | GMAC_PHY_RXDV_PAD | IO |

| 58   | GPIO29                        | GPIO29                       | I/O/T           | GPIO29 | I/O/T | SPI2_D_PAD    | I1/O/T | GMAC_PHY_RXDO_PAD | IO |

| 60   | GPIO30                        | GPIO30                       | I/O/T           | GPIO30 | I/O/T | SPI2_CK_PAD   | I1/O/T | GMAC_PHY_RXD1_PAD | IO |

| 61   | GPIO31                        | GPIO31                       | I/O/T           | GPIO31 | I/O/T | SPI2_Q_PAD    | I1/O/T | GMAC_PHY_RXER_PAD | IO |

| 63   | GPIO32                        | GPIO32                       | I/O/T           | GPIO32 | I/O/T | SPI2_HOLD_PAD | I1/O/T | GMAC_RMII_CLK_PAD | IO |

| 64   | GPIO33                        | GPIO33                       | I/O/T           | GPIO33 | I/O/T | SPI2_WP_PAD   | I1/O/T | GMAC_PHY_TXEN_PAD | O  |

| 65   | GPIO34                        | GPIO34                       | I/O/T           | GPIO34 | I/O/T | SPI2_I04_PAD  | I1/O/T | GMAC_PHY_TXDO_PAD | O  |

| 66   | GPIO35                        | GPIO35                       | I/O/T           | GPIO35 | I/O/T | SPI2_I05_PAD  | I1/O/T | GMAC_PHY_TXD1_PAD | O  |

| 68   | GPIO36                        | GPIO36                       | I/O/T           | GPIO36 | I/O/T | SPI2_I06_PAD  | I1/O/T | GMAC_PHY_TXER_PAD | O  |

| 69   | GPIO37                        | UARTO_RXD_PAD                | O               | GPIO37 | I/O/T | SPI2_I07_PAD  | I1/O/T | -                 | -  |

| 70   | GPIO38                        | UARTO_RXD_PAD                | I1              | GPIO38 | I/O/T | SPI2_DQS_PAD  | O/T    | -                 | -  |

| 80   | GPIO39                        | SD1_CDATA0_PAD               | I1/O/T          | GPIO39 | I/O/T | -             | -      | REF_50M_CLK_PAD   | O  |

| 81   | GPIO40                        | SD1_CDATA1_PAD               | I1/O/T          | GPIO40 | I/O/T | -             | -      | GMAC_PHY_TXEN_PAD | O  |

| 82   | GPIO41                        | SD1_CDATA2_PAD               | I1/O/T          | GPIO41 | I/O/T | -             | -      | GMAC_PHY_RXDO_PAD | O  |

| 83   | GPIO42                        | SD1_CDATA3_PAD               | I1/O/T          | GPIO42 | I/O/T | -             | -      | GMAC_PHY_TXD1_PAD | O  |

| 84   | GPIO43                        | SD1_CCLK_PAD                 | O               | GPIO43 | I/O/T | -             | -      | GMAC_PHY_TXER_PAD | O  |

| 86   | GPIO44                        | SD1_CCMD_PAD                 | I1/O/T          | GPIO44 | I/O/T | -             | -      | GMAC_RMII_CLK_PAD | IO |

| 87   | GPIO45                        | SD1_CDATA4_PAD               | I1/O/T          | GPIO45 | I/O/T | -             | -      | GMAC_PHY_RXDV_PAD | IO |

| 88   | GPIO46                        | SD1_CDATA5_PAD               | I1/O/T          | GPIO46 | I/O/T | -             | -      | GMAC_PHY_RXDO_PAD | IO |

| 89   | GPIO47                        | SD1_CDATA6_PAD               | I1/O/T          | GPIO47 | I/O/T | -             | -      | GMAC_PHY_RXD1_PAD | IO |

| 90   | GPIO48                        | SD1_CDATA7_PAD               | I1/O/T          | GPIO48 | I/O/T | -             | -      | GMAC_PHY_RXER_PAD | IO |

| 92   | GPIO49                        | GPIO49                       | I/O/T           | GPIO49 | I/O/T | -             | -      | GMAC_PHY_TXEN_PAD | O  |

| 93   | GPIO50                        | GPIO50                       | I/O/T           | GPIO50 | I/O/T | -             | -      | GMAC_RMII_CLK_PAD | IO |

| 94   | GPIO51                        | GPIO51                       | I/O/T           | GPIO51 | I/O/T | -             | -      | GMAC_PHY_RXDV_PAD | IO |

| 95   | GPIO52                        | GPIO52                       | I/O/T           | GPIO52 | I/O/T | -             | -      | GMAC_PHY_RXDO_PAD | IO |

| 97   | GPIO53                        | GPIO53                       | I/O/T           | GPIO53 | I/O/T | -             | -      | GMAC_PHY_RXD1_PAD | IO |

见下页

表 2-3 - 接上页

| 管脚序号 | IO MUX / GPIO 名称 <sup>2</sup> | IO MUX 功能 <sup>1, 2, 3</sup> |                 |        |       |    |    |                   |    |

|------|-------------------------------|------------------------------|-----------------|--------|-------|----|----|-------------------|----|

|      |                               | F0                           | 类型 <sup>3</sup> | F1     | 类型    | F2 | 类型 | F3                | 类型 |

| 98   | GPIO54                        | GPIO54                       | I/O/T           | GPIO54 | I/O/T | -  | -  | GMAC_PHY_RXER_PAD | IO |

| 104  | GPIO0                         | GPIO0                        | I/O/T           | GPIO0  | I/O/T | -  | -  | -                 | -  |

<sup>1</sup> 加粗表示默认启动模式下的默认管脚功能，详见章节 3.1 芯片启动模式控制。

<sup>2</sup> 高亮的单元格，详见章节 2.3.4 GPIO 和 LP GPIO 的限制。

<sup>3</sup> 每个 IO MUX 功能 ( $F_n$ ,  $n = 0 \sim 3$ ) 均对应一个“类型”。以下是各个“类型”的含义：

- I - 输入。O - 输出。T - 高阻。

- I1 - 输入；如果该管脚分配了  $F_n$  以外的功能，则  $F_n$  的输入信号恒为 1。

- IO - 输入；如果该管脚分配了  $F_n$  以外的功能，则  $F_n$  的输入信号恒为 0。

### 2.3.2 LP IO MUX 功能

芯片处于 Deep-sleep 模式时，章节 [2.3.1 IO MUX 功能](#) 介绍的 IO 管脚功能无法使用。这正是引入 LP IO MUX 的原因。LP IO 管脚连接 LP 系统，由 VDDPST\_1 或 VBAT 供电，使用 LP IO MUX 能在 Deep-sleep 模式下让一个 LP 输入/输出管脚连接多个输入/输出信号。

LP IO 管脚具有 LP IO MUX 功能，可以

- 用作 LP GPIO (LP\_GPIO0、LP\_GPIO1 等)，连接 LP 处理器

- 或者连接 LP 外设信号 (LP\_UART\_RXD\_PAD、LP\_UART\_RXD\_PAD) - 见表 [2-4 LP IO MUX 功能](#)

表 2-4. 通过 LP IO MUX 连接的 LP 外设信号

| 管脚功能            | 信号                   | 描述         |

|-----------------|----------------------|------------|

| LP_UART_RXD_PAD | 发送数据 (Transmit data) | LP UART 接口 |

| LP_UART_RXD_PAD | 接收数据 (Receive data)  |            |

表 [2-5 LP IO MUX 功能](#) 列出了 LP IO 管脚的 LP 功能。

表 2-5. LP IO MUX 功能

| 管脚序号 | LP IO 名称 <sup>1, 2</sup> | LP IO MUX 功能    |       |           |       |

|------|--------------------------|-----------------|-------|-----------|-------|

|      |                          | F0              | 类型    | F1        | 类型    |

| 1    | LP_GPIO1                 | LP_GPIO1        | I/O/T | LP_GPIO1  | I/O/T |

| 2    | LP_GPIO2                 | LP_GPIO2        | I/O/T | LP_GPIO2  | I/O/T |

| 3    | LP_GPIO3                 | LP_GPIO3        | I/O/T | LP_GPIO3  | I/O/T |

| 4    | LP_GPIO4                 | LP_GPIO4        | I/O/T | LP_GPIO4  | I/O/T |

| 5    | LP_GPIO5                 | LP_GPIO5        | I/O/T | LP_GPIO5  | I/O/T |

| 6    | LP_GPIO6                 | LP_GPIO6        | I/O/T | LP_GPIO6  | I/O/T |

| 7    | LP_GPIO7                 | LP_GPIO7        | I/O/T | LP_GPIO7  | I/O/T |

| 8    | LP_GPIO8                 | LP_GPIO8        | I/O/T | LP_GPIO8  | I/O/T |

| 10   | LP_GPIO9                 | LP_GPIO9        | I/O/T | LP_GPIO9  | I/O/T |

| 11   | LP_GPIO10                | LP_GPIO10       | I/O/T | LP_GPIO10 | I/O/T |

| 12   | LP_GPIO11                | LP_GPIO11       | I/O/T | LP_GPIO11 | I/O/T |

| 13   | LP_GPIO12                | LP_GPIO12       | I/O/T | LP_GPIO12 | I/O/T |

| 14   | LP_GPIO13                | LP_GPIO13       | I/O/T | LP_GPIO13 | I/O/T |

| 15   | LP_UART_RXD_PAD          | LP_UART_RXD_PAD | O     | LP_GPIO14 | I/O/T |

| 16   | LP_UART_RXD_PAD          | LP_UART_RXD_PAD | I1    | LP_GPIO15 | I/O/T |

| 104  | LP_GPIO0                 | LP_GPIO0        | I/O/T | LP_GPIO0  | I/O/T |

<sup>1</sup> 由于 LP 功能通过使用 LP GPIO 编号的 LP GPIO 寄存器配置，此列列出的是 LP GPIO 的名称。

<sup>2</sup> 高亮的单元格，详见章节 [2.3.4 GPIO 和 LP GPIO 的限制](#)。

### 2.3.3 模拟功能

部分 IO 管脚具有模拟功能，可用于任意功耗模式下的模拟外设（如触摸传感器、ADC）。模拟功能连接内部模拟信号，详见表 2-6 模拟功能。

表 2-6. 连接模拟功能的模拟信号

| 管脚功能              | 信号                              | 描述                                 |

|-------------------|---------------------------------|------------------------------------|

| XTAL_32K_N        | 负极性时钟信号 (Negative clock signal) | 连接 ESP32-P4 有源晶振的外部 32 kHz 时钟输入/输出 |

| XTAL_32K_P        | 正极性时钟信号 (Positive clock signal) |                                    |

| TOUCH_CHANNEL...  | 触摸传感器通道 0 ~ 13 信号               | 触摸传感器接口                            |

| ADC..._CHANNEL... | ADC1/2 通道 0 ~ 7 信号              | ADC1/2 接口                          |

| USB1P1_N...       | 全速 USB OTG 2.0 差分信号负极           | 全速 USB OTG 2.0 接口                  |

| USB1P1_P...       | 全速 USB OTG 2.0 差分信号正极           |                                    |

| ANA_COMP...       | PO/P1 电压                        | 模拟电压比较器 0/1 接口                     |

表 2-7 模拟功能 列出了 IO 管脚的模拟功能。

表 2-7. 模拟功能

| 管脚序号 | 模拟 IO 名称 | 模拟功能 <sup>1</sup> |    |

|------|----------|-------------------|----|

|      |          | F0                | F1 |

| 1    | GPIO1    | XTAL_32K_P        | -  |

| 2    | GPIO2    | TOUCH_CHANNEL0    | -  |

| 3    | GPIO3    | TOUCH_CHANNEL1    | -  |

| 4    | GPIO4    | TOUCH_CHANNEL2    | -  |

| 5    | GPIO5    | TOUCH_CHANNEL3    | -  |

| 6    | GPIO6    | TOUCH_CHANNEL4    | -  |

| 7    | GPIO7    | TOUCH_CHANNEL5    | -  |

| 8    | GPIO8    | TOUCH_CHANNEL6    | -  |

| 10   | GPIO9    | TOUCH_CHANNEL7    | -  |

| 11   | GPIO10   | TOUCH_CHANNEL8    | -  |

| 12   | GPIO11   | TOUCH_CHANNEL9    | -  |

| 13   | GPIO12   | TOUCH_CHANNEL10   | -  |

| 14   | GPIO13   | TOUCH_CHANNEL11   | -  |

| 15   | GPIO14   | TOUCH_CHANNEL12   | -  |

| 16   | GPIO15   | TOUCH_CHANNEL13   | -  |

| 17   | GPIO16   | ADC1_CHANNEL0     | -  |

| 18   | GPIO17   | ADC1_CHANNEL1     | -  |

| 19   | GPIO18   | ADC1_CHANNEL2     | -  |

| 20   | GPIO19   | ADC1_CHANNEL3     | -  |

| 22   | GPIO20   | ADC1_CHANNEL4     | -  |

| 23   | GPIO21   | ADC1_CHANNEL5     | -  |

| 24   | GPIO22   | ADC1_CHANNEL6     | -  |

| 25   | GPIO23   | ADC1_CHANNEL7     | -  |

见下页

表 2-7 - 接上页

| 管脚序号 | 模拟IO名称 | 模拟功能 <sup>1</sup> |           |

|------|--------|-------------------|-----------|

|      |        | F0                | F1        |

| 52   | GPIO24 | <b>USB1P1_NO</b>  | -         |

| 53   | GPIO25 | <b>USB1P1_PO</b>  | -         |

| 55   | GPIO26 | USB1P1_N1         | -         |

| 56   | GPIO27 | <b>USB1P1_P1</b>  | -         |

| 92   | GPIO49 | ADC2_CHANNEL2     | -         |

| 93   | GPIO50 | ADC2_CHANNEL3     | -         |

| 94   | GPIO51 | ADC2_CHANNEL4     | ANA_COMPO |

| 95   | GPIO52 | ADC2_CHANNEL5     | ANA_COMPO |

| 97   | GPIO53 | ADC2_CHANNEL6     | ANA_COMP1 |

| 98   | GPIO54 | ADC2_CHANNEL7     | ANA_COMP1 |

| 104  | GPIO00 | XTAL_32K_N        | -         |

<sup>1</sup> 加粗表示默认启动模式下的默认管脚功能，详见章节 [3.1 芯片启动模式控制](#)。

### 2.3.4 GPIO 和 LP GPIO 的限制

ESP32-P4 的所有 IO 管脚都有 GPIO 功能，部分还具有 LP GPIO 功能。不过，这些 IO 管脚是多功能管脚，可以根据需求配置不同的功能，也有一些使用限制，需要特别注意。

本章节的表格中，部分管脚功能有 **高亮** 标记。推荐优先使用没有高亮的 GPIO 或 LP GPIO 管脚。如需更多管脚，请谨慎选择高亮的 GPIO 或 LP GPIO 管脚，避免与重要功能冲突。

**高亮** 的 IO 管脚具有以下重要功能之一：

- **Strapping 管脚** – 启动时逻辑电平需为特定值。详见章节 [3 启动配置项](#)。

- **USB1P1\_N/P** – 默认情况下连接 USB 串口/JTAG 控制器。此类管脚需重新配置，方可用作 GPIO。

- **JTAG 接口** – 通常用于调试功能。详见表 [2-2 IO MUX 功能](#)。要释放这类管脚，可用 USB 串口/JTAG 控制器的 USB1P1\_N/P 功能代替。详见章节 [3.3 JTAG 信号源控制](#)。

- **UART 接口** – 通常用于调试功能。详见表 [2-2 IO MUX 功能](#)。

- **LP UART 接口** – 通常用于低功耗模式下的调试功能。详见表 [2-4 LP IO MUX 功能](#)。

也可参考 [附录 A – ESP32-P4 管脚总览](#)。

## 2.4 专用数字管脚

由于一些外设功能比较重要，因此将一些管脚专用于连接这些外设，如 MIPI DSI，MIPI CSI 等。

表 2-8. 专用外设信号

| 管脚功能                                   | 信号                                                          | 描述 |

|----------------------------------------|-------------------------------------------------------------|----|

| FLASH_CS                               | 片选 (Chip select)                                            |    |

| FLASH_Q                                | 数据输出 (Data output)                                          |    |

| FLASH_WP                               | 写保护 (Write Protect)                                         |    |

| FLASH_HOLD                             | 暂停 (Hold)                                                   |    |

| FLASH_CK                               | 时钟 (Clock)                                                  |    |

| FLASH_D                                | 数据输入 (Data in)                                              |    |

| MIPI DSI PHY 4.02 KΩ EXTERNAL RESISTOR | 4.02 KΩ 外部电阻                                                |    |

| MIPI DSI PHY DATAP...                  | 数据正向通道 0/1 (Data positive channel 0/1)                      |    |

| MIPI DSI PHY DATAN...                  | 数据负向通道 0/1 (Data negative channel 0/1)                      |    |

| MIPI DSI PHY CLKN                      | 时钟负向通道 (Clock negative channel)                             |    |

| MIPI DSI PHY CLKP                      | 时钟正向通道 (Clock positive channel)                             |    |

| MIPI CSI PHY 4.02 KΩ EXTERNAL RESISTOR | 4.02 KΩ 外部电阻                                                |    |

| MIPI CSI PHY DATAP...                  | 数据正向通道 0/1 (Data positive channel 0/1)                      |    |

| MIPI CSI PHY DATAN...                  | 数据负向通道 0/1 (Data negative channel 0/1)                      |    |

| MIPI CSI PHY CLKN                      | 时钟负向通道 (Clock negative channel)                             |    |

| MIPI CSI PHY CLKP                      | 时钟正向通道 (Clock positive channel)                             |    |

| USB2 OTG PHY DM                        | USB 2.0 OTG PHY 数据负向通道 (USB 2.0 OTG PHY Data minus channel) |    |

| USB2 OTG PHY DP                        | USB 2.0 OTG PHY 数据正向通道 (USB 2.0 OTG PHY Data plus channel)  |    |

表 2-9 专用数字管脚 列出了专用数字管脚。

表 2-9. 专用数字管脚

| 管脚序号 | 专用数字管脚     | 功能                                     | 类型    |

|------|------------|----------------------------------------|-------|

| FO   |            |                                        |       |

| 27   | FLASH_CS   | FLASH_CS                               | O     |

| 28   | FLASH_Q    | FLASH_Q                                | I/O/T |

| 29   | FLASH_WP   | FLASH_WP                               | I/O/T |

| 31   | FLASH_HOLD | FLASH_HOLD                             | I/O/T |

| 32   | FLASH_CK   | FLASH_CK                               | O     |

| 33   | FLASH_D    | FLASH_D                                | I/O/T |

| 34   | DSI_REXT   | MIPI DSI PHY 4.02 KΩ EXTERNAL RESISTOR | I/O/T |

| 35   | DSI_DATAP1 | MIPI DSI PHY DATAP1                    | I/O/T |

| 36   | DSI_DATAN1 | MIPI DSI PHY DATAN1                    | I/O/T |

| 37   | DSI_CLKN   | MIPI DSI PHY CLKN                      | I/O/T |

见下页

表 2-9 - 接上页

| 管脚<br>序号 | 专用<br>数字管脚 | F0<br>功能                               | 类型    |

|----------|------------|----------------------------------------|-------|

| 38       | DSI_CLKP   | MIPI DSI PHY CLKP                      | I/O/T |

| 39       | DSI_DATAPO | MIPI DSI PHY DATAPO                    | I/O/T |

| 40       | DSI_DATANO | MIPI DSI PHY DATANO                    | I/O/T |

| 42       | CSI_DATANO | MIPI CSI PHY DATANO                    | I/O/T |

| 43       | CSI_DATAPO | MIPI CSI PHY DATAPO                    | I/O/T |

| 44       | CSI_CLKP   | MIPI CSI PHY CLKP                      | I/O/T |

| 45       | CSI_CLKN   | MIPI CSI PHY CLKN                      | I/O/T |

| 46       | CSI_DATAN1 | MIPI CSI PHY DATAN1                    | I/O/T |

| 47       | CSI_DATAP1 | MIPI CSI PHY DATAP1                    | I/O/T |

| 48       | CSI_REXT   | MIPI CSI PHY 4.02 KΩ EXTERNAL RESISTOR | I/O/T |

| 49       | DM         | USB2 OTG PHY DM                        | I/O/T |

| 50       | DP         | USB2 OTG PHY DP                        | I/O/T |

## 2.5 模拟管脚

表 2-10. 模拟管脚

| 管脚序号 | 管脚名称    | 管脚类型 | 管脚功能                                                    |

|------|---------|------|---------------------------------------------------------|

| 78   | FB_DCDC | —    | 外部 DC/DC 的反馈电源管脚，与外部 DC/DC 的反馈电阻一起调节 VDD_HP_0/1/2/3 的电压 |

| 79   | EN_DCDC | O    | 外部 DC/DC 的使能管脚                                          |

| 99   | XTAL_N  | —    | 连接 ESP32-P4 有源晶振或无源晶振的外部时钟输入/输出。                        |

| 100  | XTAL_P  | —    | P/N 指差分时钟正极/负极端。                                        |

| 103  | CHIP_PU | I    | 高电平：芯片使能（上电）；<br>低电平：芯片关闭（掉电）；<br>注意不能让 CHIP_PU 管脚浮空    |

## 2.6 电源

### 2.6.1 电源管脚

表 2-11 电源管脚 列举了为芯片供电的电源管脚。

表 2-11. 电源管脚

| 管脚序号 | 管脚名称          | 方向 | 电源域 / 其他               | 电源 <sup>1</sup><br>IO 管脚 |

|------|---------------|----|------------------------|--------------------------|

| 9    | VDDPST_1      | 输入 | LP 电源域                 | LP IO                    |

| 21   | VDDPST_2      | 输入 | 数字电源域                  | HP IO                    |

| 26   | VDD_HP_0      | 输入 | 数字电源域                  |                          |

| 30   | VDDPST_3      | 输入 | Flash                  | flash IO                 |

| 41   | VDD_MIPI_DPHY | 输入 | 数字电源域                  | MIPI IO                  |

| 51   | VCCA          | 输入 | 数字电源域                  | 高速 USB IO                |

| 59   | VDDPST        | 输入 | PSRAM                  | PSRAM IO                 |

| 62   | VDDPST_4      | 输入 | 数字电源域                  | HP IO                    |

| 67   | VDDPST        | 输入 | PSRAM                  | PSRAM IO                 |

| 71   | VFB/VO1       | 输出 | 最大输出 0.1 A 电流          |                          |

| 72   | VFB/VO2       | 输出 | 最大输出 0.1 A 电流          |                          |

| 73   | VFB/VO3       | 输出 | 最大输出 0.1 A 电流          |                          |

| 74   | VFB/VO4       | 输出 | 最大输出 0.2 A 电流          |                          |

| 75   | VDDPST_LDO    | 输入 | 模拟电源域, 为 LDO 提供电源      |                          |

| 76   | VDD_HP_2      | 输入 | 数字电源域                  |                          |

| 77   | VDDPST_DCDC   | 输入 | 模拟电源域, 为 DCDC 控制部分提供电源 |                          |

| 85   | VDDPST_5      | 输入 | 数字电源域                  | HP IO                    |

| 91   | VDD_HP_3      | 输入 | 数字电源域                  |                          |

| 96   | VDDPST_6      | 输入 | 数字电源域                  | HP IO                    |

| 101  | VDDA          | 输入 | 模拟电源域                  |                          |

| 102  | VBAT          | 输入 | 模拟电源域或电池电源             |                          |

| 105  | GND           | —  | 外部接地                   |                          |

<sup>1</sup> 电压、电流的推荐值和最大值, 详见章节 5.1 绝对最大额定值 和章节 5.2 建议工作条件。

## 2.7 芯片与 flash 的管脚对应关系

ESP32-P4 需要配合封装外 flash 一起使用，用于存储应用的固件和数据。ESP32-P4 支持以 SPI、Dual SPI、Quad SPI / QPI 等接口模式连接 flash，最大可支持 128 MB flash。

ESP32-P4 内部封装了十六线、1.8 V 工作电压的 PSRAM，但是 PSRAM 的管脚并没有引出芯片。

表 2-12 列出了所有 SPI 模式下芯片与 flash 的管脚对应关系。

更多关于 SPI 控制器的信息，可参考章节 [4.2.2.2 SPI 控制器](#)。

表 2-12. 芯片与封装外 flash 的管脚对应关系

| 管脚序号 | 管脚名称       | Single SPI | Dual SPI | Quad SPI / QPI |

|------|------------|------------|----------|----------------|

| 27   | FLASH_CS   | CS#        | CS#      | CS#            |

| 28   | FLASH_Q    | DO         | DO       | DO             |

| 29   | FLASH_WP   | WP#        | WP#      | WP#            |

| 31   | FLASH_HOLD | HOLD#      | HOLD#    | HOLD#          |

| 32   | FLSH_CK    | CLK        | CLK      | CLK            |

| 33   | FLSHA_D    | DI         | DI       | DI             |

### 3 启动配置项

芯片在上电或硬件复位时，可以通过 Strapping 管脚和 eFuse 位配置如下启动参数，无需微处理器的参与：

- 芯片启动模式

- Strapping 管脚：GPIO35, GPIO36, GPIO37, GPIO38

- ROM 日志打印

- Strapping 管脚：GPIO36

- eFuse 位：EFUSE\_UART\_PRINT\_CONTROL

- JTAG 信号源

- Strapping 管脚：GPIO34

- eFuse 位：EFUSE\_DIS\_PAD\_JTAG、EFUSE\_DIS\_USB\_JTAG 和 EFUSE\_JTAG\_SEL\_ENABLE

上述 eFuse 位的默认值均为 0，也就是说没有烧写过。eFuse 只能烧写一次，一旦烧写为 1，便不能恢复为 0。

上述 strapping 管脚如果没有连接任何电路或连接的电路处于高阻抗状态，则其默认值（即逻辑电平值）取决于管脚内部弱上拉/下拉电阻在复位时的状态。

表 3-1. Strapping 管脚默认配置

| Strapping 管脚 | 默认配置 | 值 |

|--------------|------|---|

| GPIO34       | 浮空   | - |

| GPIO35       | 弱上拉  | 1 |

| GPIO36       | 浮空   | - |

| GPIO37       | 浮空   | - |

| GPIO38       | 浮空   | - |

要改变 strapping 管脚的值，可以连接外部下拉/上拉电阻。如果 ESP32-P4 用作主机 MCU 的从设备，strapping 管脚的电平也可通过主机 MCU 控制。

所有 strapping 管脚都有锁存器。系统复位时，锁存器采样并存储相应 strapping 管脚的值，一直保持到芯片掉电或关闭。锁存器的状态无法用其他方式更改。因此，strapping 管脚的值在芯片工作时一直可读取，strapping 管脚在芯片复位后作为普通 IO 管脚使用。

#### 3.1 芯片启动模式控制

复位释放后，GPIO35 ~ GPIO38 共同决定启动模式。详见表 3-2 芯片启动模式控制。

表 3-2. 系统启动模式控制

| 启动模式                             | GPIO35 | GPIO36 | GPIO37 | GPIO38 |

|----------------------------------|--------|--------|--------|--------|

| SPI Boot                         | 1      | 任意值    | 任意值    | 任意值    |

| Joint Download Boot <sup>2</sup> | 0      | 1      | 任意值    | 任意值    |

<sup>1</sup> 加粗表示默认值和默认配置。

<sup>2</sup> Joint Download Boot 模式下支持以下下载方式：

- USB Download Boot:

- USB-Serial-JTAG Download Boot

- USB 2.0 OTG Download Boot

- UART Download Boot

- SPI Slave Download Boot

## 3.2 ROM 日志打印控制

系统启动过程中，ROM 代码日志可打印至：

- (默认) UARTO 和 USB 串口/JTAG 控制器

- USB 串口/JTAG 控制器

- UARTO

EFUSE\_UART\_PRINT\_CONTROL 和 GPIO36 控制 UARTO ROM 日志打印，如表 3-3 UARTO ROM 日志打印控制所示，

表 3-3. UARTO ROM 日志打印控制

| UARTO ROM 日志打印 | EFUSE_UART_PRINT_CONTROL | GPIO36 |

|----------------|--------------------------|--------|

| 使能             | 0                        | 忽略     |

|                | 1                        | 0      |

|                | 2                        | 1      |

| 关闭             | 1                        | 1      |

|                | 2                        | 0      |

|                | 3                        | 忽略     |

<sup>1</sup> 加粗表示默认值和默认配置。

EFUSE\_DIS\_USB\_SERIAL\_JTAG\_ROM\_PRINT 控制 USB 串口/JTAG 控制器 ROM 日志打印，如表 3-4 USB 串口/JTAG ROM 日志打印控制 所示。

表 3-4. USB 串口/JTAG ROM 日志打印控制

| USB 串口/JTAG ROM 日志打印控制 | EFUSE_DIS_USB_SERIAL_JTAG_ROM_PRINT |

|------------------------|-------------------------------------|

| 使能                     | 0                                   |

| 关闭                     | 1                                   |

<sup>1</sup> 加粗表示默认值和默认配置。

## 3.3 JTAG 信号源控制

在系统启动早期阶段，GPIO34 可用于控制 JTAG 信号源。该管脚没有内部上下拉电阻，strapping 的值必须由不处于高阻抗状态的外部电路控制。

如表 3-5 所示，GPIO34 与 EFUSE\_DIS\_PAD\_JTAG、EFUSE\_DIS\_USB\_JTAG 和 EFUSE\_JTAG\_SEL\_ENABLE 共同控制 JTAG 信号源。

表 3-5. JTAG 信号源控制

| JTAG 信号源             | EFUSE_DIS_PAD_JTAG | EFUSE_DIS_USB_JTAG | EFUSE_JTAG_SEL_ENABLE | GPIO34 |

|----------------------|--------------------|--------------------|-----------------------|--------|

| USB 串口/JTAG 控制器      | 0                  | 0                  | 0                     | 忽略     |

|                      | 0                  | 0                  | 1                     | 1      |

|                      | 1                  | 0                  | 忽略                    | 忽略     |

| JTAG 管脚 <sup>2</sup> | 0                  | 0                  | 1                     | 0      |

|                      | 0                  | 1                  | 忽略                    | 忽略     |

| JTAG 关闭              | 1                  | 1                  | 忽略                    | 忽略     |

<sup>1</sup> 加粗表示默认值和默认配置。

<sup>2</sup> 即 MTDI、MTCK、MTMS 和 MTDO。

## 4 功能描述

### 4.1 系统

本章节描述了芯片操作的核心部分，包括微处理器、系统 DMA、存储器组织结构、系统组件和安全功能。

#### 4.1.1 微处理器和主控

本章节描述了芯片内的核心处理单元及其功能。

##### 4.1.1.1 高性能处理器

ESP32-P4 搭载一个高性能 RISC-V 32 位双核处理器，具有以下特性：

- 五级流水线架构，支持 400 MHz 的时钟频率

- [RV32IMAFc ISA](#) ISA (指令集架构)

- 支持 Zc 扩展 (Zcb, Zcmp, Zcmr)

- 支持自定义 AI 与 DSP 扩展 (Xai)

- 支持自定义硬件循环指令 (Xhwlp)

- 兼容 RISC-V 处理器核局部中断 (CLINT)

- 兼容 RISC-V 处理器核局部中断控制器 (CLIC)

- 支持分支预测功能 BHT, BTB 与 RAS

- 支持最多 3 个硬件断点/观察点

- 支持最多 16 个 PMP/PMA 区域

- 支持两个特权模式：机器模式与用户模式

- 用于调试的 USB/JTAG 接口

- 兼容 RISC-V 调试规范 v0.13

- 支持与 RISC-V Trace 规范 v2.0 兼容的 trace 离线调试

##### 4.1.1.2 处理器指令拓展

ESP32-P4 高性能 32-bit RISC-V 双核处理器支持标准 RV32IMAFcZc 扩展。另外，该处理器还支持自定义扩展指令集 Xhwlp 以及自定义 AI 与 DSP 扩展 Xai，Xhwlp 可降低循环体中的指令数量，Xai 可提高某些 AI 与 DSP 算法的运行效率。

Xai 支持以下特性：

- 新增 8 个 128-bit 位宽通用寄存器

- 128-bit 位宽的向量数据操作，包括乘法、加法、减法、累加、移位、比较等

- 合并数据处理指令与加载/存储运算指令

- 对齐与非对齐 128-bit 带宽的向量数据加载/存储

- 可配置舍入与饱和模式

### 4.1.1.3 低功耗处理器

ESP32-P4 搭载一个低功耗 RISC-V 32 位单核处理器。LP CPU 可以用于在正常工作模式下协助 HP CPU，也可以用于在系统休眠时代替 HP CPU 来执行任务。LP CPU 和 LP 存储器在 Deep-sleep 模式下仍保持工作状态。因此，开发者可以将 LP CPU 的程序存放在 LP 存储器中，使其能够在 Deep-sleep 模式下访问 LP IO、LP 外设、Real-Time 定时器。

LP CPU 具有以下特性：

- 二级流水线架构，支持最高 40 MHz 的时钟频率

- [RV32IMAC](#) ISA (指令集架构)

- 32 个 32 位通用寄存器

- 支持 32 位乘法器、32 位除法器

- 支持中断

- 支持最多 2 个硬件断点/观察点

- 支持 JTAG 调试

- 支持 RISC-V 调试规范 v0.13

- 支持被主 CPU、专用定时器、LP IO 启动

### 4.1.2 系统 DMA

本章节描述了芯片的系统 DMA。

#### 4.1.2.1 通用 DMA 控制器

ESP32-P4 包含两种不同的 GDMA，二者直接访问总线不同，分别为 AHB 和 AXI。分别称为 GDMA-AHB 与 GDMA-AXI。支持以下特性：

- 支持通道数均为 6，包含 3 个发送通道与 3 个接收通道

- 均支持外设与 GDMA 的各个通道之间任意映射绑定

- 均支持通道间固定优先级仲裁和权重仲裁

- 均采用链表方式实现数据收发控制。GDMA-AHB 只可访问片内存储 (SRAM 和 LP\_MEM)，GDMA-AXI 可访问片内与片外存储 (PSRAM)，二者均支持外设与存储及存储与存储之间高速数据传输

- 均支持非对齐地址访问

- GDMA-AHB 支持的外设包括 I3C、UHCI、I2S、ADC、RMT

- GDMA-AXI 支持的外设包括 LCD、CAM、GP-SPI、PARLIO、AES、SHA

#### 4.1.2.2 DW-GDMA 控制器

ESP32-P4 DW-GDMA 控制器可以进行存储到存储、外设到存储、以及存储到外设的数据传输，具有以下特性：

- 2 个 AXI 主机接口

- 4 个通道

- 支持和 CSI、DSI 和 ISP 的硬件握手

- 支持 DMA 做流控或者外设做流控

- 支持首地址非对齐的数据传输

- 支持通道传输暂停、恢复以及提前终止

- 支持寄存器配置通道之间的仲裁优先级

- 支持单块传输

- 支持连续地址、自动重载寄存器配置、影子寄存器以及链表的多块传输

#### 4.1.2.3 2D-DMA 控制器

ESP32-P4 2D-DMA 控制器是专用于二维图像处理的专用 DMA，具有以下特性：

- 1 个 AXI 主机接口

- 支持首地址非对齐的数据传输

- 支持存储到存储、外设到存储、以及存储到外设的数据传输

- 3 个存储到外设通道，2 个外设到存储通道

- 支持 PPA 和 JPEG Codec 外设

- 支持通道优先级、权重配置

- 支持宏块重排序功能

- 支持颜色格式转换功能

#### 4.1.3 存储器组织结构

本章节描述了存储器布局，解释数据的存储、访问和管理方式，以实现高效的操作。

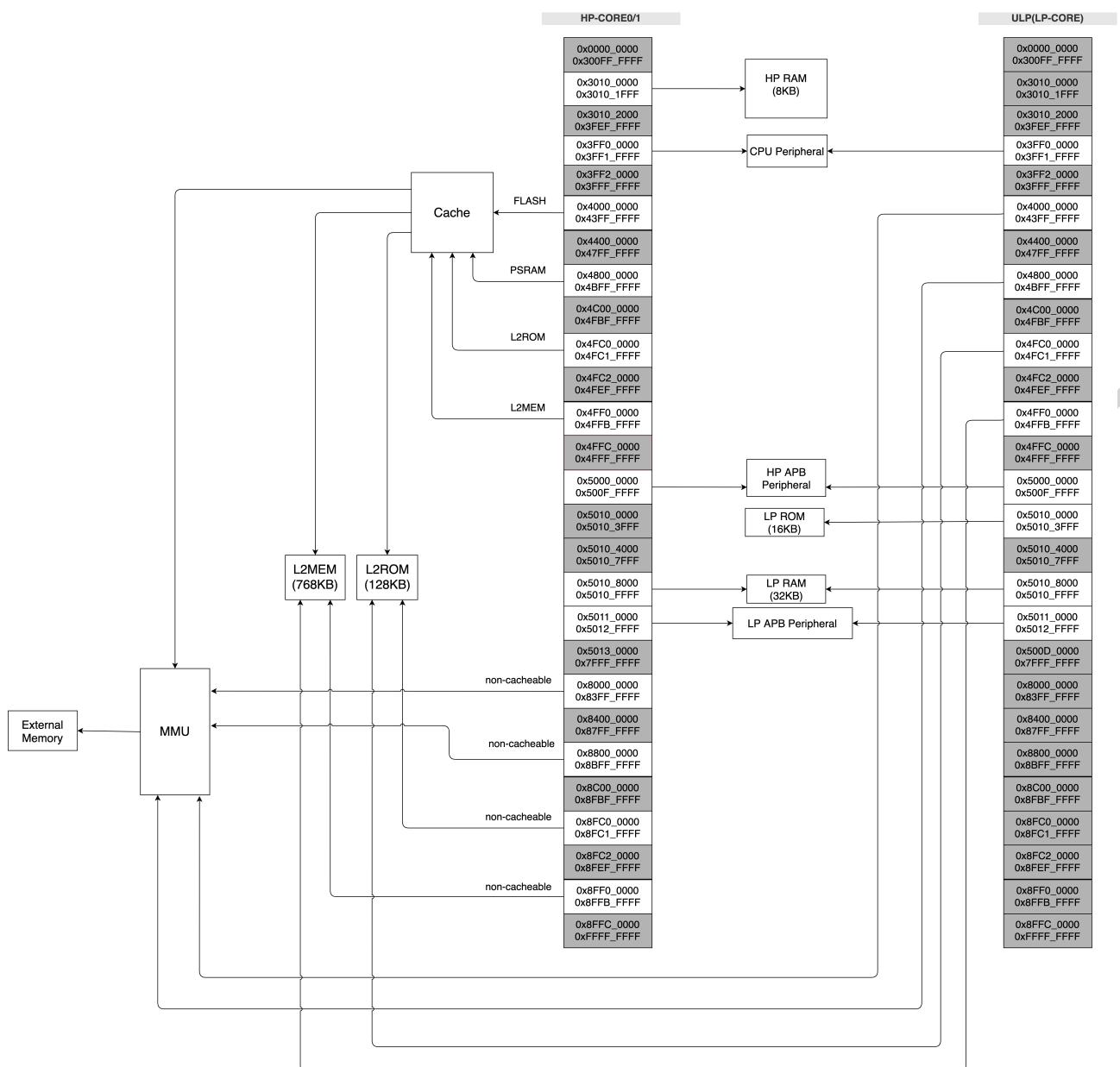

ESP32-P4 的地址映射结构如图 4-1 所示。

图 4-1. 地址映射结构

### 4.1.3.1 系统和存储器

#### 片上存储

ESP32-P4 的片上存储包括：

- **128 KB 的 HP ROM:** 200 MHz, 用于 HP CPU 的程序启动和内核功能调用

- **768 KB 的 HP L2MEM:** 200 MHz, 用于存储 HP CPU 数据和指令

- **16 KB 的 LP ROM:** 40 MHz, 用于 LP CPU 的程序启动和内核功能调用

- **32 KB 的 LP SRAM:** 40 MHz, 用于存储 LP CPU 数据和指令

- **4 Kbit 的 eFuse:** 1792 位保留给用户使用, 用于存储密钥或设备 ID 等信息

- **8 KB 的 TCM:** 400 MHz, 用于 HP CPU 的快速访问

## 外部 flash 和片外 RAM

ESP32-P4 支持以 SPI、Dual SPI、Quad SPI、QPI 等接口形式连接外部 flash；支持以 OPI、HPI 等接口形式连接片外 RAM。

外部 flash 和片外 RAM 可以映射到 CPU 的指令空间、只读数据空间，片外 RAM 还可以映射到 CPU 的数据空间。外部 flash 最大支持 128 MB，片外 RAM 最大支持 64 MB。ESP32-P4 支持基于 XTS-AES 的硬件加解密功能，从而保护开发者 flash 和片外 RAM 中的程序和数据。

通过高速缓存，ESP32-P4 一次最多可以同时有：

- 外部 flash 与片外 RAM 以 64 KB 的块映射到 64 MB 的指令空间。

- 片外 RAM 以 64 KB 的块映射到 64 MB 的数据空间，支持 8 位、16 位、32 位和 128 位读写。外部 flash 也可以以 64 KB 的块映射到 64 MB 只读数据空间，支持 8 位、16 位、32 位和 128 位读取。

### 说明：

芯片启动完成后，软件可以自定义片外 RAM 或 flash 到 CPU 地址空间的映射。

## 4.1.3.2 eFuse 控制器

ESP32-P4 内有一块 4-Kbit 的 eFuse，其中存储着参数内容。eFuse 控制器按照用户配置完成对 eFuse 中各参数中的烧写。eFuse 控制器支持以下特性：

- 4-Kbit 总存储空间，其中 1792 位可供用户使用，如存储加密密钥、用户 ID 等

- 一次性可编程存储

- 烧写保护可配置

- 读取保护可配置

- 多种硬件编码方式保护参数内容

## 4.1.3.3 Cache

ESP32-P4 采用两级 cache 结构，具有以下特性：

- L1 指令 cache 的大小为 16 KB，块大小为 64 B，四路组相联

- L1 数据 cache 的大小为 64 KB，块大小为 64 B，两路组相联，支持 write-through 和 write-back 两种写策略

- L2 cache 的大小为 128 KB/256 KB/512 KB，块大小为 64 B/128 B，八路组相联

- 支持 cacheable 和 non-cacheable 访问

- 支持 pre-load 功能

- 支持 lock 功能

- 支持关键字优先 (critical word first) 和提前重启 (early restart)

## 4.1.4 系统组件

本章节描述了对系统的整体功能和控制起到重要作用的组件。

#### 4.1.4.1 IO MUX 和 GPIO 交换矩阵

ESP32-P4 共有 55 个 GPIO 管脚，通过配置对应的寄存器，可以为这些管脚分配不同的功能。除作为数字信号管脚外，部分 GPIO 管脚也可配置为模拟功能管脚，比如 ADC 等管脚。

所有 GPIO 都可选择内部上拉/下拉，或设置为高阻。GPIO 配置为输入管脚时，可通过读取寄存器获取其输入值。输入管脚也可经设置产生边缘触发或电平触发的 CPU 中断。数字 IO 管脚都是双向、非反相和三态的，包括带有三态控制的输入和输出缓冲器。这些管脚可以复用作其他功能，例如 UART、SPI 等。当芯片低功耗运行时，GPIO 可设定为保持状态。

IO MUX 和 GPIO 交换矩阵用于将信号从外设传输至 GPIO 管脚。两者共同组成了芯片的 IO 控制。利用 GPIO 交换矩阵，可配置外设模块的输入信号来源于任何的 IO 管脚，并且外设模块的输出信号也可连接到任意 IO 管脚。

ESP32-P4 分为 HP 和 LP 两个系统，同时存在 HP 和 LP 两套 IO MUX 和 GPIO 交换矩阵。GPIO0 ~ GPIO15 管脚可以选择由 HP 系统控制还是由 LP 系统控制，默认状态下，GPIO0 ~ GPIO15 管脚由 HP 系统控制。

#### 4.1.4.2 复位和时钟

##### CPU 时钟

CPU 时钟有三种可能的时钟源：

- 外置主晶振时钟

- 内部快速 RC 振荡器时钟（通常为 20 MHz，频率可调节）

- 400 MHz PLL 时钟

应用程序可以从上述三个时钟中选择一个作为时钟源。根据不同的应用程序，被选择的时钟源直接或在分频之后驱动 CPU 时钟。CPU 一旦发生复位后，CPU 的时钟源默认选择为外置主晶振时钟。

##### 说明：

ESP32-P4 必须有外部主晶振时钟才可运行。

##### RTC 时钟

RTC 慢速时钟应用于 RTC 计数器、RTC 看门狗和低功耗控制器，有四种可能的时钟源：

- XTAL32K\_CLK (32 kHz)：外部晶振时钟

- RC\_SLOW\_CLK (默认为 150 kHz)：内部慢速 RC 振荡器时钟

- OSC\_SLOW\_CLK (默认为 32 kHz)：外置低速时钟，通过 XTAL\_32K\_N 输入

- RC32K\_CLK (32 kHz)：内置低速 RC 振荡器时钟

RTC 快速时钟应用于 RTC 外设和传感器控制器，有三种可能的时钟源：

- XTAL\_CLK (40 MHz)：外部主晶振时钟

- RC\_FAST\_CLK (通常为 20 MHz)：内置快速 RC 振荡器时钟，频率可调节

- PLL\_LP\_CLK (8 MHz)：内部 PLL 时钟，参考时钟为 XTAL32K\_CLK

### 音频 PLL 时钟

音频 PLL 时钟是给音频应用专用的高度可配置，低抖动且精确的时钟源，支持 6 ~ 125 MHz 范围内的频率调节。

#### 4.1.4.3 事件任务矩阵

ESP32-P4 带有一个 SOC ETM 外设，该外设包含多个通道 (channel)，每个通道将一个输入的事件 (event) 映射到一个输出的任务 (task)，事件是由外设产生的，任务被外设所接收，具有如下特性：

- 最多支持 50 个事件到任务的映射通道，每个通道连接一个事件和一个任务，并且每个通道都有独立的使能控制

- 每个通道的事件输入以及任务输出可以从所有的事件和任务中任意选择，即支持同一个事件通过多个通道映射到不同的任务，或多个不同的事件通过各自的通道映射到同一个任务

- 能够产生事件、接收任务的外设有：GPIO、LED PWM、通用定时器、看门狗定时器、系统定时器、MCPWM、温度传感器、ADC、I2S、GDMA、2D-DMA 和 PMU

#### 4.1.4.4 低功耗管理

ESP32-P4 采用了先进的电源管理技术，可以在不同的功耗模式之间切换。ESP32-P4 支持的功耗模式包括：

- Active 模式：CPU 处于工作状态，所有外设均可工作。

- Light-sleep 模式：CPU 暂停运行。任何唤醒事件（主机、RTC 定时器或外部中断）都会唤醒芯片。用户可将 CPU（不含 L2MEM）以及大部分外设可根据实际需求配置（见 [ESP32-P4 功能框图](#)）为关闭，进一步降低功耗。

- Deep-sleep 模式：CPU（含 L2MEM）和大部分外设（见 [ESP32-P4 功能框图](#)）都会掉电。低功耗存储器（LP Memory）处于工作状态，低功耗系统的部分外设可根据需求关闭。

#### 4.1.4.5 系统定时器

ESP32-P4 内置 52 位系统定时器，该系统定时器包含两个 52 位的时钟计数器和三个报警比较器，具有以下功能：

- 时钟计数器的频率固定为 16 MHz

- 三个报警比较器根据不同的报警值可产生三个独立的中断

- 两种报警模式：单次特定报警值报警和周期性报警

- 支持设置 52 位的单次特定报警值和 26 位的周期性报警值

- 计数器值重新加载

- 支持当 CPU 暂停或处于 OCD 模式时，时钟计数器也暂停

- 支持输出实时报警的事件 (Event)

#### 4.1.4.6 定时器组

ESP32-P4 内置四个 54 位通用定时器，具有 16 位分频器和 54 位可自动重载的向上/向下计时器。

定时器具有如下功能：

- 16 位时钟预分频器，分频系数为 2 ~ 65536

- 54 位时基计数器可配置成递增或递减

- 可读取时基计数器的实时值

- 暂停和恢复时基计数器

- 可配置的报警产生机制

- 电平触发中断

- 支持输出实时报警的事件 (Event)

- 支持响应 ETM 输入的任务 (Task)，包括：开启/关闭定时器，开启报警功能，读取定时器的实时值，重载定时器值

#### 4.1.4.7 看门狗定时器

ESP32-P4 有三个看门狗定时器：两个定时器组中各一个（称作主系统看门狗定时器，缩写为 MWDT），RTC 模块中一个（称作 RTC 看门狗定时器，缩写为 RWDT）。

在引导加载 flash 固件期间，RWDT 和定时器组 0 中的 MWDT 会自动使能，以检测引导过程中发生的错误，并恢复运行。

看门狗定时器具有如下特性：

- 四个阶段，每个阶段都可配置超时时间。每阶段都可单独配置、使能和关闭。

- 如在某个阶段发生超时，MWDT 会采取中断、CPU 复位和内核复位三种超时动作中的一种，RWDT 会采取中断、CPU 复位、内核复位和系统复位四种超时动作中的一种。

- 保护 32 位超时计数器

- 防止 RWDT 和 MWDT 的配置被误改。

- Flash 启动保护

如果在预定时间内 SPI flash 的引导过程没有完成，看门狗会重启整个主系统。

#### 4.1.4.8 RTC 定时器

ESP32-P4 内置 48 位 LP 定时器，该系统定时器包含一个 48 位的计数器和两个报警比较器，具有以下功能：

- 计数器的频率固定为 RC\_DYN\_SLOW\_CLK 的频率

- 两个报警比较器根据不同的报警值可产生两个独立的中断

- 支持设置 48 位的单次特定报警值

- 支持当 CPU 暂停，XTAL40M\_CLK 开关或系统复位时自动读取计数器值

#### 4.1.4.9 访问权限管理

ESP32-P4 集成 APM (Access Permission Management) 模块实现访问的权限管理。具有以下特性：

- DMA 访问权限管理支持 32 个区域地址范围可配

- APB 访问权限管理支持 2 个区域地址范围可配

- APB 访问在区域管控的基础上，为每个外设地址范围分配了独立的访问权限管控

- 可独立管理 HP CORE0, HP CORE1 和 LP CORE 的 APB 访问权限

- 可独立管理 User Mode 和 Machine Mode 的 APB 访问权限

- 支持异常信息记录

#### 4.1.4.10 LP 信箱控制器

ESP32-P4 包含一个 LP 信箱控制器模块，该模块提供了 16 组 32-bit message。16 组中任意一组 message 的写操作都可分别触发 LP 中断和 HP 中断。

#### 4.1.4.11 欠压监测

ESP32-P4 可以监控供电电源的电压，当电压异常时，能发出中断或者复位。

### 4.1.5 加密和安全组件

本章节描述了集成在芯片中用于保护数据和操作的安全功能。

#### 4.1.5.1 AES 加速器

ESP32-P4 内置 AES（高级加密标准）硬件加速器可使用 AES 算法，完成数据的加解密运算，具有 Typical AES 和 DMA-AES 两种工作模式。整体而言，相比基于纯软件的 AES 运算，AES 硬件加速器能够极大地提高运算速度。

ESP32-P4 支持以下特性：

- Typical AES 工作模式

- AES-128/AES-256 加解密运算，符合标准 [NIST FIPS 197](#)

- DMA-AES 工作模式

- AES-128/AES-256 加解密运算，符合标准 [NIST FIPS 197](#)

- 块（加密）模式，符合标准 [NIST SP 800-38A](#)

- \* ECB (Electronic Codebook)

- \* CBC (Cipher Block Chaining)

- \* OFB (Output Feedback)

- \* CTR (Counter)

- \* CFB8 (8-bit Cipher Feedback)

- \* CFB128 (128-bit Cipher Feedback)

- GCM (Galois/Counter Mode) 模式，符合标准 [NIST SP 800-38D](#)

- 中断发生

#### 4.1.5.2 ECC 加速器

椭圆曲线密码学 (Elliptic Curve Cryptography) 是一种基于椭圆曲线数学的公开密钥加密演算法，其优势在于相对于 RSA 算法，使用较小长度的密钥就能够提供相当等级的加密安全性。

ESP32-P4 ECC 硬件加速器支持对于可选曲线的多种基础运算，用以实现对 ECC 基本运算、衍生算法（如 ECDSA 等算法）的加速。

ESP32-P4 ECC 硬件加速器支持以下功能：

- 支持两种可选 ECC 曲线，即 [FIPS 186-3](#) 中定义的 P-192 和 P-256

- 提供两种可选坐标系，即仿射坐标系和 Jacobian 坐标系

- 提供多种可选点运算，包含点加、点乘和点验证

- 提供基于曲线阶数或模数的多种可选模运算，包含模加、模减、模乘、模除

- 提供计算完成的中断和中断控制

#### 4.1.5.3 HMAC 加速器

如 RFC 2104 中所述，HMAC 模块通过 Hash 算法 SHA-256 和密钥计算得到数据信息的信息认证码 (MAC)。长度为 256 位的 HMAC 密钥存储在 eFuse 的密钥块中，可配置成不能被用户读取，即无法直接从 HMAC 加速器外部访问密钥。主要特性包括：

- 使用标准 HMAC-SHA-256 算法

- 仅支持可配的硬件外设访问 HMAC 计算的 hash 结果（下行模式）

- 兼容挑战-应答身份验证算法

- 支持生成数字签名外设所需的密钥（下行模式）

- 重启软禁用的 JTAG（下行模式）

#### 4.1.5.4 RSA 加速器

RSA 加速器可为多种运用于“RSA 非对称式加密演算法”的高精度计算提供硬件支持，能够极大地降低此类运算的运行时间和软件复杂度。与纯软件 RSA 算法相比，硬件 RSA 加速器的运算速度更快。RSA 加速器还支持多种“运算子长度”，具有很高的灵活性。主要特性包括：

- 大数模幂运算（支持两个加速选项）

- 大数模乘运算，最大可达 4096 位

- 大数乘法运算，运算子最大可达 2048 位

- 多种运算子长度

- 支持在运算完成后触发中断

#### 4.1.5.5 SHA 加速器

SHA（安全哈希算法）硬件加速器可完成 SHA 运算，具有 Typical SHA 和 DMA-SHA 两种工作模式。整体而言，相比基于纯软件的 SHA 运算，SHA 硬件加速器能够极大地提高运算速度。

ESP32-P4 的 SHA 硬件加速器：

- 支持 [FIPS PUB 180-4 规范](#) 中的以下运算标准

- SHA-1 运算

- SHA-224 运算

- SHA-256 运算

- 提供两种工作模式

- Typical SHA 工作模式

- DMA-SHA 工作模式

- 允许插入 (interleaved) 功能 (仅限 Typical SHA 工作模式)

- 允许中断功能 (仅限 DMA-SHA 工作模式)

#### 4.1.5.6 数字签名

数字签名技术使用密码学算法，用于验证消息的真实性和完整性。该技术也可用于向服务器验证设备身份，或验证消息是否经过篡改。

ESP32-P4 包含一个数字签名 (Digital Signature, DS) 模块，可提供硬件加速，高效生成基于 RSA 的数字签名。HMAC 作为密钥导出函数，使用 eFuse 作为输入密钥，输出 DS\_KEY 密钥。随后，数字签名模块使用 DS\_KEY 解密预先加密的参数，计算出签名。上述过程都发生在硬件层面，因此在计算过程中，不论是解密 RSA 参数的密钥，还是用于 HMAC 密钥导出函数的输入密钥，都对用户不可见。

主要特性包括：

- 支持长度最大为 4096 位的 RSA 数字签名密钥

- 支持仅限 DS 读取的加密私钥数据

- 支持 SHA-256 摘要，用于保护私钥数据免遭攻击者篡改

#### 4.1.5.7 椭圆曲线数字签名算法

在密码学中，椭圆曲线数字签名算法 (ECDSA) 是使用椭圆曲线密码对数字签名算法 (DSA) 的模拟。

ESP32-P4 的 ECDSA 加速器可高效安全地计算 ECDSA 签名。ECDSA 加速器可以进行快速计算，同时确保签名过程的保密性，防止信息泄漏。因此，ECDSA 加速器可用于高速加密运算并提供强大的安全保障，它可以保护用户数据的安全，而且不会影响性能。

ESP32-P4 的 ECDSA 加速器：

- 支持签名生成和签认认证

- 支持两种椭圆曲线，即 [FIPS 186-3](#) 中定义的 P-192 和 P-256

- 支持两种哈希算法用于信息的哈希操作，即 [FIPS PUB 180-4 Spec](#) 中定义的 SHA-224 和 SHA-256

- 提供高安全性，其拥有不同工作状态下的动态访问权限控制，防止一切中间数据泄漏而导致的密钥泄露

#### 4.1.5.8 片外存储器加密与解密

ESP32-P4 芯片集成了片外存储器加密与解密模块，使用 [IEEE Std 1619-2007](#) 指定的 XTS-AES 标准算法，为用户存放在片外存储器 (flash) 的应用代码和数据提供了安全保障。用户可以将专有固件、敏感的用户数据（如用来访问私有网络的证书）存放在封装外 flash 中。主要特性包括：

- 使用通用 XTS-AES 算法，符合 [IEEE Std 1619-2007](#)

- 支持手动加密，需要软件参与

- 支持高速自动解密，无需软件参与

- 由寄存器配置、eFuse 参数、启动 (boot) 模式共同决定开启/关闭加解密功能

- 支持可配置的抗 DPA 攻击功能

#### 4.1.5.9 真随机数生成器

ESP32-P4 内置一个真随机数发生器，其生成的 32 位随机数可作为加密等操作的基础。

ESP32-P4 的真随机数发生器通过物理过程而非算法生成真随机数，所有生成的随机数在特定范围内出现的概率完全一样。

#### 4.1.5.10 密钥管理器

ESP32-P4 以密钥管理器作为系统的安全核心，以实现完全安全的密钥存储和部署。密钥管理器利用每一块芯片独有的物理不可复制特性 (PUF)，生成每一块芯片独有的硬件唯一密钥 (HUK)，以此作为一块芯片的信任根。HUK 在每次芯片上电时自动生成，在芯片掉电后消失。密钥管理器以这种方式保证密钥存储和部署的安全。

ESP32-P4 的密钥管理器，将密钥信息（非明文，用于恢复密钥的信息）存储在外部储存器中，能够实现无限制数量的密钥存储、实现动态密钥切换等灵活密钥管理功能。

## 4.2 外设

本章节介绍了芯片上的外设接口，包括扩展芯片功能的通信接口和片上传感器。

### 4.2.1 图像和声音处理

本章节介绍了图像与声音处理的外设。

#### 4.2.1.1 JPEG 图像编解码器

ESP32-P4 包含一个 baseline JPEG 编/解码器，可以将其配置为 JPEG 编码器或 JPEG 解码器使用。

当配置为 JPEG 编码器时，具有以下特性：

- 支持 8-bit 颜色采样

- 支持 RGB888, RGB565, YUV422 和 GRAY 原始图像格式

- 支持 YUV444, YUV422 和 YUV420 待压缩图像格式（即支持原始图像 RGB 到 YUV 的色彩空间转换）

- 支持可配置量化参数

- 静态图像编码可达 4K 分辨率

- MJPEG 编码最大性能为 720p@88fps 或 1080p@34fps（不包括包头传输时间）

当配置为 JPEG 解码器时，具有以下特性：

- 支持 8-bit 颜色采样

- 支持 YUV444, YUV422 和 YUV420 压缩图像格式

- 支持 4 个 8 bit 或 16 bit 精度量化表（由码流包头传输的量化表决定）

- 支持 2 个 DC 和 2 个 AC 哈夫曼编码表（由码流包头传输的哈夫曼编码表决定）

- 支持分辨率是 8 的倍数的压缩图像

- 静态图像解码可达 4K 分辨率

- MJPEG 解码最大性能为 720p@88fps 或 1080p@30fps（不包括包头解码时间）

#### 管脚分配

JPEG 编/解码器无需直接与 IO 进行交互，因此无需分配管脚。

#### 4.2.1.2 图像信号处理器

ESP32-P4 带有一个图像信号处理器 (ISP)，具有如下特性：

- 最大分辨率 1920 x 1080

- 三个输入通道：MIPI CSI、DVP、DW-GDMA

- 输入格式：RAW8、RAW10、RAW12

- 输出格式：RAW8、RGB888、RGB565、YUV422、YUV420

- pipeline 结构：拜尔域降噪 (BF)、去马赛克 (Demosaic)、色彩矩阵 (CCM)、伽马矫正 (Gamma Correction)、锐化 (Edge)、对比度色相饱和度亮度调节 (Contrast/Hue/Saturation/Brightness)、自动曝光统计 (AE)、自动对焦统计 (AF)、白平衡统计 (AWB)、直方图统计 (HIST)

### 管脚分配

图像信号处理器的 CAM 接口通过 GPIO 交换矩阵可配置使用任意 GPIO 管脚。

#### 4.2.1.3 像素处理加速器

ESP32-P4 带有一个像素处理加速器 (PPA)，可实现 SRM 与 BLEND 两大功能，具有如下特性：

- SRM 可实现图像旋转、缩放、镜像

- 输入格式支持 ARGB8888、RGB888、RGB565、YUV420

- 输出格式支持 ARGB8888、RGB888、RGB565、YUV420

- 支持逆时针 90°、180°、270° 旋转

- 支持水平、垂直方向缩放，缩放系数的整数部分为 8-bit，小数部分为 4-bit

- 支持水平、垂直方向镜像

- BLEND 可实现两个相同尺寸的图层叠加

- 输入格式支持 ARGB8888、RGB888、RGB565、L4、L8、A4、A8

- 输出格式支持 ARGB8888、RGB888、RGB565

- 支持两个图层基于 Alpha 通道叠加。若图层不包含 Alpha 通道信息，可通过寄存器配置补全

- 通过设置前景以及背景 color-key 范围实现特殊颜色过滤

### 管脚分配

像素处理加速器无需直接与 IO 进行交互，因此无需分配管脚。

#### 4.2.1.4 Camera-LCD 控制器

ESP32-P4 的 Camera-LCD 控制器包含一个独立的 LCD 控制模块和 Camera (摄像头) 控制模块，可以外接 LCD 和摄像头设备，功能灵活多样。

LCD\_CAM 模块具有以下主要特性：

- 支持以下工作模式：

- LCD 主机发送模式

- Camera 从机接收模式

- Camera 主机接收模式

- 支持同时外接 LCD 和摄像头设备

- 当外接 LCD 设备时，支持：

- 8/16/24 位并行输出模式

- RGB、MOTO6800、I8080 多种 LCD 模式

- LCD 数据可由 GDMA 取自内部或外部存储器

- 当外接摄像头设备（即 DVP 图像传感器）时，支持：

- 8/16 位并行输入模式

- 视频数据可由 GDMA 存入内部或外部存储器

- 支持 LCD\_CAM 接口中断

### 管脚分配

Camera-LCD 控制器的 CAM 和 LCD 接口通过 GPIO 交换矩阵可配置使用任意 GPIO 管脚。

#### 4.2.1.5 H264 编码器

ESP32-P4 包含一个 baseline H264 视频编码器，具有以下特性：

- 支持 YUV420 逐行视频，最大编码性能为 1080p@30fps

- 支持 I 帧和 P 帧

- 支持两种工作模式：GOP 模式和双码流模式（在双码流工作模式下，要编码的两个视频图像序列总带宽不超过 1080p@30fps）

- 支持帧内亮度宏块  $4 \times 4$  分割和  $16 \times 16$  分割

- 支持帧内亮度宏块  $4 \times 4$  分割的所有 9 种预测模式， $16 \times 16$  分割的所有 4 种预测模式

- 支持帧内色度宏块的所有 4 种预测模式

- 支持帧间预测宏块所有的分割模式： $4 \times 4$ ,  $4 \times 8$ ,  $8 \times 4$ ,  $8 \times 8$ ,  $8 \times 16$ ,  $16 \times 8$ ,  $16 \times 16$

- 支持  $1/2$  和  $1/4$  像素精度运动估计

- 支持帧间预测水平方向运动搜索范围  $[-29.75, +16.75]$ ，垂直方向搜索范围  $[-13.75, +13.75]$

- 支持去块滤波的打开和关闭

- 支持上下文自适应变长编码（CAVLC）

- 支持 P-skip 块

- P 切片 (slice) 支持 I 宏块

- 支持亮度和色度分量量化结果缩减操作

- 支持定 QP 以及宏块级码率控制

- 支持 MV 合并功能，可以将各个宏块的 MV 输出到存储器中

- 支持感兴趣区域 (ROI)，最多可以配置 8 个任意位置的矩形 ROI 区域（允许重叠，固定优先级），每个 ROI 区域可以为定 QP 或 QP 偏移，非 ROI 区域可以指定 QP 的偏移

### 管脚分配

H264 编码器无需直接与 IO 进行交互，因此无需分配管脚。

### 4.2.1.6 MIPI 相机串行接口

ESP32-P4 带有一个 MIPI CSI 接口，用于连接 MIPI 接口的摄像头，具有如下特性：

- 符合 MIPI CSI-2 协议

- 使用 DPHY v1.1 版本

- 2-lane x 1.5 Gbps

- 输入格式支持 RGB888、RGB666、RGB565、YUV422、YUV420、RAW8、RAW10、RAW12

#### 管脚分配

MIPI 相机串行接口使用专用数字管脚，管脚序号为 42 ~ 48。

### 4.2.1.7 MIPI 显示串行接口

ESP32-P4 带有一个 MIPI DSI 接口，用于连接 MIPI 接口的显示屏，具有如下特性：

- 符合 MIPI DSI 协议

- 使用 DPHY v1.1 版本

- 2-lane x 1.5 Gbps

- 输入格式支持 RGB888、RGB666、RGB565、YUV422

- 输出格式支持 RGB888、RGB666、RGB565

- 使用 video mode 输出视频流

- 支持输出固定图像 pattern

#### 管脚分配

MIPI 显示串行接口使用专用数字管脚，管脚序号为 34 ~ 40。

## 4.2.2 通讯接口

本章节介绍了芯片与外部设备和网络进行通信和交互的接口。

### 4.2.2.1 UART 控制器

ESP32-P4 有 5 个 UART 接口，即 UART0 ~ 4。5 个 UART 均支持 CTS 和 RTS 信号的硬件流控以及软件流控 (XON 和 XOFF)。

UART0 ~ 4 支持异步通信 (RS232 和 RS485) 和 IrDA，通信速率可达到 5 Mbps。UART0 ~ 4 接口通过共用的 UHCIO 接口（即通用主机控制接口）与 GDMA 相连，可被 GDMA 访问或者 CPU 直接访问。

#### 管脚分配

UART0 接口连接发送和接收信号 (UOTXD 和 UORXD) 的管脚通过 IO MUX 与 GPIO37 ~ GPIO38 和 SPI2 的一组八线接口管脚复用，其硬件流控管脚 (UORTS 和 UOCTS) 通过 IO MUX 与 GPIO8 ~ GPIO9 和 SPI2 接口的一组四线接口管脚复用。

UART1 接口连接发送和接收信号（U1TXD 和 U1RXD）的管脚通过 IO MUX 与 GPIO10 ~ GPIO11 和 SPI2 的一组四线接口管脚复用，其硬件流控管脚（U1RTS 和 U1CTS）通过 IO MUX 与 GPIO12 ~ GPIO13 复用。

其他信号通过 GPIO 交换矩阵可配置使用任意 GPIO 管脚。

### 4.2.2.2 SPI 控制器

ESP32-P4 具有以下 SPI 接口：

- flash SPI，用于连接封装外的 flash

- PSRAM SPI，用于连接封装内 / 封装外的 PSRAM

- SPI2，通用 SPI 控制器

- SPI3，通用 SPI 控制器

- 低功耗 SPI，简称 LP-SPI

#### flash SPI 和 PSRAM SPI 特性

- 可配置为 SPI 存储器模式

- 数据传输以字节为单位

- flash SPI 最高支持四线 SDR 读写操作，PSRAM SPI 最高支持十六线 DDR 读写操作

- 时钟频率可配置，flash SPI SDR 模式下支持的最高时钟频率为 120 MHz，PSRAM SPI DDR 模式下支持的最高时钟频率为 250 MHz

#### SPI2 和 SPI3 特性

- 支持主机和从机模式

- 支持半双工和全双工通信

- 支持 CPU 控制的传输模式和 DMA 控制的传输模式

- SPI2 支持 1-bit SPI、2-bit Dual SPI、4-bit Quad SPI、QPI、8-bit Octal SPI 和 OPI 模式；SPI3 支持 1-bit SPI、2-bit Dual SPI、4-bit Quad SPI 和 QPI 模式

- 时钟频率可配置：主机模式下，时钟频率可达 80 MHz；从机模式下，时钟频率可达 60 MHz

- 数据长度可配置

- 数据位的读写顺序可配置

- 时钟极性和相位可配置

#### LP-SPI 特性

- 用作主机或用作从机

- 支持半双工通信和全双工通信

- 仅支持 CPU 控制的传输类型

- 仅支持 1-bit SPI 数据模式

- 数据长度可配置

### 管脚分配

Flash SPI 使用专用数字管脚，管脚序号为 27 ~ 33。

SPI2 接口的管脚有两组，一组四线接口通过 IO MUX 与 GPIO6 ~ GPIO11 和 UART0/1 接口的管脚复用，另一组八线接口通过 IO MUX 与 GPIO28 ~ GPIO38、UART0 接口的管脚和 EMAC 的第一组 RMII 接口的管脚复用。

SPI3 接口通过 GPIO 交换矩阵可配置使用任意 GPIO 管脚。

### 4.2.2.3 I2C 控制器

ESP32-P4 有两个 I2C 总线接口，根据用户的配置，I2C 总线接口可以用作主机或从机。I2C 接口支持：

- 标准模式 (100 Kbit/s)

- 快速模式 (400 Kbit/s)

- 速度最高可达 800 Kbit/s，但受制于 SCL 和 SDA 上拉强度

- 7 位寻址模式和 10 位寻址模式

- 双寻址模式

- 7 位广播地址

### 管脚分配

I2C 控制器通过 GPIO 交换矩阵可配置使用任意 GPIO 管脚。

### 4.2.2.4 模拟 I2C 主机

该模块是一个专用 I2C 主机，可与部分模拟模块通信，完成对这些模块的参数配置。每个可配置模块中均有一个 I2C 从机，并拥有各自的地址。

### 管脚分配

模拟 I2C 主机接口通过 GPIO 交换矩阵可配置使用任意 GPIO 管脚。

### 4.2.2.5 I3C 控制器

ESP32-P4 带有一个 I3C 主机接口 (Main Master) 和一个 I3C 从机接口。I3C 主机接口具有以下特性：

- 符合 I3C 协议

- 兼容 I2C 模式 (FM, FM+)

- 支持 SDR 模式

- 支持动态地址分配

- 支持 In-Band 中断

- 支持 DMA 传输

I3C 从机接口具有以下特性：

- 有限兼容 I2C 模式

- 支持 SDR 模式

- 可编程静态地址

- 支持动态地址分配

- 支持多种通用命令码 (Common Command Code, CCC)

- 支持 In-Band 中断

#### 管脚分配

I<sup>2</sup>C 控制器主机接口的 SCL 和 SDA (时钟和数据) 信号与 GPIO32 ~ GPIO33 复用，其余信号通过 GPIO 交换矩阵可配置使用任意 GPIO 管脚。

I<sup>2</sup>C 控制器从机接口通过 GPIO 交换矩阵可配置使用任意 GPIO 管脚。

#### 4.2.2.6 I<sup>2</sup>S 控制器

ESP32-P4 有三个标准 I<sup>2</sup>S 接口，可以以主机或从机模式，在全双工或半双工模式下工作，并且可被配置为 I<sup>2</sup>S 串行 8 位、16 位、24 位、32 位的收发数据模式，支持频率从 10 kHz 到 40 MHz 的 BCK 时钟。

I<sup>2</sup>S 接口连接 GDMA 控制器。支持 TDM PCM、TDM MSB 对齐、TDM 标准和 PDM 接口。三个 I<sup>2</sup>S 中，I<sup>2</sup>S0 支持 PDM 转 PCM 输入以及 PCM 转 PDM 输出。

#### 管脚分配

I<sup>2</sup>S 控制器通过 GPIO 交换矩阵可配置使用任意 GPIO 管脚。