# M95M01

# 1 Mbit serial SPI bus EEPROM with high speed clock

Compatible with SPI bus serial interface

(Positive Clock SPI modes)

(POSITIVE CLOCK SPI Modes)

Schmitt trigger inputs for enhanced noise margin

Single supply voltage: 2.8 V to 5.

5 V

8 ms Write time

Status Register

Hardware Protection of the

Status Register

Self-timed programming cycle Adjustable size read-only EEPROM

area

Enhanced ESD Protection More than 1 000 000 Write cycles More than 40-year data retention Packages

ECOPACK® (RoHS compliant)

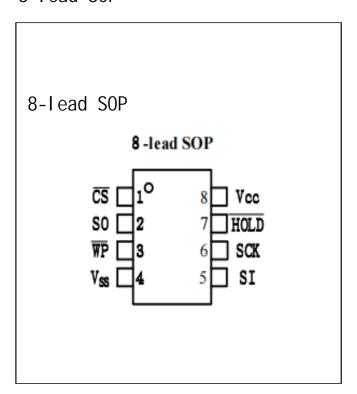

8-Lead SOP

# Examples

| 型号                 | 封装   | 私印              | 工作电压      |

|--------------------|------|-----------------|-----------|

| M95M01-RMN6TP-TUDI | SOP8 | 95 <b>M</b> 01R | 2.8to 5.5 |

www.sztdbdt.com

## **Pin Descriptions**

| Pin Name        | Туре | Functions          |

|-----------------|------|--------------------|

| CS              | I    | Chip Select        |

| SO              | 0    | Serial Data Output |

| WP              | I    | Write Protect      |

| $V_{SS}$        | Р    | Ground             |

| V <sub>CC</sub> | Р    | Power Supply       |

| HOLD            | I    | Hold               |

| SCK             | I    | Serial Clock       |

| SI              | I    | Serial Data Input  |

| Table 1  |                 |      |     |          |  |  |  |

|----------|-----------------|------|-----|----------|--|--|--|

| Position | A               | C    | D   |          |  |  |  |

| 1        | -               | -    | SCK | -        |  |  |  |

| 2        | V <sub>CC</sub> | HOLD | -   | SI       |  |  |  |

| 3        | CS              | -    | -   | $V_{SS}$ |  |  |  |

| 4        | -               | SO   | WP  | -        |  |  |  |

Table 2

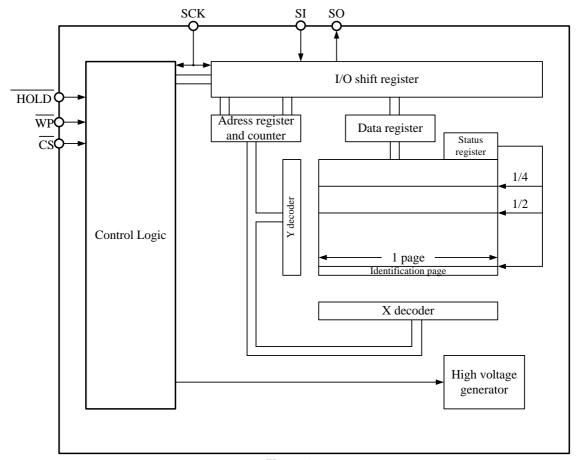

## **Block Diagram**

Figure 1

Serial Data Input (SI):

The SPI Serial data input (SI) is used to serially receive write instructions, addresses or data to the device on the rising edge of the Serial Clock (SCK) input pin.

Serial Data Output (SO): The SPI Serial data output (SO) is used to read data or status from the device on the falling edge of CLK.

Serial Clock (SCK): The SPI Serial Clock Input (SCK) pin provides the timing for serial input and output operations.

Chip Select  $(\overline{CS})$ : The SPI Chip Select  $(\overline{CS})$  pin enables and disables device operation. When  $(\overline{CS})$  is high, the device is deselected and the Serial Data Output (SO) pins are at high impedance. When deselected, the devices power consumption will be at standby levels unless an internal write cycle is in progress. When  $(\overline{CS})$  is brought low, the device will be selected, power consumption will increase to active levels and instructions can be written to and data read from the device. After power-up,  $(\overline{CS})$  must transition from high to low before a new instruction will be accepted.

Hold  $(\overline{HOLD})$ : The  $\overline{HOLD}$  pin allows the device to be paused while it is actively selected. When  $\overline{HOLD}$  is brought low, while  $\overline{CS}$  is low, the SO pin will be at high impedance and signals on the SI and SCK pins will be ignored (don't care). When  $\overline{HOLD}$  is brought high, device operation can resume. The  $\overline{HOLD}$  function can be useful when multiple devices are sharing the same SPI signals. The  $\overline{HOLD}$  pin is active low.

Write Protect ( $\overline{WP}$ ): The Write Protect ( $\overline{WP}$ ) pin is used in conjunction with the Status Register Write Disable (SRWD) Bit to prevent the Status Registers from being written. Write Protect ( $\overline{WP}$ ) pin and Status Register Write Disable (SRWD) Bit enable the device to be put in the Hardware Protected mode (when Status Register Write Disable (SRWD) Bit is set to 1, and Write Protect ( $\overline{WP}$ ) pin is driven low).

#### **Functional Description**

The M95M01device supports the Serial Peripheral Interface (SPI) bus protocol, modes (0,0) and (1,1). The device contains an 8-bit instruction register. The instruction set and associated op-codes are listed in Table 3.

Reading data stored in the M95M01is accomplished by simply providing the READ command and an address. Writing to the M95M01, in addition to a WRITE command, address and data, also requires enabling the device for writing by first setting certain bits in a Status Register, as will be explained later.

After a high to low transition on the  $\overline{\text{CS}}$  input pin, the M95M01will accept any one of the six instruction op-codes listed in Table 3 and will ignore all other possible 8-bit combinations. The communication protocol follows the timing from Figure 14.

The M95M01 features an additional Identification Page (256 bytes) which can be accessed for Read and Write operations when the IPL bit from the Status Register is set to "1". The user can also choose to make the Identification Page permanent write protected by setting the LIP bit from the Status Register (LIP= "1").

| Instruction | Opcode    | Operation                                       |  |

|-------------|-----------|-------------------------------------------------|--|

| WREN        | 0000 0110 | Enable Write Operations                         |  |

| WRDI        | 0000 0100 | Disable Write Operations                        |  |

| RDSR        | 0000 0101 | Read Status Register                            |  |

| WRSR        | 0000 0001 | Write Status Register                           |  |

| READ        | 0000 0011 | Read Data from Memory                           |  |

| WRITE       | 0000 0010 | Write Data to Memory                            |  |

| RDID        | 1000 0011 | Read identification page                        |  |

| WRID        | 1000 0010 | Write identification page                       |  |

| RDLS        | 1000 0011 | Reads the identification page lock status       |  |

| LID         | 1000 0010 | Locks the identification page in read-only mode |  |

Table 3

#### 1. Status Register

The Status Register, as shown in Table 4, contains a number of status and control bits.

| 7    | 6 | 5 | 4 | 3   | 2   | 1   | 0     |

|------|---|---|---|-----|-----|-----|-------|

| SRWD | 0 | 0 | 0 | BP1 | BP0 | WEL | READY |

Table 4

READY: The READY bit indicates whether the device is busy with a write operation. This bit is automatically set to 1 during an internal write cycle, and reset to 0 when the device is ready to accept commands. For the host, this bit is read only.

BP0, BP1: The BP0 and BP1 (Block Protect) bits determine which blocks are currently write protected. They are set by the user with the WRSR command and are non-volatile. The user is allowed to protect a quarter, one half or the entire memory, by setting these bits according to Table 5. The protected blocks then become read-only.

| Status Re | Status Register Bits |                         | Protection               |

|-----------|----------------------|-------------------------|--------------------------|

| BP1       | BP0                  | Array Address Protected | Protection               |

| 0         | 0                    | None                    | No Protection            |

| 0         | 1                    | 18000h-1FFFFh           | Quarter Array Protection |

| 1         | 0                    | 10000h-1FFFFh           | Half Array Protection    |

| 1         | 1                    | 00000h-1FFFFh           | Full Array Protection    |

Table 5

SRWD: The SRWD (Status Register Write Disable) bit acts as an enable for the  $\overline{WP}$  pin. Hardware write protection is enabled when the  $\overline{WP}$  pin is low and the SRWD bit is 1. This condition prevents writing to the status register and to the block protected sections of memory. While hardware write protection is active, only the non-block protected memory can be written. Hardware write protection is disabled when the  $\overline{WP}$  pin is high or the SRWD bit is 0. The SRWD bit,  $\overline{WP}$  pin and WEL bit combine to either permit or inhibit Write operations, as detailed in Table 6.

| SRWD | WP   | WEL | Protected Blocks   | Unprotected Blocks | Status Register |

|------|------|-----|--------------------|--------------------|-----------------|

| 0    | X    | 0   | Protected          | Protected          | Protected       |

| 0    | X    | 1   | Protected Writable |                    | Writable        |

| 1    | Low  | 0   | Protected          | Protected          | Protected       |

| 1    | Low  | 1   | Protected          | Writable           | Protected       |

| X    | High | 0   | Protected          | Protected          | Protected       |

| X    | High | 1   | Protected          | Writable           | Writable        |

Table 6

#### 2. Write Operations

The M95M01device powers up into a write disable state. The device contains a Write Enable Latch (WEL) which must be set before attempting to write to the memory array or to the status register. In addition, the address of the memory location(s) to be written must be outside the protected area, as defined by BP0 and BP1 bits from the status register.

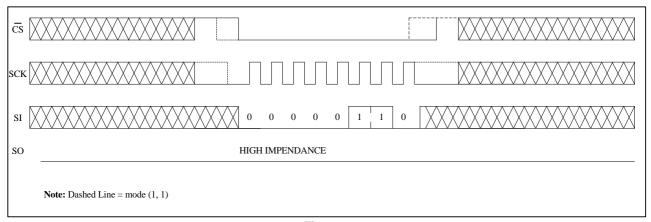

Write Enable and Write Disable: The internal Write Enable Latch and the corresponding Status Register WEL

bit are set by sending the WREN instruction to the M95M01. Care must be taken to take the idput high after the WREN instruction, as otherwise the Write Enable Latch will not be properly set. WREN timing is illustrated in Figure 2. The WREN instruction must be sent prior to any WRITE or WRSR instruction.

Figure 2

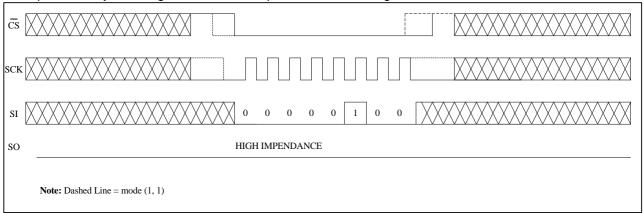

The internal write enable latch is reset by sending the WRDI instruction as shown in Figure 3. Disabling write operations by resetting the WEL bit, will protect the device against inadvertent writes.

Figure 3

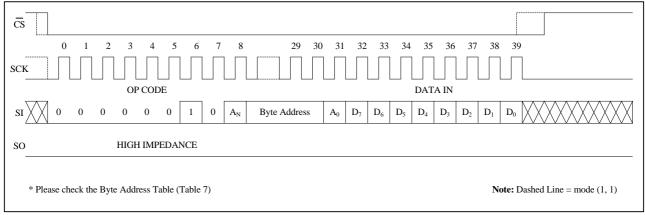

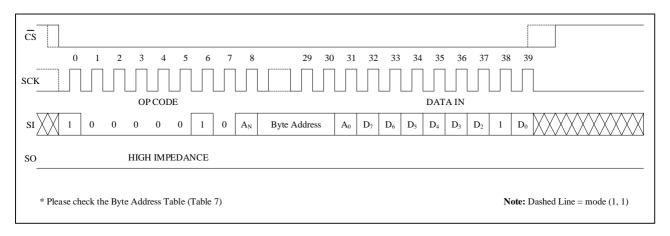

Byte Write: Once the WEL bit is set, the user may execute a write sequence, by sending a WRITE instruction, a 24-bit address and a data byte as shown in Figure 4. Only 17 significant address bits are used by the M95M01. The rest are don't care bits, as shown in Table 7. Internal programming will start after the low to high  $\overline{\text{CS}}$  transition. During an internal write cycle, all commands, except for RDSR (Read Status Register) will be ignored. The  $\overline{\text{READY}}$  bit will indicate if the internal write cycle is in progress ( $\overline{\text{READY}}$  high), or the device is ready to accept commands ( $\overline{\text{READY}}$  low).

Figure 4

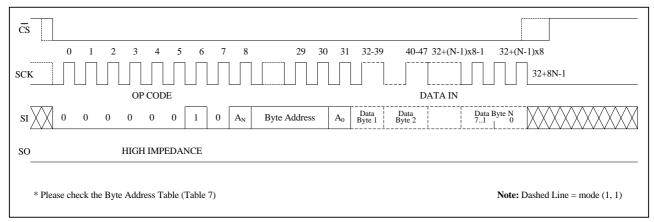

Page Write: After sending the first data byte to the M95M01, the host may continue sending data, up to a total of 256 bytes, according to timing shown in Figure 5. After each data byte, the lower order address bits are automatically incremented, while the higher order address bits (page address) remain unchanged. If during this process the end of page is exceeded, then loading will "roll over" to the first byte in the page, thus possibly overwriting previously loaded data. Following completion of the write cycle, the M95M01is automatically returned to the write disable state.

Figure 5

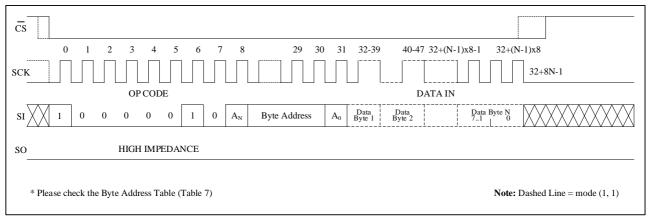

Write Identification Page: The additional 256-byte Identification Page (IP) (256 bytes) is an additional page which can be written and (later) permanently locked in Read-only mode. Writing this page is achieved with the Write Identification Page instruction, according to timing shown in Figure 6. Address bit A10 must be 0, upper address bits are Don't Care, the lower address bits [A7:A0] address bits define the byte address inside the identification page. The byte address must not exceed the 256-byte page boundary.

Figure 6

| Device              | Address Significant Bits | Address Don't Care Bits | # Address Clock Pulses |

|---------------------|--------------------------|-------------------------|------------------------|

| Main Memory Array   | A16 – A0                 | A23 – A17               | 24                     |

| Identification Page | A7 – A0                  | A23 – A8                | 24                     |

Table 7

Write Status Register: The Status Register is written by sending a WRSR instruction according to timing shown in Figure 6. Only bits 2, 3, 4, 5, 6 and 7 can be written using the WRSR command.

Figure 7

Lock Identification Page: The Lock ID instruction permanently locks the Identification Page in read-only mode. Before this instruction can be accepted, a Write Enable (WREN) instruction must have been executed. Lock Identification page is achieved with the Write Identification Page instruction, according to timing shown in Figure 8. Address bit A10 must be 1, all other address bits are Don't Care. The data bit1 must be"1", other bits

The instruction is discarded, and is not executed, under the following conditions:

- If a Write cycle is already in progress,

- If the Block Protect bits (BP1, BP0) = (1,1),

- If a rising edge on Chip Select (CS) happens outside of a byte boundary.

Figure 8

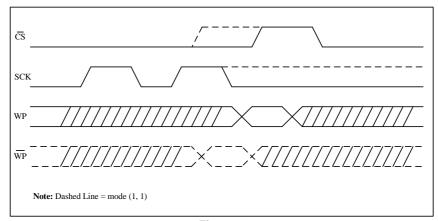

Write Protection: The Write Protect  $(\overline{WP})$  pin can be used to protect the Block Protect bits BP0 and BP1 against being inadvertently altered. When  $\overline{WP}$  is low and the SRWD bit is set to "1", write operations to the Status Register are inhibited.  $\overline{WP}$  going low while  $\overline{CS}$  is still low will interrupt a write to the status register. If the internal write cycle has already been initiated,  $\overline{WP}$  going low will have no effect on any write operation to the Status Register. The  $\overline{WP}$  pin function is blocked when the SRWD bit is set to "0". The  $\overline{WP}$  input timing is shown in Figure 9.

Figure 9

#### 3. Read Operations

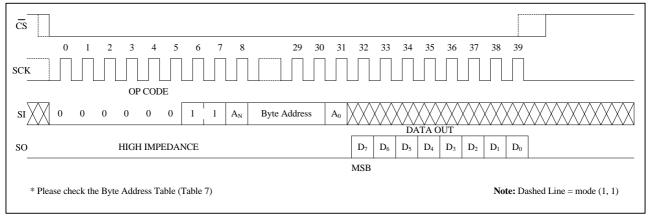

Read from Memory Array: To read from memory, the host sends a READ instruction followed by a 24-bit address (see Table 6 for the number of significant address bits). After receiving the last address bit, the M95M01will respond by shifting out data on the SO pin (as shown in Figure 10). Sequentially stored data can be read out by simply continuing to run the clock. The internal address pointer is automatically incremented to the next higher address as data is shifted out. After reaching the highest memory address, the address counter "rolls over" to the lowest memory address, and the read cycle can be continued indefinitely. The read operation is terminated by taking  $\overline{\text{CS}}$  high.

Figure 10

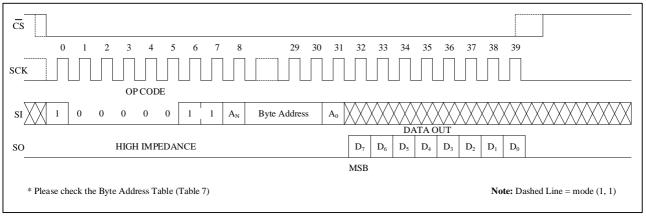

Read Identification Page: Reading the additional 256-byte Identification Page (IP) is achieved using the RDID instruction, according to timing shown in Figure 11. Address bit A10 must be 0, upper address bits are Don't Care, the lower address bits [A7:A0] address bits define the byte address inside the identification page. The byte address must not exceed the 256-byte page boundary.

Figure 11

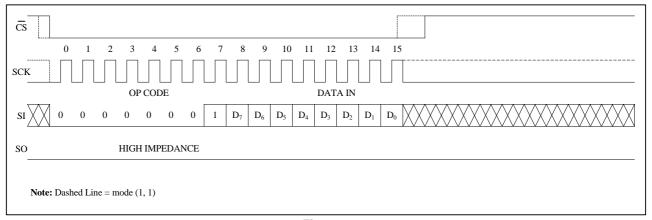

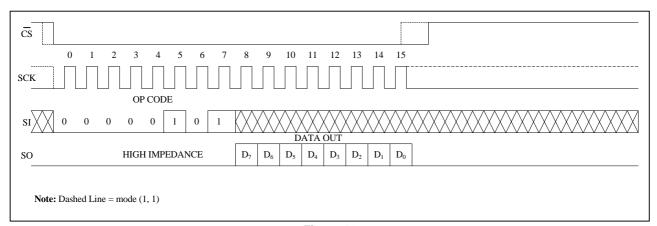

Read Status Register: To read the status register, the host simply sends a RDSR command. After receiving the last bit of the command, the M95M01will shift out the contents of the status register on the SO pin (Figure 12). The status register may be read at any time, including during an internal write cycle.

Figure 12

Read Identification Page Lock Status: To read Identification Page Lock status, the host simply sends a RDLS command, according to timing shown in Figure 11. The address bit A10 must be 1, all other address bits are Don't Care. The Lock bit is the bit0 of the byte read on the SO pin. It is at "1" when the lock is active and at "0" when the lock is not active. The same date byte may be read at any time, including during an internal write cycle.

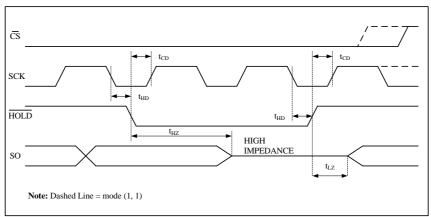

#### 4. Hold Operation

The  $\overline{\text{HOLD}}$  input can be used to pause communication between host and M95M01. To pause,  $\overline{\text{HOLD}}$  must be taken low while SCK is low (Figure 13). During the hold condition the device must remain selected ( $\overline{\text{CS}}$  low). During the pause, the data output pin (SO) is tri–stated (high impedance) and SI transitions are ignored. To resume communication,  $\overline{\text{HOLD}}$  must be taken high while SCK is low.

Figure 13

#### 5. Design Considerations

The M95M01device incorporates Power-On Reset (POR) circuitry which protects the internal logic against powering up in the wrong state. The device will power up into Standby mode after VCC exceeds the POR trigger level and will power down into Reset mode when VCC drops below the POR trigger level. This bi-directional POR behavior protects the device against 'brown-out' failure following a temporary loss of power.

The M95M01device powers up in a write disable state and in a low power standby mode. A WREN instruction must be issued prior to any writes to the device.

After power up, the  $\overline{\text{CS}}$  pin must be brought low to enter a ready state and receive an instruction. After a successful byte/page write or status register write, the device goes into a write disable mode. The  $\overline{\text{CS}}$  input must be set high after the proper number of clock cycles to start the internal write cycle. Access to the memory array during an internal write cycle is ignored and programming is continued. Any invalid op-code will be ignored and the serial output pin (SO) will remain in the high impedance state.

#### **Electrical Characteristics**

#### **Absolute Maximum Stress Ratings:**

| Parameters                                         | Ratings      | Units |

|----------------------------------------------------|--------------|-------|

| Storage Temperature                                | -65 to +150  | °C    |

| Voltage on any Pin with Respect to Ground (Note 1) | -0.5 to +6.5 | V     |

| VESD (HBM)                                         | 8000         | V     |

Table 8

#### Comments:

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

#### **RELIABILITY CHARACTERISTICS (Note 4):**

| Symbol                        | Parameter      | Min       | Units                |

|-------------------------------|----------------|-----------|----------------------|

| N <sub>END</sub> (Notes 2, 3) | Endurance      | 1,000,000 | Program/Erase Cycles |

| TDR                           | Data Retention | 100       | Years                |

Table 9

#### D. C. OPERATING CHARACTERISTICS:

(VCC = 2.8 V to 5.5 V, unless otherwise specified)

| M95M01    | TA =-40°C to +85°C  |                      |

|-----------|---------------------|----------------------|

| M95M01-E1 | TA =-40°C to +105°C | VCC = +2.8V to +5.5V |

| M95M01-E0 | TA =-40°C to +125°C |                      |

| Symbol                    | Parameter                     | Test                                                                                                                                                                                                 | Conditions                              | Min     | Max     | Units |

|---------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|---------|---------|-------|

| I <sub>CCR</sub>          | Supply Current<br>(Read Mode) | Read, SO open                                                                                                                                                                                        | 2.8 V < VCC < 5.5 V                     | -       | 3       | mA    |

| $I_{CCW}$                 | Supply Current (Write Mode)   | Write, $\overline{CS} = VCC$                                                                                                                                                                         | 2.8 V < VCC < 5.5 V                     | -       | 3       | mA    |

| I <sub>SB1</sub> (Note 5) | Standby Current               | $\begin{aligned} &V_{IN} = \text{GND or VCC},\\ &\overline{\text{CS}} = \text{VCC},  \overline{\text{WP}} = \text{VCC},\\ &\text{HOLD} = \text{VCC},\\ &\text{VCC} = 5.5 \text{V} \end{aligned}$     |                                         | -       | 5       | μΑ    |

| I <sub>SB2</sub> (Note 5) | Standby Current               | $\begin{aligned} &V_{IN} = \text{GND or VCC,} \\ &\overline{\text{CS}} = \text{VCC, } \overline{\text{WP}} = \text{GND,} \\ &\text{HOLD} = \text{GND,} \\ &\text{VCC} = 5.5 \text{ V} \end{aligned}$ |                                         | 1       | 5       | μΑ    |

| $I_L$                     | Input Leakage Current         | $V_{IN} = GND$ or VCC                                                                                                                                                                                |                                         | -       | ± 2     | μΑ    |

| I <sub>LO</sub>           | Output Leakage<br>Current     | CS = VCC<br>VOUT = GND or VCC                                                                                                                                                                        |                                         | -       | ± 2     | μΑ    |

| $V_{\rm IL1}$             | Input Low Voltage             | VCC ≥ 2.8V                                                                                                                                                                                           |                                         | -0.45   | 0.3 VCC | V     |

| V <sub>IH1</sub>          | Input High Voltage            | VCC ≥ 2.8 V                                                                                                                                                                                          |                                         | 0.7 VCC | VCC+1   | V     |

| V <sub>OL1</sub>          | Output Low Voltage            | $VCC \geqslant 2.8 \text{ V}, I_{OL} = 3.0 \text{ mA}$                                                                                                                                               |                                         | -       | 0.4     | V     |

| V <sub>OH1</sub>          | Output High Voltage           | VCC ≥ 2.8                                                                                                                                                                                            | $3 \text{ V}, I_{OH} = -1.6 \text{ mA}$ | 0.8 VCC | -       | V     |

Table 10

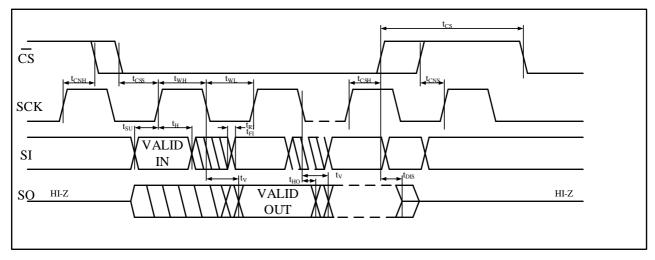

#### A.C. CHARACTERISTICS:

(VCC = 2.8 V to 5.5 V, unless otherwise specified.) (Note 6)

| M95M01-   | TA =-40°C to +85°C  |                        |

|-----------|---------------------|------------------------|

| M95M01-E1 | TA =-40°C to +105°C | VCC = +2.8V  to  +5.5V |

| M95M01-E0 | TA =-40°C to +125°C |                        |

| Symbol                        | Parameter                   | VCC = 2.8  V - 5.5  V |     |       |

|-------------------------------|-----------------------------|-----------------------|-----|-------|

|                               |                             | Min                   | Max | Units |

| f <sub>SCK</sub>              | Clock Frequency             | DC                    | 5   | MHz   |

| t <sub>SU</sub>               | Data Setup Time             | 20                    |     | ns    |

| t <sub>H</sub>                | Data Hold Time              | 20                    |     | ns    |

| t <sub>WH</sub>               | SCK High Time               | 75                    |     | ns    |

| $t_{ m WL}$                   | SCK Low Time                | 75                    |     | ns    |

| t <sub>LZ</sub>               | HOLD to Output Low Z        |                       | 50  | ns    |

| t <sub>RI</sub> (Note 7)      | Input Rise Time             |                       | 2   | μs    |

| t <sub>FI</sub> (Note 7)      | Input Fall Time             |                       | 2   | μs    |

| t <sub>HD</sub>               | HOLD Setup Time             | 0                     |     | ns    |

| t <sub>CD</sub>               | HOLD Hold Time              | 10                    |     | ns    |

| $t_{ m V}$                    | Output Valid from Clock Low |                       | 75  | ns    |

| t <sub>HO</sub>               | Output Hold Time            | 0                     |     | ns    |

| $t_{ m DIS}$                  | Output Disable Time         |                       | 50  | ns    |

| t <sub>HZ</sub>               | HOLD to Output High Z       |                       | 100 | ns    |

| $t_{CS}$                      | CS High Time                | 80                    |     | ns    |

| t <sub>CSS</sub>              | CS Setup Time               | 60                    |     | ns    |

| t <sub>CSH</sub>              | CS Hold Time                | 60                    |     | ns    |

| t <sub>CNS</sub>              | CS Inactive Setup Time      | 60                    |     | ns    |

| t <sub>CNH</sub>              | CS Inactive Hold Time       | 60                    |     | ns    |

| $t_{\mathrm{WPS}}$            | WP Setup Time               | 20                    |     | ns    |

| t <sub>WPH</sub>              | WP Hold Time                | 20                    |     | ns    |

| t <sub>WC</sub> (Notes 9, 10) | Write Cycle Time            |                       | 8   | ms    |

#### Table 11

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

#### POWER-UP TIMING (Notes 7, 8):

| Symbol             | Parameter                          | Max | Units |

|--------------------|------------------------------------|-----|-------|

| $t_{PUR}, t_{PUW}$ | Power-up to Read / Write Operation | 0.1 | ms    |

Table 12

#### Note:

- 1. The DC input voltage on any pin should not be lower than −0.5 V or higher than VCC + 0.5 V. During transitions, the voltage on any pin may undershoot to no less than −1.5 V or overshoot to no more than VCC + 1.5 V, for periods of less than 20 ns.

- 2. Page Mode, VCC = 5 V, 25°C.

- 3. The device uses ECC (Error Correction Code) logic with 6 ECC bits to correct one bit error in 4 data bytes. Therefore, when a single byte has to be written, 4 bytes (including the ECC bits) are re-programmed. It is recommended to write by multiple of 4 bytes located at addresses 4N, 4(N+1), 4(N+2), 4(N+3), in order to benefit from the maximum number of write cycles.

- 4. These parameters are tested initially and after a design or process change that affects the parameter according to appropriate AEC-Q100 and JEDEC test methods.

- 5. When not driven, the  $\overline{WP}$  and  $\overline{HOLD}$  inputs are pulled up to VCC internally. For noisy environments, when the pin is not used, it is recommended the  $\overline{WP}$  and  $\overline{HOLD}$  input to be tied to VCC, either directly or through a resistor.

- 6. AC Test Conditions:

Input Pulse Voltages: 0.3 VCC to 0.7 VCC

Input rise and fall times: ≤ 10 ns

Input and output reference voltages: 0.5 VCC

Output load: current source IoL max/IoH max; CL = 30 pF

- 7. This parameter is tested initially and after a design or process change that affects the parameter.

- 8. tpur and tpuw are the delays required from the time VCC is stable until the specified operation can e initiated.

- 9.  $t_{WC}$  is the time from the rising edge of  $\overline{CS}$  after a valid write sequence to the end of the internal write cycle.

#### **Bus Timing**

Figure 14

#### 重要通知与免责声明

深圳市钍地半导体有限公司将准确可靠地提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、WEB工具、安全信息和其他资源,但不保证任何缺陷,一切以实物测试为准,并且不作任何明示或暗示的保证,包括但不限于对适销性的暗示保证、对特定目的适用的暗示保证或不侵犯任何第三方知识产权的暗示保证。

这些资源旨在为使用钍地产品的熟练开发人员提供支持:(1)为您的应用程序选择合适的产品;(2)设计、验证和测试您的应用程序;(3)确保您的应用程序符合适用的标准和任何其他安全、安保或其他要求;(4)钍地和钍地标志是钍地半导体的注册商标。所有商标均为其各自所有者的财产;(5)有关更改详情,请查阅任何修订文件中包含的修订历史记录。资源可能会在不通知的情况下更改。我公司将不对使用此产品及其使用而导致的专利或第三方知识产权的侵权负责。

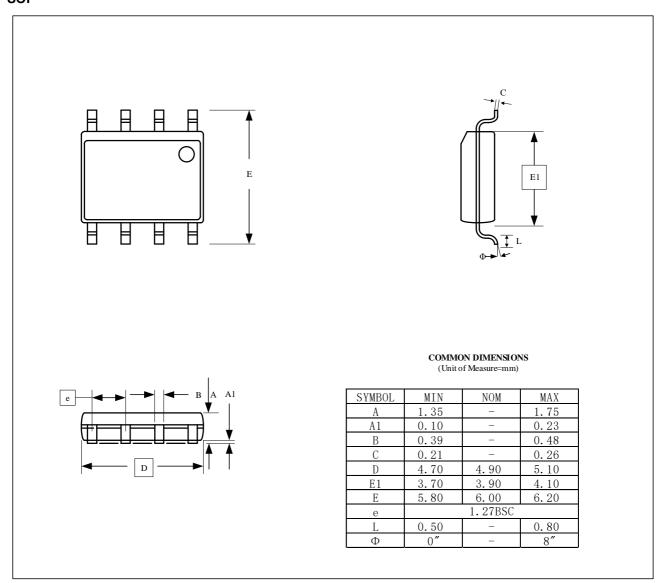

#### **Package Information**

#### SOP

#### 重要通知与免责声明

深圳市钍地半导体有限公司将准确可靠地提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、WEB工具、安全信息和其他资源,但不保证任何缺陷,一切以实物测试为准,并且不作任何明示或暗示的保证,包括但不限于对适销性的暗示保证、对特定目的适用的暗示保证或不侵犯任何第三分上只想供去技术(1),他们应用程度选择会适知来只要是

这些资源旨在为使用钍地产品的熟练开发人员提供支持:(1)为您的应用程序选择合适的产品;(2)设计、验证和测试您的应用程序;(3)确保您的应用程序符合适用的标准和任何其他安全、安保或其他要求;(4)钍地和钍地标志是钍地半导体的注册商标。所有商标均为其各自所有者的财产;(5)有关更改详情,请查阅任何修订文件中包含的修订历史记录。资源可能会在不通知的情况下更改。我公司将不对使用此产品及其使用而导致的专利或第三方知识产权的侵权负责。