# MSKSEMI 美森科

**ESD**

1/5

TSS

MOV

GDT

PLED

## PTVSHC2EN5VB-MS

**Product specification**

#### **Features**

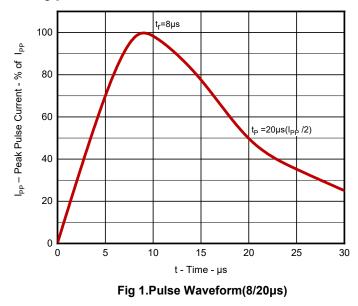

- 1500W Peak pulse power per line (tP = 8/20μs)

- DFN1610-2L package

- Response time is typically < 1 ns</li>

- Protect one I/O or power line

- Low clamping Voltage

- RoHS compliant

- Transient protection for data lines to IEC 61000-4-2(ESD) ±30KV(air), ±30KV(contact);

IEC 61000-4-4 (EFT) 40A (5/50ns)

## **Mechanical Characteristics**

- Lead finish:100% matte Sn(Tin)

- Mounting position: Any

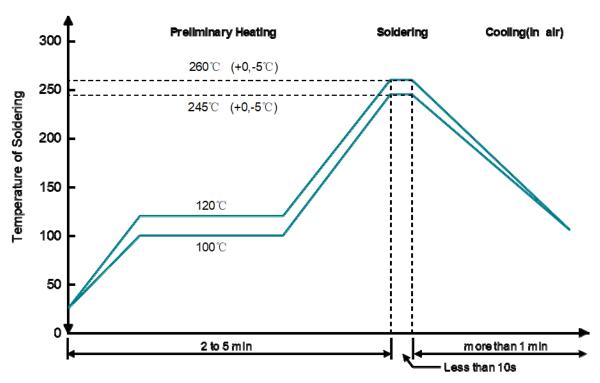

- Qualified max reflow temperature:260 ℃

- Pure tin plating: 7 ~ 17 um

- Pin flatness:≤3mil

- Device meets MSL3 requirement

## **Applications**

- Cell phone handsets and accessories

- Personal digital assistants (PDA's)

- Notebooks, desktops, and servers

- Portable instrumentation

- Cordless phones

- Digital cameras

- Peripherals

- MP3 players

### **Reference News**

| PACKAGE OUTLINE | Circuit Diagram | Marking |

|-----------------|-----------------|---------|

|                 |                 | D5N     |

| DFN1610-2       |                 |         |

## **Electronics Parameter**

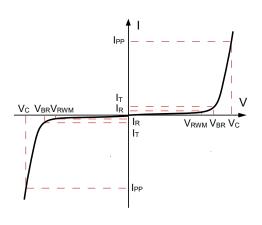

| Symbol          | Parameter                          |  |

|-----------------|------------------------------------|--|

| Vrwm            | Peak Reverse Working Voltage       |  |

| lr              | Reverse Leakage Current @ VRWM     |  |

| V <sub>BR</sub> | Breakdown Voltage @ I⊤             |  |

| н               | Test Current                       |  |

| IPР             | Maximum Reverse Peak Pulse Current |  |

| Vc              | Clamping Voltage @ IPP             |  |

| Ppp             | Peak Pulse Power                   |  |

| CJ              | Junction Capacitance               |  |

## Electrical characteristics per line@25℃ (unless otherwise specified)

| Parameter                    | Symbol          | Conditions                   | Min. | Тур. | Max. | Units |

|------------------------------|-----------------|------------------------------|------|------|------|-------|

| Peak Reverse Working Voltage | VRWM            |                              |      |      | 5.0  | V     |

| Breakdown Voltage            | V <sub>BR</sub> | lt = 1mA                     | 5.5  |      | 7.5  | V     |

| Reverse Leakage Current      | lR              | V <sub>RWM</sub> = 5V T=25°С |      |      | 1.0  | μA    |

| Clamping Voltage             | Vc              | IPP=20A tp = 8/20µs          |      | 8.0  | 10   | V     |

| Clamping Voltage             | Vc              | IPP=50A tp = 8/20µs          |      | 9.0  | 11   | V     |

| Clamping Voltage             | Vc              | IPP=100A tP = 8/20µs         | 3    | 10   | 12   | V     |

| Clamping Voltage             | Vc              | Ipp=140A tp = 8/20μs         | 3    | 11   | 13   | ٧     |

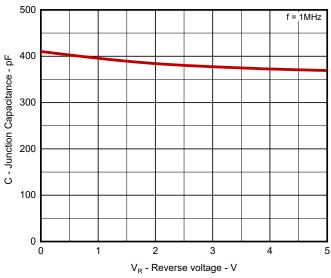

| Junction Capacitance         | Cj              | V <sub>R</sub> =0V f = 1MHz  |      | 400  | 450  | pF    |

### Note

## Absolute maximum rating@25℃

| Rating                                      | Symbol               | Value        | Units      |

|---------------------------------------------|----------------------|--------------|------------|

| Peak Pulse Power (t <sub>P</sub> = 8/20μs ) | P <sub>PP</sub>      | 1500         | W          |

| Peak Pulse Current ( t⊳ = 8/20µs )          | <b> </b> PP          | 140          | А          |

| Lead Soldering Temperature                  | TL                   | 260 (10 sec) | $^{\circ}$ |

| Junction and Storage Temperature Range      | Т <sub>J</sub> ,Тsтg | -55~+150     | °C         |

<sup>1)</sup> VRWM is the maximum reverse working voltage, or reverse stand-off voltage. ESD can protect signal line properly within its rated voltage. If the signal line's voltage is over VRWM, ESD will change to other state.

V<sub>c</sub> - Clamping Voltage - V

12

8

0 **L**

20

40

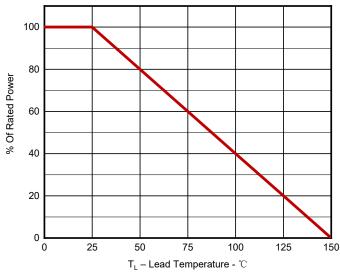

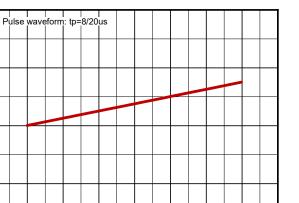

## **Typical Characteristics**

100

120

140

160

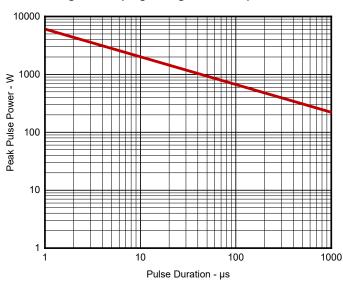

Fig 2.Power Derating Curve

$\label{eq:Ipp-Peak pulse current-A}$  Fig 3. Clamping voltage vs. Peak pulse current

Fig 4. Capacitance vs. Reveres voltage

Fig 5. Non Repetitive Peak Pulse Power vs. Pulse time

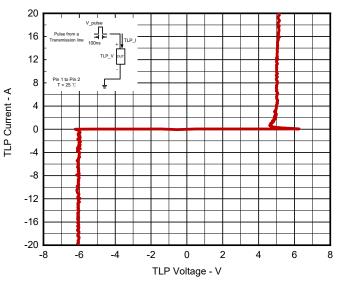

Fig 6. TLP Measurement

## **Solder Reflow Recommendation**

Remark: Pb free for 260°C; Pb for 245°C.

## **PCB Design**

For TVS diodes a low-ohmic and low-inductive path to chassis earth is absolutely mandatory in order to achieve good ESD protection. Novices in the area of ESD protection should take following suggestions to heart:

- Do not use stubs, but place the cathode of the TVS diode directly on the signal trace.

- Do not make false economies and save copper for the ground connection.

- Place via holes to ground as close as possible to the anode of the TVS diode.

- Use as many via holes as possible for the ground connection.

- Keep the length of via holes in mind! The longer the more inductance they will have.

### **PACKAGE MECHANICAL DATA**

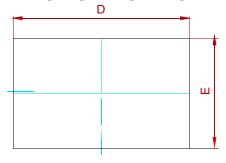

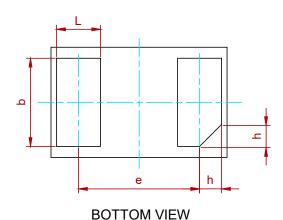

**TOP VIEW**

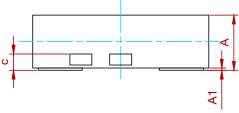

SIDE VIEW

| Cumhal | Dimensions in Millimeters |      |      |  |

|--------|---------------------------|------|------|--|

| Symbol | Min.                      | Тур. | Max. |  |

| A      | 0.45                      | 0.50 | 0.55 |  |

| A1     | 0.00                      | 0.02 | 0.05 |  |

| С      | 0.15 Ref.                 |      |      |  |

| b      | 0.75                      | 0.80 | 0.85 |  |

| L      | 0.35                      | 0.40 | 0.45 |  |

| D      | 1.55                      | 1.60 | 1.65 |  |

| E      | 0.95                      | 1.00 | 1.05 |  |

| е      | 1.10 BSC                  |      |      |  |

| h      | 0.20 Ref.                 |      |      |  |

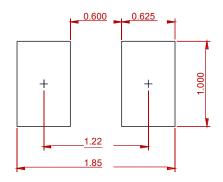

### Recommend PCB Layout (Unit: mm)

#### Notes:

This recommended land pattern is for reference purposes only. Please consult your manufacturing group to ensure your PCB design guidelines are met.

## **REEL SPECIFICATION**

| P/N             | PKG       | QTY  |

|-----------------|-----------|------|

| PTVSHC2EN5VB-MS | DFN1610-2 | 3000 |

## **Attention**

- Any and all MSKSEMI Semiconductor products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your MSKSEMI Semiconductor representative nearest you before using any MSKSEMI Semiconductor products described or contained herein in such applications.

- MSKSEMI Semiconductor assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all MSKSEMI Semiconductor products described or contained herein.

- Specifications of any and all MSKSEMI Semiconductor products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer'sproducts or equipment.

- MSKSEMI Semiconductor. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with someprobability. It is possiblethat these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents—or events cannot occur. Such measures include but are not limited to protective circuits anderror prevention circuitsfor safedesign, redundant design, and structural design.

- In the event that any or all MSKSEMI Semiconductor products (including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from theauthorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of MSKSEMI Semiconductor.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. MSKSEMI Semiconductor believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. Whendesigning equipment, refer to the "Delivery Specification" for the MSKSEMI Semiconductor productthat you intend to use.