#### **Features**

- 8 simultaneously sampled inputs

- Single 5V analog supply and 1.71 to 5V VDRIVE

- 16bit ADC with 200 kSPS on all channels

- Bipolar inputs ranges: ±10V, ±5V

- · Analog input clamp protection

- 1 MΩ analog input impedance

- · On chip reference and buffer

- · On chip oversampling digital filter

- · SPI compatible interface

- Temperature range: -40°C to 125°C

- Package: LQFP10X10-64

### **Applications**

- Power line monitor

- Power line protection relays

- Motor control

- Data acquisition system (DAS)

- · Industrial Automation and controls

### **Description**

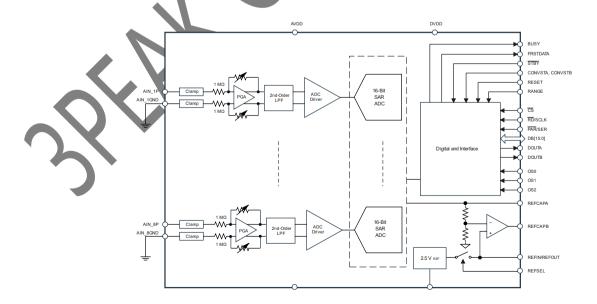

TSAFE516 is a 16bit, 8-channel simultaneous sampling, successive approximation (SAR) ADC. Each channel has a complete analog front end, as well as an ADC operating at 200 kSPS per channel. The analog front end features input clamp, a programmable gain amplifier (PGA) with high input impedance of  $1M\Omega_{\rm J}$  low pass filter and ADC input driver.

The device features an internal precision reference with buffer to driver the ADC. A digital interface supports serial, parallel and parallel byte communication, which can be used with varies host controllers.

The TSAFE516 can accept ±10V or ±5V true bipolar inputs with a single 5V supply. Also the high input impedance allows direct connection to transformers or other sensors without external driver circuits.

The zero latency conversion with high performance also makes the device suitable for industrial automation and control applications.

### Typical Application Circuit

### **Product Family Table**

| Order Number       | Input Range(V) | Package      |  |

|--------------------|----------------|--------------|--|

| TSAFE5160SI08-QP7R | ±10, ±5        | LQFP10X10-64 |  |

### **Table of Contents**

| Features                                | <i>'</i> |

|-----------------------------------------|----------|

| Applications                            |          |

| Description                             |          |

| Typical Application Circuit             |          |

| Product Family Table                    |          |

| Revision History                        |          |

| Pin Configuration and Functions         |          |

| Pin Functions                           | į        |

| Specifications                          |          |

| Absolute Maximum Ratings                |          |

| ESD, Electrostatic Discharge Protection | 9        |

| Recommended Operating Conditions        |          |

| Thermal Information                     |          |

| Electrical Characteristics              | 10       |

| Detailed Description                    | 1        |

| Overview                                | 15       |

| Feature Description                     | 1        |

| Device Functional Modes                 | 16       |

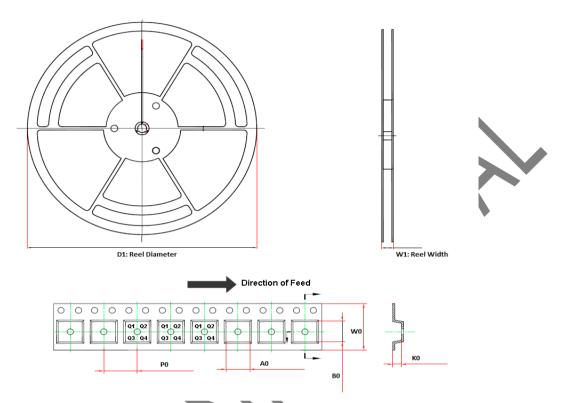

| Tape and Reel Information               | 22       |

| Package Outline Dimensions              |          |

| LQFP10X10-64                            |          |

### **Revision History**

| Date       | Revision  | Notes                       |

|------------|-----------|-----------------------------|

| 2021-11-15 | Rev.Pre.0 | Pre-Release Version         |

| 2022-6-20  | Rev.Pre.1 | Update diagram and EC table |

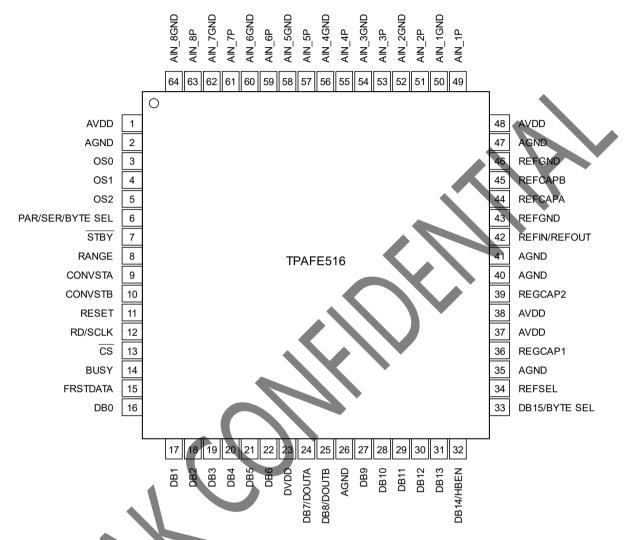

### **Pin Configuration and Functions**

### **Pin Functions**

|    |                  |      | ·                                                                        |

|----|------------------|------|--------------------------------------------------------------------------|

| NO | PIN<br>Name      | TYPE | DESCRIPTION                                                              |

| 1_ | AVDD             | Р    | Analog supply pin.                                                       |

| 2  | AGND             | Р    | Analog ground pin.                                                       |

| 3  | OS0              | DI   | Oversampling control pin.                                                |

| 4  | OS1              | DI   | Oversampling control pin.                                                |

| 5  | OS2              | DI   | Oversampling control pin.                                                |

|    |                  |      |                                                                          |

| 6  | PAR/SER/BYTE SEL | DI   | Control pin to select serial, parallel, or parallel byte interface mode. |

| 7  | STBY             | DI   | Control pin to select standby or shutdown mode, active low.              |

|            |                      |    | Multi-function logic input pin:                                                       |

|------------|----------------------|----|---------------------------------------------------------------------------------------|

|            |                      |    | When STBY is low, this pin selects between the standby and shutdown modes.            |

| 8          | RANGE                | DI | When STBY is high, this pin selects input range ±10V or ±5V.                          |

|            |                      |    | Active high logic input to control start of conversion for first half count of device |

|            |                      |    | input                                                                                 |

| 9          | CONVSTA              | DI | channels                                                                              |

|            |                      |    | Active high logic input to control start of conversion for second half count of       |

|            |                      |    | device input                                                                          |

| 10         | CONVSTB              | DI | channels                                                                              |

| 11         | RESET                | DI | Active high logic input to reset the device digital logic                             |

|            |                      |    | Multi formation lands instead with                                                    |

|            |                      |    | Multi-function logic input pin:                                                       |

| 40         | <del>DD</del> (0011) | 5  | this pin is active-low ready input pin in parallel and parallel byte interface;       |

| 12         | RD/SCLK              | DI | this pin is clock input pin in serial interface mode.                                 |

| 13         | <u>CS</u>            | DI | Active low logic input chip-select signal                                             |

| 14         | BUSY                 | DO | Active high digital output indicating ongoing conversion                              |

| 15         | FRSTDATA             | DO | Active high digital output indicating data read back from channel 1 of the device     |

| 16         | DB0                  | DO | Data output DB0 (LSB) in parallel interface mode                                      |

| 17         | DB0<br>DB1           | DO | Data output DB0 (LSB) in parallel interface mode                                      |

| 18         | DB1                  | DO | Data output DB2 in parallel interface mode                                            |

| 19         | DB2                  | DO | Data output DB3 in parallel interface mode                                            |

| -          | DB3<br>DB4           | DO | Data output DB4 in parallel interface mode                                            |

| 20         | DB4<br>DB5           | DO | Data output DB4 in parallel interface mode                                            |

|            |                      |    |                                                                                       |

| 22         | DB6                  | DO | Data output DB6 in parallel interface mode                                            |

| 23         | DVDD                 | Р  | Digital supply pin; decouple with AGND on pin 26.                                     |

|            |                      |    | Multi-function logic output pin:                                                      |

|            |                      |    | this pin is data output DB7 in parallel and parallel byte interface mode;             |

| 24         | DB7/DOUTA            | DO | this pin is a data output pin in serial interface mode.                               |

|            |                      |    |                                                                                       |

|            |                      |    | Multi-function logic output pin:                                                      |

|            |                      |    | this pin is data output DB8 in parallel and parallel byte interface mode;             |

| <b>2</b> 5 | DB8/DOUTB            | DO | this pin is a data output pin in serial interface mode.                               |

| 26         | AGND                 | Р  | Analog ground pin.                                                                    |

| 27         | DB9                  | DO | Data output DB9 in parallel interface mode                                            |

| 28         | DB10                 | DO | Data output DB10 in parallel interface mode                                           |

| 29         | DB11                 | DO | Data output DB11 in parallel interface mode                                           |

| 30         | DB12                 | DO | Data output DB12 in parallel interface mode                                           |

| 31         | DB13                 | DO | Data output DB13 in parallel interface mode                                           |

|    |               |                                       | Multi-function legis input or output pio.                                                                                        |

|----|---------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

|    |               |                                       | Multi-function logic input or output pin:                                                                                        |

|    |               |                                       | this pin is data output DB14 in parallel interface mode;                                                                         |

| 32 | DB14/HBEN     | DO                                    | this pin is a control input pin for byte selection (high or low) in parallel byte interface mode                                 |

| 32 | DB14/FIDEN    | ЪО                                    | interface mode                                                                                                                   |

|    |               |                                       | Multi-function logic input or output pin:                                                                                        |

|    |               |                                       | this pin is data output DB15 (MSB) in parallel interface mode;                                                                   |

| 33 | DB15/BYTE SEL | DO                                    | this pin is an active high control input pin to enable parallel byte interface mode.                                             |

| 34 | REFSEL        | DI                                    | Active high logic input to enable the internal reference                                                                         |

| 35 | AGND          | Р                                     | Analog ground pin.                                                                                                               |

|    |               |                                       | Output pin 1 for the internal voltage regulator; decouple separately to AGND                                                     |

| 36 | REGCAP1       | AO                                    | using a 1-µF capacitor. Typical 4V.                                                                                              |

| 37 | AVDD          | Р                                     | Analog supply pin.                                                                                                               |

| 38 | AVDD          | Р                                     | Analog supply pin.                                                                                                               |

|    |               |                                       | Output pin 2 for the internal voltage regulator, decouple separately to AGND                                                     |

| 39 | REGCAP2       | AO                                    | using a 1-µF capacitor. Typical 4V.                                                                                              |

| 40 | AGND          | Р                                     | Analog ground pin.                                                                                                               |

| 41 | AGND          | Р                                     | Analog ground pin.                                                                                                               |

|    |               |                                       | This air cate as an internal 2.5% as the cate of turban DEFCEL is high.                                                          |

|    |               |                                       | This pin acts as an internal 2.5V reference output when REFSEL is high;                                                          |

| 42 | REFIN/REFOUT  | AIO                                   | this pin functions as input pin for the external reference when REFSEL is low;                                                   |

| 42 | REFIN/REFOUT  | AIO                                   | decouple with REFGND on pin 43 using a 10-µF capacitor.  Reference GND pin. This pin must be shorted to the analog GND plane and |

|    |               |                                       | decoupled with                                                                                                                   |

| 43 | REFGND        | Р                                     | REFIN/REFOUT on pin 42 using a 10-µF capacitor.                                                                                  |

| 43 | KEI GND       | -                                     | The inviter of the pin 42 using a 10-pin capacitor.                                                                              |

|    |               | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | Reference amplifier output pins. This pin must be shorted to REFCAPB and                                                         |

| 44 | REFCAPA 👞     | AO                                    | decoupled to AGND using a low ESR, 10-µF ceramic capacitor. Typical 4V.                                                          |

|    |               |                                       |                                                                                                                                  |

|    |               |                                       | Reference amplifier output pins. This pin must be shorted to REFCAPA and                                                         |

| 45 | REFCAPB       | AO                                    | decoupled to AGND using a low ESR, 10-µF ceramic capacitor. Typical 4V.                                                          |

|    | AVI           |                                       | Reference GND pin. This pin must be shorted to the analog GND plane and                                                          |

|    |               | _                                     | decoupled with                                                                                                                   |

| 46 | REFGND        | Р                                     | REFIN/REFOUT on pin 42 using a 10-μF capacitor.                                                                                  |

| 47 | AGND          | Р                                     | Analog ground pin.                                                                                                               |

| 48 | AVDD          | Р                                     | Analog supply pin.                                                                                                               |

| 49 | AIN_1P        | AIO                                   | Analog input channel 1: positive input                                                                                           |

| 50 | AIN_1GND      | AIO                                   | Analog input channel 1: negative input                                                                                           |

| 51 | AIN_2P        | AIO                                   | Analog input channel 2: positive input                                                                                           |

| 52 | AIN_2GND      | AIO                                   | Analog input channel 2: negative input                                                                                           |

| 53 | AIN_3P        | AIO                                   | Analog input channel 3: positive input                                                                                           |

| 54 | AIN_3GND      | AIO                                   | Analog input channel 3: negative input                                                                                           |

| 55 | AIN_4P        | AIO                                   | Analog input channel 4: positive input                                                                                           |

| 56 | AIN_4GND | AIO | Analog input channel 4: negative input |  |

|----|----------|-----|----------------------------------------|--|

| 57 | AIN_5P   | AIO | Analog input channel 5: positive input |  |

| 58 | AIN_5GND | AIO | Analog input channel 5: negative input |  |

| 59 | AIN_6P   | AIO | Analog input channel 6: positive input |  |

| 60 | AIN_6GND | AIO | Analog input channel 6: negative input |  |

| 61 | AIN_7P   | AIO | Analog input channel 7: positive input |  |

| 62 | AIN_7GND | AIO | Analog input channel 7: negative input |  |

| 63 | AIN_8P   | AIO | Analog input channel 8: positive input |  |

| 64 | AIN_8GND | AIO | Analog input channel 8: negative input |  |

### **Specifications**

#### **Absolute Maximum Ratings**

At T<sub>A</sub>=25°C

|                                            | Parameter                             | Min  | Max        | Unit |

|--------------------------------------------|---------------------------------------|------|------------|------|

| AVDD to AGND                               |                                       | -0.3 | 7          | V    |

| DVDD to DGND                               |                                       | -0.3 | 7          | V    |

| AGND to DGND                               |                                       | -0.3 | 0.3        | V    |

|                                            | Analog input voltage to AGND          | -15  | 15         |      |

|                                            | Digital input to DGND                 | -0.3 | DVDD + 0.3 | ٧    |

|                                            | REFIN to AGND                         | -0.3 | AVDD + 0.3 | V    |

| Inpu                                       | ut current to any pin except supplies | -10  | 10         | mA   |

| TJ                                         | Maximum Junction Temperature          | -40  | 150        | °C   |

| T <sub>A</sub> Operating Temperature Range |                                       | -40  | 125        | °C   |

| T <sub>STG</sub>                           | Storage Temperature Range             | -65  | 150        | °C   |

| TL                                         | Lead Temperature (Soldering 10 sec)   |      | 260        | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

#### **ESD, Electrostatic Discharge Protection**

| Symbol | Parameter                                                  | Condition                 | Minimum Level | Unit        |

|--------|------------------------------------------------------------|---------------------------|---------------|-------------|

| НВМ    | Human Body Model ESD for all pins except analog input pins | ANSI/ESDA/JEDEC JS-001(1) | ±5000         | <b>&gt;</b> |

| НВМ    | Human Body Model ESD for analog input pins only            | ANSI/ESDA/JEDEC JS-001(1) | ±7000         | <b>&gt;</b> |

| CDM    | Charged Device Model ESD                                   | ANSI/ESDA/JEDEC JS-002(2) | ±1500         | V           |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### **Recommended Operating Conditions**

| Para | Min                        | Тур  | Max | Unit |   |

|------|----------------------------|------|-----|------|---|

| AVDD | AVDD Analog supply voltage |      | 5   | 5.25 | V |

| DVDD | Digital supply voltage     | 1.71 | 3.3 | AVDD | V |

#### **Thermal Information**

| Package Type | $	heta_{JA}$ | $oldsymbol{	heta}_{	extsf{JC(top)}}$ | Unit |  |

|--------------|--------------|--------------------------------------|------|--|

| LQFP10X10-64 | 46           | 7.8                                  | °C/W |  |

www.3peakic.com.cn 9 / 24 Rev.Pre.1

<sup>(2)</sup> This data was taken with the JEDEC low effective thermal conductivity test board.

<sup>(3)</sup> This data was taken with the JEDEC standard multilayer test boards.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### **Electrical Characteristics**

All test conditions:  $V_{REF}$ =2.5V external/internal, AVDD = 4.75V to 5.25V,  $V_{DRIVE}$ =1.71V to AVDD,  $f_{SAMPLE}$  = 200 kSPS,  $T_{A}$ =-40°C to 125°C, Low Bandwidth Mode, unless otherwise noted.

| Symbol         | Parameter                   | Test c                       | ondition                             | MIN | TYP  | MAX | Unit |

|----------------|-----------------------------|------------------------------|--------------------------------------|-----|------|-----|------|

| Dynamic Perfe  | ormance                     |                              |                                      |     |      |     |      |

|                |                             | fin=1kHz<br>sine wave,       | ±10V No oversampling                 |     | 89.7 |     | dB   |

|                | Signal to noise             | unless<br>otherwise<br>noted | ±5V No<br>oversampling               |     | 89.5 |     | dB   |

| SNR            | ratio                       | fin=130Hz                    | Oversampling<br>by 16, ±10V<br>Range |     | 95.2 |     | dB   |

|                |                             | fin=130Hz                    | Oversampling<br>by 16, ±5V<br>Range  |     | 94.7 |     | dB   |

|                | Signal to noise             | fin=1kHz<br>sine wave,       | ±10V No oversampling                 |     | 89.5 |     | dB   |

| SINAD          | + distortion ratio          | unless<br>otherwise<br>noted | ±5V No<br>oversampling               |     | 89.4 |     | dB   |

| THD            | Total harmonic distortion   | All input range, fin=1KHz    |                                      |     | -106 |     | dB   |

| SFDR           | Spurious free dynamic range | fin=1KHz                     |                                      |     | -106 |     | dB   |

| Analog Input I | Filter                      |                              |                                      |     |      |     |      |

|                |                             | Low<br>Bandwidth<br>Mode     | -3dB, ±10V                           |     | 20.0 |     | KHz  |

|                | Small signal                | Low<br>Bandwidth<br>Mode     | -3dB, ±5V                            |     | 12.7 |     | KHz  |

| BW(-3 dB)      | bandwidth                   | High<br>Bandwidth<br>Mode    | -3dB, ±10V                           |     | 26.5 |     | KHz  |

|                |                             | High<br>Bandwidth<br>Mode    | -3dB, ±5V                            |     | 16.4 |     | KHz  |

|              | T             | T                       | T            | T     | 1    | 1   | 1     |  |

|--------------|---------------|-------------------------|--------------|-------|------|-----|-------|--|

|              |               | Low                     |              |       |      |     |       |  |

|              |               | Bandwidth               | -0.1dB, ±10V |       | 3.3  |     | KHz   |  |

|              |               | Mode                    |              |       |      |     |       |  |

|              |               | Low                     |              |       |      |     |       |  |

|              |               | Bandwidth               | -0.1dB, ±5V  |       | 2.2  |     | KHz   |  |

| BW(-0.1 dB)  | Small signal  | Mode                    |              |       |      |     |       |  |

| BVV(-0.1 dB) | bandwidth     | High                    |              |       |      |     |       |  |

|              |               | Bandwidth               | -0.1dB, ±10V |       | 4.3  |     | KHz   |  |

|              |               | Mode                    |              |       |      | 1   |       |  |

|              |               | High                    |              |       |      |     |       |  |

|              |               | Bandwidth               | -0.1dB, ±5V  |       | 2.6  |     | KHz   |  |

|              |               | Mode                    |              |       |      |     |       |  |

|              |               | Low                     |              |       |      |     |       |  |

|              |               | Bandwidth               | ±10V         |       | 10   |     | us    |  |

|              |               | Mode                    |              |       | / -  |     |       |  |

| Tgroup_delay | Group delay   | Low                     |              |       |      |     |       |  |

|              |               | Bandwidth               | ±5V          |       | 16   |     | us    |  |

|              |               | Mode                    |              |       |      |     |       |  |

|              |               |                         |              |       |      |     |       |  |

|              |               | High                    | W            |       |      |     |       |  |

|              |               | Bandwidth 4             | ±10V         |       | 8    |     | us    |  |

|              |               | Mode                    |              |       |      |     |       |  |

|              |               | High                    |              |       |      |     |       |  |

|              |               | Bandwidth               | ±5V          |       | 12   |     | us    |  |

|              |               | Mode                    |              |       |      |     |       |  |

| DC Accuracy  | 4             | \ \ \                   |              |       |      |     |       |  |

|              |               |                         | NO missing   |       |      |     |       |  |

|              | Resolution    |                         | code         |       | 16   |     | bit   |  |

|              |               | fsample = 1             | 200 kSPS, -  |       |      |     |       |  |

| DNL          | Differential  |                         |              | -0.99 | ±0.5 |     | LSB   |  |

|              | nonlinearity  | 40~                     | ~85°C        |       | 10.0 |     | LOB   |  |

|              |               | f <sub>SAMPLE</sub> = 1 | 200 kSPS, -  |       |      |     |       |  |

| INL          | Integral      |                         |              |       | ±0.7 |     | LSB   |  |

|              | nonlinearity  | 40~                     | ~85°C        |       |      |     |       |  |

|              |               | Ext                     |              |       |      |     |       |  |

|              | Positive and  | reference               |              |       | ±4   | ±50 | LSB   |  |

|              | Negative Full | Int                     |              |       |      |     |       |  |

|              | Scale Error   | reference               |              |       | ±15  |     | LSB   |  |

|              |               | Ext                     |              |       |      |     |       |  |

|              | Positive Full | reference               |              |       | ±2   |     | ppm/C |  |

|              | Scale Error   | Int                     |              |       |      |     |       |  |

|              | Drift         | reference               |              |       | ±10  |     | ppm/C |  |

|              |               | reference               |              |       |      |     |       |  |

|                 | <u> </u>         |                  |                 |       | I            |       |       |

|-----------------|------------------|------------------|-----------------|-------|--------------|-------|-------|

|                 | Negative Full    | Ext              |                 |       | ±2           |       | ppm/C |

|                 | Scale Error      | reference        |                 |       |              |       |       |

|                 | Drift            | Int              |                 |       | ±10          |       | ppm/C |

|                 | 5: 1 7           | reference        | 4014            |       |              |       |       |

|                 | Bipolar Zero     |                  | ±10V            |       | ±1           | ±15   | LSB   |

|                 | Code Error       |                  | ±5V             |       |              |       |       |

|                 | Bipolar Zero     |                  | ±10V            |       | ±10          |       | μV/C  |

|                 | Code Error Drift |                  | ±5V             |       | ±5           |       | μV/C  |

|                 | Bipolar Full     |                  |                 |       |              |       |       |

|                 | Scale Error      |                  |                 |       | ±6           | ±22   | LSB   |

|                 | Matching         |                  |                 |       |              |       |       |

|                 | Bipolar Zero     |                  | . 51/           |       | 1. 1         |       |       |

|                 | Code Error       |                  | ±5V<br>±10V     |       | ±3           | ±20   | LSB   |

|                 | matching         |                  | ±10V            |       |              |       |       |

| Analog Input    | 1                |                  | I               |       |              |       |       |

|                 |                  |                  | RANGE=1,        |       |              | 40    |       |

|                 |                  | \/ \/ OND        | ±10V range      | -10   |              | 10    | .,    |

|                 | Input Range      | Vx-VxGND         | RANGE=0,        |       |              | _     | V     |

|                 |                  |                  | ±5V range       | -5    |              | 5     |       |

|                 | Analog Input     |                  | 10V range       |       | () (' O) (D) |       | uA    |

|                 | Current          |                  | 5V range        |       | (Vin-2)/Rin  |       | uA    |

| 0               | Input            |                  |                 |       | _            |       |       |

| $C_{IN}$        | capacitance      |                  |                 |       | 5            |       | pF    |

| R <sub>IN</sub> | Input resistance |                  |                 |       | 1Mohm        |       | Mohm  |

| Input           | Innut 4          |                  |                 |       |              |       |       |

| Impedance       | Input            |                  |                 |       | ±20          |       | ppm/C |

| Drift           | Impedance Drift  |                  |                 |       |              |       |       |

| Reference inp   | ut/output        |                  |                 |       |              |       |       |

|                 | Reference input  | REF SELEC        | T=0, select Ext |       |              |       |       |

|                 |                  | Ref, force       | e voltage on    | 2.475 | 2.5          | 2.525 | V     |

|                 | voltage          | REFIN            | /REFOUT         |       |              |       |       |

| AV              |                  | REF_S            | ELECT=1,        |       |              | _     |       |

| 1 1             | Reference        | REFIN/RE         | FOUT output     | 0.405 | 0.5          | 0.505 | .,    |

|                 | output voltage   | vo               | ltage           | 2.495 | 2.5          | 2.505 | V     |

|                 |                  | T <sub>A</sub> = | =25°C           |       |              |       |       |

|                 | Reference        |                  |                 |       | .40          |       | nn=/0 |

|                 | voltage TC       |                  |                 |       | ±10          |       | ppm/C |

|                 |                  | Voltage on I     | REFCAPA and     |       |              |       |       |

|                 | V(REFCAPA/B)     | REFCAPB,         | also used for   |       | 4            |       | V     |

|                 |                  | A                | \DC             |       |              |       |       |

| LOGIC INPUT     |                  |                  |                 |       |              |       |       |

|                 |                  |                  |                 |       |              |       |       |

|                 |                  |              |              |            |              | -          |      |

|-----------------|------------------|--------------|--------------|------------|--------------|------------|------|

| V <sub>IH</sub> | Input high       | input logic  |              | 0.7*VDRIVE |              |            | V    |

|                 | voltage          | high voltage |              |            |              |            |      |

| VIL             | Input low        | input logic  |              |            |              | 0.3*VDRIVE | V    |

|                 | voltage          | low voltage  |              |            |              |            |      |

| Cı              | Input            | input        |              |            | 5            |            | nE   |

|                 | capacitance      | capacitance  |              |            | 5            |            | pF   |

|                 |                  | input        |              |            |              | <b>A</b> 0 |      |

| lı .            | Input current    | current      |              |            |              | #2         | uA   |

| LOGIC OUTPL     | JT               |              | <u> </u>     |            |              | 1          |      |

|                 | Output high      |              | current      |            |              |            |      |

| V <sub>OH</sub> | voltage          |              | source=100uA | VDRIVE-0.2 |              |            | V    |

|                 | _                |              |              |            | . •          |            |      |

| V <sub>OL</sub> | Output low       |              | current      |            | 1 1          | 0.2        | V    |

|                 | voltage          |              | sink=100uA   |            |              |            |      |

|                 | Float state      |              |              |            | ±1           | ±20        | uA   |

|                 | leakage current  |              |              |            |              |            |      |

| Co              | Output           |              |              |            | 5            |            | pF   |

| 00              | capacitance      |              |              |            | 3            |            | рг   |

| Conversion ra   | te               |              |              |            | <del>-</del> |            |      |

|                 | conversion time  |              |              |            | 1.65         |            | us   |

|                 | Acquisition      |              |              |            | 1.2          |            |      |

|                 | Time             | •            |              |            | 1.2          |            | us   |

|                 | Throughput       |              | 11 3         |            |              |            |      |

|                 | Rate             | Per channel  |              |            |              | 200        | kSPS |

| Timing specifi  | cations          |              |              |            |              |            |      |

|                 |                  |              |              |            |              |            |      |

|                 |                  |              |              |            |              |            |      |

|                 |                  |              |              |            |              |            |      |

|                 |                  |              | VDRIVE>2.7V  |            | 30           |            | MHz  |

|                 |                  |              |              |            |              |            |      |

|                 |                  |              |              |            |              |            |      |

| SCLK            | frequency of     |              |              |            |              |            |      |

| JOLIN           | serial interface |              |              |            |              |            |      |

|                 |                  |              |              |            |              |            |      |

| J K             | Ť                |              |              |            |              |            |      |

|                 |                  |              | VDRIVE>2.3V  |            | 20           |            | MHz  |

|                 |                  |              |              |            |              |            |      |

|                 |                  |              |              |            |              |            |      |

|                 |                  |              |              |            |              |            |      |

| AVCC normal      |  | 41 | 51 | mA |

|------------------|--|----|----|----|

| AVCC Stanby      |  | 5  | 9  | mA |

| AVCC<br>Shutdown |  | -  | 25 | uA |

(1) 100% tested at  $T_A = 25$ °C.

### **Detailed Description**

#### Overview

TSAFE516 is a 16bit, 8-channel simultaneous sampling, successive approximation (SAR) ADC. Each channel has a complete analog front end, as well as an ADC operating at 200 kSPS per channel. The analog front end features input clamp, a programmable gain amplifier (PGA) with high input impedance of  $1M\Omega$ , low pass filter and ADC input driver.

The device features an internal precision reference with buffer to driver the ADC. A digital interface supports serial, parallel and parallel byte communication, which can be used with varies host controllers.

The TSAFE516 can accept ±10V or ± 5V true bipolar inputs with a single 5V supply. Also the high input impedance allows direct connection to transformers or other sensors without external driver circuits.

#### **Feature Description**

#### **Analog inputs**

The TSAFE516 has 8 analog input channels, and positive inputs AIN\_nP (n = 1 to 8) are the single ended analog inputs and the negative inputs AIN nGND should be tied to GND.

The input voltage range can be configured to bipolar ±10 V or ±5 V by the RANGE pin.

The device allows a ±0.3-V range on the AIN\_nGND

#### Analog input impedance

Each analog input channel in the device presents a constant resistive impedance of 1 M $\Omega$ .

Matching the external source impedance on the AIN\_nP input pin with an equivalent resistance on the AIN\_nGND pin is recommended to cancel any additional offset error contributed by the external resistance.

#### **Input Clamp Protection Circuit**

The input clamp protection circuit allows analog input to swing up to  $\pm 30$  V (typical). The input clamp circuit turns on beyond clamp voltage.

For input voltages above the clamp threshold, make sure that input current never exceeds the absolute maximum rating to prevent any damage to the device.

Don't keep the device in a state such that the clamp circuit is activated for extended periods of time, because this fault condition can degrade device performance and reliability.

#### **Programmable Gain Amplifier (PGA)**

The device has a programmable gain amplifier (PGA) at each individual input channel. The PGA converts the single-ended input signal into a fully-differential signal to drive internal ADC. The PGA also adjusts the common-mode voltage feeding into the ADC to ensure maximum usage of the ADC input dynamic range. The PGA gain is adjusted by configuring the RANGE pin of the ADC accordingly.

#### **Low Pass Filter**

Each channel of the TSAFE516 features a second-order antialiasing low pass filter (LPF) at the output of the PGA, to remove the noise of the front-end amplifiers and gain resistors of the PGA.

#### **ADC Driver**

There is an integrated ADC input driver before each ADC channel. This integrated ADC driver eliminates the need any external amplifier, helping inputs of the ADC to settle to better than 16-bit accuracy before any sampled analog voltage gets converted. And thus the signal chain design for the user is simplified.

#### **Digital filter**

The TSAFE516 has an optional digital averaging filter that can be used in slower throughput applications requiring lower noise and higher dynamic range. The oversampling ratio of the digital filter is determined by the configuration of the OS[2:0] pins.

In oversampling mode, the samples are averaged to reduce the noise of the signal chain as well as to improve the SNR of the ADC. The final output is also decimated to provide data for each channel.

| OS[2:0] | OS RATIO | MAX THROUGHPUT<br>PER CHANNEL<br>(kSPS) |

|---------|----------|-----------------------------------------|

| 000     | NO OS    | 200                                     |

| 001     | 2        | 175 100                                 |

| 010     | 4        | 87.5 50                                 |

| 011     | 8        | 43.75 25                                |

| 100     | 16       | 21.875 12.5                             |

| 101     | 32       | 10.94 6.25                              |

| 110     | 64       | 5.47 3.125                              |

| 111     | NA       | 200                                     |

#### Reference

The TSAFE516 can operate with either an internal voltage reference or an external voltage reference. The internal or external reference selection is determined by an external REFSEL pin,

The REFIN/REFOUT pin outputs the internal band-gap voltage (in internal reference mode) or functions as input pin to the external reference voltage (in external reference mode). The on-chip amplifier is enabled in both modes to drive the actual reference input of the internal ADC core. The REFCAPA and REFCAPB pins must be shorted together externally and a ceramic capacitor of minimum 10 µF should be connected between this node and REFGND to ensure that the internal reference buffer is operating as closed loop.

#### **ADC transfer function**

The TSAFE516 outputs 16 bits data in binary twos complement format for both bipolar input ranges. The format for the output codes is the same across all analog channels.

| Input range(V) | Full scale Range(V) | LSB(µV)         |  |  |

|----------------|---------------------|-----------------|--|--|

| ±10            | 20                  | 305. 18         |  |  |

| ±5             | 10                  | 152 <b>.</b> 59 |  |  |

#### **Device Functional Modes**

**Device Interface: Pin Description**

REFSEL (Input)

The REFSEL pin selects between the internal and external reference mode of the device.

www.3peakic.com.cn 16 / 24 Rev.Pre.1

If the REFSEL pin is set to logic high, then the internal reference is enabled and selected.

If the REFSEL pin is set to logic low, then the internal reference circuit is disabled and powered down. In this mode, an external reference voltage must be provided to the REFIN/REFOUT pin.

The internal reference buffer is always enabled under both conditions.

The reference mode after power-up depends on the state of the REFSEL input pin.

#### RANGE (Input)

The RANGE pin selects input range for all analog input channels.

If this pin is set to logic high, the device is configured to operate in the ±10-V input range.

If this pin is set to logic low, the device is configured to operate in the ±5-V input range.

The RANGE pin is also used to put the device in standby or shutdown mode depending on the state of the STBY input pin, as explained in the Power-Down Modes section.

#### • STBY (Input)

The STBY pin puts the device into one of two power down modes: standby and power down

If this pin is set to logic high, the device is in normal operation mode.

If this pin is set to logic low, the device is in standby or power down mode, depending on the state of RANGE pin.

In shutdown mode, all internal circuitry is powered down,

In standby mode, the internal reference remains powered up to enable a relatively quicker recovery to normal operation mode.

#### PAR/SER/BYTE SEL (Input)

The PAR/SER/BYTE SEL pin selects between the parallel, serial and parallel byte interface mode for reading data from the device.

If this pin is set to logic high, then the serial or parallel byte interface mode is selected depending on the state of DB15/BYTE SEL pin. If DB15/BYTE SEL pin is high, the parallel byte interface is selected, and if the DB15/BYTE SEL is low, then serial mode is selected.

#### CONVSTA, CONVSTB (Input)

CONVSTA, CONVSTB (Input) are conversion control input pins.

CONVSTA can be used to simultaneously sample and initiate the conversion process for the first half count of device input channels (channels 1-4), and CONVSTB can be used to simultaneously sample and initiate the conversion process for the latter half count of device input channels (channels 5-8).

On the rising edge of the CONVSTA, CONVSTB signals, the internal track-and-hold circuits for each analog input channel are placed into hold mode and the sampled input signal is converted.

The CONVSTA, CONVSTB signals can be pulled low when the internal conversion is over, as indicated by the BUSY signal. At this point, the front-end circuit for all analog input channels acquires the respective input signals and the internal ADC is not converting.

The output data can be read from the device irrespective of the status of the CONVSTA, CONVSTB pins.

#### **RESET (Input)**

The RESET pin can be used to reset the device at any time in an asynchronous manner. When the RESET pin is set to logic high, the device is in reset mode, and remains the state until the pin returns low.

The device should be reset after power-up or recovery from shut down mode when all the supplies and

www.3peakic.com.cn 17 / 24 Rev.Pre.1

references have settled to the required accuracy.

#### RD/SCLK(Input)

RD/SCLK(Input) is dual function pin to be used in different interface mode.

| Device operating condition | n                                 | Functionality of RD/SCLK(Input)                                                                                     |  |

|----------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------|--|

| Darallal interfece         | PAR/SER/BYTE SEL=0                | Active-low digital input pin to read the output data from the device.  In parallel or parallel byte interface mode, |  |

| Parallel interface         | DB15/BYTE=0                       | the output bus is enabled when both the                                                                             |  |

| Parallel byte interface    | PAR/SER/BYTE SEL=1<br>DB15/BYTE=1 | CS and RD inputs are tied to a logic low input.                                                                     |  |

|                            |                                   | External clock input for the serial data                                                                            |  |

|                            |                                   | interface. In serial mode, all synchronous                                                                          |  |

|                            |                                   | accesses to the device are timed with                                                                               |  |

|                            | PAR/SER/BYTE SEL=1                | respect to the rising edge of                                                                                       |  |

| Serial interface           | DB15/BYTE=0                       | the SCLK signal.                                                                                                    |  |

#### CS (Input)

The  $\overline{\text{CS}}$  pin is an active-low, chip-select signal.

A rising edge on the  $\overline{\text{CS}}$  signal outputs all the data lines in tri-state mode.

A falling edge of the  $\overline{CS}$  signal marks the beginning of the output data transfer frame in any interface mode of operation for the device.

#### OS[2:0]

The OS[2:0] pins are active-high digital input pins used to configure the oversampling ratio for the internal digital filter on the device.

When OS[2:0]=111, a higher filter bandwidth of ~30kHz is selected.

#### **Device Modes of Operation**

#### **Power Down Modes**

The device supports two power-down modes: standby mode and shutdown mode. The device can enter either power-down mode by pulling the  $\overline{\text{STBY}}$  pin to a logic level. Additionally, the selection between these two power-down modes is done by the state of the RANGE pin.

| Power Down Mode | STBY | Range |  |  |

|-----------------|------|-------|--|--|

| Standby         | 0    | 1     |  |  |

| Shutdown        | 0    | 0     |  |  |

#### Standby mode

In standby mode, only internal reference of the circuit is powered up, and analog front-end, signal-conditioning

www.3peakic.com.cn 18 / 24 Rev.Pre.1

circuit for each channel remains powered down.

#### Shutdown mode

In shutdown mode, the entire internal circuitry is powered down.

#### **Conversion Control**

The device offers precise control of simultaneously sampling all analog input channels.

#### Simultaneous Sampling on All Input Channels

All the analog input channels to be simultaneously sampled by connecting CONVSTA and CONVSTB signals together, and a single CONVST signal should be used to control the sampling of all analog input channels of the device.

Sampling of all input channels in Parallel Interface Timing Diagram

#### Simultaneous Sampling Two Sets of Input Channels

Two sets of analog input channels can be simultaneously sampled by separating CONVSTA and CONVSTB signals. And the device could not operate in oversampling mode in this state.

#### **Data read operation**

The device updates the internal data registers with the conversion data for all analog channels at the end of every conversion phase (when BUSY goes low).

If the output data are read after BUSY goes low, then the device outputs the conversion results for the current sample.

If the output data are read when BUSY is high, then the device outputs conversion result for the previous sample.

There are three interface mode:

| Interface mode          | PAR/SER/BYTE SEL | DB15/BYTE SEL |

|-------------------------|------------------|---------------|

| Parallel interface      | 0                | 0             |

| Parallel byte interface | 1                | 1             |

| Serial interface        | 1                | 0             |

#### **Parallel Data Read**

The device supports a parallel interface mode for reading the device output data using the control inputs ( $\overline{CS}$  and  $\overline{RD}$ ), the parallel output bus (DB[15:0]), and the BUSY indicator.

For applications that use only one device in the system and does not share the parallel output bus with any other devices, the  $\overline{CS}$  and  $\overline{RD}$  input signals can be tied together, or the  $\overline{CS}$  signal can be permanently tied low. At the first falling edge of the  $\overline{CS}$  and  $\overline{RD}$  signal, the output data of channel 1 becomes available on the parallel bus to be read by the digital host. At this instant the FRSTDATA output also goes high, indicating channel 1 data are ready to be read back. The output data for the remaining channels are clocked out on the parallel bus on subsequent falling edges of the  $\overline{CS}$  and  $\overline{RD}$  signal in a sequential manner.

www.3peakic.com.cn 19 / 24 Rev.Pre.1

For applications that use multiple devices in the system, the CS and RD input signals must be driven separately.

#### Parallel Byte Data Read

The parallel byte interface mode is very similar to the parallel interface mode, except that the output data for each channel is read in two data transfers of 8-bit byte sizes.

In parallel byte mode, the DB14/HBEN pin decides the order of most significant byte (MSB byte) and least significant byte (LSB byte). When DB14/HBEN pin is tied high, the MSB byte of the conversion results is output first followed by the LSB byte. This order is reversed when DB14/HBEN is tied to logic low.

At the first falling edge of the  $\overline{\text{RD}}$  signal, the first byte of the channel 1 conversion result becomes available on DB[7:0]. This byte is followed by the second byte of conversion data on the next falling edge of the RD signal.

#### **Serial Data Read**

This interface mode uses a CS control input, a communication clock input (SCLK), BUSY and FRSTDATA output indicators, and serial data output lines DOUTA and DOUTB.

A total of 16 SCLK cycles are required to clock out 16 bits of conversion result for each channel and the same process can be repeated for the remaining channels in an ascending order.

The conversion results from the first set of channels appear first on DOUTA, followed by the second set of channels if only DOUTA is used for reading data. This order is reversed for DOUTB, in which the second set of channels appear first followed by the first set of channels. The use of both data output lines reduces the time needed for data retrieval and a higher throughput can therefore be achieved in this mode.

#### **Data Read During Conversion**

The device allows data read when and the ADC is converting and the BUSY output is high status. In this case, the ADC outputs conversion results for previous samples.

The data read back during conversion mode allows faster throughput to be achieved from the device.

#### **Data Read During Conversion**

The device can be configured in oversampling mode by the OS[2:0] pins. The input on the OS pins is latched on the falling edge of the BUSY signal to configure the oversampling rate for the next conversion. In this mode, the CONVST A and CONVST B signals should be tied or driven together.

The BUSY signal duration varies with the OSR setting because the conversion time increases with OSR setting.

Oversampling the input signal reduces noise during the conversion process, thus reducing the histogram code spread for a dc input signal to the ADC.

www.3peakic.com.cn 20 / 24 Rev.Pre.1

### **Tape and Reel Information**

| Order Number       | Package      | D1<br>(mm) | W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | W0<br>(mm) | Pin1<br>Quadrant |

|--------------------|--------------|------------|------------|------------|------------|------------|------------|------------|------------------|

| TSAFE5160SI08-QP7R | LQFP10X10-64 | 330        | 28.4       | 12.085     | 12.085     | 2.1        | 16         | 24         | Q2               |

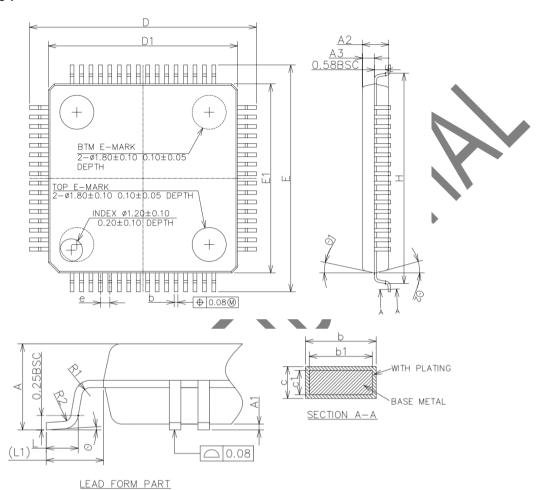

### **Package Outline Dimensions**

### LQFP10X10-64

### COMMON DIMENSIONS (UNITS OF MEASURE=MILLIMETER)

| SYMBOL | MIN   | NOM     | MAX   |  |  |  |  |

|--------|-------|---------|-------|--|--|--|--|

| А      | _     | _       | 1.60  |  |  |  |  |

| A1     | 0.05  | _       | 0.15  |  |  |  |  |

| A2     | 1.35  | 1.40    | 1.45  |  |  |  |  |

| A3     | 0.59  | 0.64    | 0.69  |  |  |  |  |

| b      | 0.18  | _       | 0.27  |  |  |  |  |

| b1     | 0.17  | 0.20    | 0.23  |  |  |  |  |

| С      | 0.13  | _       | 0.18  |  |  |  |  |

| c1     | 0.117 | 0.127   | 0.137 |  |  |  |  |

| D      | 11.95 | 12.00   | 12.05 |  |  |  |  |

| D1     | 9.90  | 10.00   | 10.10 |  |  |  |  |

| E      | 11.95 | 12.00   | 12.05 |  |  |  |  |

| E1     | 9.90  | 10.00   | 10.10 |  |  |  |  |

| е      | 0.40  | 0.50    | 0.60  |  |  |  |  |

| Н      | 11.09 | 11.13   | 11.17 |  |  |  |  |

| L      | 0.53  | _       | 0.70  |  |  |  |  |

| L1     |       | 1.00REF |       |  |  |  |  |

| R1     |       | 0.15REF |       |  |  |  |  |

| R2     |       | 0.13REF |       |  |  |  |  |

| Θ      | 0°    | 3.5°    | 7°    |  |  |  |  |

| Θ1     | 11°   | 12°     | 13°   |  |  |  |  |

| Θ2     | 11°   | 12°     | 13°   |  |  |  |  |

|        |       |         |       |  |  |  |  |

#### **Order Information**

| Order Number       | Operating Temperature Range | Package      | Marking<br>Information | MSL | Transport Media,<br>Quantity | Eco Plan |

|--------------------|-----------------------------|--------------|------------------------|-----|------------------------------|----------|

| TSAFE5160SI08-QP7R | -40 to 125                  | LQFP10X10-64 | AFE5160                | 3   | 1000                         | Green    |

Green: 3PEAK defines "Green" to mean RoHS compatible and free of halogen substances.

**<sup>♣</sup>** 3PEAK and the 3PEAK logo are registered trademarks of 3PEAK INCORPORATED. All other trademarks are the property of their respective owners.