# NSG4437 双通道 2A 超高速功率开关驱动器

## 1 产品特性

- 锁存保护：可承受 0.5A 反向电流

- 低至-10V 的输入逻辑保护

- 输出阻抗低

- 单芯片集成两路驱动

- SD 同时关断两通道，高电平有效

- 输出峰值电流：2A

- 工作范围：4.5V~25V

- 最大输入电压可达 25V

- 高电容负载驱动能力：

- 在 1nF 负载时，开关时间< 25ns

- 上升/下降时间匹配

- 宽温度范围：-40°C~125°C

- 符合 RoSH 标准

SOP8

## 3 产品概述

NSG4437 是功率开关系列驱动器。在对功率开关的栅极进行充电和放电时，它具有匹配的上升和下降时间。NSG4437 在其额定功率和电压范围内的任何条件下都具有高度的锁存抵抗能力。当接地引脚上出现高达 5V 的噪声尖峰（任一极性）时，NSG4437 不会受到损坏。NSG4437 可以接受高达 500mA 的反向电流强制返回其输出，而不会造成损坏或逻辑混乱。所有端子均受到高达 2.0 kV 静电放电 (ESD) 的全面保护。

## 器件信息

| 零件号     | 封装   | 封装尺寸（标称值）     |

|---------|------|---------------|

| NSG4437 | SOP8 | 4.9mm x 3.9mm |

## 2 应用范围

- 交换式电源、开关变换器

- 线路驱动器

- 脉冲变压器驱动

- 驱动 MOSFETs 和 IGBTs

- 电机控制

- 脉冲发生器

- 电源开关

- DC-DC 转换器

- D 类开关放大器

## 简化示意图

#### 4 产品选型

| 产品型号    | 输入输出逻辑 | 封装        | Ton/Toff (ns) |

|---------|--------|-----------|---------------|

| NSG4437 | 同相位带SD | 8-PIN SOP | 30/30         |

#### 5 订购指南

| 产品名     | 打标印记                                                                                                | 封装形式 | 装料形式 | 最小包装数量 |

|---------|-----------------------------------------------------------------------------------------------------|------|------|--------|

| NSG4437 |  NSG4437<br>XXXXXX | SOP8 | 编带   | 4 K/卷  |

#### 6 修订历史

| 版本   | 修改内容          | 修改时间       |

|------|---------------|------------|

| V1.0 | 创建            | 2022.04.29 |

| V2.0 | 产品特性及应用信息     | 2022.09.01 |

| V2.1 | 更新功能说明，添加应用信息 | 2022.10.18 |

# 目录

|                     |    |

|---------------------|----|

| 1 产品特性 .....        | 1  |

| 2 应用范围 .....        | 1  |

| 3 产品概述 .....        | 1  |

| 4 产品选型 .....        | 2  |

| 5 订购指南 .....        | 2  |

| 6 修订历史 .....        | 2  |

| 7 引脚功能描述 .....      | 4  |

| 8 产品规格 .....        | 5  |

| 8.1 极限工作范围 .....    | 5  |

| 8.2 ESD 额定值 .....   | 5  |

| 8.3 额定功率 .....      | 5  |

| 8.4 热量信息 .....      | 5  |

| 8.5 推荐工作范围 .....    | 5  |

| 8.6 电气特性 .....      | 6  |

| 9 功能描述 .....        | 7  |

| 10 NSG4437 说明 ..... | 8  |

| 10.1 概览 .....       | 8  |

| 10.2 功能框图 .....     | 8  |

| 10.3 芯片工作逻辑 .....   | 8  |

| 10.4 信号输入端口 .....   | 9  |

| 10.5 SD 端口 .....    | 9  |

| 10.6 输出端口 .....     | 9  |

| 11 应用信息 .....       | 10 |

| 11.1 应用建议 .....     | 10 |

| 11.2 典型应用电路 .....   | 10 |

| 11.3 PCB 布局指南 ..... | 10 |

| 12. 封装信息 .....      | 12 |

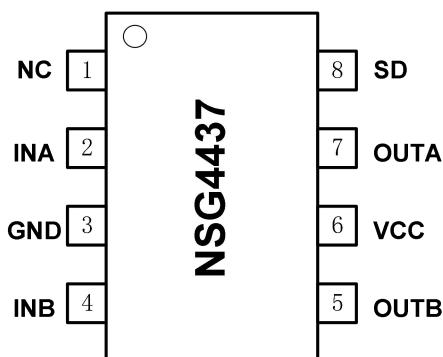

## 7 引脚功能描述

图 7-1 8-脚 SOP8 顶视图

表 7-1 芯片引脚描述

| 编号 | 名称   | 功能       |

|----|------|----------|

| 1  | NC   | 空引脚      |

| 2  | INA  | 通道 A 输入端 |

| 3  | GND  | 引脚地      |

| 4  | INB  | 通道 B 输入端 |

| 5  | OUTB | 通道 B 输出  |

| 6  | VCC  | 电源       |

| 7  | OUTA | 通道 A 输出  |

| 8  | SD   | 通道关断输入引脚 |

## 8 产品规格

### 8.1 极限工作范围

超过极限最大额定值可能造成器件永久性损坏。所有电压参数的额定值是以 GND 为参考的，电流参数以流入端口为正，环境温度为 25°C。

| 符号              | 定义              | 最小值 | 最大值                  | 单位 |

|-----------------|-----------------|-----|----------------------|----|

| V <sub>CC</sub> | 电源电压            | —   | 25                   | V  |

| V <sub>IN</sub> | 逻辑输入电压(INA/INB) | -10 | V <sub>CC</sub> +0.3 |    |

### 8.2 ESD 额定值

| 符号  | 定义     | 最小值 | 最大值  | 单位 |

|-----|--------|-----|------|----|

| ESD | 人体放电模式 | —   | 2000 | V  |

|     | 机器放电模式 | —   | 500  | V  |

### 8.3 额定功率

| 符号 | 定义                   | 最小值 | 最大值 | 单位 |

|----|----------------------|-----|-----|----|

| PD | SOP 封装功率 (TA ≤ 70°C) | —   | 470 | mW |

### 8.4 热量信息

| 符号             | 定义   | 最小值 | 最大值  | 单位 |

|----------------|------|-----|------|----|

| T <sub>J</sub> | 结温   | —   | +150 | °C |

| T <sub>S</sub> | 存储温度 | -45 | +150 |    |

### 8.5 推荐工作范围

为了正确地操作，器件应当在以下推荐条件下使用。所有电压参数的额定值是以 GND 为参考的，电流参数以流入端口为正，环境温度为 25°C。

| 符号              | 定义   | 最小  | 最大  | 单位 |

|-----------------|------|-----|-----|----|

| V <sub>CC</sub> | 电源电压 | 4.5 | 20  | V  |

| T <sub>C</sub>  | 环境温度 | -40 | 125 | °C |

## 8.6 电气特性

无特殊说明的情况下  $T_A = 25^\circ\text{C}$ ,  $4.5\text{V} \leq V_{CC} \leq 18\text{V}$ 。

| 符号        | 定义                                                                          | 最小值            | 典型值  | 最大值   | 单位            |

|-----------|-----------------------------------------------------------------------------|----------------|------|-------|---------------|

| $V_{IH}$  | 逻辑高电平“1”输入电压                                                                | 2.4            | —    | —     | V             |

| $V_{IL}$  | 逻辑低电平“0”输入电压                                                                | —              | —    | 0.8   | V             |

| $I_{IN}$  | 输入电流, $IN=5\text{V}$                                                        | —              | 50   | —     | $\mu\text{A}$ |

| $V_{OH}$  | 高电平输出电压降                                                                    | $V_{CC}-0.025$ | —    | —     | V             |

| $V_{OL}$  | 低电平输出电压降                                                                    | —              | —    | 0.025 | V             |

| $I_{O+}$  | 输出拉电流                                                                       | —              | 2    | —     | A             |

| $I_{O-}$  | 输出灌电流                                                                       | —              | 2    | —     | A             |

| $I_{REV}$ | 锁存保护可承受反向电流(工作周期 $\leq 2\%$ , $t \leq 300\text{us}$ , $V_{CC}=18\text{V}$ ) | —              | >0.5 | —     | A             |

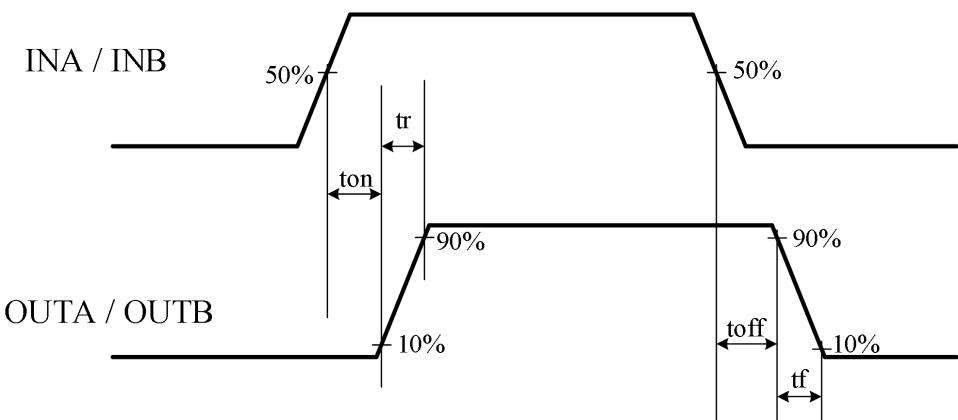

| $t_R$     | 上升时间( $V_{CC}=18\text{V}$ , $C_{LOAD}=100\text{pF}$ )                       | —              | —    | 20    | ns            |

| $t_F$     | 下降时间( $V_{CC}=18\text{V}$ , $C_{LOAD}=100\text{pF}$ )                       | —              | —    | 20    | ns            |

| $t_{ON}$  | 开通传输延时( $V_{CC}=18\text{V}$ , $C_{LOAD}=100\text{pF}$ )                     | —              | —    | 50    | ns            |

| $t_{OFF}$ | 关断传输延时( $V_{CC}=18\text{V}$ , $C_{LOAD}=100\text{pF}$ )                     | —              | —    | 50    | ns            |

| $I_{Q1}$  | 电源电流( $V_{INA}=V_{INB}=\text{逻辑高}$ )                                        | —              | —    | 0.25  | mA            |

| $I_{Q0}$  | 电源电流( $V_{INA}=V_{INB}=\text{逻辑低}$ )                                        | —              | —    | 0.25  | mA            |

## 9 功能描述

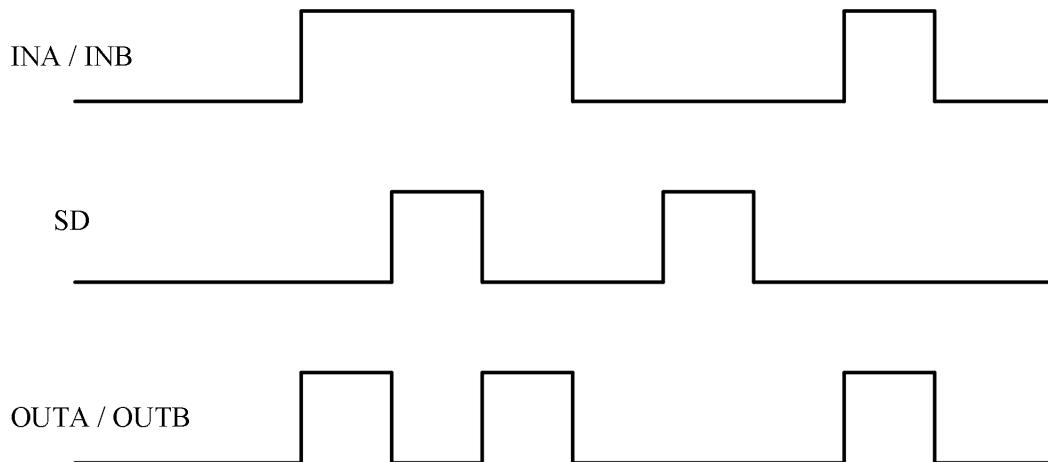

图 9-1 输入输出延时波形图

图 9-2 输入输出逻辑功能图

## 10 NSG4437 说明

### 10.1 概览

NSG4437 是超高速、大电流功率芯片驱动器，在对功率开关的栅极进行充放电时，它具有匹配的上升和下降时间。NSG4437 在其额定功率和电压范围内的任何条件下都具有高度的锁存抵抗能力。当接地引脚上出现高达 5V 的噪声尖峰（任一极性）时，NSG4437 不会受到损坏。NSG4437 可以接受高达 500mA 的反向电流强制返回其输出，而不会造成损坏或逻辑混乱。

NSG4437 包含有 SD 通道关断输入引脚，SD 引脚为高电平时，驱动芯片在任何条件下均不触发输出。

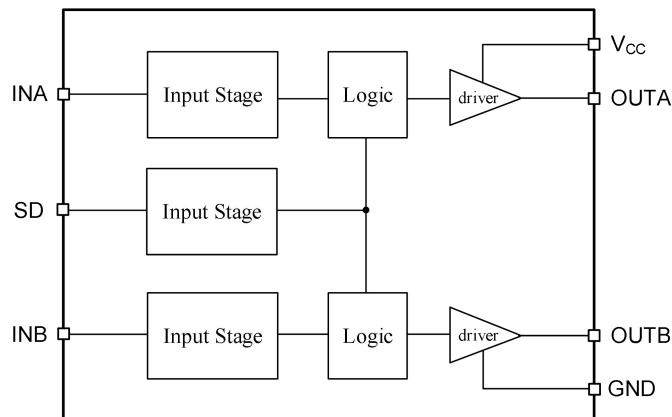

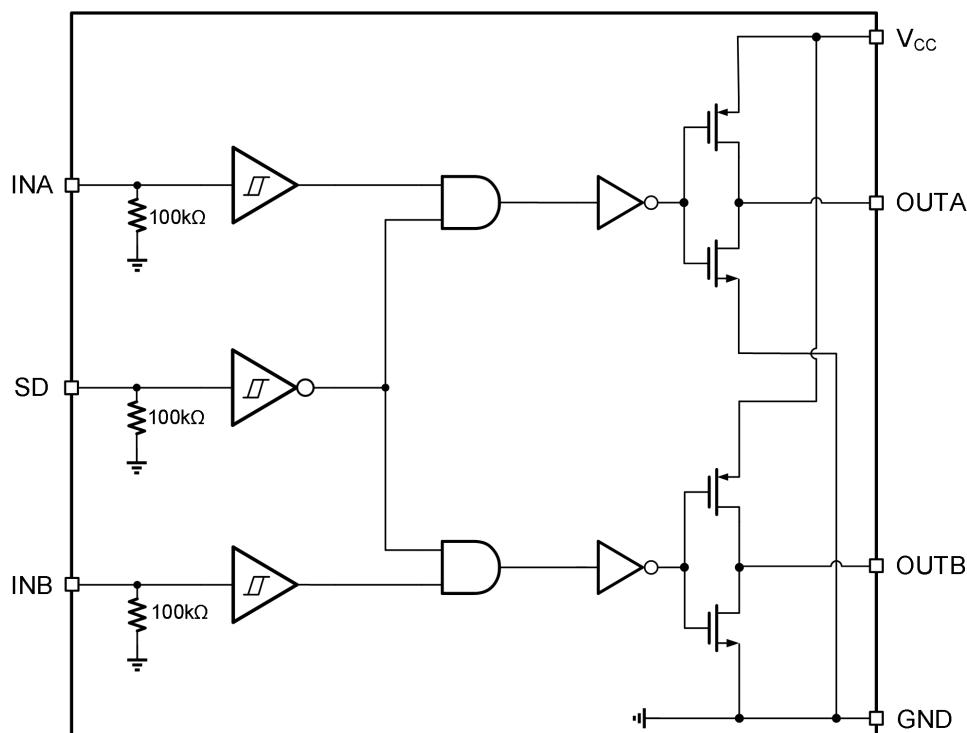

### 10.2 功能框图

图 10-1 NSG4437 功能框图

### 10.3 芯片工作逻辑

NSG4437 信号输入端口（INA、INB）采用电平触发模式，即电压值符合逻辑要求，芯片即可正常工作，如表 10-1 所示。

表 10-1 输入输出逻辑表

| INPUT |     |    | OUTPUT |      |

|-------|-----|----|--------|------|

| INA   | INB | SD | OUTA   | OUTB |

| X     | X   | H  | L      | L    |

| L     | L   | L  | L      | L    |

| L     | H   | L  | L      | H    |

| H     | L   | L  | H      | L    |

| H     | H   | L  | H      | H    |

注：H 代表高电平；L 代表低电平

## 10.4 信号输入端口

NSG4437 包含有两路独立的信号输入端口用于接收来自主控的控制信号，不会发生互相干扰。这两个端口设计有高度的可靠性，即使发生 500mA 的反向电流强制返回其输出，也不会造成损坏或逻辑混乱。信号输入端口同时具备了直接处理-10V 电压的能力，在较大的噪声波形影响下仍然能保证芯片的安全工作，增加了芯片的稳定性。不建议在设计时通过调整输入端口波形斜率或延迟等方式以实现调整输出波形的目的。如果需要调整功率端的上升下降时间，则建议在输出端到功率端之间增加额外的电阻。

NSG4437 的信号输入端口有对 GND 的上拉电阻，建议在不使用时将该端口与 GND 短接。

## 10.5 SD 端口

NSG4437 的 SD 引脚至 GND 引脚之间内置 100KΩ的下拉电阻。如果不使用 SD 功能，可以将该引脚浮空放置或者短接至 GND。在电磁噪声较大的环境中，建议使用 1nf 电容将 EN 引脚连接至 VSS 引脚，并且电容尽可能地靠近 EN 引脚。

## 10.6 输出端口

NSG4437 输出与输入同相位，可以用于驱动 P 型或者 N 型 MOSFET。每个输出端口都能提供峰值为 2A 的上拉或者下拉电流，其高速大电流的特点可以用于驱动高频应用设计中的 MOSFET。

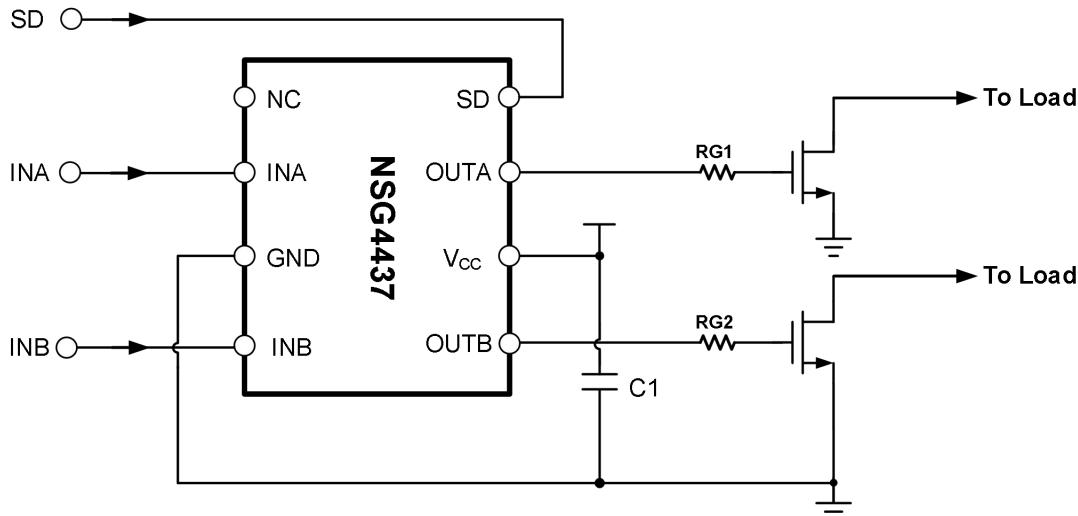

## 11 应用信息

NSG4437 的高速大电流特性可以用于高频电源等应用场景。其典型应用有，主控 IC 的 PWM 输出级功率往往不足以驱动功率端的 MOSFET，因此与 MOSFET 之间需要一个大功率的驱动级芯片用于驱动 MOSFET 的栅极电压，这样才能保证 MOSFET 工作在一个稳定状态。

### 11.1 应用建议

在高频大功率的应用环境中，保证芯片的稳定运行显得尤为重要。因此在 NSG4437 应用时提出以下建议：

- 1) NSG4437 在开关过程中，会输出峰值为 2A 的开关电流，并且随着频率的增加，对 VCC 的稳定性要求更为苛刻。因此在设计时，可以选用一个较大容值的电解电容用于稳定 VCC 电压，并且为了应对高频特性，可以再选用一个低 ESR/ESL 的电容（陶瓷电容或者贴片电容）并联使用。在物理层面上，电容应该尽可能地靠近 VCC 与 GND 两端。

- 2) 输出端口也是组成电源回路的一部分，为了保证输出波形的平整性，输出端口在设计时应该与功率端 MOSFET 的栅极尽可能地靠近。另外，可以在 OUT 外设计额外的电阻，可以使工作波形更加平稳。

### 11.2 典型应用电路

图 10-1 NSG4437 典型应用电路图

### 11.3 PCB 布局指南

为了实现高速低侧门驱动器的最佳性能。建议使用时关注以下几点：

- 1) 低 ESR/ESL 电容必须紧密连接到 VCC 和 GND 引脚之间的 IC，以支持在 mosfet 开启期间从 VDD 引出的高峰值电流。

- 2) 接地方面的考虑：

- 设计接地连接的首要目标是将 MOSFET 栅极充放电回路限制在尽量小的环路面积内。这种方式降低了环路电感，能够有效避免 MOSFET 栅极上的噪声问题。同时，栅极驱动芯片应尽量靠近 MOSFET。

- 星点接地是减少一个电流回路到另一个电流回路的噪声耦合的好方法。驱动器的地单点与功率 MOSFET 的源、PWM 控制器的地等其他电路节点连接。连接的路径必须尽可能短以减少电感，尽可能宽以减少电阻。

- 使用接地面屏蔽噪音。由于 OUT 的快速上升和下降时间可能会破坏过渡期间的输入信号，通过接地面屏蔽噪声，可以保证输入信号不受到干扰。接地面不能是任何电流回路的传导通路，同时地平面必须连接到星点建立地电位。除了屏蔽噪音外，接地平面还可以帮助散热。

3)在有噪声的环境中，为了防止噪声导致输出故障，可以将未使用的 PIN 连接到 VDD 或 GND。

4)电源回路和信号回路分开，如输出和输入信号。

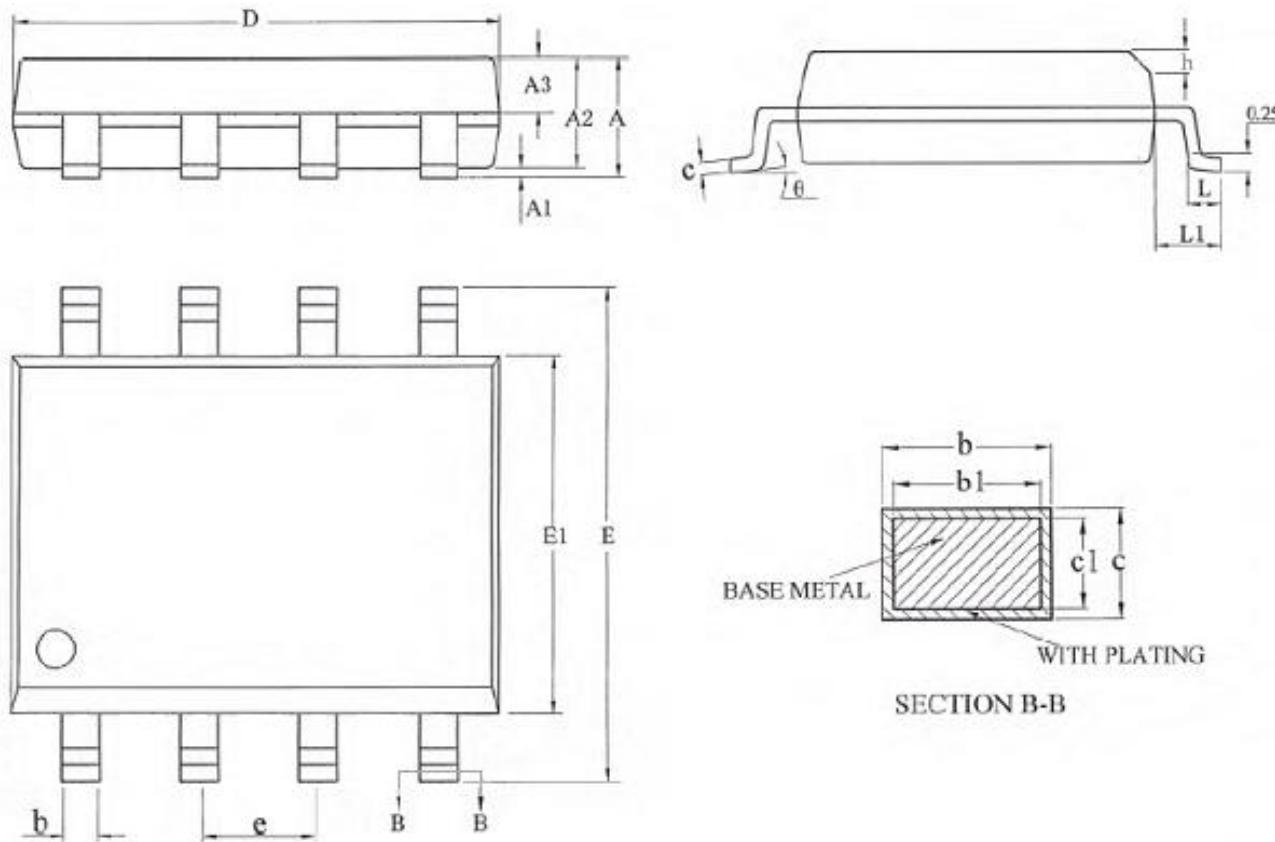

## 12.封装信息

### SOP-8 Package Dimensions

| Size Symbol | MIN(mm) | TYP(mm) | MAX(mm) | Size Symbol | MIN(mm) | TYP(mm) | MAX(mm) |

|-------------|---------|---------|---------|-------------|---------|---------|---------|

| A           | -       | -       | 1.75    | D           | 4.70    | 4.90    | 5.10    |

| A1          | 0.10    | -       | 0.225   | E           | 5.80    | 6.00    | 6.20    |

| A2          | 1.30    | 1.40    | 1.50    | E1          | 3.70    | 3.90    | 4.10    |

| A3          | 0.60    | 0.65    | 0.70    | e           |         | 1.27BSC |         |

| b           | 0.39    | -       | 0.48    | h           | 0.25    | -       | 0.50    |

| b1          | 0.38    | 0.41    | 0.43    | L           |         | 0.50    |         |

| c           | 0.21    | -       | 0.26    | L1          | 1.05BSC |         |         |

| c1          | 0.19    | 0.20    | 0.21    | θ           | 0       | -       | 8°      |

### SOP-8 Package Outlines