# PART NUMBER UCS5810R^B

## Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All re-creations are done with the approval of the Original Component Manufacturer. (OCM)

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

### **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-38535

- Class Q Military

- Class V Space Level

Qualified Suppliers List of Distributors (QSLD)

Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OCM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

### UCN-5800A AND UCN-5801A BIMOS II LATCHED DRIVERS

#### **FEATURES**

- 4.4 MHz Minimum Data Input Rate

- High-Voltage, High-Current Outputs

- Output Transient Protection

- CMOS, PMOS, NMOS, TTL Compatible Inputs

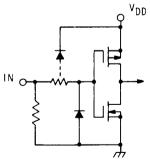

- Internal Pull-Down Resistors

- Low-Power CMOS Latches

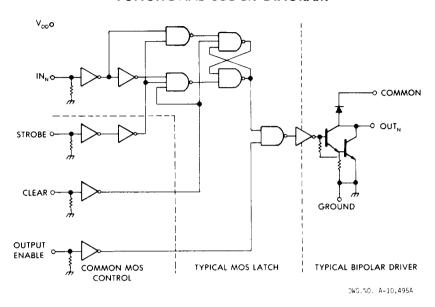

THE UCN-5800A and UCN-5801A latched drivers are high-voltage, high-current integrated circuits comprised of four or eight CMOS data latches, a bipolar Darlington transistor driver for each latch, and CMOS control circuitry for the common CLEAR, STROBE, and OUTPUT ENABLE functions.

The bipolar/MOS combination provides an extremely low-power latch with maximum interface flexibility. Type UCN-5800A contains four latched drivers; Type UCN-5801A contains eight latched drivers.

BiMOS II devices have much faster data input rates than the original BiMOS circuits. With a 5 V supply, they will typically operate at better than 5 MHz. With a 12 V supply, significantly higher speeds are obtained.

The CMOS inputs are compatible with standard CMOS. PMOS, and NMOS circuits. TTL or DTL circuits may require the use of appropriate pull-up resistors. The bipolar outputs are suitable for use with relays, solenoids, stepping motors, LED or incandescent displays, and other high-power loads.

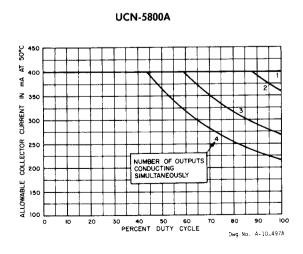

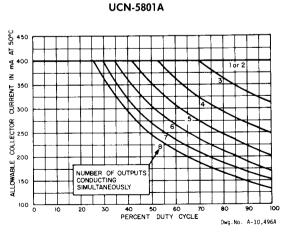

Both units have open-collector outputs and integral diodes for inductive load transient suppression. The output transistors are capable of sinking 500 mA and will sustain at least 50 V in the off state. Because of limitations on package power dissipation, the simultaneous operation of all drivers at maximum rated current can only be accomplished by a

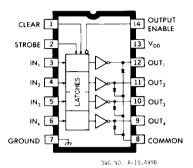

#### UCN-5800A

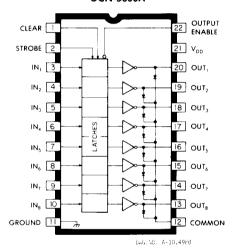

UCN-5801A

reduction in duty cycle. Outputs may be paralleled for higher load current capability.

UCN-5800A, the 4-latch device, is furnished in a standard 14-pin dual in-line plastic package. UCN-5801A, the 8-latch device, is supplied in a 22-pin dual in-line plastic package with lead spacing on 0.400" (10.16 mm) centers. To simplify circuit board layout, all outputs are opposite their respective inputs.

### FUNCTIONAL BLOCK DIAGRAM

### ABSOLUTE MAXIMUM RATINGS at + 25°C Free-Air Temperature

| Output Voltage, V <sub>CE</sub>                                                   |

|-----------------------------------------------------------------------------------|

| Supply Voltage, V <sub>DD</sub>                                                   |

| Input Voltage Range, $V_{IN}$ $-0.3$ V to $V_{DD}$ + 0.3 V                        |

| Continuous Collector Current, I <sub>c</sub> 500 mA                               |

| Package Power Dissipation, Pp                                                     |

| (UCN-5800A)                                                                       |

| (UCN-5801A)                                                                       |

| Operating Temperature Range, $T_A = -20^{\circ}\text{C}$ to $+85^{\circ}\text{C}$ |

| Storage Temperature Range, T <sub>s</sub> 55°C to + 125°C                         |

<sup>\*</sup>Derate at the rate of 16.7 mW/°C above  $T_A = +25$ °C.

Caution: Sprague CMOS devices have input-static protection but are susceptible to damage when exposed to extremely high static electrical charges.

### TYPICAL INPUT CIRCUIT

Dwg.No. A-12,520

<sup>\*\*</sup>Derate at the rate of 20 mW/°C above  $T_{A} = +25$ °C.

### ELECTRICAL CHARACTERISTICS at $T_A = +25$ °C, $V_{DD} = 5$ V (unless otherwise noted)

|                             | Symbol                                 |                                                                 | Limits |      |      |       |

|-----------------------------|----------------------------------------|-----------------------------------------------------------------|--------|------|------|-------|

| Characteristic              |                                        | Test Conditions                                                 | Min.   | Тур. | Max. | Units |

| Output Leakage Current      | I <sub>CEX</sub>                       | $V_{CE} = 50 \text{ V}, T_{A} = +25^{\circ}\text{C}$            | _      |      | 50   | μΑ    |

|                             | June                                   | $V_{CE} = 50 \text{ V}, T_A = +70^{\circ}\text{C}$              | _      | _    | 100  | μΑ    |

| Collector-Emitter           | V <sub>CE(SAT)</sub>                   | $I_{\rm C}=100~{\rm mA}$                                        | _      | 0.9  | 1.1  | ٧     |

| Saturation Voltage          |                                        | $I_c = 200 \text{ mA}$                                          | _      | 1.1  | 1.3  | ٧     |

|                             |                                        | $I_{c} = 350 \text{ mA}, V_{DD} = 7.0 \text{ V}$                |        | 1.3  | 1.6  | ٧     |

| Input Voltage               | V <sub>IN(0)</sub>                     |                                                                 | _      |      | 1.0  | ٧     |

|                             | V <sub>IN(1)</sub>                     | $V_{DD} = 12 V$                                                 | 10.5   |      |      | ٧     |

|                             |                                        | $V_{DD} = 10 \text{ V}$                                         | 8.5    |      | _    | ٧     |

|                             |                                        | V <sub>DD</sub> = 5.0 V (See Note)                              | 3.5    |      | _    | ٧     |

| Input Resistance            | R <sub>in</sub>                        | $V_{DD} = 12 \text{ V}$                                         | 50     | 200  |      | kΩ    |

|                             |                                        | $V_{DD} = 10 \text{ V}$                                         | 50     | 300  | _    | kΩ    |

|                             |                                        | $V_{DD} = 5.0 \text{ V}$                                        | 50     | 600  |      | kΩ    |

| Supply Current              | I <sub>DD(ON)</sub><br>(Each<br>Stage) | $V_{DD}=12$ V, Outputs Open                                     |        | 1.0  | 2.0  | mA    |

|                             |                                        | V <sub>DD</sub> = 10 V, Outputs Open                            | _      | 0.9  | 1.7  | mA    |

|                             |                                        | $V_{DD} = 5.0 \text{ V}$ , Outputs Open                         |        | 0.7  | 1.0  | mA    |

|                             | I <sub>DD(OFF)</sub><br>(Total)        | $V_{DD} = 12 \text{ V}$ , Outputs Open, Inputs $= 0 \text{ V}$  | _      |      | 200  | μΑ    |

|                             |                                        | $V_{DD} = 5.0 \text{ V}$ , Outputs Open, Inputs $= 0 \text{ V}$ | _      | 50   | 100  | μΑ    |

| Clamp Diode I <sub>R</sub>  |                                        | $V_R = 50 \text{ V}, T_A = +25^{\circ}\text{C}$                 |        | _    | 50   | μΑ    |

| Leakage Current             |                                        | $V_R = 50 \text{ V}, T_A = +70^{\circ}\text{C}$                 |        |      | 100  | μΑ    |

| Clamp Diode Forward Voltage | V <sub>F</sub>                         | $I_F = 350 \text{ mA}$                                          |        | 1.7  | 2.0  | ٧     |

NOTE: Operation of these devices with standard TTL or DTL may require the use of appropriate pull-up resistors to insure a minimum logic "1".

### ALLOWABLE OUTPUT CURRENT AS A FUNCTION OF DUTY CYCLE

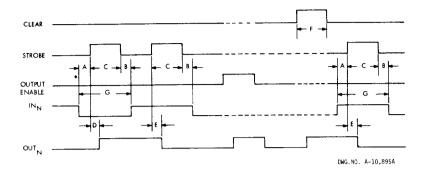

### TIMING CONDITIONS

(Logic Levels are V<sub>DD</sub> and Ground)

| A. | Minimum data active time before strobe enabled (data set-up time)      | . 50 ns |

|----|------------------------------------------------------------------------|---------|

|    | Minimum data active time after strobe disabled (data hold time)        |         |

|    | Minimum strobe pulse width                                             |         |

| D. | Typical time between strobe activation and output on to off transition | 500 ns  |

| Ē. | Typical time between strobe activation and output off to on transition | 500 ns  |

|    | Minimum clear pulse width                                              |         |

|    | Minimum data pulse width                                               |         |

### **TRUTH TABLE**

|                 | STROBE | CLEAR | OUTPUT<br>ENABLE | OUT <sub>N</sub> |     |  |

|-----------------|--------|-------|------------------|------------------|-----|--|

| IN <sub>N</sub> |        |       |                  | t-1              | t   |  |

| 0               | 1      | 0     | 0                | χ                | OFF |  |

| 1               | 1      | 0     | 0                | Χ                | ON  |  |

| Χ               | Х      | 1     | Х                | Χ                | OFF |  |

| Х               | χ      | Χ     | 1                | Х                | OFF |  |

| Χ               | 0      | 0     | 0                | ON               | ON  |  |

| Χ               | 0      | 0     | 0                | OFF              | OFF |  |

X = irrelevant.

t-1 = previous output state.

t = present output state.

Information present at an input is transferred to its latch when the STROBE is high. A high CLEAR input will set all latches to the output OFF condition regardless of the data or STROBE input levels. A high OUTPUT ENABLE will set all outputs to the OFF condition, regardless of any other input conditions. When the OUTPUT ENABLE is low, the outputs depend on the state of their respective latches.

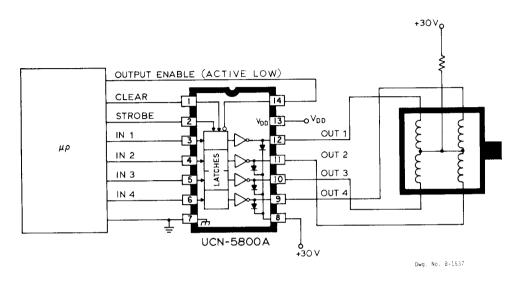

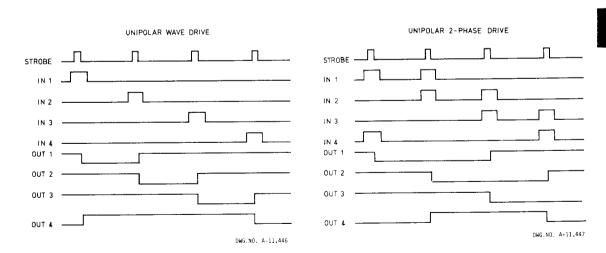

### TYPICAL APPLICATION UNIPOLAR STEPPER-MOTOR DRIVE