# HA16163T

## Synchronous Phase Shift Full-Bridge Control IC

REJ03F0001-0500Z

Rev.5.0

Mar.15.2004

### Features

- High frequency operation; oscillator frequency = 2 MHz max.

- Full-bridge phase-shift switching circuit with adjustable delay times

- Integrated secondary synchronous rectification control with adjustable delay times

- Three-level over current protection; pulse by pulse, timer Latch, one shot OCP

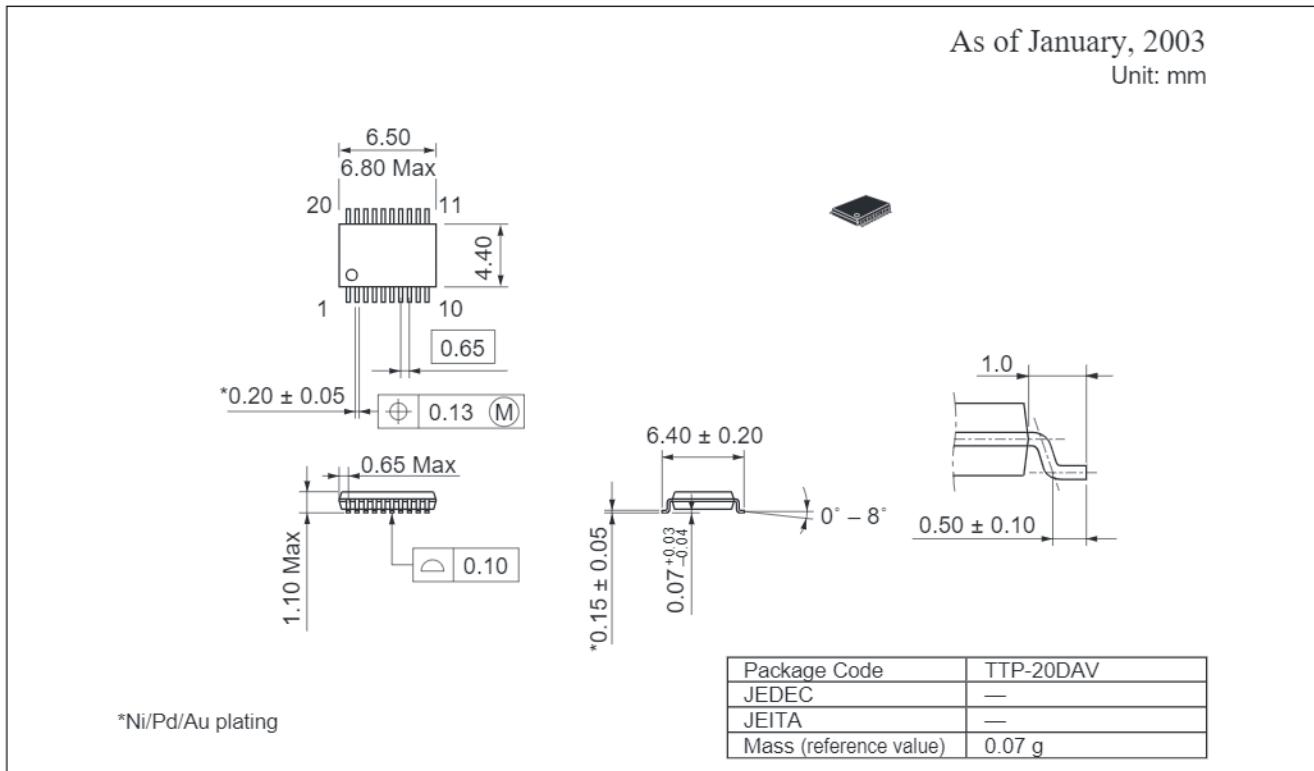

- Package: TSSOP-20

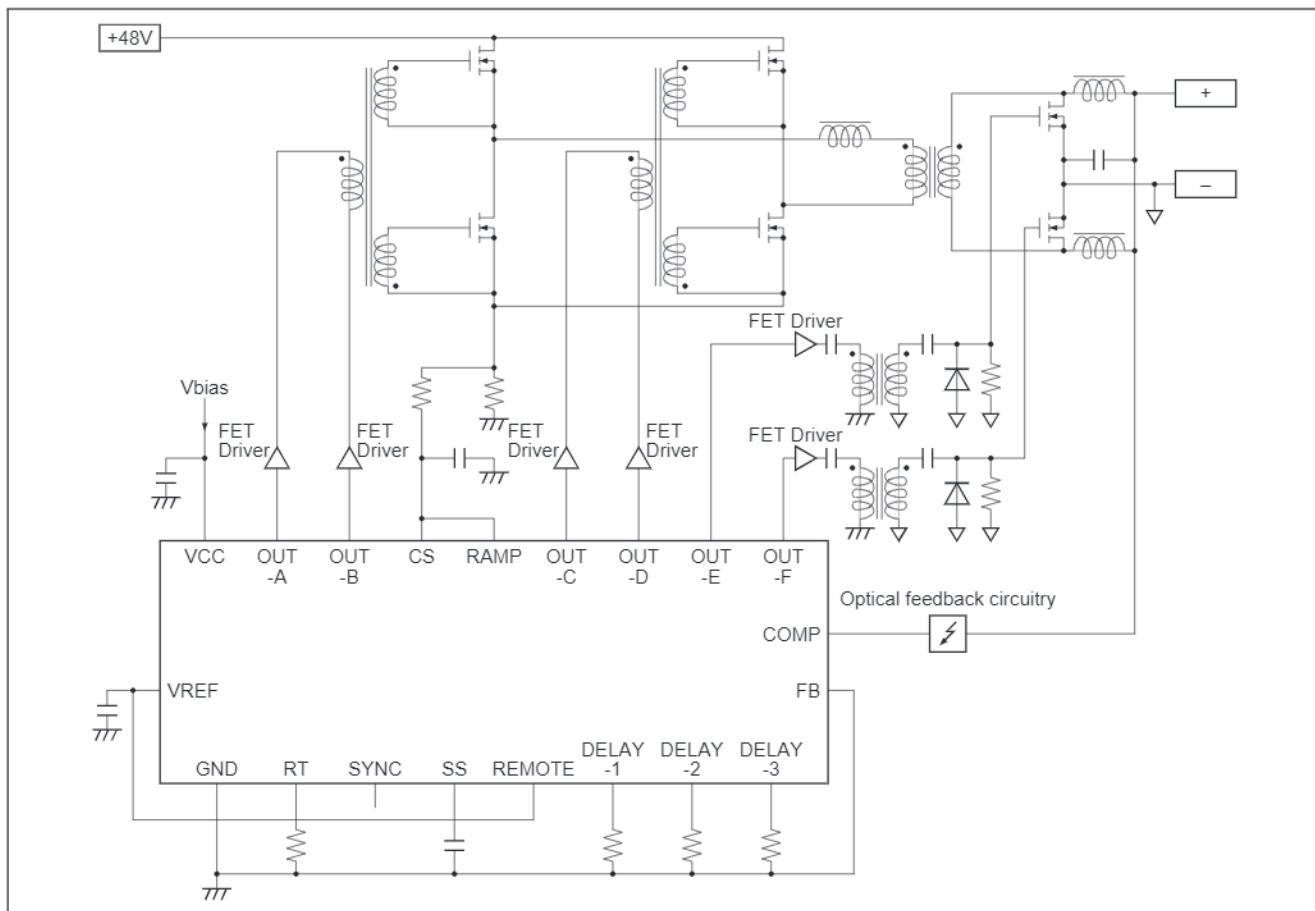

### Application

- 48 V input isolated DC/DC converter

- Primary; Full-bridge circuit topology

- Secondary; current doubler or center-tapped rectification

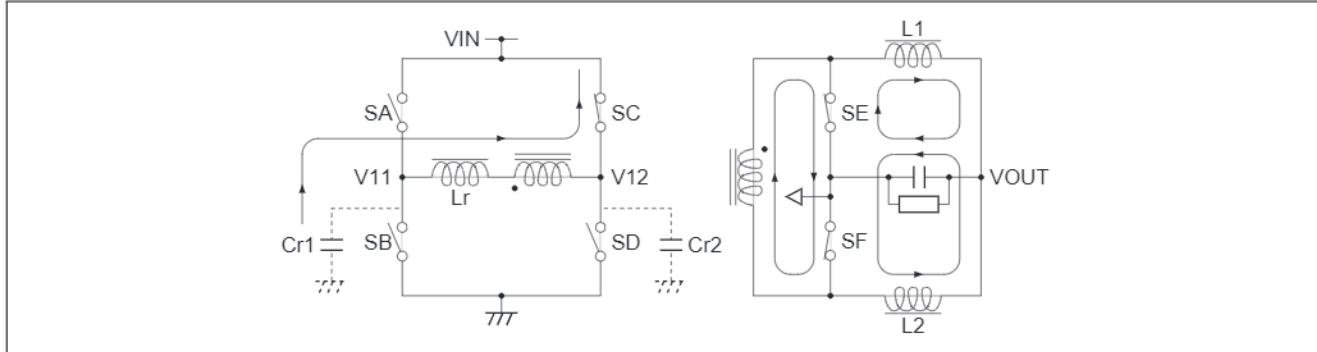

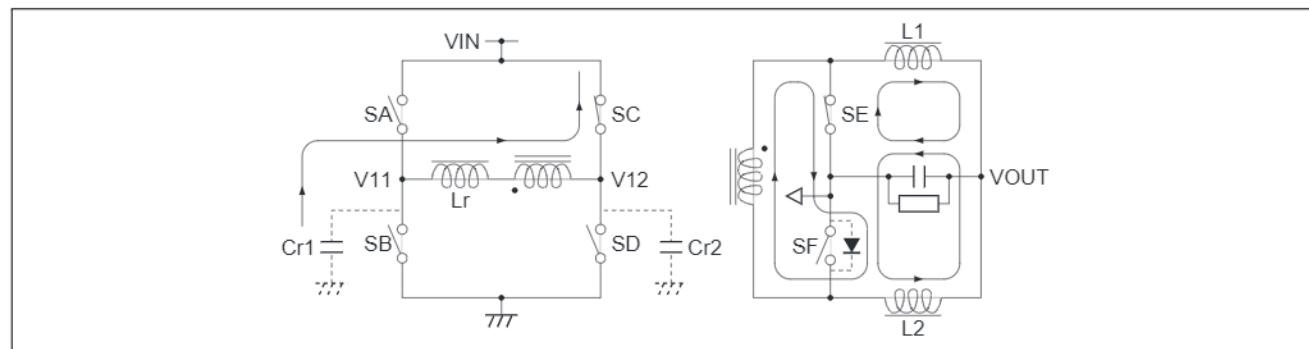

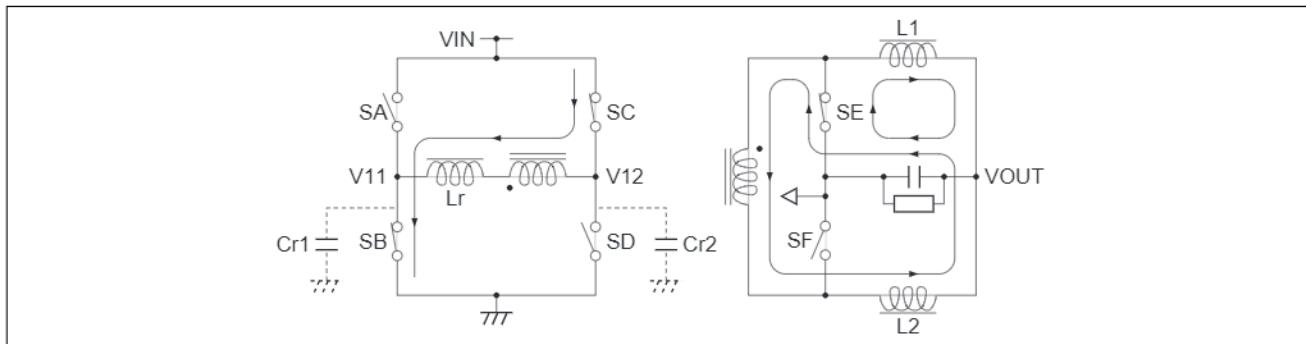

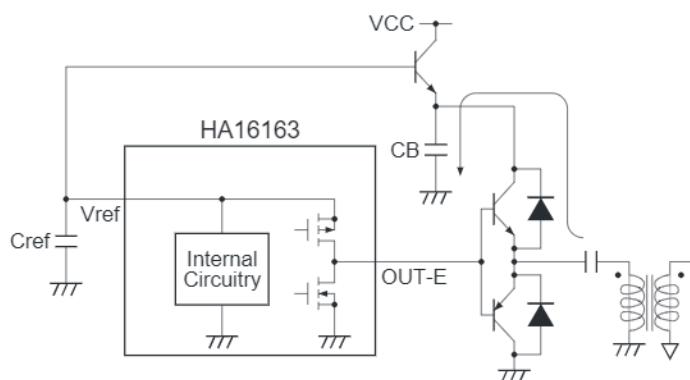

### Illustrative Circuit

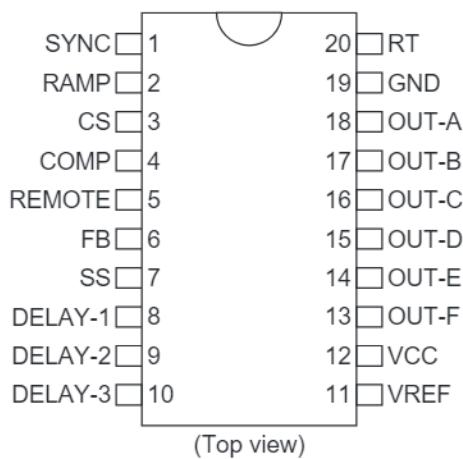

## Pin Arrangement

## Pin Functions

| Pin No. | Pin Name | Pin Function                                                         |

|---------|----------|----------------------------------------------------------------------|

| 1       | SYNC     | Synchronization I/O for the oscillator                               |

| 2       | RAMP     | Current sense signal input for the full-bridge control loop          |

| 3       | CS       | Current sense signal input for OCP                                   |

| 4       | COMP     | Error amplifier output                                               |

| 5       | REMOTE   | Remote on/off control                                                |

| 6       | FB       | Voltage feedback input                                               |

| 7       | SS       | Timing capacitor for both soft start and timer latch                 |

| 8       | DELAY-1  | Delay time adjustor for the full-bridge control signal (OUT-A and B) |

| 9       | DELAY-2  | Delay time adjustor for the full-bridge control signal (OUT-C and D) |

| 10      | DELAY-3  | Delay time adjustor for the secondary control signal (OUT-E and F)   |

| 11      | VREF     | 5 V/20 mA Output                                                     |

| 12      | VCC      | IC power supply input                                                |

| 13      | OUT-F    | Secondary control signal                                             |

| 14      | OUT-E    | Secondary control signal                                             |

| 15      | OUT-D    | Full-bridge control signal                                           |

| 16      | OUT-C    | Full-bridge control signal                                           |

| 17      | OUT-B    | Full-bridge control signal                                           |

| 18      | OUT-A    | Full-bridge control signal                                           |

| 19      | GND      | Ground level for the IC                                              |

| 20      | RT       | Timing resistor for the oscillator                                   |

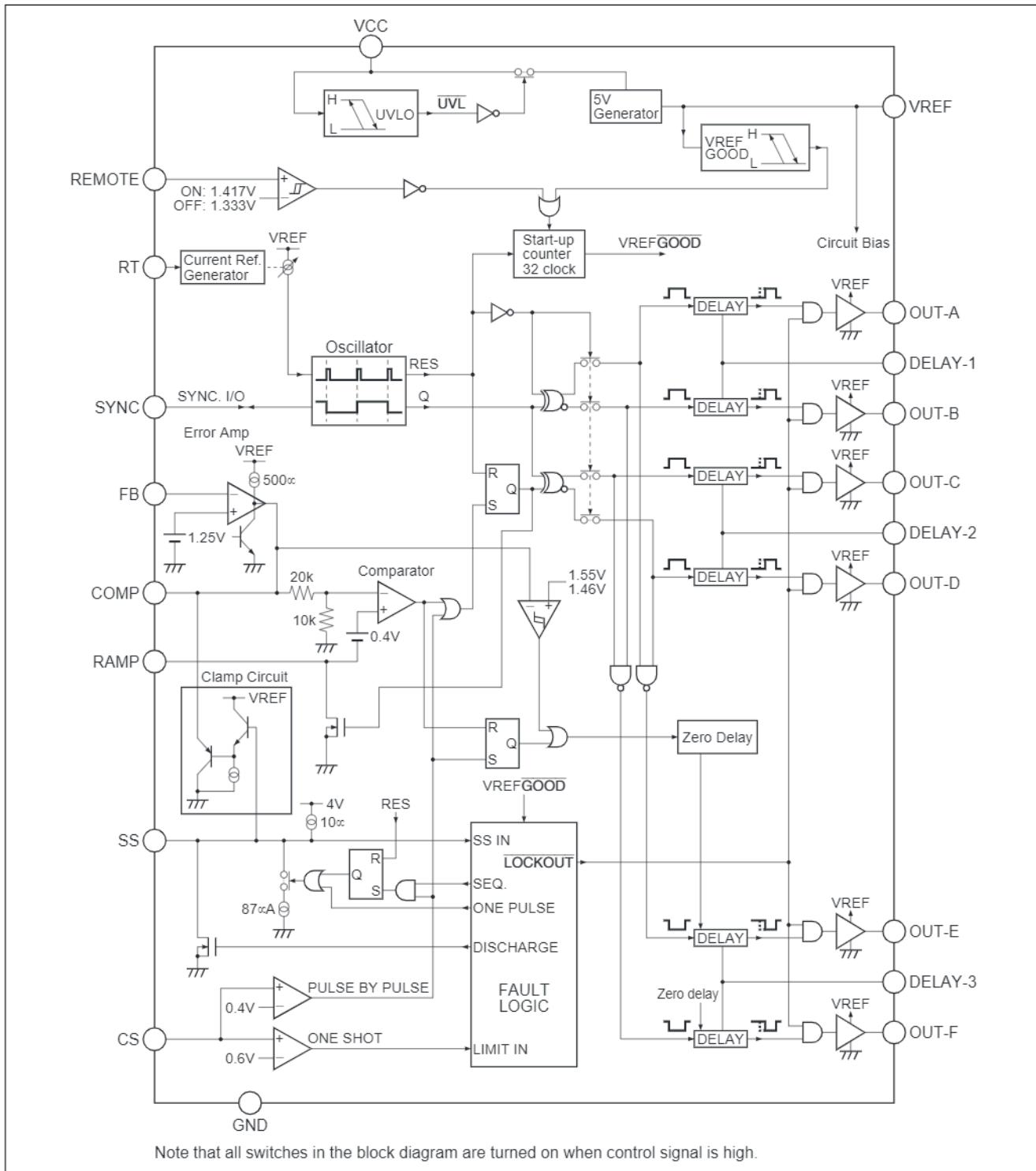

## Block Diagram

## Absolute Maximum Ratings

(Ta = 25°C)

| Item                           | Symbol     | Rating              | Unit | Note |

|--------------------------------|------------|---------------------|------|------|

| Power supply voltage           | Vcc        | 20                  | V    | 1    |

| Peak output current            | Ipk-out    | ±50                 | mA   | 2, 3 |

| DC output current              | Idc-out    | ±5                  | mA   | 3    |

| VREF output current            | Iref-out   | -20                 | mA   | 3    |

| COMP sink current              | Isink-comp | 2                   | mA   | 3    |

| DELAY set current              | Iset-delay | 0.3                 | mA   | 3    |

| RT set current                 | Iset-rt    | 0.3                 | mA   | 3    |

| VREF terminal voltage          | Vter-ref   | -0.3 to 6           | V    | 1, 4 |

| Terminal group 1 voltage       | Vter-1     | -0.3 to (Vref +0.3) | V    | 1, 5 |

| Operating junction temperature | Tj-opr     | -40 to +125         | °C   | 6    |

| Storage temperature            | Tstg       | -55 to +150         | °C   |      |

- Notes:

1. Rated voltages are with reference to the GND pin.

2. Shows the transient current when driving a capacitive load.

3. For rated currents, inflow to the IC is indicated by (+), and outflow by (-).

4. VREF pin voltage must not exceed VCC pin voltage.

5. Terminal group 1 is defined the pins;

REMOTE, CS, RAMP, COMP, FB, SS, RT, SYNC, DELAY-1 to 3, OUT-A to F

6.  $\theta_{ja}$

228°C/W Board condition; Glass epoxy 55 mm × 45 mm × 1.6 mm, 10% wiring density.

## Electrical Characteristics

(Ta = 25°C, Vcc = 12 V, RT = 33 kΩ, Rdelay = 51 kΩ, unless otherwise specified.)

| Item            | Symbol                              | Min                               | Typ   | Max                 | Unit  | Test Conditions |

|-----------------|-------------------------------------|-----------------------------------|-------|---------------------|-------|-----------------|

| Supply          | Start threshold                     | VH                                | 9.0   | 9.8                 | 10.6  | V               |

|                 | Shutdown threshold                  | VL                                | 7.3   | 7.9                 | 8.5   | V               |

|                 | UVLO hysteresis                     | dVUVL                             | 1.7   | 1.9                 | 2.1   | V               |

|                 | Start-up current                    | Is                                | —     | 90                  | 150   | µA              |

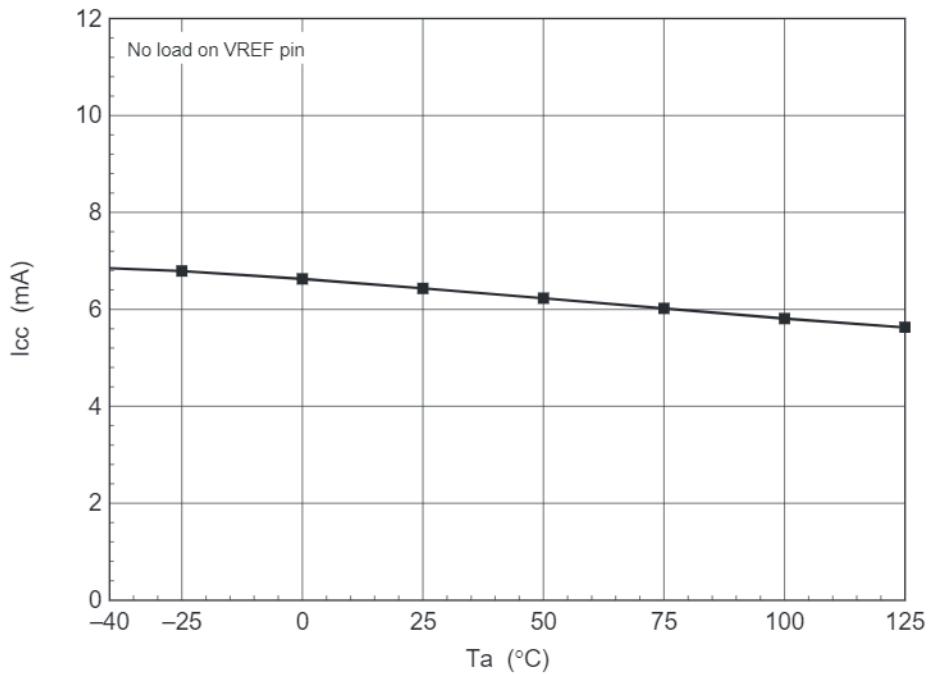

|                 | Operating current                   | Icc                               | —     | 7                   | 10    | mA              |

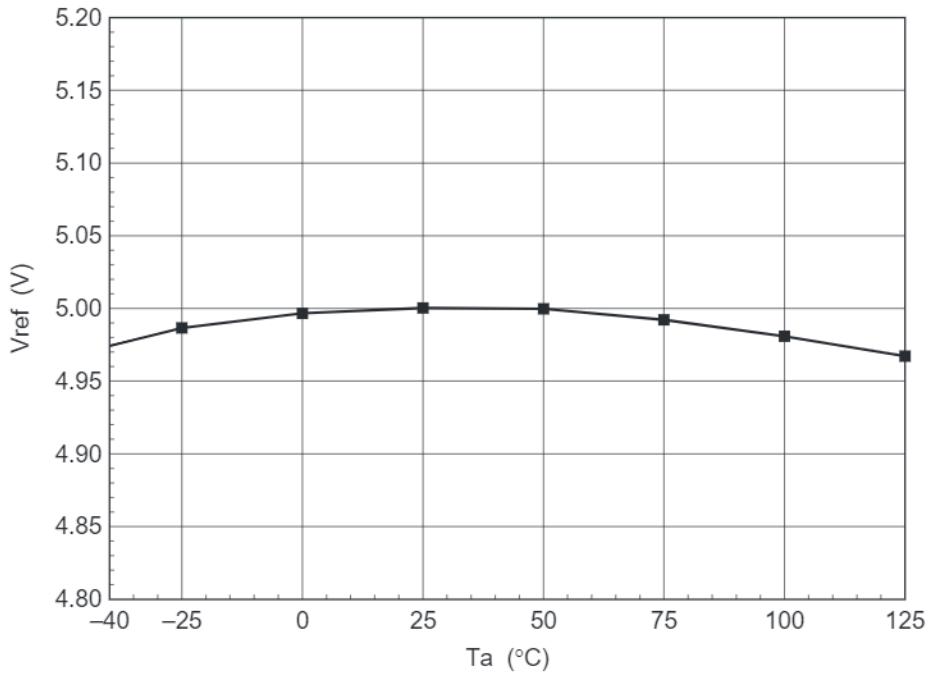

| VREF            | Output voltage                      | Vref                              | 4.9   | 5.0                 | 5.1   | V               |

|                 | Line regulation                     | Vref-line                         | —     | 0                   | 10    | mV              |

|                 | Load regulation                     | Vref-load                         | —     | 6                   | 20    | mV              |

|                 | Temperature stability               | dVref/dTa                         | —     | ±80 * <sup>1</sup>  | —     | ppm/°C          |

| Oscillator      | Oscillator frequency                | fosc                              | —     | 960 * <sup>1</sup>  | —     | kHz             |

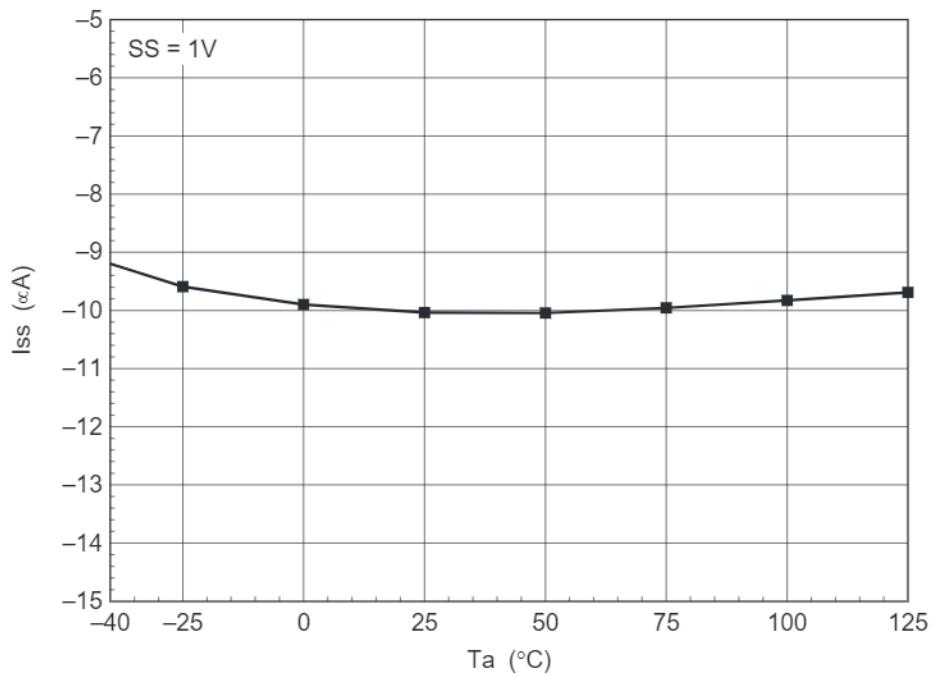

|                 | Switching frequency                 | fsw                               | 412   | 480                 | 547   | kHz             |

|                 | Line stability                      | fsw-line                          | -1.5  | 0                   | 1.5   | %               |

|                 | Temperature stability               | dfs <sub>w</sub> /dT <sub>a</sub> | —     | ±0.1 * <sup>1</sup> | —     | %/°C            |

|                 | RT voltage                          | VRT                               | 2.5   | 2.7                 | 2.9   | V               |

| SYNC            | Input threshold                     | V <sub>TH-SYNC</sub>              | 2.5   | 2.85                | 3.2   | V               |

|                 | Output high                         | V <sub>OH-SYNC</sub>              | 3.5   | 4.0                 | —     | V               |

|                 | Output low                          | V <sub>OL-SYNC</sub>              | —     | 0.05                | 0.15  | V               |

|                 | Minimum input pulse                 | T <sub>i-MIN</sub>                | 50    | —                   | —     | ns              |

|                 | Output pulse width                  | T <sub>o-SYNC</sub>               | —     | 500                 | —     | ns              |

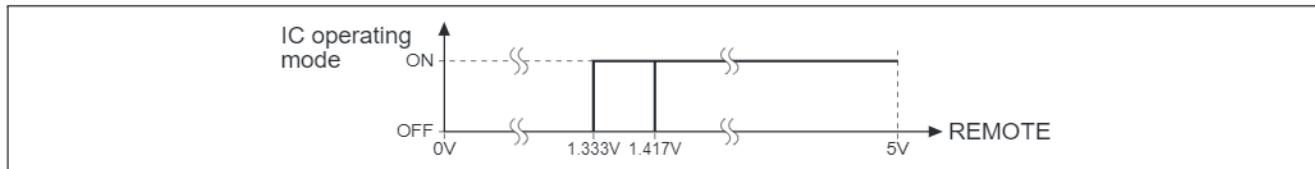

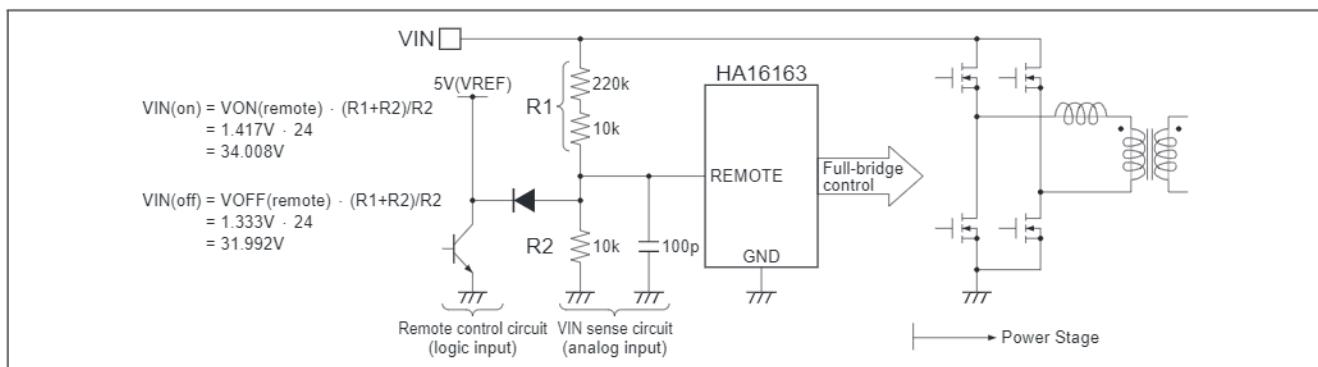

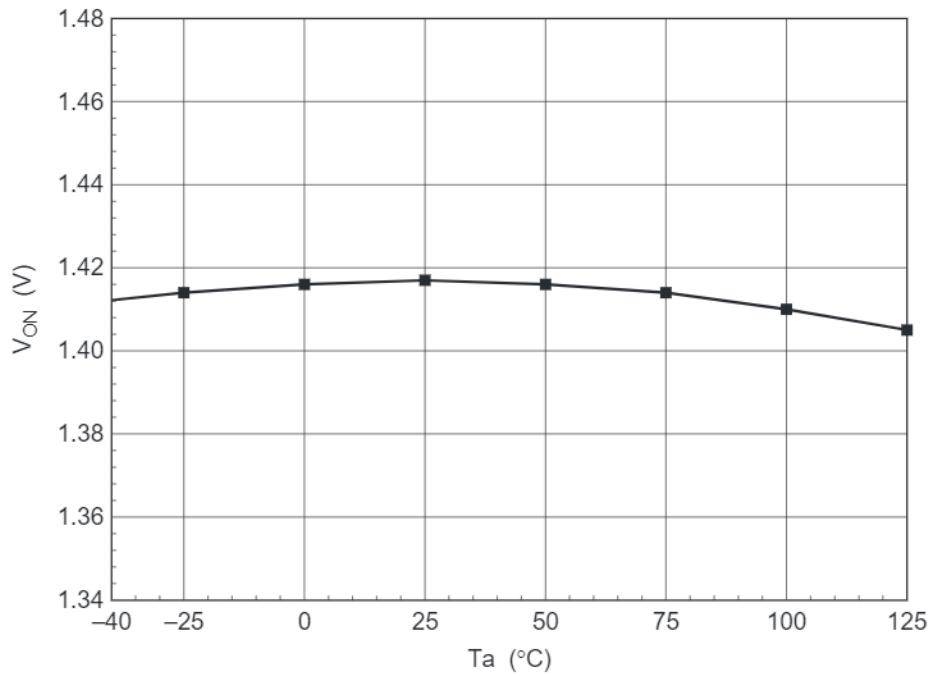

| Remote          | On threshold voltage                | V <sub>ON</sub>                   | 1.374 | 1.417               | 1.460 | V               |

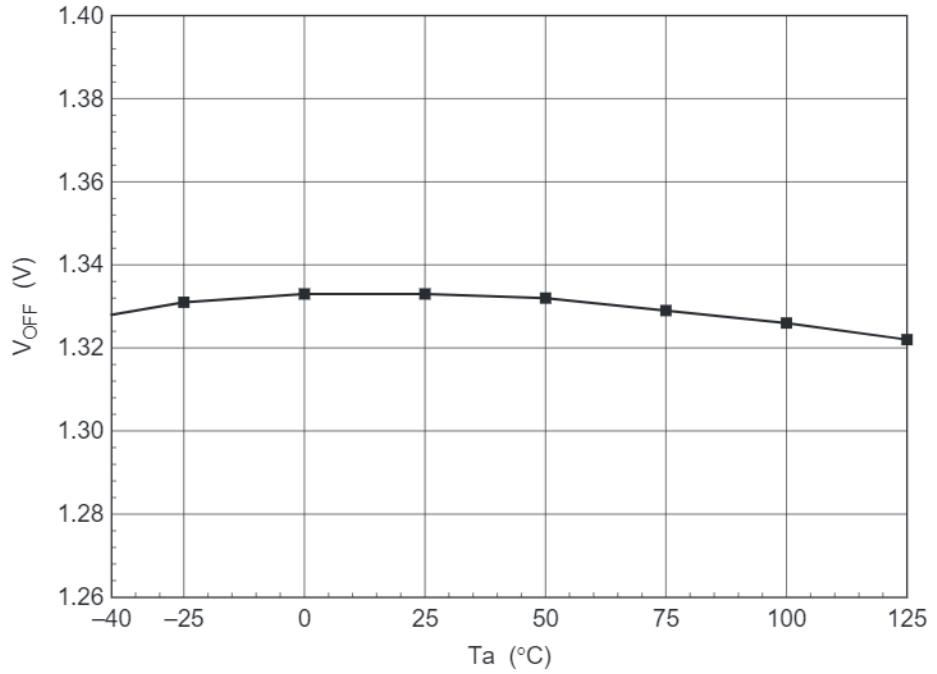

|                 | Off threshold voltage               | V <sub>OFF</sub>                  | 1.293 | 1.333               | 1.373 | V               |

| Error amplifier | Input bias current                  | I <sub>REMOTE</sub>               | 0     | 0.4                 | 2     | µA              |

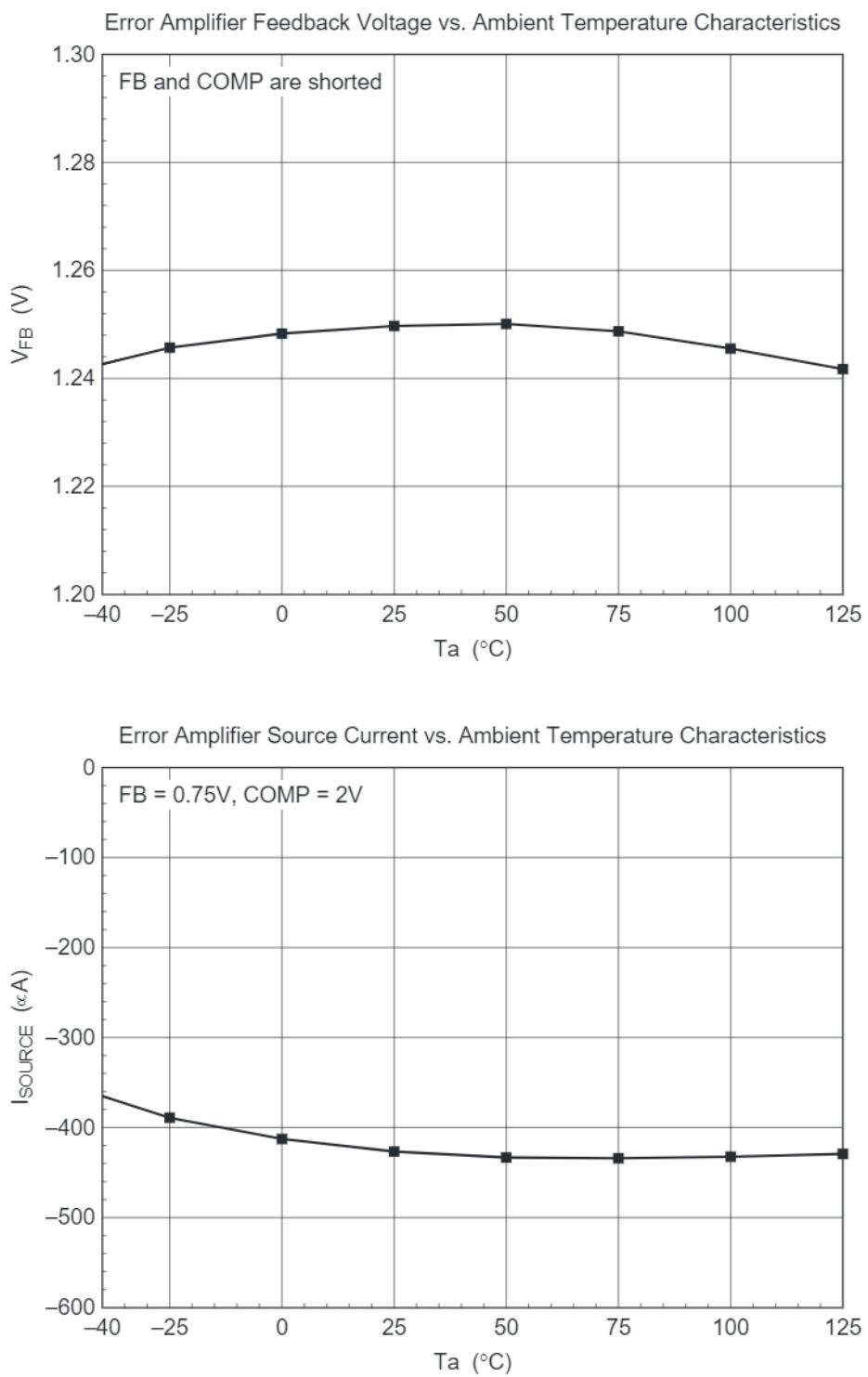

|                 | FB input voltage                    | V <sub>FB</sub>                   | 1.225 | 1.250               | 1.275 | V               |

|                 | FB input current                    | I <sub>FB</sub>                   | -1.0  | 0                   | 1.0   | µA              |

|                 | Open-loop DC gain                   | A <sub>v</sub>                    | —     | 80 * <sup>1</sup>   | —     | dB              |

|                 | Unity gain bandwidth                | BW                                | —     | 2 * <sup>1</sup>    | —     | MHz             |

|                 | Output source current               | I <sub>SOURCE</sub>               | -610  | -430                | -350  | µA              |

|                 | Output sink current                 | I <sub>SINK</sub>                 | 2.0   | 6.5                 | —     | mA              |

|                 | Output high voltage                 | V <sub>OH-EO</sub>                | 3.7   | 3.9                 | —     | V               |

|                 | Output low voltage                  | V <sub>OL-EO</sub>                | —     | 0.1                 | 0.4   | V               |

|                 | Output clamp voltage * <sup>2</sup> | V <sub>CLAMP-EO</sub>             | -0.16 | -0.07               | 0.0   | V               |

Notes: 1. Reference values for design. Not 100% tested in production.

2. V<sub>CLAMP-EO</sub> = V<sub>COMP</sub> – SS voltage (1V)

## Electrical Characteristics (cont.)

(Ta = 25°C, Vcc = 12 V, RT = 33 kΩ, Rdelay = 51 kΩ, unless otherwise specified.)

| Item            |                                   | Symbol     | Min  | Typ                                | Max  | Unit | Test Conditions        |

|-----------------|-----------------------------------|------------|------|------------------------------------|------|------|------------------------|

| Phase modulator | RAMP offset voltage               | VRAMP      | —    | 0.4 * <sup>1</sup>                 | —    | V    |                        |

|                 | RAMP bias current                 | IRAMP      | -5   | -0.8                               | 5    | μA   | RAMP = 0.3V            |

|                 | RAMP sink current                 | ISINK-RAMP | 8    | 26                                 | —    | mA   | RAMP = 1V, COMP = 0V   |

|                 | Minimum phase shift               | Dmin       | —    | 0 * <sup>1</sup> * <sup>4</sup>    | —    | %    | RAMP = 1V, COMP = 0V   |

|                 | Maximum phase shift               | Dmax       | —    | 97.0 * <sup>1</sup> * <sup>4</sup> | —    | %    | RAMP = 0V, COMP = 2.1V |

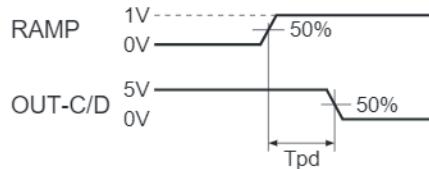

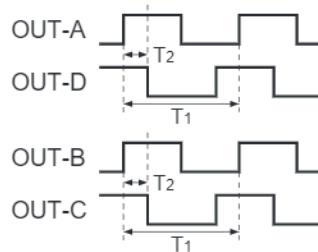

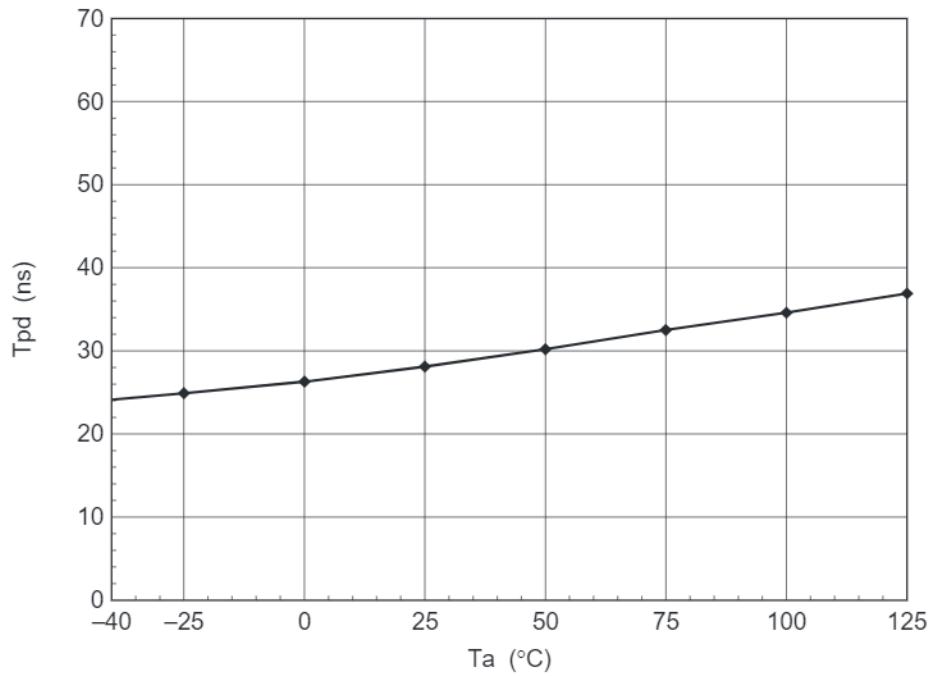

|                 | Delay to OUT-C, -D * <sup>2</sup> | Tpd        | —    | 30                                 | 60   | ns   | COMP = 2.1V            |

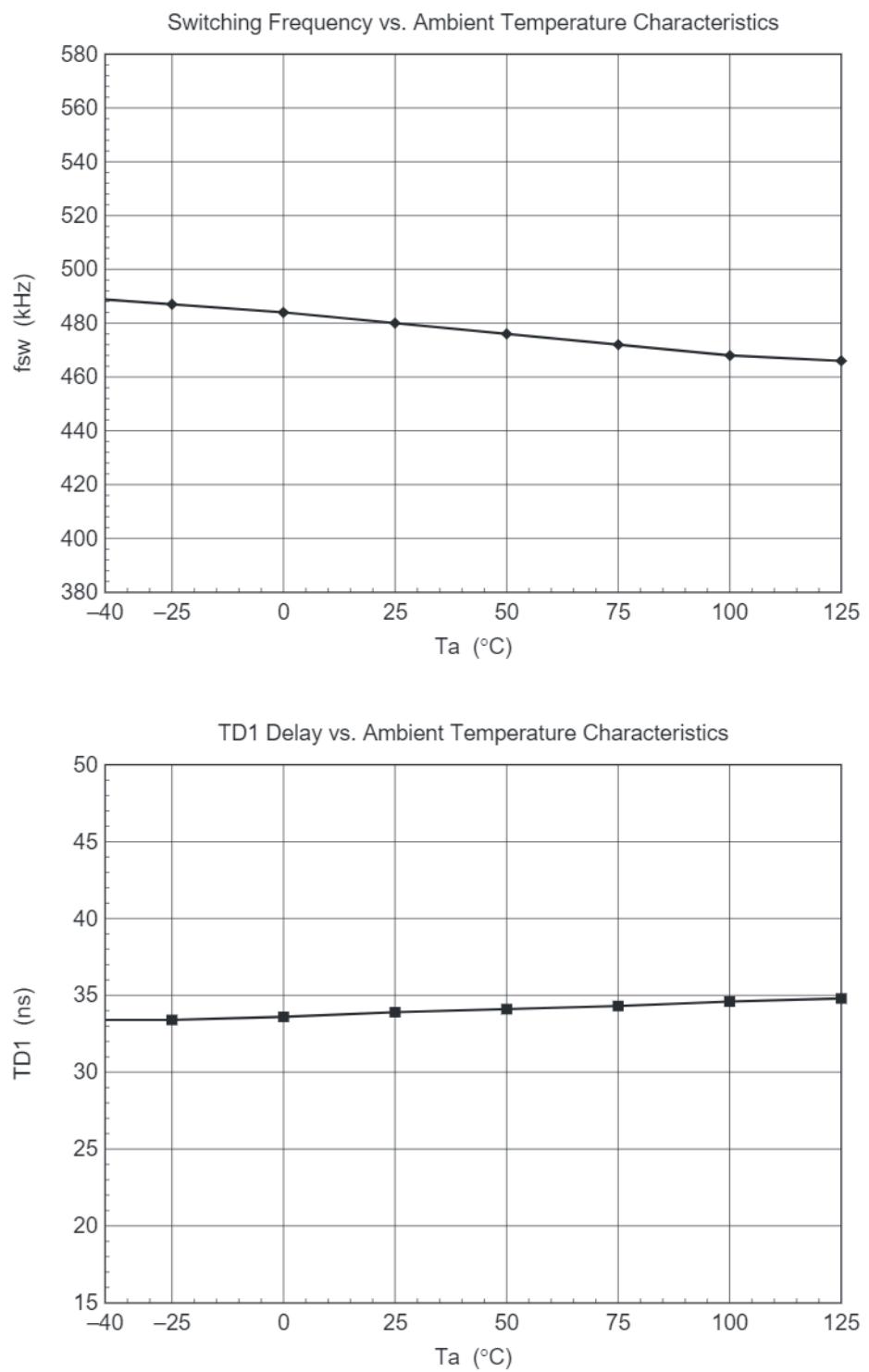

| Delay           | DELAY-1, -2, -3 * <sup>3</sup>    | TD1, 2, 3  | 22   | 33.5                               | 45   | ns   | Delay set R = 51k      |

|                 | Terminal voltage                  | VD1, 2, 3  | 1.9  | 2.0                                | 2.1  | V    | Delay set R = 51k      |

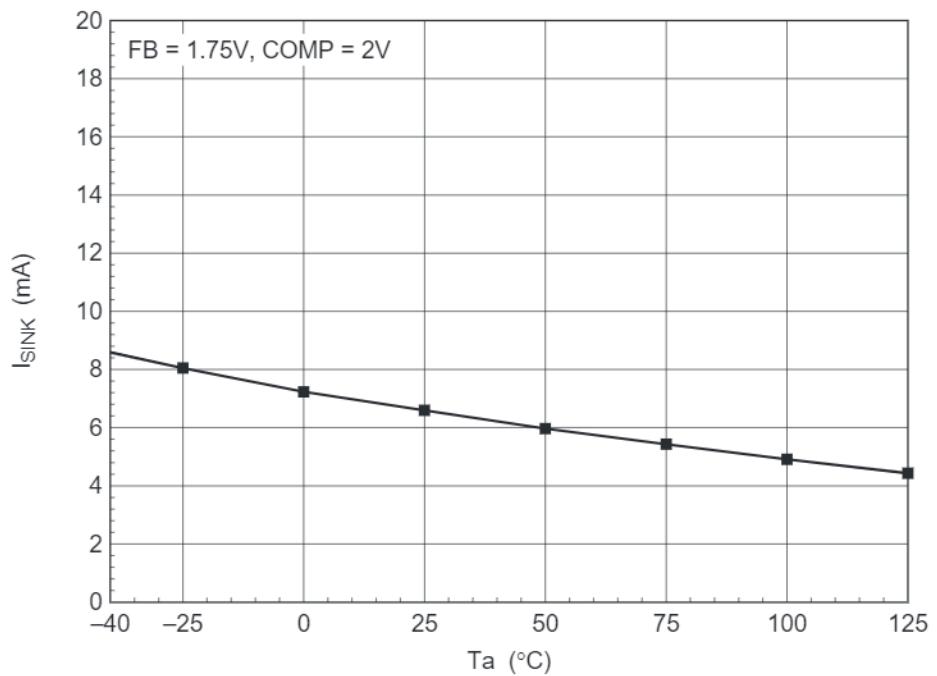

| Soft start      | Source current                    | ISS        | -14  | -10                                | -6   | μA   | SS = 1V                |

|                 | Discharge current                 | IRES-SS    | 5    | 10                                 | —    | mA   | SS = 1V, REMOTE = 0V   |

|                 | Soft-start reset voltage          | VRES-SS    | 0.25 | 0.40                               | 0.55 | V    | Measured on SS         |

|                 | SS high voltage                   | VOH-SS     | 3.9  | 4.0                                | 4.1  | V    |                        |

Notes: 1. Reference values for design. Not 100% tested in production.

2. Tpd is defined as;

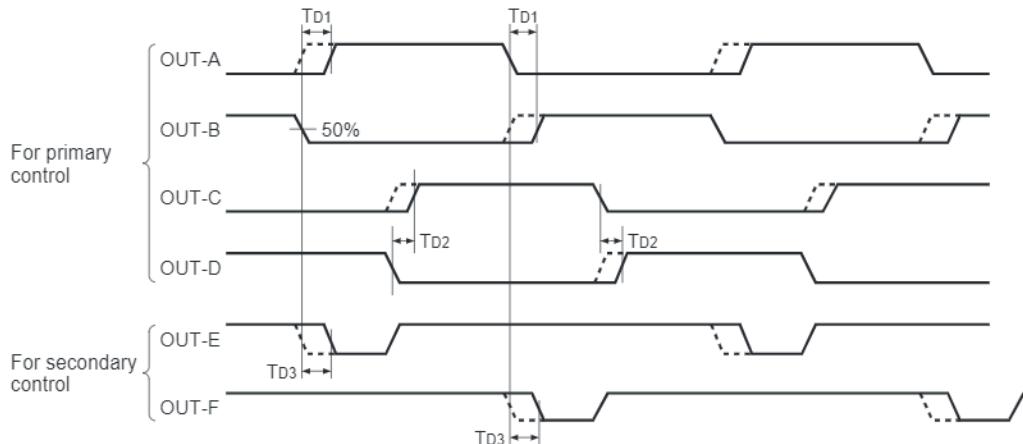

3. TD1, 2, 3 are defined as;

4. Maximum/Minimum phase shift is defined as;

$$D = \frac{T_2}{T_1} \times 2 \times 100 \text{ (%)}$$

## Electrical Characteristics (cont.)

(Ta = 25°C, Vcc = 12 V, RT = 33 kΩ, Rdelay = 51 kΩ, unless otherwise specified.)

| Item                    |                                        | Symbol               | Min  | Typ             | Max  | Unit | Test Conditions                        |

|-------------------------|----------------------------------------|----------------------|------|-----------------|------|------|----------------------------------------|

| Over current protection | Pulse-by-pulse current limit threshold | VCS-PP               | 0.36 | 0.40            | 0.44 | V    |                                        |

|                         | One-shot OCP threshold                 | VCS-SD               | 0.54 | 0.60            | 0.66 | V    |                                        |

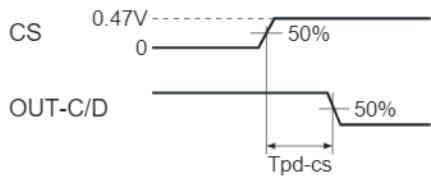

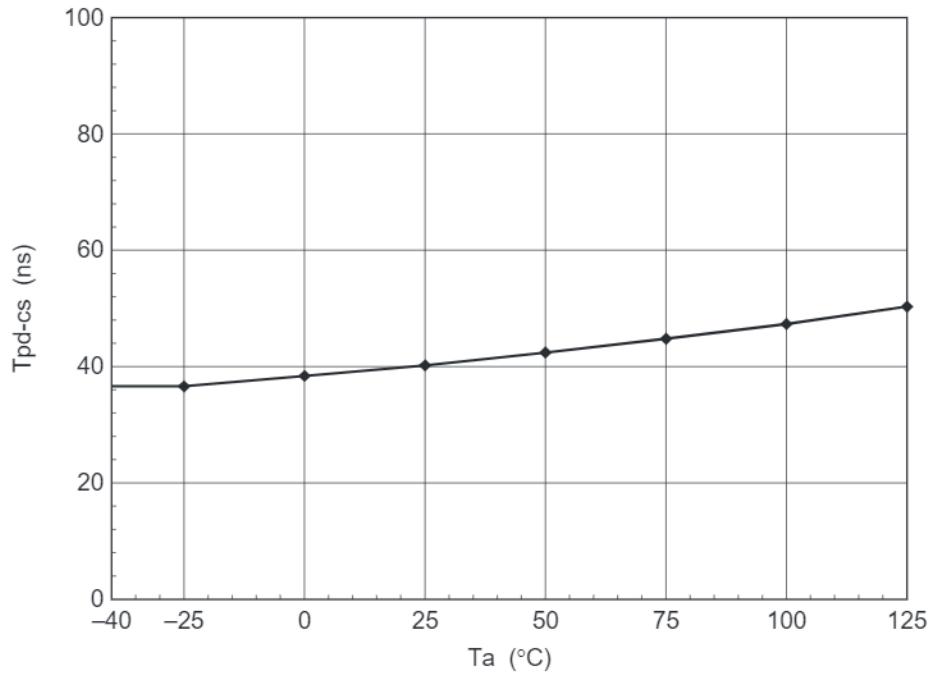

|                         | Delay to OUT pins <sup>*1</sup>        | Tpd-cs               | —    | 40              | 80   | ns   | CS = 0V to 0.47V                       |

|                         | Timer latch integration time           | TTL                  | 44   | 63              | 82   | μs   | CS = 0.47V step function, SS = 0.022μF |

| Output                  | High voltage                           | V <sub>OH</sub> -OUT | 4.3  | 4.8             | —    | V    | I <sub>OUT</sub> = -5mA                |

|                         | Low voltage                            | V <sub>OL</sub> -OUT | —    | 0.1             | 0.4  | V    | I <sub>OUT</sub> = 5mA                 |

|                         | Rise time                              | tr                   | —    | 5               | 15   | ns   | C <sub>OUT</sub> = 33pF                |

|                         | Fall time                              | tf                   | —    | 5               | 15   | ns   | C <sub>OUT</sub> = 33pF                |

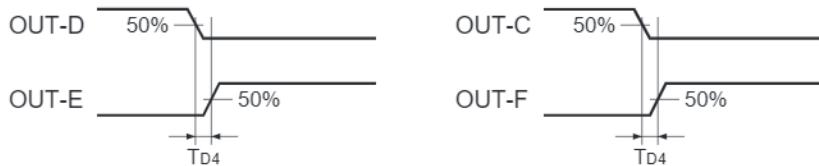

|                         | Timing offset <sup>*2</sup>            | TD4                  | —    | 3 <sup>*3</sup> | —    | ns   |                                        |

Notes: 1. Tpd-cs is defined as;

2. TD4 is defined as;

3. Reference values for design. Not 100% tested in production.

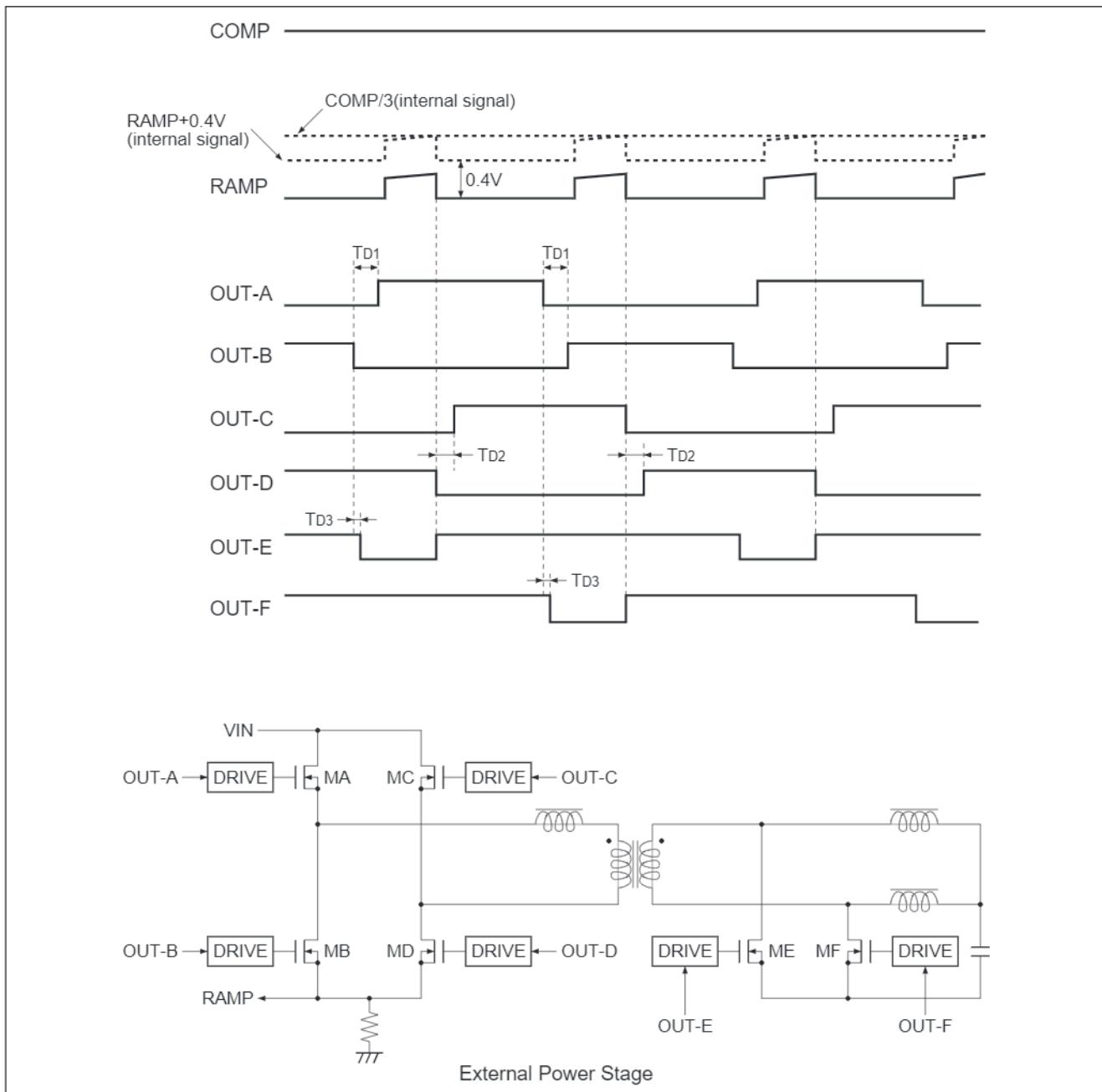

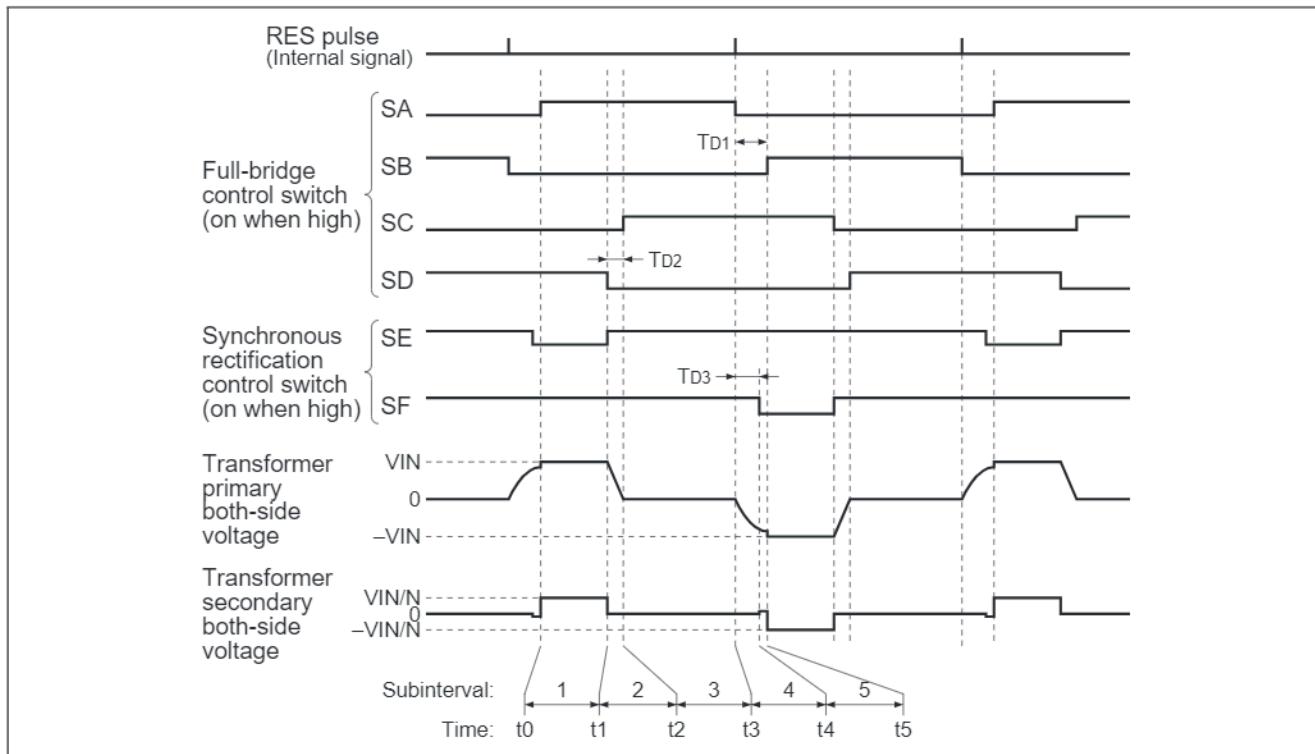

## Timing Diagram

Note: All voltage, current, time shown in the diagram is typical value.

### Full Bridge and Secondary Control

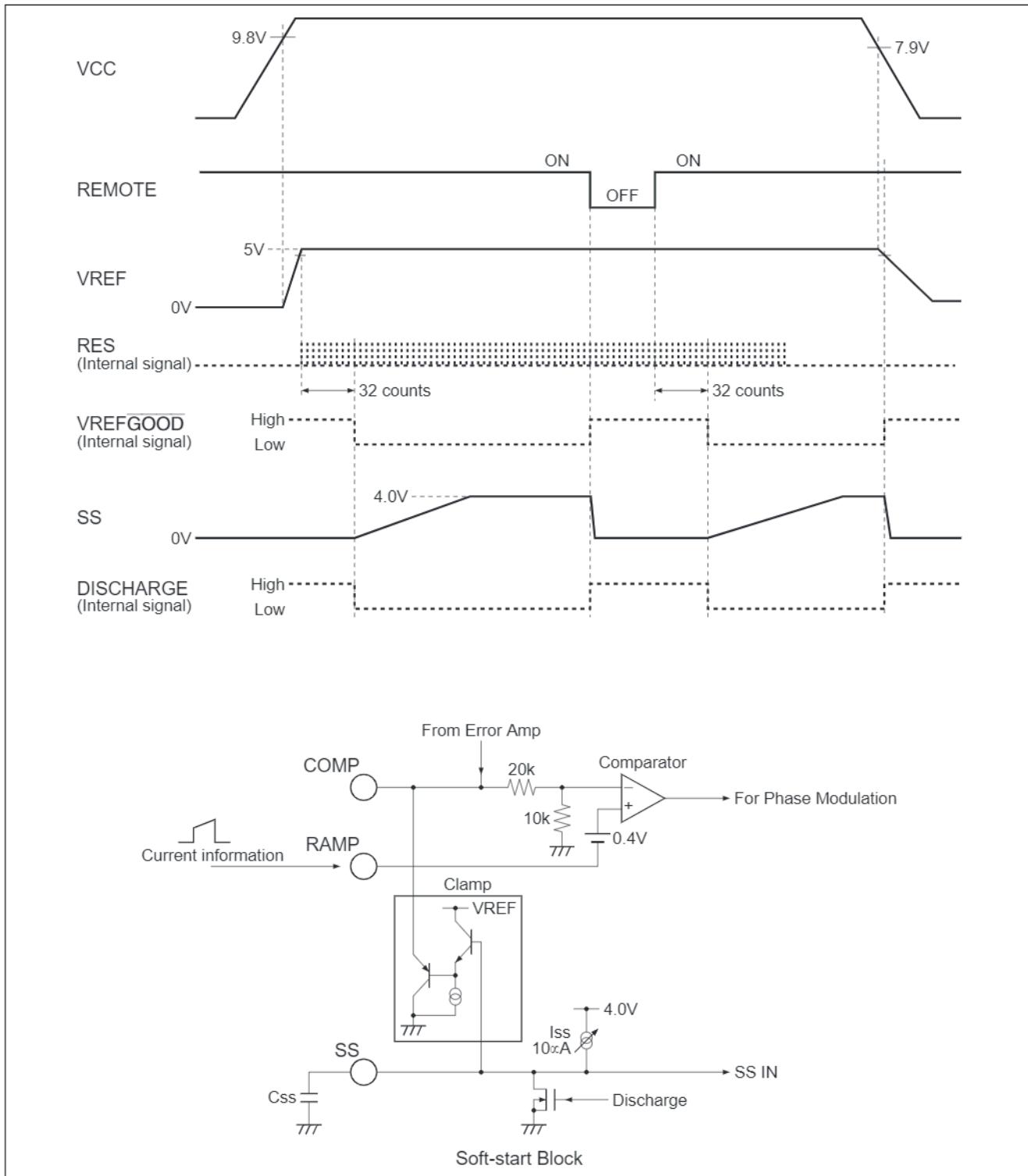

## Start-up and Shutdown

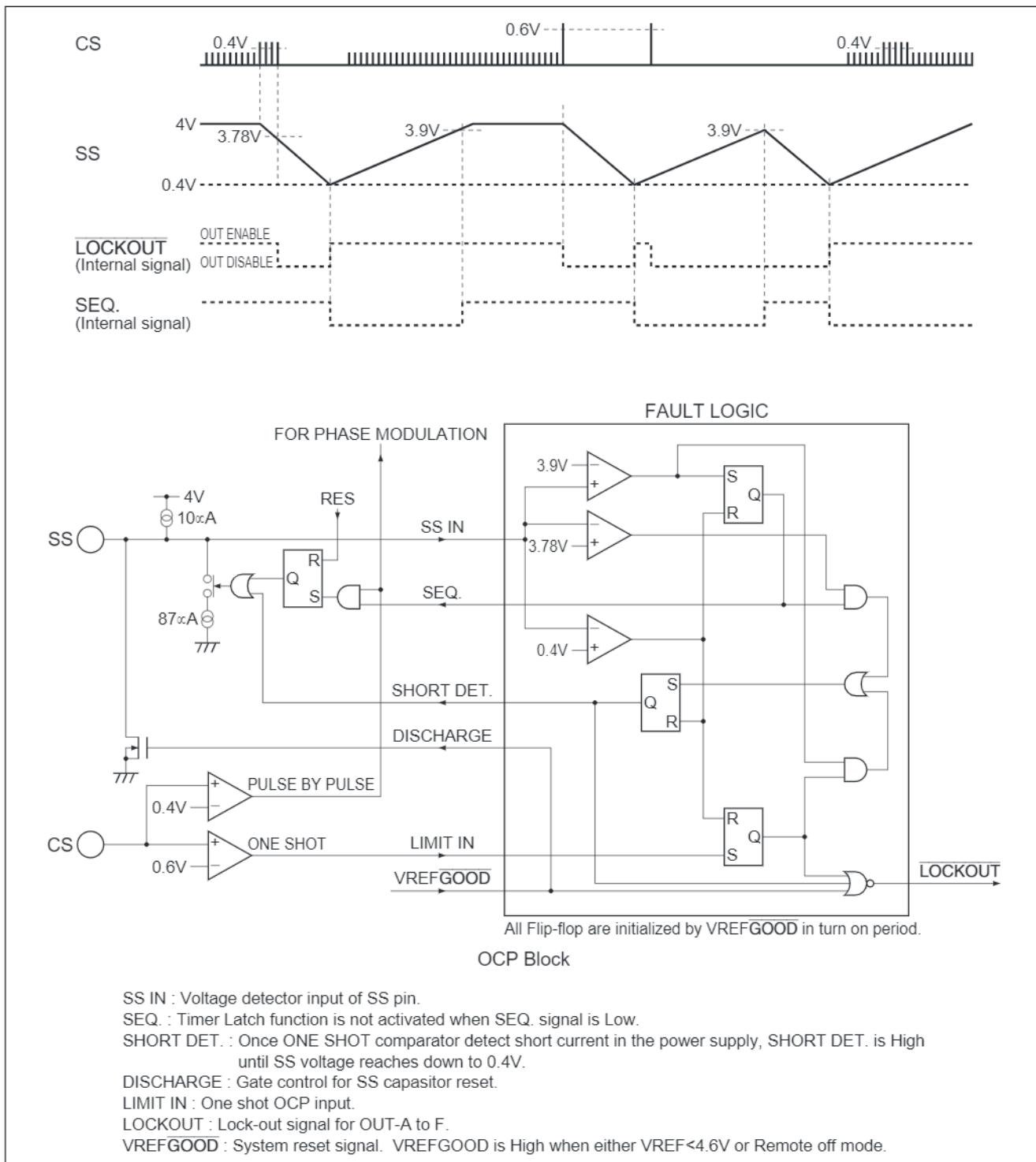

## Timer Latch and One Shot OCP

## Functional Description

Note: All voltage, current, time shown in the diagram is typical value unless otherwise noted.

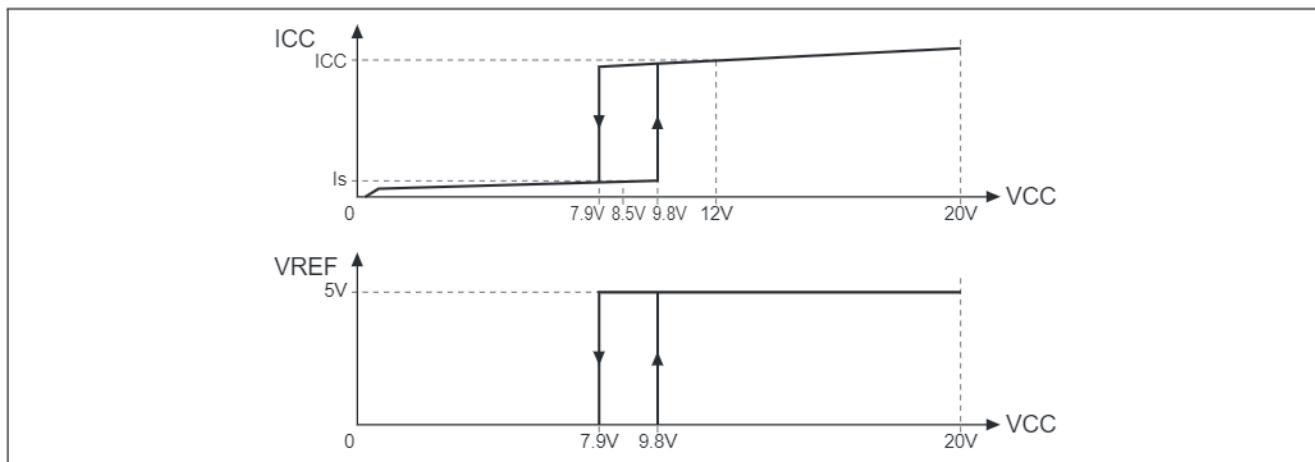

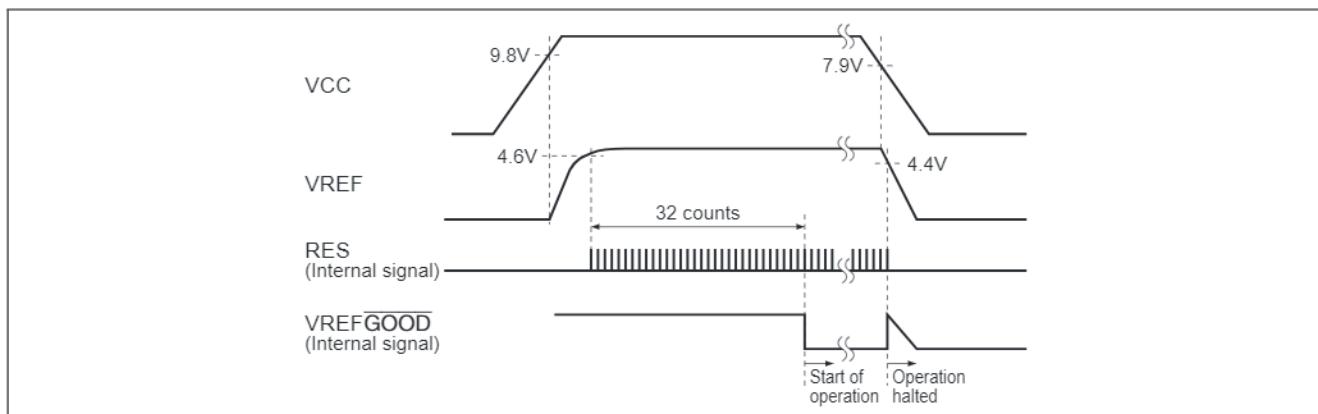

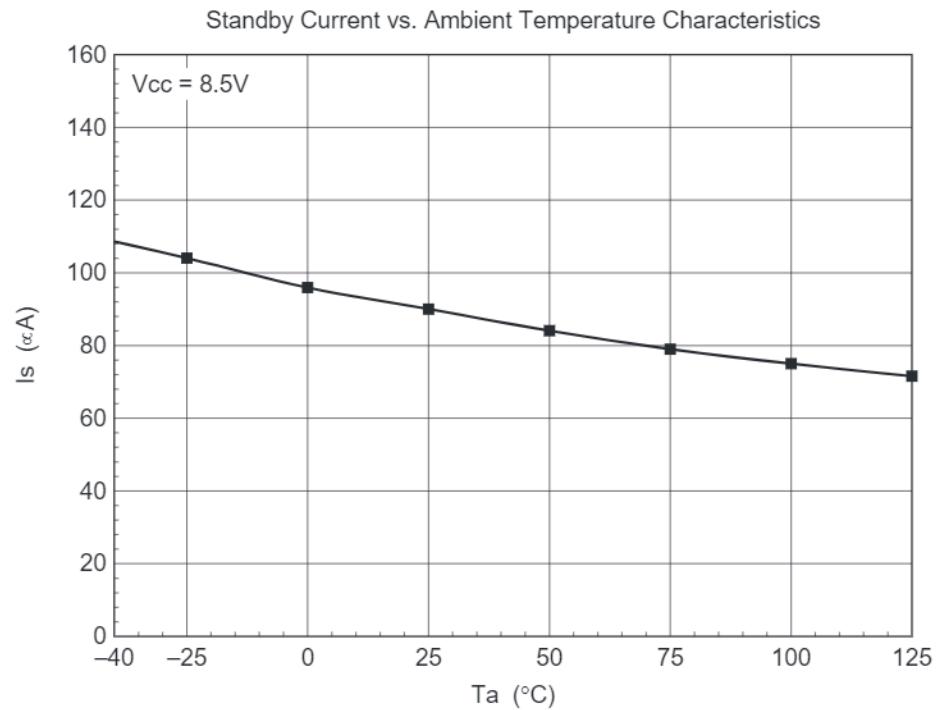

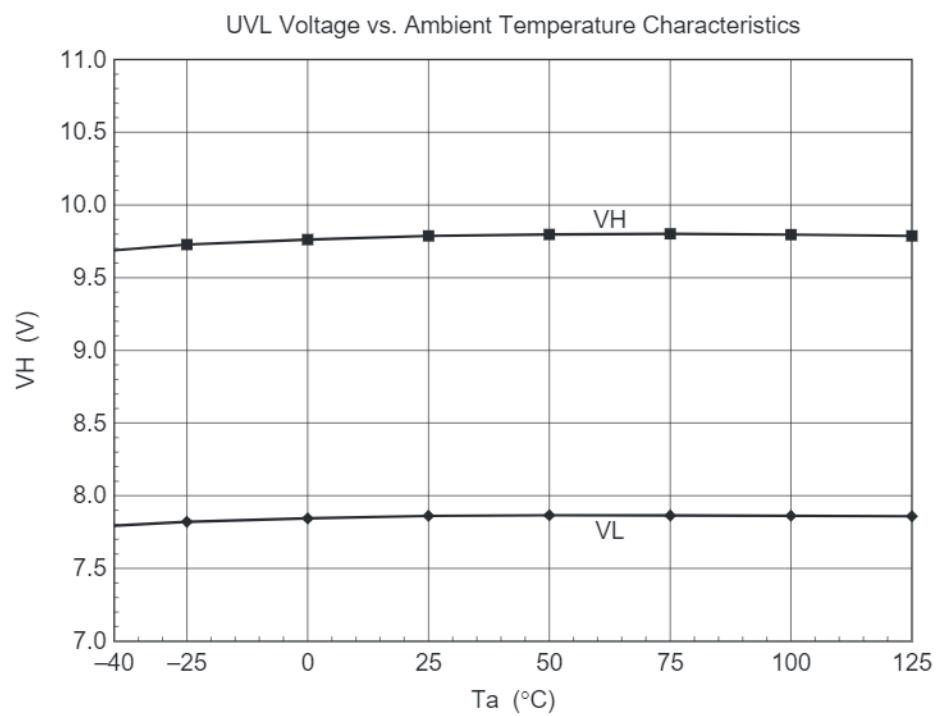

### UVLO

UVLO (Under Voltage Lockout Operation) is a function that halts operation of the IC in the event of a low IC power supply voltage.

When IC operation is halted, the 5 V internal voltage generation circuit (VREF) halts, and therefore operation of circuitry using VREF as the operating power supply halts. Circuit blocks other than UVLO use VREF as their operating power supply. Therefore, the power supply current of the IC becomes equal to the current dissipated by the UVLO circuit. The following graphs show the relationship between the VCC input current and VCC input voltage, and between VREF and the VCC input voltage.

Figure 1

### REMOTE

IC outputs (OUT-A through OUT-F) can be halted by means of the REMOTE pin. In this case, the IC output logic level is low.

In the remote off state, VREF output is not halted, and therefore the current dissipation of the IC does not decrease to the start-up level. Also, control by means of the REMOTE pin is not possible when the IC has been halted by UVLO. The soft start capacitance is discharged in the remote off state. Therefore, operation begins from soft start mode when the next remote on operation is performed. The relationship between the REMOTE pin and the operating mode of the IC is shown in the following figure.

Figure 2

The remote on and off threshold voltages are provided with hysteresis of 84 mV (typ). Remote control can be performed by means of analog input as shown in the diagram below as well as by means of logic control. The following diagram shows an example in which the power supply set input voltage is sensed by means of the REMOTE pin, and the power supply set start-up voltage is set to 34 V, and the shutdown voltage to 32 V.

Figure 3

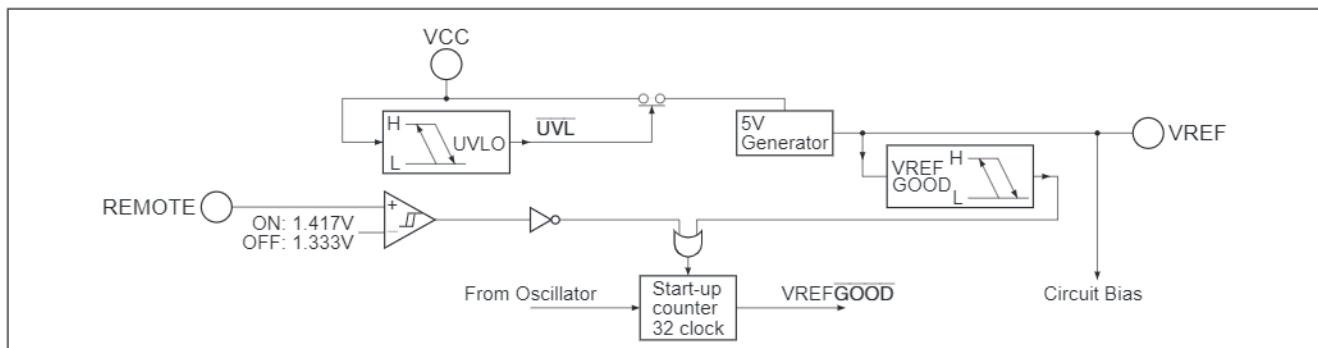

## Start-up Counter

When the **VREFGOOD** signal (internal signal) goes to the logic low level, the HA16163 starts operating as a controller. The **VREFGOOD** signal is created from the REMOTE comparator and **VREFGOOD** circuit output via a 32-clock start-up counter.

**Figure 4**

Therefore, the start of IC operation is a 32-count later than UVLO release or the remote on trigger. When the oscillator frequency is set to 1 MHz, this represents a delay of 32  $\mu$ s. This delay enables operation to be halted until VREF (5 V) stabilizes when UVLO is released. Note that the start-up counter operates when VREF rises or when a remote on operation is performed, but does not operate when VREF falls or when a remote off operation is performed (there is no logic delay due to the start-up counter).

Figure 5

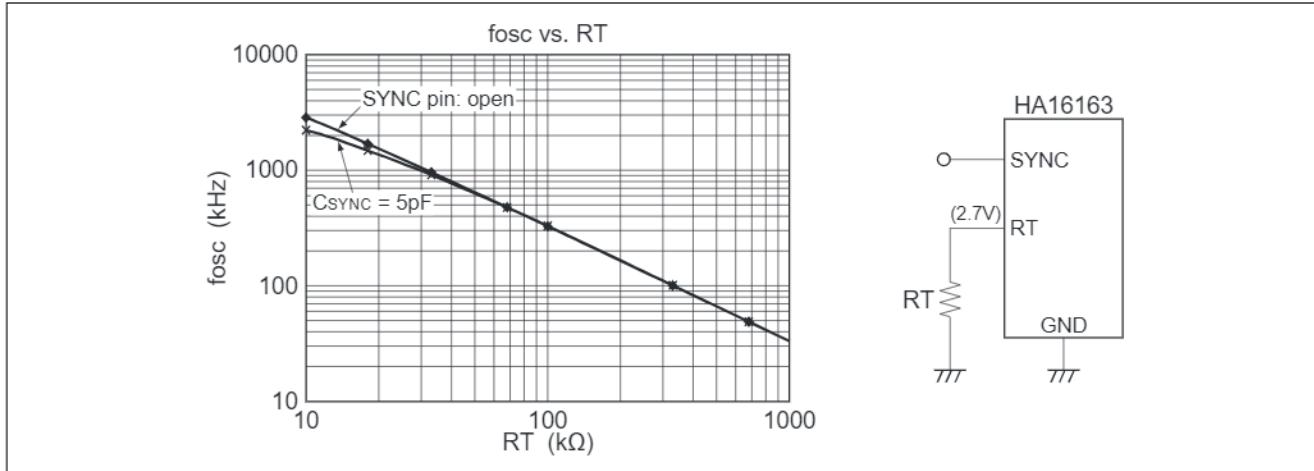

## Oscillator

The oscillation frequency of the oscillator is set by means of a resistance connected between the RT pin and GND. The following graph shows the relationship between the external resistance and the oscillation frequency. The typical value of the oscillation frequency is given by the following equation.

$$f_{osc} = \frac{1}{30p[F] \times RT[\Omega] + 50[ns]} \quad [\text{Hz}]$$

**Figure 6**

Place the resistor for connection to the RT pin as close to the pin as is possible. Please design the pattern so that the level of cross-talk from other signals is minimized.

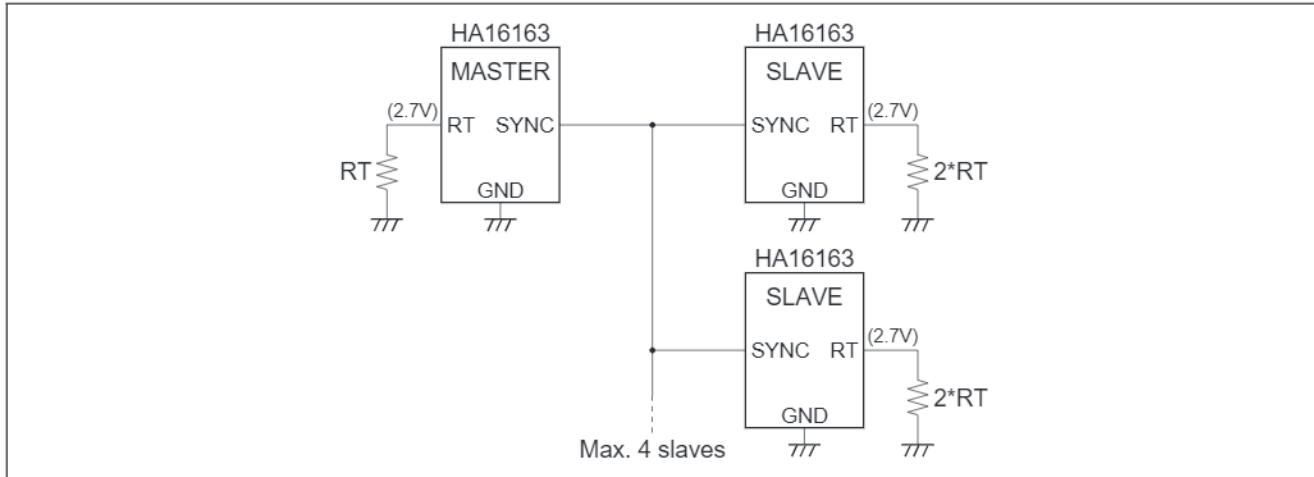

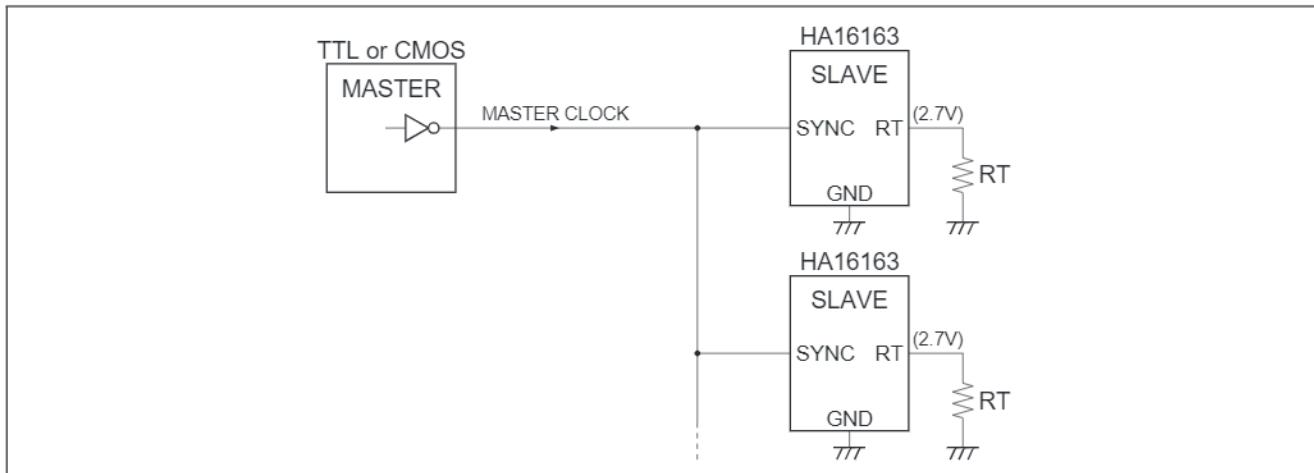

## Synchronized Operation

Parallel synchronized operation is possible by connecting the SYNC pins of HA16163s. In this case, up to four slave ICs can be connected to one master IC. A value of at least twice the master RT value should be set for the slave IC RT values.

**Figure 7 Parallel Synchronized Operation**

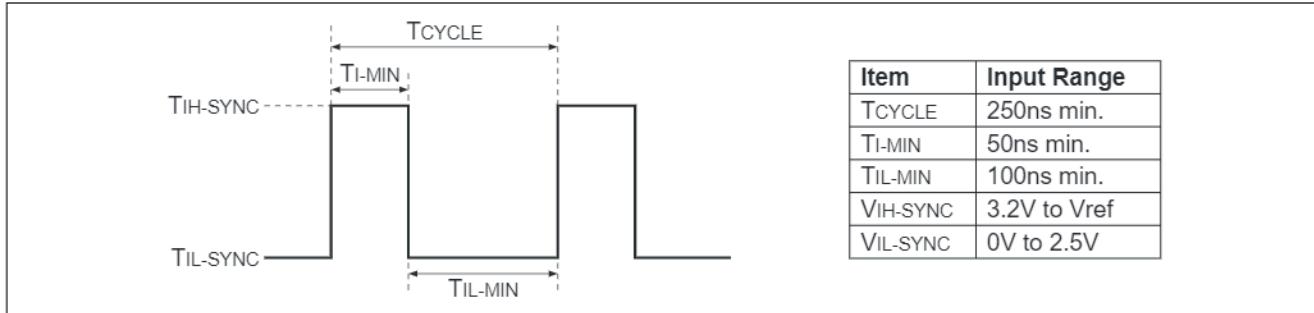

External synchronized operation is possible by supplying a synchronization signal to the SYNC pins of HA16163s. In this case, a frequency not exceeding 1/2 that of the master clock should be set for the HA16163s. A maximum master clock frequency of 4 MHz should be used. See the figure below for the input waveform conditions.

Figure 8 External Synchronized Operation

Figure 9 SYNC Pin Input Conditions

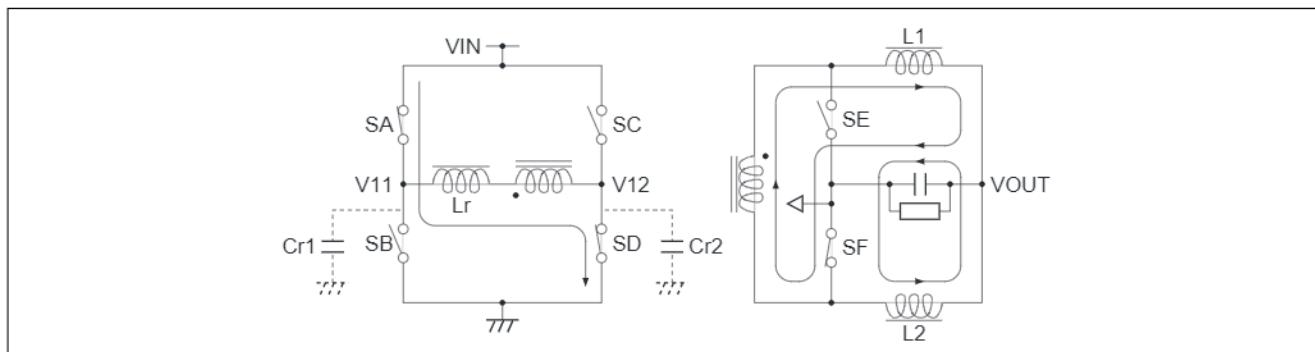

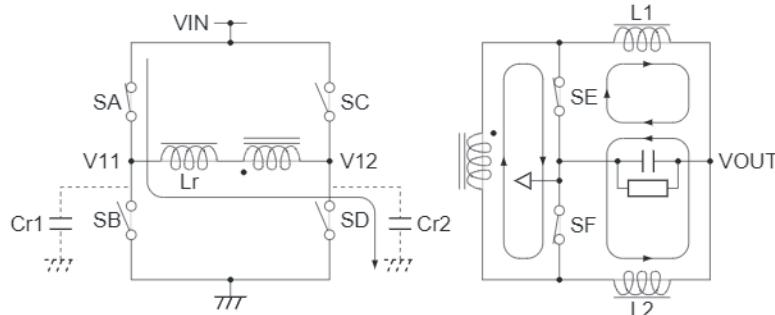

### Synchronous Phase Shift Full-Bridge Control

The HA16163 is provided with full-bridge control outputs OUT-A through OUT-D, and secondary-side synchronous rectification control outputs OUT-E and OUT-F. ZVS (Zero Voltage Switching) can be performed by adjusting timing delays  $T_{D1}$  and  $T_{D2}$  between the OUT-A through OUT-D outputs by means of an external resistance. OUT-E and OUT-F have an output timing suitable for secondary-side full-wave rectification, and so can be used in either current doubler or center tap applications. The following figure shows full-bridge ZVS + current doubler operation using an ideal model.

Figure 10

- Subinterval:1

In interval 1, SA and SD are turned on, and VIN is generated on the transformer primary side. On the transformer secondary side, a value proportional to the winding ratio is generated, and the primary-side power is transmitted to the load side.

At this time, secondary-side switch SE is off and SF is on.

Subinterval: 1

- Subinterval:2

As SD is turned off at point t1, the primary-side current flows into resonant capacitance Cr2. At this time Cr2 is charged, and therefore the potential of V12 rises. Considering that the exciting current and the L1 and L2 ripple currents are considerably smaller than Io, the following is an approximate equation for the slope of V12.

$$\frac{dV12}{dt} = \frac{0.5 Io}{N} \cdot \frac{1}{Cr2} \quad [\text{V/s}] \quad \dots\dots(1)$$

Here, N is the ratio of the primary coil to the secondary coil ( $N = N1/N2$ ), and Io is the output current.

As SE and SF are on, the transformer secondary side is in the shorted state, and the value of the current flowing up to that time is retained.

### Subinterval: 2

- Subinterval:3

SC is turned on at point t2. ZVS operation can be attained by setting the SD off (t2)  $\rightarrow$  SC on (t3) delay to the optimal value. This delay time can be expressed by equation (2).

$$TD2 = \frac{N}{0.5 Io} \cdot Cr2 \cdot VIN \quad [\text{s}] \quad \dots\dots(2)$$

After SC is turned on, the transformer primary side is in the shorted state, and therefore the current value immediately after SC was turned on is retained.

### Subinterval: 3

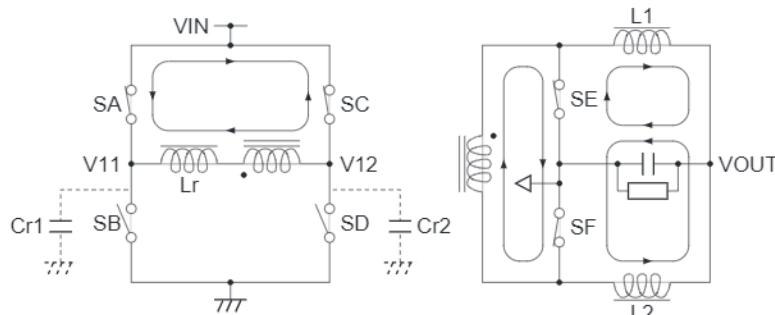

- Subinterval:4

As SA is turned off at point t3, the primary-side current discharges resonant capacitance Cr1, and the potential of V11 falls. A negative potential is applied to resonant inductor Lr, and a flux reset starts. At this time, since the series resonance circuit is composed of Cr1 and Lr, the V11 waveform changes to a sine wave. The resonance frequency is given by equation (3).

$$f_r = \frac{1}{2\pi \sqrt{(Cr1 \cdot Lr)}} \text{ [Hz]} \quad \dots(3)$$

## Subinterval: 4

- Subinterval:5

When synchronous switch SF is turned off at point t4, the current flowing in SF up to that time continues to flow through the SF body diode. SF turn-off must be performed before completion of the resonant inductor Lr flux reset. If SF is not off on completion of the Lr flux reset, power transmission will be performed with the transformer secondary-side shorted, and therefore an excessive current will flow in the transformer primary and secondary sides, and parts may be damaged.

Also, if the SF body diode is on for a long period, loss will be high. Therefore, optimal timing should be set by means of the HA16163's delay adjustment pin, **DELAY-3**.

Lr reset time tr is given by equation (4) when the resonance voltage peak value is within the input voltage.

$$\begin{aligned} t_{reset}(Lr)|_{Vpp \leq VIN} &= \frac{1}{4} \cdot \frac{1}{f_r} \\ &= 0.5\pi \sqrt{(Cr1 \cdot Lr)} \text{ [s]} \dots(4) \end{aligned}$$

Here, vpp is the resonance voltage peak value.

$$vpp = \frac{Io}{2} \cdot \frac{1}{N} \cdot \sqrt{(Lr/Cr1)} \text{ [V]} \quad \dots(5)$$

## Subinterval: 5

- Time:t5

SB is turned on at point t5. The SB switching loss can be minimized by turning on SB when the SB both-side voltages are at a minimum (when the resonance voltage is at a peak). The SB turn-on timing can be set with TD1 of the HA16163. The time when the resonance voltage is at a peak is given by equation (4).

From t5 onward, operation is on the same principle as in Subinterval 1 through Subinterval 5.

Time:t5

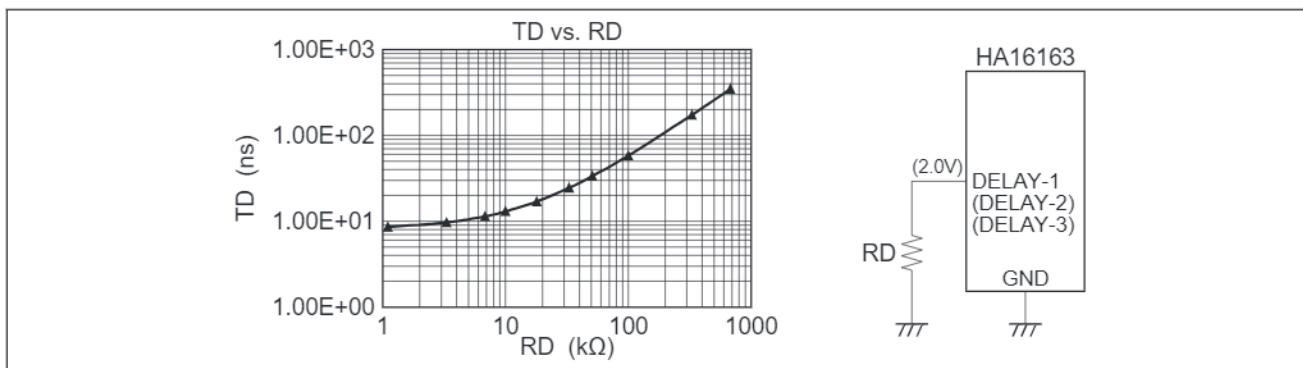

## Delay Setting

Inter-output delays (TD1, TD2, TD3) are set by means of a resistance connected between the DELAY-1 (-2, -3) pin and GND. The following graph shows the relationship between the external resistance and delay. The typical value of the delay set time is given by the following equation.

$$TD = 0.5p[F] \cdot RD[\Omega] + 8n[s] \quad [s]$$

When the RD value is small, the set time will be larger than the above calculated value due to the effect of internal delay, etc., and therefore a constant setting should be made with reference to the following graph.

Figure 11

Place the resistor for connection to the DELAY-1,2,3 pin as close to the pin as is possible. Please design the pattern so that the level of cross-talk from other signals is minimized.

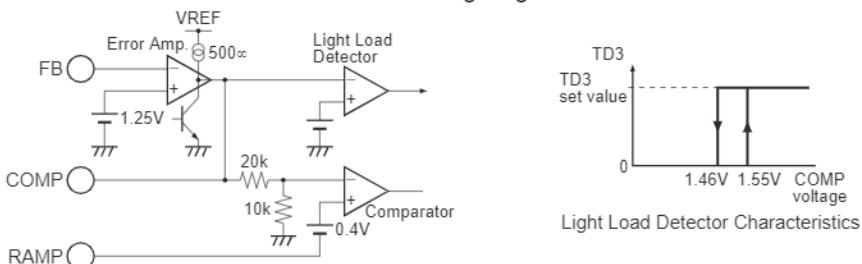

## DELAY-3 (TD3)

There is a condition that secondary-side control output OUT-E and OUT-F delay TD3 is 0 s (typical) in order to prevent shorting of the transformer secondary side. The relationship between TD3 and the IC operating state is shown in the following table.

| Mode               | Definition   | Operation of OUT-E, OUT-F    | Note |

|--------------------|--------------|------------------------------|------|

| Light load         | COMP < 1.65V | TD3 = 0                      | 1    |

| Pulse by pulse OCL | CS ≥ 0.4V    | TD3 = 0                      | 2    |

| One shot OCL       | CS ≥ 0.6V    | Fixed low (operation halted) |      |

Notes: 1. Light-load detection is performed by means of the error amplifier output voltage. Light-load detection characteristics are as shown in the following diagram.

2. TD3 of the next OUT-E or OUT-F after the pulse-by-pulse current limiter (PBP OCL) operates is 0 s (typical). When OUT-C and OUT-D are subsequently inverted by the Phase Shift Comparator, not the PBP OCL, TD3 is restored to the value set by means of the DELAY-3 pin.

## Application

Note: All voltage, current, time shown in the diagram are typical value.

Sample application circuits are given here. Confirmatory experiments should be carried out when applying these examples to products.

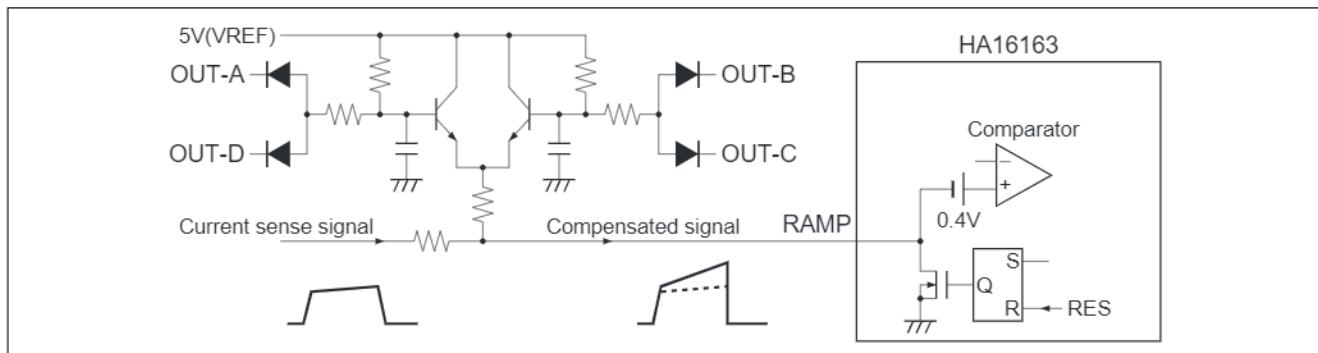

## Slope Compensation

In order to improve the unstable operation characteristic of current mode, voltage slopes in a current sense signal can be superimposed. The following is a possible slope compensation method.

**Figure 12**

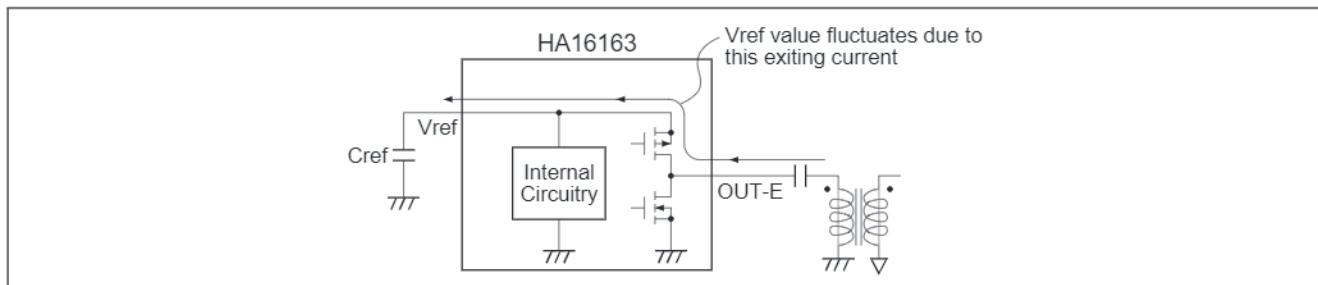

## Driving a Pulse Transformer

OUT-A through OUT-F of this IC are CMOS outputs that use Vref as their power supply. When directly driving a pulse transformer, the Vref voltage fluctuates according to the exciting current. As Vref fluctuation may make internal circuit operation unstable, direct drive of a pulse transformer should be avoided.

- Case 1 (NG)

The figure below shows a case where a pulse transformer is driven directly. Vref voltage fluctuation occurs due to the exciting current.

### Case 1 (NG)

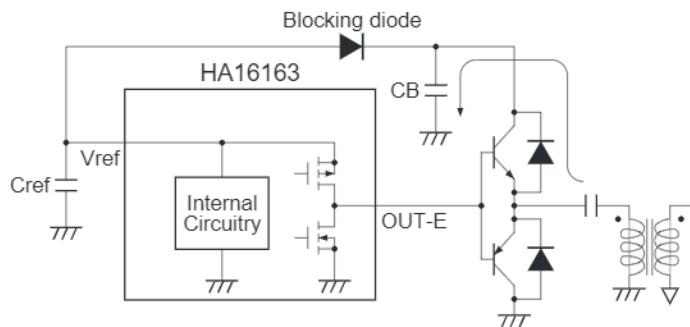

- Case 2

The figure below shows an example in which a current amplifier is added by means of transistors. A reverse current due to the exciting current is prevented by a blocking diode, and therefore capacitance  $CB$  is charged. In this way, fluctuation of the  $C_{ref}$  potential is suppressed and stable operation can be achieved.

As well as a buffer implemented by means of a transistor, standard logic IC or buffer IC connection is also possible. The buffer circuit power supply method should be implemented in the same way.

### Case 2

- Case 3

The figure below shows an example of a drive power supply method using emitter following. For the same reason as described above, fluctuation of the Cref potential is suppressed and stable operation can be achieved.

### Case 3

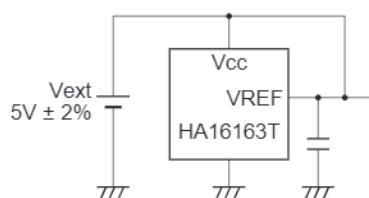

## Supplying Power from an External Power Supply

It is also possible to use an external source as the power supply for the HA16163T as shown in figure 13. The **VREFGOOD** circuit controls whether the IC is operating or stopped. The threshold voltage of the **VREFGOOD** circuit is 4.6 V (typ.) on the rising edge and 4.4 V on the falling edge. Since the IC's characteristics vary with the value of the external voltage, this voltage must be provided by a high-precision 5-V source.

**Figure 13**

## Characteristic Curves

Operating Current vs. Ambient Temperature Characteristics

VREF Output Voltage vs. Ambient Temperature Characteristics

Remote-on Voltage vs. Ambient Temperature Characteristics

Remote-off Voltage vs. Ambient Temperature Characteristics

Error Amplifier Sink Current vs. Ambient Temperature Characteristics

Soft-start Pin Current vs. Ambient Temperature Characteristics

Current Sense Delay Time vs. Ambient Temperature Characteristics

Overcurrent Protection Delay Time vs. Ambient Temperature Characteristics

## Package Dimensions

## Renesas Technology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

Keep safety first in your circuit designs!

1. Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

Notes regarding these materials

1. These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party.

2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein.

- The information described here may contain technical inaccuracies or typographical errors.

- Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

- Please also pay attention to information published by Renesas Technology Corp. by various means, including the Renesas Technology Corp. Semiconductor home page (<http://www.renesas.com>).

4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials.

7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

- Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.

### RENESAS SALES OFFICES

<http://www.renesas.com>

**Renesas Technology America, Inc.**

450 Holger Way, San Jose, CA 95134-1368, U.S.A

Tel: <1> (408) 382-7500 Fax: <1> (408) 382-7501

**Renesas Technology Europe Limited.**

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, United Kingdom

Tel: <44> (1628) 585 100, Fax: <44> (1628) 585 900

**Renesas Technology Europe GmbH**

Dornacher Str. 3, D-85622 Feldkirchen, Germany

Tel: <49> (89) 380 70 0, Fax: <49> (89) 929 30 11

**Renesas Technology Hong Kong Ltd.**

7/F., North Tower, World Finance Centre, Harbour City, Canton Road, Hong Kong

Tel: <852> 2265-6688, Fax: <852> 2375-6836

**Renesas Technology Taiwan Co., Ltd.**

FL 10, #99, Fu-Hsing N. Rd., Taipei, Taiwan

Tel: <886> (2) 2715-2888, Fax: <886> (2) 2713-2999

**Renesas Technology (Shanghai) Co., Ltd.**

26/F., Ruijin Building, No.205 Maoming Road (S), Shanghai 200020, China

Tel: <86> (21) 6472-1001, Fax: <86> (21) 6415-2952

**Renesas Technology Singapore Pte. Ltd.**

1, Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632

Tel: <65> 6213-0200, Fax: <65> 6278-8001