# MSD95C00

# Small Computer System Interface (SCSI) Controller-SCSIC

# **FEATURES** ☐ Initiator and Target Operation ☐ 5 MByte/Sec Synchronous and 3 MByte/Sec Asynchronous Data Transfers ☐ Automatic Arbitration and (Re) Selection ☐ Supports both Arbitration and Non-Arbitration/Applications ☐ Internal Twelve Byte Buffer ☐ Internal 24-bit Byte Transfer Counter ☐ Built-in 48 mA High-current SCSI Bus Drivers ☐ User Selectable Selection Timeout ☐ Separate Busses for Data and Microprocessor ☐ Separate DMA for Processor and Data Channels ☐ Burst Mode DMA Transfers on Data Bus ☐ Programmed I/O or DMA Transfers on Processor Data Bus ☐ Eight Bit Bi-Directional General Purpose I/O Port ☐ Bus Architecture allows caching ☐ Compatible with MSD95C02 and MSD95C01 Storage Controllers □ Low Power CMOS

## **SCSI OVERVIEW**

Up to 8 SCSI devices, known as Initiators and Targets, may be connected to a single SCSI bus. These SCSI devices communicate across the SCSI bus using a protocol based on ten distinct bus phases. Target devices execute high level commands which they receive from Initiator devices.

☐ TTL compatible inputs and outputs

A SCSI device may have up to 256 Logical Units associated with it. Host adapters, disk drives and printers are examples of Logical Units. Any SCSI device may be connected to a SCSI port. This allows the user to connect any SCSI compatible device to any SCSI bus providing that the operating system is able to associate the type of device connected with its SCSI ID and Logical Unit Number.

The SCSI bus phases are Bus Free, Arbitration, Selection, Reselection, Command, Data In, Data Out, Message In, Message Out and Status. A target is capable of generating an Arbitration, Reselection, Command, Data In, Data Out, Message In, Message Out or Status phase. An initiator is capable of generating an Arbitration or Selection phase. When the SCSI devices are not generating any of the above phases, the system is said to be in the Bus Free phase. Note that the Arbitration phase may be generated by either a target or an initiator. For a complete description of the SCSI protocol, refer to the ANSI X3.131 specification.

#### **GENERAL DESCRIPTION**

The MSD95C00 SCSI Controller is capable of arbitrating for and supporting data transfer on an ANSI SCSI (Small Computer System Interface) compatible computer bus. The internal twelve byte buffer makes this device suitable for both peripheral and host adapter applications in systems that support both Asynchronous and Synchronous data transfer modes.

The MSD95C00 includes circuitry that automatically arbitrates for the SCSI bus and selects or reselects another device. This feature combined with the size of the internal buffer allows a selected Target device to transfer an entire command from an Initiator with a minimum of processor intervention on either side.

The MSD95C00 has three independent busses: one connects to the local microprocessor (the System bus), a second which connects to the data Ring buffer (the Data

bus) and a third which connects to the SCSI bus. Information transfers may be made between the SCSI bus and either of the other two buses. The Data bus supports burst mode DMA transfers and the System Bus supports both programmed I/O and DMA transfers.

Accesses to the Ring buffer are controlled via a DMA request/acknowledge handshake. Local processor transfers, as well as transfers to logical units (e.g. media transfers), are asynchronous with respect to transfers across the SCSI bus.

The MSD95C00 can be combined with the flexible MSD95C02 or MSD95C01 Storage Controllers, a standard microprocessor, and static RAM to support embedded SCSI peripheral applications with minimum component count and synchronous SCSI speeds of up to 5 megabytes per second.

T-52-33-27

# **TABLE OF CONTENTS**

| FEATURES                     | 1  |

|------------------------------|----|

| PIN CONFIGURATION            | 1  |

| SCSI OVERVIEW                | 1  |

| GENERAL DESCRIPTION          | 1  |

| DESCRIPTION OF PIN FUNCTIONS | 3  |

| SYSTEM DESCRIPTION           | 5  |

| FUNCTIONAL DESCRIPTION       | 5  |

| OPERATION DESCRIPTION        | 10 |

| REGISTER DESCRIPTION         | 11 |

| REGISTER BIT MAP             | 12 |

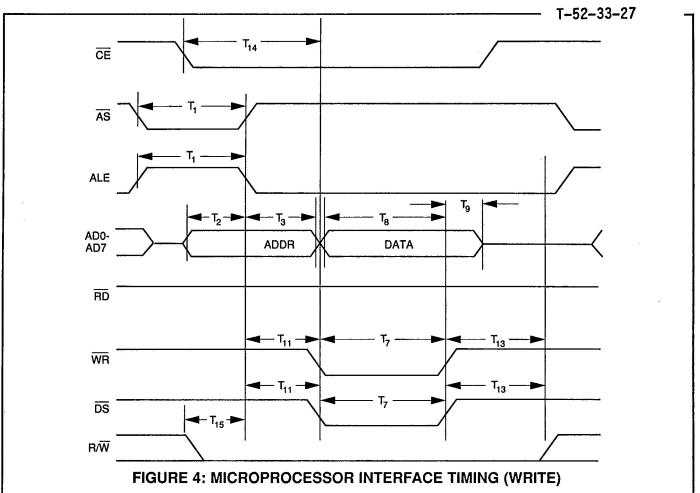

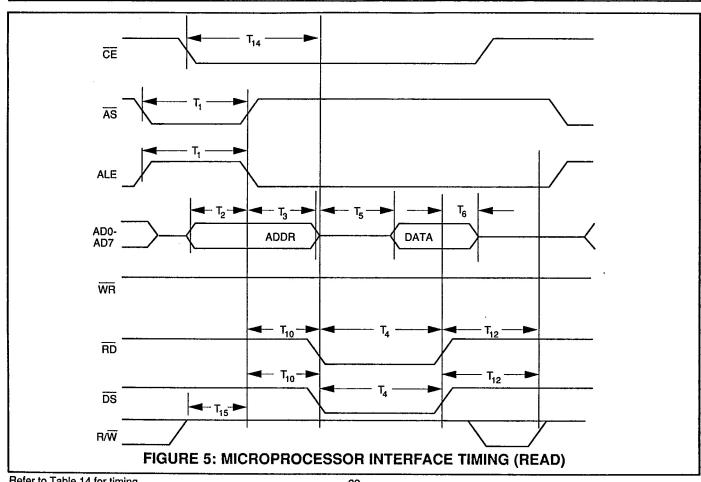

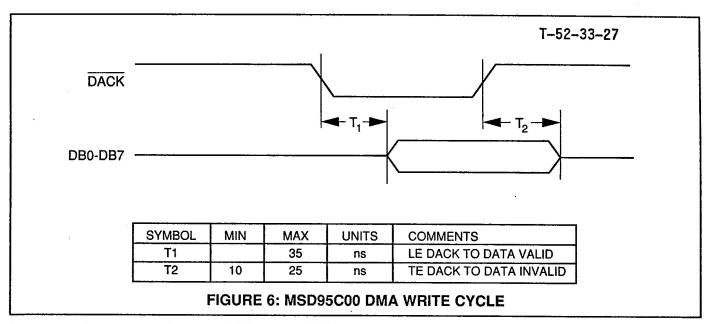

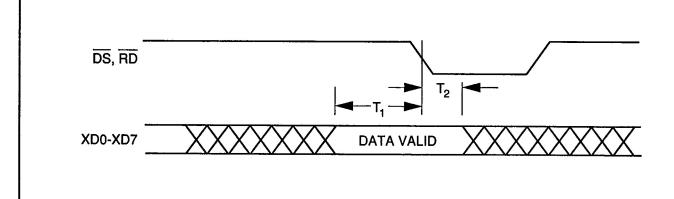

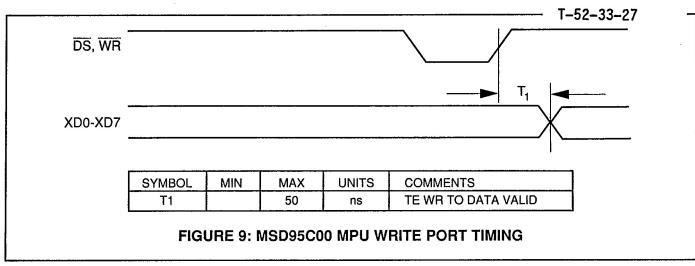

| TIMING DIAGRAMS              | 22 |

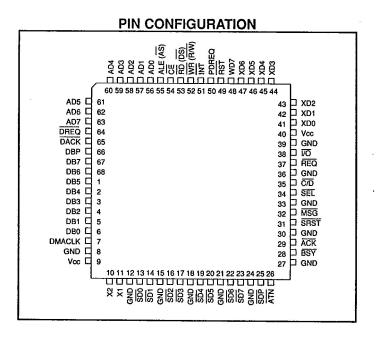

# **DESCRIPTION OF PIN FUNCTIONS**

T-52-33-27

| SCSI INT                               | SCSI INTERFACE NOTE: These Signals are Active Low. |                          |     |                                                                                                                                                                                                                                                                                      |  |  |  |  |

|----------------------------------------|----------------------------------------------------|--------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PIN NO.                                | NAME                                               | SYMBOL                   | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                          |  |  |  |  |

| 13,14,16,<br>17, 19, 20,<br>22, 23, 25 | SCSI DATA<br>and PARITY                            | SD <u>0-S</u> D7,<br>SDP | 1/0 | These pins are the eight bi-directional SCSI data signals and the SCSI parity signal to/from the SCSI bus. Except during arbitration, their direction depends on the state of the I/O signal and the mode, Initiator or Target, of the chip. Parity is not valid during arbitration. |  |  |  |  |

| 26                                     | ATTENTION                                          | ATN                      | I/O | This pin is the bi-directional ATTENTION signal to/from the SCSI bus. It is an output when the controller is programmed as an initiator and an input when programmed as a target.                                                                                                    |  |  |  |  |

| 28                                     | BUSY                                               | BSY                      | I/O | This pin is the bi-directional BUSY signal to/from the SCSI bus.                                                                                                                                                                                                                     |  |  |  |  |

| 29                                     | ACKNOWLEDGE                                        | ACK                      | 1/0 | This pin is the bi-directional ACKNOWLEDGE signal to/from the SCSI bus. It is an output when the controller is programmed as an initiator and an input when programmed as a target.                                                                                                  |  |  |  |  |

| 31                                     | SCSI BUS<br>RESET                                  | SRST                     | 1/0 | This pin is the bi-directional RESET signal to/from the SCSI bus. A low on this pin indicates a SCSI bus Reset.                                                                                                                                                                      |  |  |  |  |

| 32                                     | MESSAGE                                            | MSG                      | 1/0 | This pin is the bi-directional MESSAGE signal to/from the SCSI bus. It is an output when the controller is programmed as a target and an input when programmed as an initiator.                                                                                                      |  |  |  |  |

| 34                                     | SELECT                                             | SEL                      | 1/0 | This pin is the bi-directional SELECT signal to/from the SCSI bus.                                                                                                                                                                                                                   |  |  |  |  |

| 35                                     | COMMAND/<br>DATA                                   | C/D                      | 1/0 | This pin is the bi-directional COMMAND/DATA signal to/from the SCSI bus. It is an output when the controller is programmed as a target and an input when programmed as an initiator.                                                                                                 |  |  |  |  |

| 37                                     | REQUEST                                            | REQ                      | 1/0 | This pin is the bi-directional REQUEST signal to/from the SCSI bus. It is an output when the controller is programmed as a target and an input when programmed as an initiator.                                                                                                      |  |  |  |  |

| 38                                     | INPUT/OUTPUT                                       | Ī/O                      | 1/0 | This pin is the bi-directional INPUT/OUTPUT signal to/from the SCSI bus. It is an output when the controller is programmed as a target and an input when programmed as an initiator.                                                                                                 |  |  |  |  |

| RING BUFFER INTERFACE |                           |         |     |                                                                                                                          |  |  |  |

|-----------------------|---------------------------|---------|-----|--------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PIN NO                | NAME                      | SYMBOL  | 1/0 | DESCRIPTION                                                                                                              |  |  |  |

| 1-6<br>67,68          | RING BUFFER<br>DATA BUS   | DB0-DB7 | 1/0 | These pins are the eight bi-directional data signals to/from the Ring Buffer.                                            |  |  |  |

| 7                     | DMA CLOCK                 | DMACLK  | 0   | This output is a buffered clock signal derived from the X1 input.                                                        |  |  |  |

| 64                    | DMA REQUEST               | DREQ    | 0   | This active low output to the external DMA controller is used to request a DMA transfer of data to/from the Ring Buffer. |  |  |  |

| 65                    | DMA<br>ACKNOWLEDGE        | DACK    | 1   | This active low input from the external DMA controller is used to strobe data to/from the Ring Buffer.                   |  |  |  |

| 66                    | SYSTEM DATA<br>BUS PARITY | DBP     | 1/0 | This pin is the parity bit for the Ring Buffer Data Bus.                                                                 |  |  |  |

# STANDARD MICROSYSTEMS 33E D 3564686 0005189 9 328C

# DESCRIPTION OF PIN FUNCTIONS (CONTINUED)

T-52-33-27

| MICROPR | MICROPROCESSOR INTERFACE                                      |                     |     |                                                                                                                                                                                                                                          |  |  |  |

|---------|---------------------------------------------------------------|---------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PIN NO  | NAME                                                          | SYMBOL              | 1/0 | DESCRIPTION                                                                                                                                                                                                                              |  |  |  |

| 41-48   | BI-<br>DIRECTIONAL<br>EXTERNAL<br>DATA BUS                    | XD0-XD7             | 1/0 | These pins are open drain general purpose I/O bus signals and have internal 1K pullup resistors.                                                                                                                                         |  |  |  |

| 50      | PROCESSOR<br>DMA REQUEST                                      | PDREQ               | 0   | This output is active high when byte transfers to/from the Processor is required.                                                                                                                                                        |  |  |  |

| 51      | INTERRUPT                                                     | ĪNT                 | 0   | This output is the interrupt signal to the local processor. This output is active low open drain and has an internal pullup resistor.                                                                                                    |  |  |  |

| 52      | WRITE <u>STROB</u> E<br>(READ/WRITE)                          | W <u>R</u><br>(R/W) | I   | When the SCSIC is configured for ALE, this active low strobe is used to latch write data from the AD7-0 bus into the SCSIC. When the SCSIC is configured for AS, the R/W input is used to qualify DS for a read or write cycle.          |  |  |  |

| 53      | READ STROBE<br>(DATA STROBE)                                  | RD (DS)             | L   | When the SCSIC is configured for ALE, this active low strobe is used to enable read data from the SCSIC onto the AD7-0 bus. When the SCSIC is configured for AS, this active low signal is used to strobe data into or out of the SCSIC. |  |  |  |

| 54      | CHIP ENABLE                                                   | CE                  | ı   | This input, when low, enables the SCSIC's registers for reading and writing.                                                                                                                                                             |  |  |  |

| 55      | ADDRESS LATCH<br><u>ENABLE</u><br>( <u>ADDRESS</u><br>STROBE) | ALE (ĀS)            | ı   | When active, this signal indicates a valid address is on the AD7-0 bus. The local processor must read a SCSIC register to configure the chip for ALE or AS operation.                                                                    |  |  |  |

| 56-63   | LOCAL<br>PROCESSOR<br>ADDRESS/<br>DATA BUS                    | AD0-AD7             | I/O | These eight signals are the multiplexed address/data bus to/from the local processor.                                                                                                                                                    |  |  |  |

| MISCELLA | MISCELLANEOUS     |        |     |                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|----------|-------------------|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PIN NO   | NAME              | SYMBOL | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 49       | RESET             | RST    | ı   | This active low input causes the MSD95C00 to reset to an initial state. This signal must be held low for at least 1 ms. All SCSI signals are deasserted. DREQ is inactive high. PDREQ is inactive low. INT is inactive high. AD7-0 are inputs. DB7-0 are inputs. Refer to individual register descriptions for the reset state of each register. |  |  |  |  |

| 11       | CRYSTAL<br>INPUT  | X1     | 1   | A 20 MHz. (max) crystal is connected to this input. A TTL clock may be used as an input to this pin.                                                                                                                                                                                                                                             |  |  |  |  |

| 10       | CRYSTAL<br>OUTPUT | X2     | 0   | A 20 MHz. (max) crystal is connected to this output. If a TTL is clock is connected to X1, this input must be left floating.                                                                                                                                                                                                                     |  |  |  |  |

| POWER and GROUND                            |        |        |     |                       |  |  |  |

|---------------------------------------------|--------|--------|-----|-----------------------|--|--|--|

| PIN NO                                      | NAME   | SYMBOL | I/O | DESCRIPTION           |  |  |  |

| 8,12,15,<br>18,21,24,<br>27,30,33,<br>36,39 | GROUND | GND    | Р   | Ground connections.   |  |  |  |

| 9,40                                        | POWER  | Vcc    | Р   | +5V Power connection. |  |  |  |

pair in an effort to complete the command.

#### 33E D

# Initiator to inform the Target being selected that it wishes to send a message to the target.

T-52-33-27

## SYSTEM DESCRIPTION

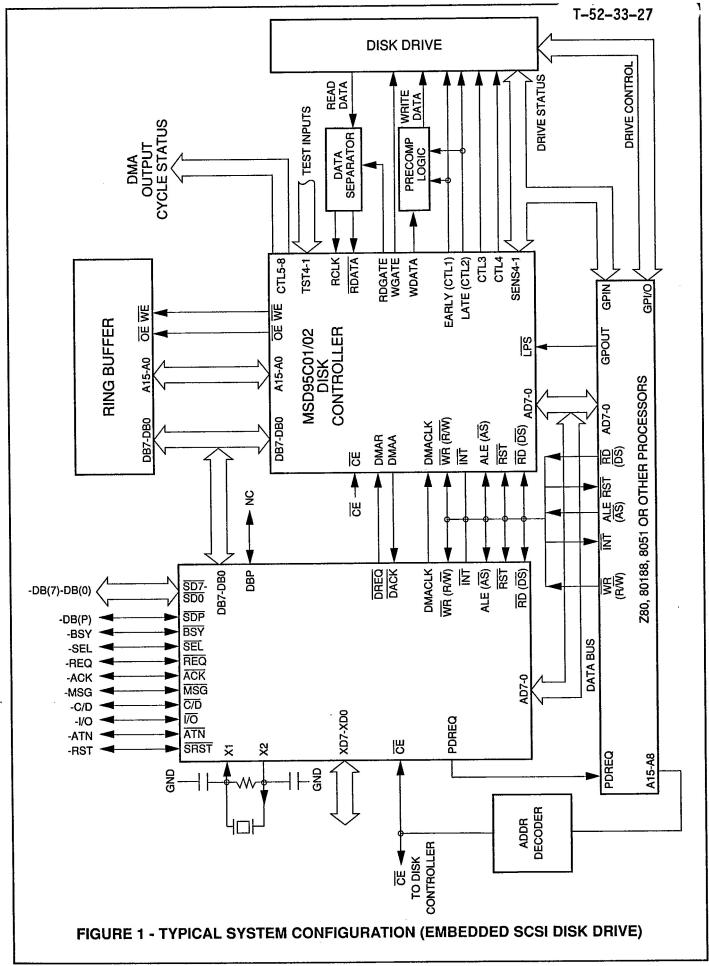

The block diagram in Figure 1 illustrates a typical implementation of the MSD95C00 used in a hard drive application. The MSD95C00 provides simple interfacing to the SCSI bus, microprocessor and controller logic.

#### **SCSI** Interface

The eighteen SCSI signals may be connected directly to a single ended (open collector) SCSI bus. The MSD95C00 drivers and receivers are fully capable of driving and receiving SCSI bus signals as defined by the ANSI X3.131 specification.

### **Microprocessor Interface**

The microprocessor interface consists of an 8-bit data bus and control bus. With the exception of optional address decoding logic for the CE input, all signals are tied directly to the microprocessor eliminating the need for external circuitry.

#### **Controller Interface**

The controller interface consists of and 8-bit bi-directional data bus, a clock and a pair of request/acknowledge handshake signals. These signals may be connected directly to memory and controller logic such as the SMC MSD95C02 or MSD95C01 storage controllers.

# **FUNCTIONAL DESCRIPTION**

#### **Arbitration Phase**

Arbitration is a system option which allows a SCSI device to gain control of the SCSI bus. Arbitration is required in systems which contain more than one initiator or in systems which support Reselection. While generating an Arbitration phase the MSD95C00 will assert the SCSI Busy signal and it's own ID bit.

Since the Arbitration Phase is a system option, its generation is enabled or disabled via software. Arbitration is enabled in the MSD95C00 by writing a logic 1 to bit 1 of the Mode register during initialization. Arbitration phase timing an Bus Free detection is handled completely by the MSD95C00. If enabled, this phase will be generated prior to a Selection or Reselection phase, with no additional microprocessor intervention, after a Select command (writing a logic 1 to bit 6 of the Command register) has been issued to the MSD95C00. The Arbitrating device with the highest ID typically wins arbitration with Bit 7 having the highest priority and bit 0 having the lowest. Parity is not valid during the Arbitration Phase.

### **Selection Phase**

The Selection phase is generated by an Initiator. The MSD95C00 will assert the SCSI I/O and Select signals during the Selection phase. During the Selection phase the MSD95C00 also asserts it's own SCSI ID bit as well as the SCSI ID bit of the target it wishes to select. Selection phase timing, including Selection Timeout, is handled completely by the MSD95C00. This phase will be generated after a Select command (writing a logic 1 to bit 6 of the Command register) has been issued to the MSD95C00 if bit 0 of the Mode register is set to a logic "1" (Initiator Mode). If bit 0 of the Control register has been set to a logic 1 the SCSI Attention signal will be asserted during the Selection phase. This is part of the SCSI protocol which allows an

#### **Reselection Phase**

Reselection is a system option. The Reselection phase is generated by a Target. The MSD95C00 will assert the SCSI Select signal during the Reselection phase. During the Reselection phase, the MSD95C00 also asserts it's own SCSI ID bit as well as the SCSI ID bit of the initiator it wishes to reselect. Reselection phase timing, including Reselection Timeout, is handled completely by the MSD95C00. This phase will be generated after a Select command (writing a logic 1 to bit 6 of the Command register) has been issued to the MSD95C00 if bit 0 of the Mode register is reset to a logic '0' (Target Mode). This phase should only be used if an Initiator had previously selected a Target and the Target then performed a Disconnect. The Reselection would again establish a connection between the original Initiator Target

#### **Command Phase**

The Command phase is generated by a Target. The local microprocessor must write a logic 1 to bit 2 of the Command 2 register. The phase is initiated and data transfer begins when the local microprocessor writes the Byte Counter Low register. The phase is terminated by initiating a new phase or performing a Disconnect command. The Command phase allows a Target to request a Command Descriptor Block (CDB) from the Initiator. Command discriptor blocks are six, ten or twelve bytes in length. The first byte of the command discriptor block indicates the number of bytes which comprise the command discriptor block. After the first byte is passed from the Initiator to the Target the local microprocessor must read the byte from the Target's FIFO, calculate the number of remaining bytes and set up the Target to transfer the remaining bytes. The remaining bytes of the command discriptor block are then transferred to the Target's FIFO. The target microprocessor is informed, via interrupt or polling, of the completion of this transfer. This block is then transferred, via DMA or programmed I/O, from the FIFO to the target microprocessor's memory. The target microprocessor must then digest and execute the command.

#### **Data-In Phase**

The Data-In phase is generated by a Target. The Target microprocessor writes a logic 1 into bit 1 of the Command 2 register. The phase is initiated and data transfer begins when the Target microprocessor writes to the Byte Counter Low register. The phase is terminated by initiating a new phase or executing a Disconnect command. The Data-In phase allows data to be transferred from a Target to an Initiator. Data-In and Data-Out transfers may be asynchronous or synchronous. All other transfers, such as message, status and command, are defined by the SCSI protocol as being asynchronous. A typical data-in transfer would transfer data from the Target Ring buffer, through the Target SCSIC's FIFO, across the SCSI bus, into the Initiator SCŠI's FIFO and into the Initiators local memory. The Target microprocessor would set up the Target to perform the transfer, initiate the transfer by writing to the Byte Counter Low register and then wait for an interrupt indicating the transfer has been completed. The three bus architecture of the MSD95C00 allows the Initiator and Target microprocessors to perform their housekeeping duties while the data transfer is taking place.

FIGURE 2 - MSD95C00 BLOCK DIAGRAM

#### **Data-Out Phase**

The Data-Out phase is generated by a Target. The Target microprocessor writes a logic 0 into each bit of the Command 2 register. The phase is initiated and transfer begins when the Target microprocessor writes to the Byte Counter Low register. The phase is terminated by initiating a new phase or executing a Disconnect command. The Data-Out phase allows data to be transferred from an Initiator to a Target. Data-In and Data-Out transfers may be asynchronous or synchronous. All other transfers, such as message, status and command, are defined by the SCSI protocol as being asynchronous. A typical data-out transfer would transfer data from Initiator memory to the Initiator SCSIC's FIFO, over the SCSI bus, through the Target SCSIC's FIFO then to the Target Ring buffer. The Target microprocessor would set up the Target to perform the transfer, initiate the transfer by writing to the Byte Counter Low register and then wait for an interrupt indicating the transfer has been completed. The three bus architecture of the MSD95C00 allows the Initiator and Target microprocessors to perform their housekeeping duties while the data transfer is taking place.

# Message-In Phase

The Message-In phase is generated by a Target. The Target microprocessor writes a logic 1 into bit 7 of the Command 2 register. The phase is initiated and transfer begins when the Target microprocessor writes to the Byte Counter Low register. The phase is terminated by initiating a new phase or executing a Disconnect command. Messages are typically one byte in length. The local microprocessor would write the message byte(s) into the Target FIFO and set the Target up for the proper number of bytes to be transferred. Writing to the Byte Counter Low register generates the phase and initiates the transfer.

#### Message-Out Phase

The Message-Out phase is generated by a Target. The Target microprocessor writes a logic 1 into bit 6 of the Command 2 register. The phase is initiated and transfer begins when the Target microprocessor writes to the Byte Counter Low register. The phase is terminated by initiating a new phase or executing a Disconnect command. Messages are typically one byte in length. The Initiator microprocessor would write the message byte(s) into the Initiator FIFO. The target microprocessor would set up the Target for a one byte transfer. Writing to the Byte Counter Low register initiates the transfer. If the target microprocessor detects an extended message is to be transferred it must load the Byte Counter to allow the target to transfer the remainder of the message bytes.

# **Status Phase**

The Status phase is generated by a Target. The Target microprocessor writes a logic 1 into bit 3 of the Command 2 register. The phase is initiated and transfer begins when the Target microprocessor writes to the least significant byte of the Byte counter. The phase is terminated by initiating a new phase or executing a Disconnect command. Status transfers are one byte in length. The Target microprocessor would write the status byte into the Target FIFO and set the Target up for a one byte transfer.

# **Bus Free Phase**

The Bus Free phase occurs when no SCSI devices are driving the SCSI bus and the SCSI SEL and BUSY signals have been false for a specified period of time.

### **Being Selected or Reselected**

T-52-33-27

Typically Targets may be selected and Initiators may be reselected. A device responds to selection or reselection during a selection or reselection phase if it recognizes it's SCSI ID bit on the bus and there are not more than two ID bits on the bus. Parity, if enabled, must not be in error. The MSD95C00 has two bits, bits 1 and 2 of the Control register, which enable or disable it from responding to an attempted selection or attempted reselection regardless of whether the MSD95C00 is programmed to be an initiator or target. If a selection or reselection is attempted, maskable interrupts may be generated and the appropriate status bits are set.

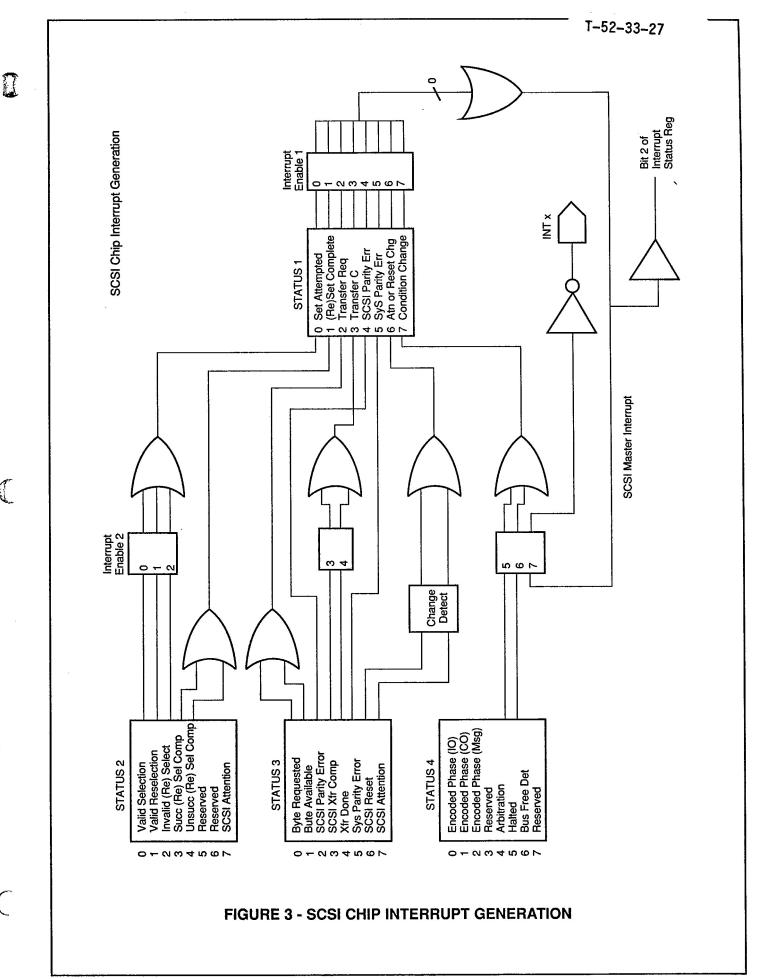

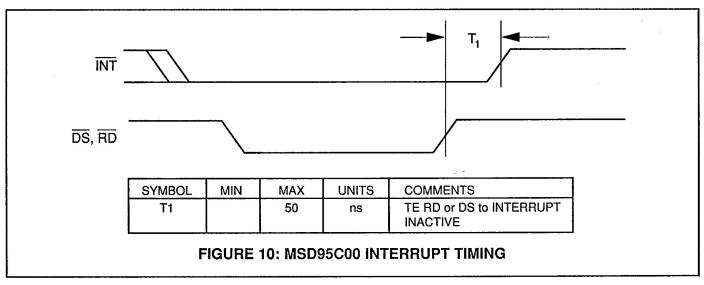

#### Interrupts

There are fifteen interrupt causing conditions generated by the MSD95C00, all of which are maskable. These interrupt causing conditions generate status bits in the Status 2, 3 and 4 registers. Reading the Status 2, 3 or 4 registers will reset the interrupt causing condition in that register. Some of these status bits are ORed together and are readable through the Status 1 register. The remaining status bits are directly readable through the Status 1 register. Reading the Status 1 register allows the software to decide which of Status 2, 3 or 4 registers to read. Reading the Status 1 register does not reset the interrupt causing condition. Please refer to Figure 3.

#### **Transfer Modes**

Data (any information being passed through the system is referred to as data) may be transferred between the SCSI bus and microprocessor memory. Data may also be transferred between the SCSI bus and the Ring buffer memory. All data transfers to and from the SCSI bus pass through the MSD95C00's FIFO. Data cannot be transferred between the microprocessor and the Ring Buffer through the MSD95C00.

# Interrupt Driven I/O

The processor responds to an interrupt by reading the Interrupt Status register. If the SCSIC status bit is active high, the Processor reads the Status 1 register to determine the source of the interrupt.

If the Transfer Requested status bit is active high, the Processor should read the Status 3 register to determine whether it was set by Byte Available or Byte Requested. In response the SCSIC resets the Transfer Requested status

If the Byte Available status bit is set, the processor should read the SCSI Data Out register. The SCSIC clears the Byte Available status bit if, and only if, there is no more data in the FIFO. If the Byte Available status bit is still set, the SCSIC generates a new transfer Request interrupt.

If the Byte Requested status bit is set, the processor should write a byte of data to the SCSIC Data Out register. The SCSIC then clears the Byte Requested status bit if the Byte Counter equals zero or if the FIFO is full. If the Byte Requested status bit remains set after the processor writes the byte of data, the SCSIC generates another Transfer Request interrupt.

#### **DMA Driven I/O**

A DMA controller may be used to transfer a Command Descriptor Block, a message or status byte between the MSD95C00's FIFO and processor memory. Transfers are performed when the PDREQ is a function of the Byte

Requested status bit when writing to the FIFO and is a function of the Byte Available bit when reading the FIFO.

#### Polled I/O

The processor reads the Status 3 register to see if either the Byte Available or Byte Requested status bits are high.

If Byte Available is high, the Processor transfers the byte from the SCSIC Data In register to the Processor or the Processor RAM. If there is no more data in the buffer, the SCSIC clears the Byte Available status bit.

If the Byte Requested is high, the processor transfers the byte from the processor or the processor RAM to the SCSIC Data Out register. If no SCSI REQs are pending or the Buffer is full, the Byte Requested status bit is cleared.

## **SCSI Parity Error Handling**

Initiator (Status, Message In, Data In Phases):

If the Halt On Parity Error bit in the Control Register is set to 1 the SCSIC will halt and set the Halted and PE status bits if data has even parity. If these bits are set, the SCSIC will generate a PE interrupt. If enabled, a Condition Change interrupt will also be generated. In response to the interrupt, the processor reads the Status registers and resets the Parity Error and Condition Change Interrupts.

The processor asserts ATN to request Message Out Phase in order to signal its desire to send either a Message Reject or Message Parity Error. The processor then issues a (Re) Start Command.

Target (Command, Message Out, Data Out Phases):

The SCSIC will set the PE status bit if data has even parity. If the PE bit is set, the SCSIC will generate a PE interrupt. In response to the interrupt, the processor reads the Status registers. Finally, the SCSIC resets the Parity Error Interrupts.

Note: The Halt On Parity Error bit in the Control Register does not affect Target operation.

### **OPERATION DESCRIPTION**

#### **SCSI Read Sequence of Events**

The following is an example of a SCSI Initiator reading from a SCSI Target.

A Host system with SCSIID of 80h wishes to read data from a peripheral containing a hard disk drive with SCSIID of 04h. The initiator and target SCSIID's are encoded using three of the 8 bits available at the general purpose I/O port. Assume the system supports arbitration and parity checking. The Host's MSD95C00 has been initialized as per Table 1.

The host  $\mu P$  assembles the six byte Command Descriptor Block in local memory.

Upon detecting the "Halted" interrupt, the host microprocessor must determine the current bus phase. If the Command phase is detected, the host microprocessor must load the Byte counter with the proper number of bytes. The CDB is transferred to the FIFO one byte for each received SREQ.

The host  $\mu P$  then issues a Select command to its MSD95C00. This is accomplished by writing a "1" to bit 6 of the Command 1 register.

The initiator MSD95C00 will wait for a Bus Free Phase. Upon detection the Bus Free phase the initiator MSD95C00 will arbitrate for the bus. If unsuccessful the initiator MSD95C00 will again wait for the Bus Free phase. When successful, the initiator MSD95C00 will generate the Selection phase. If the target MSD95C00 responds to the selection prior to the initiator's selection timeout period the initiator MSD95C00 will set the Successful Selection Complete bit in Status 2 register and generate an interrupt. If the target MSD95C00 does not respond to the selection within the initiator's selection timeout period the initiator MSD95C00 will set the Unsuccessful Selection Complete bit in the Status 2 register and generate an interrupt. Arbitration and Selection phase timing are handled fully by the MSD95C00. The host microprocessor need only initiate the Select command and wait for an interrupt (or poll the Status 1 register for the (re)selection complete bit). Assuming the target MSD95C00 has responded to the selection the CDB would have to be transferred to the target. The target MSD95C00 has been initialized as per Table 2.

The target MSD95C00 will detect when it has been selected. It will respond by asserting the SCSI Busy signal, internally latching the Source ID (the selecting initiator's ID with the target's ID masked off) and generating a Valid Selection (Status 2 register bit 0) interrupt. The target  $\mu P$  would typically read the Interrupt Status register and decide if the target MSD95C00 is the interrupt causing device. If so it would then read the Status 1 register. Reading the Status 1 register allows the  $\mu P$  to decide which of the remaining status registers holds the interrupt causing status bit. In this

| TABLE 1  |      |                                                                                                             |  |  |  |

|----------|------|-------------------------------------------------------------------------------------------------------------|--|--|--|

| Register | Data | Comments                                                                                                    |  |  |  |

| 00h      | 00h  | Asynchronous transfer mode.                                                                                 |  |  |  |

| 01h      | 7Fh  | Initiator, arbitration enable, parity check enable, DREQ multiple, PDREQ level, selection timeout = 1.6 ms. |  |  |  |

| 06h      | 13h  | Enable the following interrupts: Selection Attempted, (Re) Selection Complete, SCSI parity error.           |  |  |  |

| 07h      | 82h  | Enable the following interrupts: Valid Reselection, SCSI Master Interrupt.                                  |  |  |  |

| 08h      | C4h  | Enable reselection, enable PDREQ, enable DREQ.                                                              |  |  |  |

| 0Eh      | 80h  | Initiator ID.                                                                                               |  |  |  |

| Register | Data | TABLE 2 T-52-33-27 Comments                                                                                         |  |  |  |

|----------|------|---------------------------------------------------------------------------------------------------------------------|--|--|--|

| 00h      | 00h  | Asynchronous Transfer mode.                                                                                         |  |  |  |

| 01h      | 66h  | Target, Enable Arbitration, Enable Parity, DREQ Single Pulse, PDREQ Pulsed, Selection Timeout = 1.6 ms.             |  |  |  |

| 06h      | 1Bh  | Enable the following interrupts: Selection Attempted, (Re)Selection Complete, Transfer Complete, SCSI Parity Error. |  |  |  |

| 07h      | 99h  | Enable the following interrupts: Valid Selection, SCSI Transfer Complete, Transfer Done, SCSI Master Interrupt.     |  |  |  |

| 08h      | C2h  | Enable Selection, Enable REQ, Enable DREQ.                                                                          |  |  |  |

| 0Eh      | 04h  | Target ID.                                                                                                          |  |  |  |

case the Status 2 register should be read. The target  $\mu P$  would determine the interrupt causing condition(s) (in this case the Valid Selection bit, Bit 0, would be set). The target  $\mu P$  should also examine the SCSI Attention signal, bit 7 of the Status 2 register, at this time. This will allow the target to determine if the initiator is requesting a Message-Out phase. A Message-Out phase would be necessary if the initiator wished to perform synchronous data transfers for the first time.

If the SCSI Attention Signal is not asserted the target would typically respond with a Command phase. To accomplish this, the target uP would write a 04h into the Command 2 register and an FEh into the Byte Counter Low register. Upon writing the Byte Counter Low register the target MSD95C00 will generate the Command phase and a SCSI REQ signal. The initiator MSD95C00 will respond by supplying the first byte of the CDB and the SCSI ACK signal. The handshaking is automatically handled by the initiator and target MSD95C00 pair.

The target uP would receive an interrupt (or poll the Transfer Complete bit in the Status 1 register) caused by the SCSI Transfer Complete bit in the Status 3 register. It would respond by reading the Data-In register of the MSD95C00.

The target  $\mu P$  would then examine this first byte. The three MSB's indicate the group code and therefore the number of bytes in the CDB. For the Read command a group code "000" is expected, indicating a six byte CDB including the first byte. The target  $\mu P$  would then write an FFh, FFh, FAh to the Byte Counter register. This would initiate a transfer for the remaining five CDB bytes. The SCSI Transfer Complete bit in the Status 3 register would cause a second interrupt informing the  $\mu P$  that the remainder of the CDB is in the target MSD95C00's FIFO.

The target  $\mu P$  could either transfer five bytes from the MSD95C00's FIFO into it's own memory or use a handshake method, by interrogating the Byte Available bit in the Status 3 register, to transfer the remainder of the CDB.

Once the CDB has been transferred to the target  $\mu$ P's memory the  $\mu$ P must digest and execute the Read command.

The target  $\mu P$  then sets-up the hard disk controller, such as the SMC MSD95C01/02, and the target MSD95C00 for the transfer. The target  $\mu P$  initiates a Data-In Phase by writing an 02h to the Command 2 register, and writing the proper byte count, in 1's complement form, into the Byte Counter registers. Upon writing the Byte Counter Low register the target MSD95C00 will generate a Data-In phase and perform the transfer by handshaking with both the initiator

MSD95C00 and the MSD95C01/02. The target  $\mu P$  is free to perform any other tasks during the read operation and will be interrupted by the Transfer Done bit, bit 4 of the Status 3 register, at the completion of the transfer.

The initiator's  $\mu P$  would need to examine and respond to the SCSI bus phases. When the Data-In phase is detected, the initiator  $\mu P$  would load the Byte counter with the 1's complement of the number of bytes to be transferred and set up it's DMA controller, if one existed. Upon completion of the transfer the initiator  $\mu P$  would receive a Transfer Done interrupt (Bit 4 of the Status 3 register).

Using a similar algorithm, Status and Message Phase transfers would take place. The target would then disconnect from the SCSI bus allowing a new operation to take place.

#### REGISTER DESCRIPTION

**Reset Register**

8-Bits Read Only (ADDRESS 00H)

An initial dummy read configures the chip for ALE or AS type timing. Reading the Reset register address places the MSD95C00 into the same state as driving the RST input low and simultaneously reads the general purpose I/O port. A write to any other MSD95C00 register will terminate the reset state as well as write to the addressed register. Both the hardware and software resets will perform the same function as the Clear command in addition to resetting certain register bits as detailed below.

**Negotiation Register**

8-Bit Write Only (ADDRESS 00H)

The 4 MSB's, bits 7 - 4, of this eight bit write only register are used to program the Transfer Period for synchronous data transfers. The transfer period will be (2 + N)T where T is twice the clock period. For a 20 MHz crystal with the Negotiation register programmed for 0xh the transfer frequency is (2 + 0) 100ns = 200ns = 5MHz.

The 4 LSB's are used to program the SCSI REQ/ACK offset and are reset to zero by a hard or soft System Reset. Programming the 4 LSB's to zero configures the SCSIC for Asynchronous operation. Programming the 4 LSB's for 1 thru 12 configures the SCSIC for Synchronous operation with a REQ/ACK offset value equal to the value programmed. The maximum offset value the MSD95C00 will support is 12. This register should be programmed with a REQ/ACK Offset value regardless of whether the chip is operating in Initiator or Target mode.

# MSD95C00 REGISTER BIT MAPS

T-52-33-27

| -                                | ON REGISTER               |                            |                           | (WRITE REGISTER—ADDRESS 00H          |                                       |                                   |                                   |

|----------------------------------|---------------------------|----------------------------|---------------------------|--------------------------------------|---------------------------------------|-----------------------------------|-----------------------------------|

| TR                               | ANSFE                     | R PER                      | IOD                       | REQ/ACK OFFSET                       |                                       |                                   |                                   |

| MODE REGI                        | ·                         |                            |                           |                                      |                                       | GISTER-A                          | DORESS 01H                        |

| RESERVEC                         |                           | N TIMEOUT<br>bit 0         | PDREQ<br>LEVEL/<br>PULSED | DREQ<br>MULTIPLE/<br>SINGLE<br>PULSE | PARITY<br>CHECK<br>ENABLE/<br>DISABLE | ARBITRATE<br>ENABLE/<br>DISABLE   | INITIATOR/<br>TARGET              |

| BYTE COU                         | NTER HIGH                 |                            |                           |                                      | <del></del>                           |                                   | DRESS 02H)                        |

|                                  | MOS                       | T SIGN                     | IIFICAN<br>GISTE          | NT BYT<br>R (1's c                   | E OF E                                | BYTE<br>nent)                     |                                   |

|                                  | TER MIDDLE                | NAME OF TAXABLE PARTY.     |                           |                                      |                                       |                                   | DDRESS 03H)                       |

| M                                | IDDLE                     | BYTE (                     |                           | rE COU<br>plimen                     |                                       | EGISTE                            | ER<br>                            |

| BYTE COUN                        | TER LOW RE                | GISTER                     |                           |                                      | (WRITE RE                             | GISTERAI                          | DDRESS 04H)                       |

|                                  |                           | ST SIGN<br>JNT RE          |                           |                                      |                                       |                                   |                                   |

| VO REGISTE                       | R                         |                            |                           |                                      | (WRITE RE                             | GISTER—AI                         | ODRESS 05H)                       |

|                                  | LATC                      | HED D                      | ATA TO                    | XD7 T                                | O XD0                                 | PINS                              |                                   |

| NTERRUPT                         | ENABLE 1 RE               | EGISTER                    |                           | <del></del>                          | (WRITE RE                             | GISTER—AL                         | DDRESS 06H)                       |

| CONDI-<br>TION<br>CHANGE         | ATN or<br>RESET<br>CHANGE | SYSTEM<br>PARITY<br>ERROR  | SCSI<br>PARITY<br>ERROR   | TRANSFER<br>COMPLETE                 | TRANSFER<br>REQUEST                   | (RE)-<br>SELECT<br>COMPLETE       | SELEC-<br>TION<br>ATTEMPT-<br>ED  |

|                                  | ENABLE 2 RE               | EGISTER                    | r                         |                                      | (WRITE RE                             | GISTER-AL                         | DDRESS 07H)                       |

| SCSI<br>MASTER<br>INTER-<br>RUPT | BUS FREE<br>DETECT        | HALT<br>INTERRUPT          | TRANSFER<br>DONE          | SCSI<br>TRANSFER<br>COMPLETE         | INVALID<br>(RE)-<br>SELECT            | VALID<br>RESELECT                 | VALID<br>SELECT                   |

| CONTROL R                        | EGISTER                   |                            |                           |                                      | (WRITE RE                             | GISTER—AL                         | DDRESS 08H)                       |

| ENABLE<br>DREQ                   | ENABLE<br>PDREQ           | HALT ON<br>PARITY<br>ERROR | ALWAYS 0                  | ALWAYS 0                             | ENABLE<br>RESELECT                    | ENABLE<br>SELECT                  | AUTO<br>ATTEN-<br>TION<br>ASSERT  |

| COMMAND                          | REGISTER                  |                            |                           |                                      | (WRITE RE                             | GISTER—A                          | DDRESS 09H)                       |

| DISCON-<br>NECT                  | SELECT                    | (RE)-<br>START             | CLEAR                     | NEGATE<br>ATTEN-<br>TION             | ASSERT<br>ATTEN-<br>TION              | NEGATE<br>SCSI<br>RESET<br>SIGNAL | ASSERT<br>SCSI<br>RESET<br>SIGNAL |

| COMMAND                          | REGISTER                  |                            |                           |                                      | (WRITE RE                             | GISTER-A                          | DRESS OAH)                        |

| SET<br>MESSAGE<br>IN             | SET<br>MESSAGE<br>OUT     | RESERVED                   | RESERVED                  | SET<br>STATUS<br>PHASE               | SET<br>COMMAND<br>PHASE               | SET<br>DATA IN                    | RESERVED                          |

| RESERVED                         |                           |                            |                           |                                      | (WRITE RE                             | GISTER—AL                         | DRESS (18H)                       |

| (MSB)                            |                           |                            | RESE                      | RVED                                 |                                       |                                   | (LSB)                             |

| RESERVED                         |                           | ·                          |                           |                                      | (WRITE RE                             | GISTER—AD                         | DRESS OCH)                        |

| (MSB)                            |                           |                            | RESE                      | RVED                                 |                                       |                                   | (LSB)                             |

| DESTINATIO                       | N ID REGIST               | ~                          |                           |                                      |                                       | GISTER—AD                         | DRESS (DH)                        |

| (MSB)                            |                           |                            | DESTIN                    | AOITA                                | IID                                   |                                   | (LSB)                             |

| SCSI ID REG                      | ISTER                     |                            |                           |                                      | (WRITE RE                             | GISTER-AD                         | ORESS (EH)                        |

| (MSB)                            |                           | SC                         | SI ID (I                  | NODE                                 | ID)                                   |                                   | (LSB)                             |

| DATA OUT R                       | EGISTER                   |                            |                           |                                      | (WRITE RE                             | GISTER-AC                         | ORESS OFH)                        |

(MSB) DATA TO BE OUTPUT TO THE SCSI BUS (LSB)

| RESET REC                                                                                                 | ISTER                                         |                             |                                     |                                        | (READ RE                              | EGISTER—AI                             | DDRESS 00                        |

|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------|-------------------------------------|----------------------------------------|---------------------------------------|----------------------------------------|----------------------------------|

|                                                                                                           | XD7-XD0 (IN)                                  |                             |                                     |                                        |                                       |                                        |                                  |

| MODE REG                                                                                                  | ISTER                                         |                             |                                     |                                        | (READ RE                              | GISTER—A                               | DDRESS 0                         |

| RESERVE                                                                                                   |                                               | N TIMEOUT                   | PDREQ<br>LEVEL/<br>PULSED           | DREQ<br>MULTIPLE/<br>SINGLE<br>PULSE   | PARITY<br>CHECK<br>ENABLE/<br>DISABLE | ARBITRA-<br>TION<br>ENABLE/<br>DISABLE | INITIATOI<br>TARGET              |

| BYTE COU                                                                                                  | NTER HIGH                                     | REGISTER                    |                                     |                                        | (READ RE                              | GISTER-AD                              | DRESS 02                         |

| (MSB)                                                                                                     |                                               | MOST                        | SIGNI                               | FICAN                                  | ГВҮТЕ                                 |                                        | (LS                              |

| BYTE COUN                                                                                                 | ITER MIDDLE                                   | REGISTER                    |                                     |                                        | (READ RE                              | GISTER—A                               | DDRESS 0                         |

| (MSB)                                                                                                     | Ŋ                                             | MIDDLE                      | SIGN                                | IFICAN                                 | T BYT                                 | E                                      | (LS                              |

| BYTE COUN                                                                                                 | ITER LOW RE                                   | GISTER                      |                                     |                                        | (READ RE                              | GISTERA                                | ODRESS 0                         |

| (MSB)                                                                                                     |                                               | LEAST                       | SIGNI                               | FICAN                                  | ГВҮТЕ                                 |                                        | (LS                              |

| VO REGISTI                                                                                                | ER                                            |                             |                                     |                                        | (READ RE                              | GISTER—AL                              | DRESS 0                          |

| (MSB)                                                                                                     | LATCHI                                        | ED DAT                      | A FRO                               | M XD7                                  | -XD0 P                                | INS (IN                                | <b>1)</b> (LS                    |

| INTERRUPT                                                                                                 | ENABLE 1 RE                                   | GISTER                      |                                     |                                        | (READ RE                              | GISTER—AI                              | . —                              |

| CONDI-<br>TION<br>CHANGE                                                                                  | ATN or<br>RESET<br>CHANGE                     | SYSTEM<br>PARITY<br>ERROR   | PARITY<br>ERROR                     | TRANSFER<br>DONE                       | TRANSFER<br>REQUEST                   | (RE)-<br>SELECT<br>COMPLETE            | SELEC-<br>TION<br>ATTEMP<br>ED   |

| INTERRUPT                                                                                                 | ENABLE 2 RE                                   | GISTER                      |                                     |                                        | (READ RE                              | GISTER—A                               | DRESS 0                          |

| MASTER<br>INTER-<br>RUPT                                                                                  | BUS FREE<br>DETECT                            | HALT<br>INTERRUPT<br>ENABLE | TRANSFER<br>DONE                    | SCSI<br>TRANSFER<br>COMPLETE           | INVALID<br>(RE)-<br>SELECT            | VALID<br>RESELECT                      | VALID<br>SELEC-<br>TION          |

| CONTROL F                                                                                                 | REGISTER                                      |                             | •                                   |                                        | (READ RE                              | GISTER—AL                              | DRESS 0                          |

| ENABLE<br>DREQ                                                                                            | ENABLE<br>PDREQ                               | HALT ON<br>PARITY<br>ERROR  | ALWAYS 0                            | ALWAYS 0                               | ENABLE<br>RESELECT                    | ENABLE<br>SELECT                       | AUTO<br>ATTEN-<br>TION<br>ASSERT |

| NTERRUPT                                                                                                  | STATUS REG                                    | ISTER                       | •                                   |                                        | (READ RE                              | GISTER—AL                              | ODRESS 0                         |

|                                                                                                           | RE                                            | SERV                        | ED                                  |                                        | SCSI<br>INTER-<br>RUPT                | RESE                                   | RVE                              |

| STATUS 1 R                                                                                                | EGISTER                                       |                             |                                     |                                        | (READ RE                              | GISTERAD                               | DRESS 0                          |

| CONDI-<br>TION<br>CHANGE                                                                                  | ATTN or<br>RESET<br>CHANGE                    | SYSTEM<br>PARITY<br>ERROR   | SCSI<br>PARITY<br>ERROR             | TRANSFER<br>COMPLETE                   | TRANSFER<br>REQUEST                   | (RE)-<br>SELECT<br>COMPLETE            | SELEC-<br>TION AT-<br>TEMPTE     |

| STATUS 2 R                                                                                                | EGISTER<br>T                                  | <del></del>                 | UNSUC-                              | suc-                                   | (READ RE                              | GISTER—AD                              | DRESS OF                         |

| SCSI<br>ATTN<br>SIGNAL                                                                                    | RESERVED                                      | RESERVED                    | CESS<br>(RE)-<br>SELECT<br>COMPLETE | CESSFUL<br>(RE)-<br>SELECT<br>COMPLETE | INVALID<br>(RE)-<br>SELECT            | VALID<br>RESELECT                      | VALID<br>SELEC-<br>TION          |

| STATUS 3 RI                                                                                               | EGISTER                                       |                             |                                     |                                        | (READ RE                              | GISTER-AD                              | DRESS OC                         |

| SCSI<br>ATTN<br>SIGNAL                                                                                    | SCSI<br>RESET                                 | SYSTEM<br>PARITY<br>ERROR   | TRANSFER<br>DONE                    | SCSI<br>TRANSFER<br>COMPLETE           |                                       | BYTE<br>AVAILABLE                      | BYTE RE<br>QUESTE                |

| STATUS 4 R                                                                                                | EGISTER                                       |                             |                                     | ı · <del></del>                        |                                       | GISTER-AD                              |                                  |

| RESERVED BUS FREE DETECTED HALTED ARBITRATION RESERVED RESERVED PHASE PHASE C/D ENCODED ENCODED PHASE L/O |                                               |                             |                                     |                                        |                                       |                                        |                                  |

| SCSI BUS ID                                                                                               | CSI BUS ID REGISTER (READ REGISTER—ADDRESS 0E |                             |                                     |                                        |                                       |                                        |                                  |

| (MSB)                                                                                                     |                                               | SI BUS                      | ID (NC                              | DE SC                                  | URCE                                  | ID)                                    | (LS                              |

| DATA IN REC                                                                                               | SISTER                                        | ··· ··                      |                                     |                                        | (READ RE                              | GISTER-AD                              | DRESS OF                         |

| (MSB)                                                                                                     |                                               | DAT                         | A FRO                               | M BUF                                  | FER                                   | •                                      | (LS                              |

|                                                                                                           |                                               |                             |                                     |                                        |                                       |                                        |                                  |

**Mode Register**

8-Bits Read/Write (ADDRESS 01H)

T-52-33-27

This 8 bit Read/Write register defines the operating mode a hard or soft System Reset. Refer to Table 3 for the of the SCSIC. The bits in this register are reset to zero by description of the Mode Register bits.

# **TABLE 3 - Mode Register**

|         |                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | IADLE                                                                                                                                                                            | - WOUE TO        | -gistoi                         |                                                                                              |  |  |

|---------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------|----------------------------------------------------------------------------------------------|--|--|

| BIT NO. | BIT NAME                                                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                  |                  |                                 |                                                                                              |  |  |

| 0       | I <u>nitiato</u> r/<br>Target                               | Writing a "1" to this bit will place the chip into an initiator mode. Writing a "0" to this bit places the chip into a target mode. The state of this bit will not prevent the chip from being selected or reselected by another device. The state of this bit determines whether the select command will start either the select function or the reselect function.                                                                                                                                                                                                     |                                                                                                                                                                                  |                  |                                 |                                                                                              |  |  |

| 1       | Arbitration<br>Enable/<br>Disable                           | Arbitration phase                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | will occur fo                                                                                                                                                                    | ollowing a B     | us Free Phase                   | to this bit disables Arbitration. An if the <u>Select Command</u> has been able/Disable = 1. |  |  |

| 2       | Parity<br>Check<br>Enable                                   | Writing a "1" to the except Bus Free checked.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Writing a "1" to this bit enables the MSD95C00 parity checking for all SCSI bus phases except Bus Free and Arbitration. When this bit is "0", Parity on the SCSI bus will not be |                  |                                 |                                                                                              |  |  |

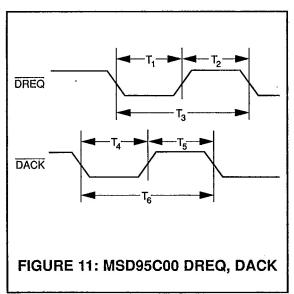

| 3       | DREQ<br><u>Multiple</u> /<br>Single<br><u>Pulse</u><br>Mode | Writing a "1" to this bit will allow the SCSIC to generate up to 12 DREQ pulses before receiving the first DACK from the external controller logic. When this bit is "0", the SCSIC will not generate the next DREQ unless it has received the previous DACK. In both cases, a transfer is not considered complete until the number of DACK's received equals the number of DREQ's generated.                                                                                                                                                                            |                                                                                                                                                                                  |                  |                                 |                                                                                              |  |  |

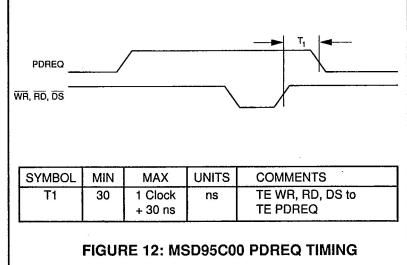

| 4       | PDREQ<br><u>Level/</u><br>Pulsed                            | Writing a "1" to this bit will cause the PDREQ signal to operate as a level. When receiving from the SCSI bus PDREQ will be high as long as the buffer is not empty. When sending to the SCSI bus PDREQ will be high as long as the buffer is not full. Writing a "0" to this bit will cause the PDREQ signal to operate as a pulse. The MSD95C00 will drive PDREQ low if receiving and the Data IN register is read. PDREQ will also be driven low when sending and the Data Out register is written. PDREQ will then be driven high if there is more data to transfer. |                                                                                                                                                                                  |                  |                                 |                                                                                              |  |  |

| 6,5     | Selection<br>Timeout                                        | These two bits ar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | e used to se                                                                                                                                                                     | elect the follo  | owing SCSI S                    | election Timeout:                                                                            |  |  |

|         | Titleout                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Bit 6                                                                                                                                                                            | Bit 5            | Timeout*                        |                                                                                              |  |  |

|         |                                                             | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0<br>0<br>1<br>1                                                                                                                                                                 | 0<br>1<br>0<br>1 | 839ms<br>210ms<br>52ms<br>1.6ms |                                                                                              |  |  |

|         |                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | *based on 20MHz crystal operation                                                                                                                                                |                  |                                 |                                                                                              |  |  |

| 7       | Reserved.                                                   | Must be reset to '                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Must be reset to "0".                                                                                                                                                            |                  |                                 |                                                                                              |  |  |

#### Byte Counter High Register 8-Bit Read/Write (Address 02H)

This 8-bit Read/Write register holds the most significant byte that is to be loaded into the Byte Counter. The data is transferred from the Byte Counter High Register into the Byte Counter when the Byte Counter Low register is loaded. Bit 7 is the MSB and bit 0 is the LSB. The Byte Counter registers are loaded with the 1's complement of the desired byte count.

#### **Byte Counter Middle Register** 8-Bit Read/Write (Address 03H)