# 512 Bit Electrically Alterable Read Only Memory

- 32 Word x 16 Bit Organization

- 5 Bit Binary Addressing

- +5, -28 V Power Supplies

- Word Alterable

- 10 Year Data Storage for ER2051 (at +70°C)

- 1 Year Data Storage for ER2051IR (at +85°C) and ER2051HR (at +125°C)

- TTL Compatibility with Pull-Up Resistors on Inputs

- Tri-State Outputs

- Read Time: 1µs (ER2051), 2µs (ER2051IR and ER2051HR)

- Write/Erase Time: 50ms (ER2051), 100ms (ER2051HR)

- No Voltage Switching Required

- Chip Select

- Two Extended Temperature Ranges;

- -40°C to +85°C ER2051IR

- -55°C to +125°C ER2051HR

# DESCRIPTION

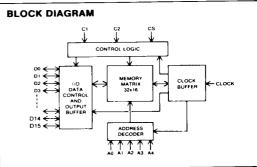

The ER2051, ER20511R and ER2051HR are fully decoded 32 x 16 electrically erasable and reprogramable ROMs. Write, erase, and read voltages are switched internally via a 2-bit code applied to C1 and C2

Data is stored by applying negative writing pulses that selectively tunnel charge into the oxide-nitride interface of the gate insulator of the 512 MNOS memory transistors. When the writing voltage is removed the charge trapped at the interface is manifested as a negative shift in the threshold voltage of the selected memory transistors.

The EAROM may be operated with the  $V_{SS}$  power supply between +5V and +10Volts, as long as the  $V_{SS}$ — $V_{GG}$  always equals 33 Volts. Thus,  $V_{SS}$  can be +5Volts for TTL compatibility or up to +10Volts for CMOS compatibility, if  $V_{GG}$  is appropriately adjusted. The ER20511R and ER2051HR are screened to Mil Std. 883B/

The ER20511R and ER2051HR are screened to Mil Std. 8838/ method 5004.1/level B, pre-cap visual inspection, environmental testing, burn-in and external visual. They are available in 28 lead ceramic dual in line packages.

# **OPERATION**

Data is stored in a two transistor memory cell. After the cell is preconditioned by an erase signal (which causes a positive shift in the threshold of both transistors), data is written into one of the transistors making its threshold more negative. A sensing flip flop is used to read the memory cell and presents a logic high or low to the output depending upon which transistor is written.

It is important to note two things: first, that an erase is required before a wire to precondition the cell, and second, that after an erase, both transistors will have the same threshold voltage and valid data will not be present at the output.

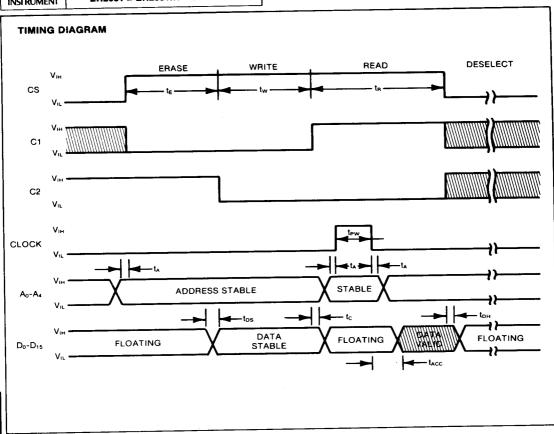

The ER2051, ER2051IR and ER2051HR EAROM's use internal dynamic, edge triggered circuits. This requires either a mode change, a clock, or a transition of the chip select between successive operations. Thus successive operations in the same mode must be separated by transitions of one of these four lines. Clock pulses are not normally required during erase or write operations, but are needed for successive operations if the chip select is held high, i.e., applications where one EAROM is used.

#### PIN FUNCTIONS

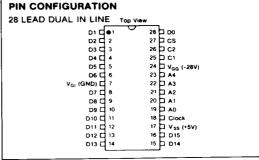

| Pin No         | Name<br>A <sub>0</sub> -A <sub>4</sub> | Function  5-Bit Word Address.                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|----------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 19, 20, 21, 22 |                                        |                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| 1-6, 8-14, 28  | D <sub>0</sub> -D <sub>15</sub>        | Data input and output pins.                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| 27             | cš                                     | Chip Select. Chip selected at logic "1". When chip select is at logic "0", outputs are open circuit, read, write and erase are disabled. Power is reduced.                                                                                                                                                                |  |  |  |  |  |  |

| 25, 26         | C1, C2                                 | Mode Control Inputs.  C1 C2 0 1 Erase Mode: stored data is erased at addressed location. 1 Don't Care Read Mode: addressed data read after clock pulse. Output data retained at output pins until chip deselected or control lines switched.  0 Write Mode: input data written at addressed location. Clock not required. |  |  |  |  |  |  |

| 18             | CLK                                    | Clock input. Pulse to logic "1" for read operation.                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| 17             | V <sub>ss</sub>                        | Substrate supply. Normally at +5 volts.                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| 7              | V <sub>GI</sub>                        | Ground Input.                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| 24             | V <sub>GG</sub>                        | Power Supply Input. Normally at -28 volts.                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

10-48

### **ELECTRICAL CHARACTERISTICS**

Maximum Ratings\*

# Standard Conditions (for TTL compatibility)

$V_{SS} = +5V \pm 5\%$  $V_{GG} = -28V \pm 5\%$

VGI = GND

Operating Temperature T<sub>A</sub> = 0°C to +70°C for ER2051

$T_A = -40$ °C to +85°C for ER2051 IR

$T_A = -55^{\circ} \text{ C to } + 125^{\circ} \text{ C for ER2051 HR}$

Output Load = 100pf, 1 TTL load

\* Exceeding these ratings could cause permanent damage to the device. This is a stress rating only and functional operation of this device at these conditions is not implied—operating ranges are specified in Standard Conditions. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Data labeled "typical" is presented for design guidance only and is not guaranteed.

|                                  |                 | ER2051                           |          |          | ER2051               | ER2051 IR/ER2051 HR |                                                  |          |                                                                |

|----------------------------------|-----------------|----------------------------------|----------|----------|----------------------|---------------------|--------------------------------------------------|----------|----------------------------------------------------------------|

| Characteristics                  | Sym             | Min.                             | Typ.**   | Max.     | Min.                 | Typ.*               |                                                  | Units    | Conditions                                                     |

| DC CHARACTERISTICS               |                 |                                  |          |          |                      |                     | <del>                                     </del> | <b>†</b> |                                                                |

| Input Logic "1"                  | V <sub>IH</sub> | Vss -1.5                         | _        | Vss +0.3 | V <sub>SS</sub> -1.5 | l _                 | Vss +0.3                                         | l v      |                                                                |

| Input Logic "0"                  | VIL             | Vss -15                          |          | 0.8      | V <sub>SS</sub> -10  | _                   | 0.6                                              | ľ        | į                                                              |

| Output Logic "1"                 | Von             | Vss 1.5                          |          |          | V <sub>SS</sub> -1.5 | l _                 | 0.0                                              | v        | I <sub>OH</sub> = 100μA                                        |

| Output Logic "0"                 | Vol             | _                                | l _      | 0.6      | VSS 1.5              | _                   | 0.6                                              | ľ        | $I_{OL} = 1.6 \text{mA for } V_{SS} = +5 \text{V}$             |

| Input Leakage                    | IL              | _                                | 2        | 10       | _                    | 2                   | 10                                               | μA       | $V_{IN} = V_{SS} - 15$                                         |

| Output Leakage                   | Io              |                                  | 2        | 10       |                      | 2                   | 10                                               | μA       |                                                                |

| Power Supply Current             | -0              |                                  | _        | ,,,      | _                    | _                   | "                                                | μΑ.      | Chip deselected                                                |

| Read                             | Igg             | _                                |          | 14       | _                    | •                   | 40                                               |          |                                                                |

| Write                            | Igg             | _                                | _        | 11       | _                    | -                   | 18                                               | mA       | l <b>( .</b>                                                   |

| Erase                            | IGG             | _                                | _        | 11       | _                    | _                   | 15                                               | mA       | Igg returned                                                   |

| Deselected                       | Icc             |                                  | _        | 9        | _                    | _                   | 15                                               | mA       | through Vss                                                    |

| AC CHARACTERISTICS               | 166             | _                                | _        |          | _                    | _                   | 12                                               | mA       | <b>'</b>                                                       |

| Access Time                      | tacc            |                                  |          | 1        | _                    | _                   | 2                                                |          |                                                                |

| Clock Pulse Width                | tew             | 2                                | _        | 20       | 2                    | _                   | 20                                               | μs       |                                                                |

| Erase Cycle Time                 | t∈              | 50                               |          | 200      | 100                  | _                   | 200                                              | μs<br>ms |                                                                |

| Write Cycle Time                 | tw              | 50                               | _        | 200      | 100                  |                     | 200                                              |          |                                                                |

| Read Cycle Time                  | ta              | 3.5                              | _        | 24       | 4.5                  | _                   | 25                                               | ms       |                                                                |

| Address to Clock Time            | ta              | 50                               | _ 1      |          | 50                   | _                   | 25                                               | μs       |                                                                |

| Data Set Up Time                 | tos             | 50                               | _ ]      | _ !      | 50                   | _                   | _                                                | ns<br>ns |                                                                |

| Data Hold Time                   | ton             | 50                               |          | _ 1      | 50                   |                     |                                                  | ns       |                                                                |

| Control to Address & Data Change | tc              | 0                                | _        | [        | 0                    | _                   |                                                  |          |                                                                |

| Number of Reads/Word Refresh     | Nea             | 10''                             | _        | _        | 10''                 | _                   | _                                                | ns       |                                                                |

| Number of Erase/Write Cycles     | Nw I            | 10 <sup>6</sup>                  | _ 1      | _        | 10 <sup>5</sup>      | _                   |                                                  |          |                                                                |

| Input Capacitance (all pins)     | C10             | _                                | 8        | 15       |                      | ĺ                   |                                                  | pf       |                                                                |

| Unpowered Data Storage Time      | ts              | 10                               | _        | - 15     | 1                    | 8                   | 15                                               | ' 1      | *********                                                      |

| Power Dissipation Read Cycle     | Po              | ]                                | 450      | 500      |                      | 450                 | 500                                              | Years    | at max temperature                                             |

| ,                                | Pp              | 1                                |          |          | - 1                  | - 1                 | 500                                              | mW       | at 25°C $V_{SS} = +5$ , $V_{GG} = -29$                         |

| 1                                | Pp              | not applicable<br>not applicable |          |          | -                    | _                   | 600                                              | mW<br>mW | at $125^{\circ}$ C $V_{ss} = +5$ , $V_{gg} = -29$              |

| Pulse Rise, Fall Time            | to to           | 10                               | _  <br>_ | - 1      | _                    | _                   |                                                  | 11144    | at $-55^{\circ}$ C V <sub>ss</sub> = +5, V <sub>ss</sub> = -29 |

| Tunical values are at 1050.0     | la: l:          | 10                               |          | 100      | 10                   |                     | 100                                              | ns       |                                                                |

<sup>\*\*</sup>Typical values are at +25°C and nominal voltages.